ARM七种运行模式

ARM单片机简介

电子产业链全程电子商务平台|旗下网站华强电子网华强LED网华强手机制造网华强电子交易所华强电子检测中心外贸通English|繁体|帮助中心|产品服务会员套餐诚易通600条竞价排名ISCP现货认证BCP品牌认证中国制造委托交易洽洽酷管家旺铺推介竞标推广服务在线交易诚信保证服务手机华强电子网华强手机制造网超级买家|进入互联商务系统上传IC库存参与竞价排名发布求购信息查看客户评价修改企业网站发布元器件发布推介信息管理询报价查看客户留言修改注册信息[当前1041位会员在线]华强电子网购物车首页供应信息中国制造求购信息诚信交易技术资料求职招聘商情资讯商友社区客服热线:400-887-3118位置:首页技术资料电子维基arm单片机电子维基arm单片机[浏览次数:334次]arm单片机是以ARM处理器为核心的一种单片微型计算机,是近年来随着电子设备智能化和网络化程度不断提高而出现的新兴产物。

ARM是一家微处理器设计公司的名称,ARM既不生产爱心篇也不销售芯片,是专业从事技术研发和授权转让的公司,世界知名的半导体电子公司都与ARM简历了合作伙伴关系,包括国内许多公司也从ARM购买芯核技术用于设计专用芯片。

arm单片机以其低功耗和高性价比的优势逐渐步入高端市场,成为了时下的主流产品。

目录arm单片机的优势arm单片机的结构特性arm单片机的工作状态和模式arm单片机的寄存器结构arm单片机的常见异常arm单片机的应用arm单片机的发展趋势arm单片机的优势ARM单片机采用了新型的32位ARM核处理器,使其在指令系统,总线结构,调试技术,功耗以及性价比等方面都超过了传统的51系列单片机,同时arm 单片机在芯片内部集成了大量的片内外设,所以功能和可靠性都大大提高。

arm单片机的结构特性具有统一和固定长度的指令域,使指令集和指令译码都大大简化具有一个大而统一的寄存器文件,大多数数据操作都在寄存器中完成,使指令执行速度更快采用加载/存储结构,使数据处理时只对寄存器操作,而不直接对存储器操作寻址方式简单而灵活,所有加载/存储的地址都只由寄存器的内容和指令域决定,执行效率高每一条数据处理指令都对算术逻辑单元和移位寄存器进行控制,以最大限度的提高算术逻辑单元和移存器的利用率采用自动增减地址的寻址方式,有利于优化循环程序的执行引入多寄存器加载/存储指令,有利于实现数据吞吐量的最大化arm单片机的工作状态和模式从编程的角度看,ARM处理器的工作状态通常有以下两种:1、ARM状态,此时处理器执行32位的字对齐的ARM指令2、Thumb状态,此时处理器执行16位的,半字对齐的Thumb指令当ARM处理器执行32位ARM指令集中的指令时,工作在ARM状态,执行16位Thumb指令集中的指令时,工作在Thumb状态,通常在刚加点开始执行代码时处于ARM状态,然后在程序的执行过程中,只要满足一定条件,随时可以在两种工作状态间切换,并且这种切换并不影响处理器的工作模式和相应寄存器中的内容。

ARM的七种异常类型

ARM7支持六种操作模式:(1)用户模式(usr):正常的程序执行状态(2)FIQ模式(fiq):支持数据传送或通道处理(3)IRQ模式(irq):用于通用的中断处理(4)管理模式(svc):用于操作系统的保护模式(5)异常模式(abt):数据或者指令预取异常时进入(6)无定义模式(und):当无定义指令被执行时进入(7)软件控制,外部中断,异常处理都可以改变操作模式。

大部分的应用程序在用户模式下执行。

其他模式,比如管理模式,在中断、异常服务、或者访问被保护资源时进入。

ARM 的中央寄存器集是16 个用户寄存器R0 – R15。

这些寄存器均是32 位宽度,R0 – R12 没有其他特殊功能,寄存器R13 – R15在CPU中有特殊功能。

R13被用作栈指针(stack pointer,SP)。

R14被称为链接寄存器(link register, LR),当调用一个函数时返回地址被自动保存到链接寄存器,在函数返回时有效。

这使得快速进入和返回“叶”函数(不调用其他函数的函数)成为可能。

如果函数是分支的一部分(即该函数将调用另一个函数),链接寄存器必须入栈(R13)。

R15 是程序计数器(program counter, PC)。

有趣的是,许多指令也可以在R13 – R15中执行,就像它们是标准的用户寄存器。

ARM中断的问题ARM的七种异常类型---------1> 复位异常2> 数据访问中止异常3> 快速中断请求异常4> 一般中断请求5> 预取指令异常6> 软件中断异常7> 未定义异常-------------------------问题:1> 为什么除了进入复位异常模式外,在别的异常处理模式中都允许FIQ中断?2> 数据访问中止异常的优先级大于 FIQ异常,为什么在数据访问异常处理模式中,还允许 FIQ中断?这样不就成了:在高优先级异常处理中允许低优先级的中断发生?即使这样,因为FIQ中断的优先级 < 数据异常中断优先级,也不会进入 FIQ中断处理程序啊,这样不就更没有用处了??ARM体系的各种异常的分析(学习日记)- [ARM7TDMI]版权声明:转载时请以超链接形式标明文章原始出处和作者信息及本声明/logs/10669519.html1.复位异常(1)当内核的nRESET信号被拉低时,ARM处理器放弃正在执行的指令,当nRESET信号再次变高时,ARM处理器进行复位操作;(2)系统复位后,进入管理模式对系统进行初始化,复位后,只有PC(0x00000000)和CPSR (nzcvqIFt_SVC)的值是固定的,另外寄存器的值是随机的。

ARM7跟ARM9的区别跟ARM体系结构新

ARM7与ARM9的区别及ARM体系结构一、 ARM7与ARM9的区别新一代的ARM9处理器,通过全新的设计,采用了更多的晶体管,能够达到两倍以上于ARM7处理器的处理能力。

这种处理能力的提高是通过增加时钟频率和减少指令执行周期实现的。

1 时钟频率的提高ARM7处理器采用3级流水线,而ARM9采用5级流水线。

增加的流水线设计提高了时钟频率和并行处理能力。

5级流水线能够将每一个指令处理分配到5个时钟周期内,在每一个时钟周期内同时有5个指令在执行。

在同样的加工工艺下,ARM9TDMI处理器的时钟频率是ARM7TDMI的1.8~2.2倍。

2 指令周期的改进指令周期的改进对于处理器性能的提高有很大的帮助。

性能提高的幅度依赖于代码执行时指令的重叠,这实际上是程序本身的问题。

对于采用最高级的语言,一般来说,性能的提高在30%左右。

2.1 loads 指令矛n stores指令指令周期数的改进最明显的是loads指令和stores指令。

从ARM7到ARM9这两条指令的执行时间减少了30%。

指令周期的减少是由于ARM7和ARM9两种处理器内的两个基本的微处理结构不同所造成的。

(1)ARM9有独立的指令和数据存储器接口,允许处理器同时进行取指和读写数据。

这叫作改进型哈佛结构。

而ARM7只有数据存储器接口,它同时用来取指令和数据访问。

(2)5级流水线引入了独立的存储器和写回流水线,分别用来访问存储器和将结果写回寄存器。

以上两点实现了一个周期完成loads指令和stores指令。

2.2 互锁(interlocks)技术当指令需要的数据因为以前的指令没有执行完而没有准备好就会产生管道互锁。

当管道互锁发生时,硬件会停止这个指令的执行,直到数据准备好为止。

虽然这种技术会增加代码执行时间,但是为初期的设计者提供了巨大的方便。

编译器以及汇编程序员可以通过重新设计代码的顺序或者其他方法来减少管道互锁的数量。

2.3 分枝指令ARM9和ARM7的分枝指令周期是相同的。

ARM微处理器的七种运行模式

ARM微处理器的七种运⾏模式

ARM微处理器的七种运⾏模式:

1. ⽤户模式(usr):正常的程序执⾏状态

2. 快速中断模式(fiq):⽤于处理快速中断,对⾼速数据传输或通道处理。

3. 中断模式(irq):对⼀般情况下的中断进⾏处理。

4. 管理模式(svc):操作系统使⽤的保护模式,处理软件中断swi reset。

5. 系统模式(sys):运⾏具有特权的操作系统任务

6. 数据访问终⽌模式(abt):数据或指令预取终⽌时进⼊该模式,可⽤于处理存储器故障、实现虚拟存储器和存储器保护。

7. 未定义指令终⽌模式(und):未定义的指令执⾏时进⼊该模式,处理未定义的指令陷阱,当未定义的指令执⾏时进⼊该模式,可⽤于

⽀持硬件协处理器的软件仿真。

特别说明

运⾏模式可以通过软件来进⾏模式切换,或者发⽣各类中断、异常时CPU⾃动进⼊相应的模式。

除⽤户模式外,其余6种⼯作模式都属于特权模式。

特权模式中除了系统模式以外的其余5种模式称为异常模式。

⼤多数程序运⾏于⽤户模式。

进⼊特权模式是为了处理中断、异常、或者访问被保护的系统资源。

嵌入式课后习题答案

第八章

一、填空题。

1、Makefile、配置文件、配置工具。

2、配置命令解释器、配置用户界面。

arch:arch目录包括了所有和体系结构相关的核心代码。include:include目录包括编译核心所需要的大部分头文件,例如与平台无关的头文件在include/linux子目录下;init:init目录包含核心的初始化代码(不是系统的引导代码),有main.c和Version.c两个文件;mm:mm目录包含了所有的内存管理代码。与具体硬件体系结构相关的内存管理代码位于arch/*/mm目录下;drivers:drivers目录中是系统中所有的设备驱动程序。它又进一步划分成几类设备驱动,每一种有对应的子目录,如声卡的驱动对应于drivers/sound;ipc:ipc目录包含了核心进程间的通信代码;modules:modules目录存放了已建好的、可动态加载的模块;fs:fs目录存放Linux支持的文件系统代码。不同的文件系统有不同的子目录对应,如ext3文件系统对应的就是ext3子目录;Kernel:Kernel内核管理的核心代码放在这里。同时与处理器结构相关代码都放在arch/*/kernel目录下;net:net目录里是核心的网络部分代码,其每个子目录对应于网络的一个方面;lib:lib目录包含了核心的库代码,不过与处理器结构相关的库代码被放在arch/*/lib/目录下;scripts:scripts目录包含用于配置核心的脚本文件;documentation:documentation目录下是一些文档,是对每个目录作用的具体说明。

ARM应用系统开发详解(入门资料)

ARM应用系统开发详解(入门资料)第1章ARM微处理器概述本章简介ARM微处理器的一些基本概念、应用领域及特点,引导读者进入ARM技术的殿堂。

本章主要内容:- ARM及相关技术简介- ARM微处理器的应用领域及特点- ARM微处理器系列- ARM微处理器的体系结构- ARM微处理器的应用选型1.1 ARM-ADV ANCED RISC MachinesARM(ADV ANCED RISC Machines),既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。

1991年ARM公司成立于英国剑桥,主要出售芯片设计技术的授权。

目前,采用ARM技术知识产权(IP)核的微处理器,即我们通常所说的ARM微处理器,已遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,基于ARM技术的微处理器应用约占据了32位RISC微处理器75%以上的市场份额,ARM技术正在逐步渗入到我们生活的各个方面。

ARM公司是专门从事基于RISC技术芯片设计开发的公司,作为知识产权供应商,本身不直接从事芯片生产,靠转让设计许可由合作公司生产各具特色的芯片,世界各大半导体生产商从ARM公司购买其设计的ARM微处理器核,根据各自不同的应用领域,加入适当的外围电路,从而形成自己的ARM微处理器芯片进入市场。

目前,全世界有几十家大的半导体公司都使用ARM公司的授权,因此既使得ARM技术获得更多的第三方工具、制造、软件的支持,又使整个系统成本降低,使产品更容易进入市场被消费者所接受,更具有竞争力。

1.2 ARM微处理器的应用领域及特点1.2.1 ARM微处理器的应用领域到目前为止,ARM微处理器及技术的应用几乎已经深入到各个领域:1、工业控制领域:作为32的RISC架构,基于ARM核的微控制器芯片不但占据了高端微控制器市场的大部分市场份额,同时也逐渐向低端微控制器应用领域扩展,ARM微控制器的低功耗、高性价比,向传统的8位/16位微控制器提出了挑战。

最新嵌入式期末考试试卷

1、 ARM 微处理器有 7种工作模式,它们分为两类 非特权模式 、 特权模式 。

其中用户模式属于 非特权模式ARM 处理器有两种总线架构,数据和指令使用同一接口的是 冯诺依曼 ,数据和指令分开使用不同接口的是 哈佛结 4、 ARM 微处理器复位后,PC 的地址通常是 0x0 ,初始的工作模式是Supervisor 。

5、 ARM 微处理器支持虚拟内存,它是通过系统控制协处理器 CP15 和MMU (存储管理部件)来进行虚拟内存的存储和管理。

当系统发生 数据 异常和指令领取 异常时,异常处理程序透过嵌入式操作系统的内存管理机制,通过MMU 交换物理内存和虚拟内存的页面,以保证程序正常执行。

6、 编译链接代码时,有两种存储代码和数据的字节顺序,一种是 小端对齐 ,另一种是 打断对齐7、 构建嵌入式系统开发环境的工具链有多种,其中开放源码的工具链是 GNU 工具链 ,ARM 公司提供的工具链是 ADS工具链计算机有CISC 和RISC 两种类型,以ARM 微处理器为核心的计算机属于 RISC 类型,其指令长度是 定长的 1、 目前使用的嵌入式操作系统主要有哪些?请举出六种较常用的。

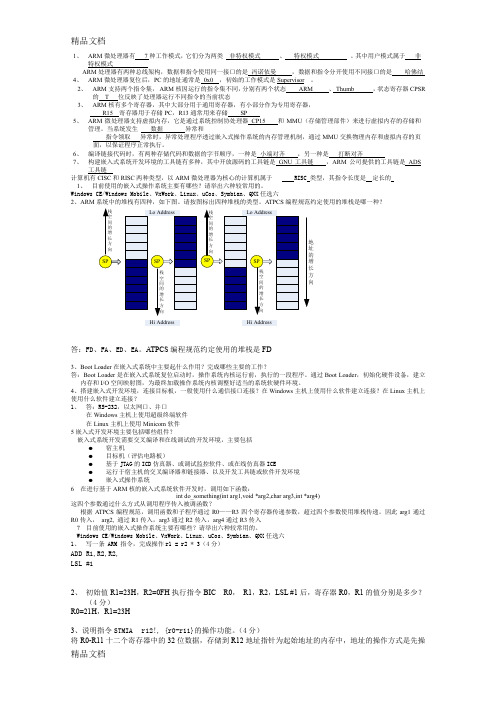

Windows CE/Windows Mobile 、VxWork 、Linux 、uCos 、Symbian 、QNX 任选六2、ARM 系统中的堆栈有四种,如下图。

请按图标出四种堆栈的类型。

ATPCS 编程规范约定使用的堆栈是哪一种?答:FD 、FA 、ED 、EA 。

A TPCS 编程规范约定使用的堆栈是FD3、Boot Loader 在嵌入式系统中主要起什么作用?完成哪些主要的工作?答:Boot Loader 是在嵌入式系统复位启动时,操作系统内核运行前,执行的一段程序。

通过Boot Loader ,初始化硬件设备,建立内存和I/O 空间映射图,为最终加载操作系统内核调整好适当的系统软硬件环境。

4、搭建嵌入式开发环境,连接目标板,一般使用什么通信接口连接?在Windows 主机上使用什么软件建立连接?在Linux 主机上使用什么软件建立连接?1、 答:RS-232,以太网口、并口在Windows 主机上使用超级终端软件 在Linux 主机上使用Minicom 软件 5嵌入式开发环境主要包括哪些组件?嵌入式系统开发需要交叉编译和在线调试的开发环境,主要包括● 宿主机 ● 目标机(评估电路板) ● 基于JTAG 的ICD 仿真器、或调试监控软件、或在线仿真器ICE ● 运行于宿主机的交叉编译器和链接器、以及开发工具链或软件开发环境 ● 嵌入式操作系统6 在进行基于ARM 核的嵌入式系统软件开发时,调用如下函数:int do_something(int arg1,void *arg2,char arg3,int *arg4)这四个参数通过什么方式从调用程序传入被调函数?根据ATPCS 编程规范,调用函数和子程序通过R0——R3四个寄存器传递参数,超过四个参数使用堆栈传递。

ARM 处理器工作状态与工作模式 ARM 体系结构所支持的异常

深入内核逻辑一个宇宙通用的事实是:结构决定功能!我们以典型的ARM嵌入式处理器内核的一般特征为例,,看看ARM设想的功能是如何被“构造”出来的。

主要说两个内容:•ARM处理器工作状态与工作模式•ARM体系结构所支持的异常基础概念字(Word):在ARM体系结构中,字的长度为32位(在8位/16位处理器体系结构中,字的长度一般为16位)。

•半字(Half-Word):在ARM体系结构中,半字的长度为16位,与8位/16位处理器体系结构中字的长度一致。

•字节(Byte):在ARM体系结构和8位/16位处理器体系结构中,字节的长度均为8位。

问:计算机存储设备是按______ (A:字Word,B:半字Half-Word,C:字节Byte)编址的。

处理器工作状态ARM状态:正在执行ARM指令的处理器的状态。

Thumb状态:正在执行Thumb指令的处理器的状态。

不同的状态下,代码密集度不同,,ARM状态按字(32位)存储代码,Thumb状态按半字(16位)存储代码,这种特性有利于我们在必要的时候调整单位存储空间的代码容量,压缩代码占用空间。

这两个状态可以根据情况软件切换,,,后面我们还会再次提到这个话题,,,Note:对于ARM 32位处理器,两种状态下代码存储密集度不同,但在执行时仍是32位的!这就是说,代码可以压缩,但执行效率并不会下降,CPU仍是按字执行的啊!不过,Thumb状态下的指令的使用有某些限制,属于ARM状态下的指令的一个子集。

另外,调整代码密集度的优点在后来的ARM一些版本中可以自动切换,,,不需要程序员再过多费神,这就是所谓Thumb2状态:一种混合型指令集,降低功耗具有高代码压缩性处理器工作模式回顾,前面说过ARM内核采用了大量内部寄存器的特性,,以便有利于支持流水线技术,,,那么这些“大量内部寄存器”如何运作?工作模式本质上就是指内核中的这堆寄存器的功能分配和使用方法ARM处理器内部寄存器一起看,,这里一共有37个32位寄存器•其中,31个通用寄存器,包括程序寄存器(PC);•6个状态寄存器:。

中山大学嵌入式系统练习与参考答案

思考与练习1、 ARM7TDMI 中的T、D、M、I 的含义是什么?答:T 表示支持高密度Thumb 指令集;D 表示支持片上调试;M 表示增加了64 位乘法指令;I 表示带有EmbededICE 观察点硬件。

2、分别列举ARM 的处理器模式和状态。

答:ARM 处理器共有7 种运行模式。

分别是用户模式(User,usr),快速中断模式(FIQ ,fiq),外部中断模式(IRQ,irq),特权模式(Supervisor,svc),数据访问模式(Abort,abt),未定义指令中止模式(Undefined, und),系统模式(System,sys)。

ARM 处理器有两种状态,ARM 状态(执行32 位字方式的ARM 指令)和Thumb 状态(执行16 位半字方式的Thumb 指令)。

3、 PC 和LR 分别使用哪个寄存器?答:PC 使用了R15 寄存器。

LR 使用了R14 寄存器。

4、定义R0=0x12345678,假设使用存储指令将R0 的值放在0x4000 单元中。

如果存储器格式为大端格式可,请写出在执行加载指令将存储器0x4000 单元的内容取出存放到R2 寄存器操作后所得R2 的值。

如果存储器格式为小端格式,所得的R2 的值又为多少?低地址0x4000 单元的字节内容分别是多少?答:按大端模式将数据0x12345678 保存在地址0x4000 处,则数据高位存放在地址此时按大端模式从地址0x4000 处的1 字数据读取到R2 则其内容为0x12345678。

如果按小端模式将数据0x12345678 保存在地址0x4000 处,则数据低位存放在此时用按小端模式从地址0x4000 读取1 字数据到R2,将会得到0x12345678。

5、简单描述一下ARM7 的三级流水线,并说明其对程序设计的影响?答:ARM7TDMI 使用流水线来增加处理器指令流的速度。

这样可使几个操作同时进行,并使处理和存储器系统连续操作,能提供0.9MIPS/MHz 的指令执行速度。

ARM嵌入式系统开发与应用课后题答案与习题

课后题答案:第一章1.写出下列英文缩写的英文原文及中文含义。

RAM随机存储器 DRAM动态随机存储器 ROM只读存储器PROM可编程只读存储器 EPROM可插除可编程只读存储器 CANCAN总线RTOS实时操作系统 SOPC片上可编程系统 ICE硬件调试器 FI快速终端请求EEPROM电可插除可编程只读存储器 API应用程序接 DMA直接内存存取RISC精简指令集计算机 SPI串行万维指令 MMU存储管理单元UART异步接受发送装置 ARM先进RISC存储器 SWI软件终端指令2、什么是嵌入式系统? P3嵌入式系统是用于检测、控制、辅助、操作机械设备的装置。

以应用为中心,一计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积和功耗等严格要求的专用计算机系统。

3、是比较嵌入式系统与通用PC的区别。

P3(1)嵌入式系统是专用的计算机系统,而PC是通用的计算机系统。

(2)技术要求不同,通用PC追求高速、海量的数据运算;嵌入式要求对象体系的智能化控制。

(3)发展方向不同,PC追求总线速度的不断提升,存储容量不断扩大;嵌入式追求特定对象系统的智能性,嵌入式,专用性。

4、嵌入式体统有哪些部分组成?简单说明各部分的功能与作用(1)硬件层是整个核心控制模块(由嵌入式微处理器、存储系统、通信模块、人机接口、其他I/O 接口以及电源组成),嵌入式系统的硬件层以嵌入式微处理器为核心,在嵌入式微处理器基础上增加电源电路、时钟电路、和存储器电路(RAM和ROM等),这就构成了一个嵌入式核心控制模块,操作系统和应用程序都可以固化在ROM中。

(2)中间层把系统软件与底层硬件部分隔离,使得系统的底层设备驱动程序与硬件无关。

一般包括硬件抽象层(Hardware Abstract Layer,HAL)和板级支持包(Board Support Package,BSP)。

(3)软件层由实时操作系统(Real Time Operating System,RTOS)、文件系统、图形用户接口(Graphical User Interfaces,GUI)、网络组件组成。

嵌入式期末复习题_(含答案)

期末考试复习题一、填空题1. ARM微处理器有7种工作模式,它们分为两类_特权模式_、_非特权模式_其中用户模式属于_非特权模式__。

2. ARM微处理器共有__37_个__32__位寄存器,其中__31_个为通用寄存器,_6___个为状态寄存器。

3. 嵌入式系统一般哪4个部分组成( 嵌入式处理器、外围设备、嵌入式操作系统(可选)、嵌入式应用软件)4. 协处理器主要控制:___片内的MMU __、___指令和数据缓存___、___写缓冲___。

5. ARM嵌入式系统主要由___相关支撑硬件___、___ARM处理器___和__嵌入式软件系统____构成。

6. S3C2410芯片外部寻址空间是1G,被分成___8__个存储块,每块_ 128 _MB。

SDRAM 存储器应连接到第____7或8__个存储块。

7. 操作系统是联接硬件与应用程序的系统程序,其基本功能有进程管理、内存管理、文件系统管理、I/O资源管理。

8. 常用的嵌入式外围设备有存储设备_、通信设备____和___显示设备___三类。

10. 嵌入式系统是用来控制或者监视哪些设备( )11. 嵌入式系统的三个基本要素。

引导程序内核文件系统12. 链接分为:(硬链接)和( 软链接)。

13. 数据寄存器,其中控制寄存器的主要功能是设置_引脚的功能_,数据寄存器的功能是从寄存器读取数据或者向寄存器写入数据。

15. 目前流行的嵌入式操作系统主要有:_ WinCE_、_ Vxworks__、_ Linux/µCLinux_和_µC/OS-II、PalmOS____。

16. 嵌入式操作系统的调试一般包括:___操作系统__调试和___应用程序__调试。

17. ARM字数据存储格式有:大端格式和小端格式。

18. 某文件的权限为:drw-r--r--,用数值形式表示该权限,则该八进制数为:( 644 ),该文件属性是( 目录)。

19. 在宿主机上使用编译器软件将嵌入式应用。

ARM的七种工作模式

ARM的七种⼯作模式⼀、ARM处理器7种⼯作模式(特权模式特权模式异常模式)1. ⽤户模式(USR):正常程序执⾏模式,不能直接切换到其他模式2. 系统模式(SYS):运⾏操作系统的特权任务,与⽤户模式类似,但具有可以直接切换到其他模式等特权3. 快中断模式(FIQ):⽀持⾼速数据传输及通道处理,FIQ异常响应时进⼊此模式4. 中断模式(IRQ):⽤于通⽤中断处理,IRQ异常响应时进⼊此模式5. 管理模式(SVC):操作系统保护模式,系统复位和软件中断响应时进⼊此模式(由系统调⽤执⾏软中断SWI命令触发)6. 中⽌模式(ABT):⽤于⽀持虚拟内存和/或存储器保护,在ARM7TDMI没有⼤⽤处7. 未定义模式(UND):⽀持硬件协处理器的软件仿真,未定义指令异常响应时进⼊此模式8. 表3-1 ARM处理器⼯作模式处理器⼯作模式特权模式异常模式说明⽤户(user)模式⽤户程序运⾏模式系统(system)模式该组模式下可以任意访问系统资源运⾏特权级的操作系统任务⼀般中断(IRQ)模式通常由系统异常状态切换进该组模式普通中断模式快速中断(FIQ)模式快速中断模式管理(supervisor)模式提供操作系统使⽤的⼀种保护模式,swi命令状态中⽌(abort)模式虚拟内存管理和内存数据访问保护未定义指令终⽌(undefined)模式⽀持通过软件仿真硬件的协处理CPU的模式可以简单的理解为当前CPU的⼯作状态,⽐如:当前操作系统正在执⾏⽤户程序,那么当前CPU⼯作在⽤户模式,这时⽹卡上有数据到达,产⽣中断信号,CPU⾃动切换到⼀般中断模式下处理⽹卡数据(普通应⽤程序没有权限直接访问硬件),处理完⽹卡数据,返回到⽤户模式下继续执⾏⽤户程序。

特权模式除⽤户模式外,其它模式均为特权模式(Privileged Modes)。

ARM 内部寄存器和⼀些⽚内外设在硬件设计上只允许(或者可选为只允许)特权模式下访问。

此外,特权模式可以⾃由的切换处理器模式,⽽⽤户模式不能直接切换到别的模式。

ARM处理器的工作模式

ARM处理器v4及以上版本有37个32位的寄存

其中31个为通用寄存器;6个为状态寄存器。

– 31个通用寄存器

R0~R15; R13_svc、R14_svc; R13_abt、R14_abt; R13_und、R14_und; R13_irq、R14_irq; R8_fiq-R14_fiq

– 6 个状态寄存器

①系统上电复位后进入管理模式,运行系统初始化 程序,如中断允许/禁止,主时钟设置,SDRAM配置, 各个功能模块初始化等。 ②当执行软件中断指令SWI时,进入管理模式。

1.1.2 ARM处理器的工作模式(4)

• 处理器模式的切换方式:

– 软件控制进行切换。 – 通过外部中断和异常进行切换

处理器启动时的模式转换图

– T控制(标志)位——反映处理器的运行状态

• T=1时,程序运行于Thumb状态 • T=0时,程序运行于ARM状态

– M控制位——决定了处理器的运行模式

• 当发生异常时这些位被改变。 • 如果处理器运行在特权模式,这些位也可以由 程序修改。

1.2.3 ARM9的状态寄存器(4)

3、保留位

CPSR中的其余位为保留位,当改变CPSR中 的条件码标志位或者控制位时,保留位不要改变, 在程序中也不要使用保留位来存储数据。保留位将 用于ARM版本的扩展。

•

从Thumb状态切换到ARM状态

有两种情况ARM处理器自动切换到Thumb状态。 (1)执行BX指令,当操作数寄存器的位[0]为0时,则 微处理器从Thumb状态切换到ARM状态。 (2)当处理器在Thumb状态时发生异常(如IRQ、FIQ、 Undef等),则处理器从Thumb状态自动切换到ARM状态 进行异常处理

1.1 ARM处理器的工作状态和模式(3)

《ARM嵌入式系统结构与编程》习题答案

1章绪论1.国内嵌入式系统行业对“嵌入式系统”的定义是什么?如何理解?答:见教材1.1节。

2.嵌入式系统是从何时产生的,简述其发展历程。

答:见教材1.1节。

3.当前最常见的源码开放的嵌入式操作系统有哪些,请举出两例,并分析其特点。

答:见教材1.2.1节的嵌入式Linux和嵌入式实时操作内核UC /OS-I 。

4.举例说明嵌入式设备在工控设备中的应用。

答:见教材1.3节的“工业控制领域”。

5.未来嵌入式技术的发展趋势有哪些?答:见教材1.4节的嵌入式技术的发展趋势。

2章ARM技术与ARM体系结构1.简述ARM处理器内核调试结构原理。

答:对教材1.2节的图2-1进行描述。

2.分析ARM7TDMI-S各字母所代表的含义。

答:参考教材2.1.2 ARM核版本命名规则说明。

3.ARM处理器的工作模式有哪几种,其中哪些为特权模式,哪些为异常模式,并指出处理器在什么情况下进入相应的模式。

ARM处理器共有7种工作模式:用户模式:非特权模式,也就是正常程序执行的模式,大部分任务在这种模式下执行。

在用户模式下,如果没异常发生,不允许应用程序自行改变处理器的工作模式,如果有异常发生,处理器会自动切换工作模式FIQ模式:也称为快速中断模式,支持高速数据传输和通道处理,当一个高优(fast)中断产生时将会进入这种模式。

IRQ模式:也称为普通中断模式,:当一个低优先级中断产生时将会进入这种模式。

在这模式下按中断的处理器方式又分为向量中断和非向量中断两种。

通常的中断处理都在IRQ 模式下进行。

SVC模式:称之为管理模式,它是一种操作系统保护模式。

当复位或软中断指令执行时处理器将进入这种模式。

中止模式:当存取异常时将会进入这种模式,用来处理存储器故障、实现虚拟存储或存储保护。

未定义指令异常模式:当执行未定义指令时会进入这种模式,主要是用来处理未定义的指令陷阱,支持硬件协处理器的软件仿真,因为未定义指令多发生在对协处理器的操作上。

嵌入式系统课后习题部分答案1

第一章1-1.简述嵌入式系统的定义。

嵌入式系统是以应用为中心,以计算机技术为基础,并且软硬件可裁剪,适用于应用系统对功能、可靠性、成本、体积、功耗有严格要求的专用计算机系统。

1-2.简述嵌入式系统的组成。

从体系结构上看,嵌入式系统主要由嵌入式处理器、支撑硬件和嵌入式软件组成。

其中嵌入式处理器通常是单片机或微控制器,支撑硬件主要包括存储介质、通信部件和显示部件等,嵌入式软件则包括支撑硬件的驱动程序、操作系统、支撑软件及应用中间件等。

嵌入式系统的组成部分是嵌入式系统硬件平台、嵌入式操作系统和嵌入式系统应用。

嵌入式系统硬件平台为各种嵌入式器件、设备(如ARM 、PowerPC、Xscale、MIPS等);嵌入式操作系统是指在嵌入式Linux、uCLinux、WinCE等。

1-3.ARM7处理器使用的是(ARMv4)指令集。

ARM7内核采用冯·诺依曼体系结构,数据和指令使用同一条总线。

内核有一条3级流水线,执行ARMv4指令集。

1.4.Cortex-M3主要应用在哪些方向?主要用在平衡ARM的产品的性能和功耗,提高ARM的性能,降低其功耗1.5.简述StrongARM处理器和ARM处理器的关系StrongARM是第一个包含5级流水线的高性能ARM处理器,但它不支持Thumb指令集1-6.ARM9采用的是(5)级流水线设计。

存储器系统根据哈佛体系结构(程序和数据空间独立的体系结构)重新设计,区分数据总线和指令总线。

1.7.简述ARM9和ARM9E的不同点硬件处理器不一样指令集不一样1.8.ARM11采用的是什么架构的指令ARMv6嵌入式操作系统的特点(1)体积小(2)实时性(3)特殊的开发调试环境SecureCore处理器系列的特点(1)支持ARM指令集和Thumb指令集,以提高代码密度和系统性能(2)采用软内核技术一提供最大限度的灵活性,可以防止外部对其进行扫描探测(3)提供了安全特性,可以抵制攻击(4)提供面向智能卡和低成本的存储保护单元MPU(5)可以集成用户自己的安全特性和其它的协处理器第二章2-1.简述ARM可以工作在几种模式。

第三节ARM体系结构

一般的通用寄存器

寄存器类别 寄存器在汇编中的名称

用户

系统

R0(a1)

R1(a2)

R2(a3)其中R0~R7为

R3(a4)

未R分4(v1) 组的寄存器,也

通用寄存器 和程序计数

器

就R是5(v2) 说对于任何处理 R6(v3)

器R模7(v4) 式,这些寄存器 都对应于相同的32位 R8(v5)

管理 (svc) 操作系下统保访护问代码用户模系统式复位的和寄软件存中器断响就应比时进较入方此模式

中止 (abt) 未定义 (und)

用或于存支储便 可持器虚 保,以拟护而使内存且用和操这/ 作个在A系模RM统式7TD的访MI一问没有些一大用特 些处权 受任 控务 的 支软持件硬仿资件真协源处。理器的 未定义指令异常响应时进入此模式

各模式下实际访问的寄存器

用户

系统

管理

中止

未定义

RR00

在汇编语言中寄存

R1

器R0~R13为保存数据

R2

或地址值的通用寄存器。

R3

它们是完全通用的寄存器, R4

不会被体系结构作为特殊

R5

用途,并且可用于任何使

R6

用通用寄存器的指令。

R7

R8

R9

R10

R11

R12

R13

RR1133__ssvc

R13_abt

SSPPSSRR__fifqiq

ARM状态各模式下可以访问的寄存器

寄存器类别 寄存器在汇编中的名称

通用寄存器和 程序计数器

状态寄存器

R0 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13(SP) R14(LR) R15(PC) CPSR SPSR

常熟理工嵌入式期末考试复习选择题部分

1.以下()不是ARM的7种运行模式之一。

A. 中断模式B. 挂起模式C. 无定义模式D. 快中断模式2 μCOS-II操作系统中,需要()个任务就绪状态列表。

A. 64B. 1C. 63D. 83 在指令系统的各种寻址方式中,获取操作数最快的方式是()。

A. 直接寻址B. 寄存器寻址C. 立即寻址D. 间接寻址4 RS-232C串行通信总线的电气特性要求总线信号采用()。

A. 负逻辑B. 低电平C. 正逻辑D. 高电平5 下面哪点不是嵌入式操作系统的特点。

()A. 高实时性B. 功能强大C. 内核精简D. 专用性强6 ARM 处理器中,()异常可以用来响应中断。

A. SVCB. SWIC. FIQD. RESET7 Linux是UNIX类操作系统的一种,它对UNIX有很好的兼容性,下面不是它特点的是()。

A. 多硬件平台支持,多处理器支持。

B. 交互操作性强C. 实时性强D. 内存保护模式,共享库支持,TCP/IP、SLIP和PPP支持。

8 ARM工作状态下,每取出一条指令后程序计数器PC的值应该()。

A. 自动加4B. 自动加1C. 自动置1D. 自动清09 在ARM处理器中,()寄存器包括全局的中断禁止位,控制中断禁止位就可以打开或者关闭中断。

A. SPSRB. CPSRC. PCD. LR10 ARM处理器比较无符号数大小时是根据()标志位来判断的。

A. C和VB. C和ZC. Z和VD. C和N11 下面()特性不符合嵌入式操作系统特点。

A. 实时性B. 易移植C. 微型化D. 不可定制12 用来描述一个任务,使得任务得以独立运行的数据结构是()。

A. 以上皆不是B. TLBC. BSPD. TCB13 在嵌入式ARM 处理器中,下面哪种异常优先级最高。

()A. ResetB. FIQC. 数据中止D. IRQ14 下面哪种嵌入式操作系统很少用于手机终端设备上。

()A. LinuxB. μCOSC. SymbianD. WinCE15 嵌入式的软件分为()和应用软件两个主要部分。

CPU的工作模式

Intel CPU 和ARM CPU 的运行模式摘要: 本文介绍了Intel CPU的三种运行模式:实模式、保护模式,虚拟实模式,同时还介绍了ARM处理器的工作模式:用户模式和特权模式,并且分析比较了两种CPU的这些运行模式的作用及适用场合,以便对这些运行模式有更深入的了解。

CPU作为计算机和各种电子设备的大脑,对计算机和电子设备起着至关重要的作用,它主要用来解释指令和处理数据,是计算机和电子设备能够实现各种各样的功能的基础。

CPU运行模式指的是各种工作环境,以及对芯片的指令和能力的影响。

CPU运行模式控制处理器如何查看和管理系统存储器以及使用它的任务。

Intel的CPU占领了大部分的PC市场,而ARM处理器则大量存在于手机和各种嵌入式设备中。

对这两种CPU的运行模式进行分析能让我们对CPU 的运行模式更加深入的理解。

绝大部分PC的CPU都是Intel公司的CPU,Intel的CPU经过多年的发展,已经当初的一种运行模式发展成了现在的三种运行模式,分别是:实模式、保护模式,虚拟实模式。

下面对这三种模式进行详细介绍。

实模式Intel的8086到80186处理器都只有一种运行模式,这就是实模式。

在这个模式下,CPU用20根地址线进行内存寻址,所以在这个模式下CPU只能访问从00000h--FFFFFh的地址范围的内存,即1M大小的内存。

同时使用16根数据线,使用l6位内部寄存器运行16位指令。

由于使用的是16根数据线,为了能够支持使用20位的地址来访问1M的内存,于是就对内存的使用引入了分段机制。

为了支持分段机制,CPU设臵了四个16位的段寄存器:CS、DS、SS、ES,分别是代码段,数据段,堆栈段和其他段,对应于地址总线中的高16位。

寻址时,将段寄存器中的值向左移四位再加上段内偏移量就得到了物理地址。

这样就实现了16位内存地址到20位物理地址的转换,这种方式叫做“映射”。

由于其偏移量只能用16位来表示,所以其支持的段的大小只有64K字节。

ARM9常识知识的笔记

ARM处理器特点:1支持Thumb和ARM双指令集,能很好地兼容8位/16位器件。

Thumb指令集比通常的8位和16位CISC/RISC处理器具有更好代码密度。

2指令采用的3级、5级流水技术。

4支持大端格式和小端格式两种方法存储数据。

5支持字节、半字、和字这3种数据类型。

6 体积小,成本低,性能高ARM工作状态:1、32位ARM状态、2、16位Thumb状态ARM处理器七种运行模式:用户、快中断、中断、管理、(指令预取)中止、系统和未定义(除用户模式外,其余6种模式称为非用户模式,或特权模式;除去用户模式和系统模式外,其余5种模式又称为异常模式)。

R13为堆栈指针SP,R14为链接寄存器LR,R15为程序计数器PC,R16状态寄存器CPSR ARM(嵌入式)系统(从模块结构上看)三大组成部分:硬件、软件、开发平台。

嵌入式系统概念:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

嵌入式开发环境主要组件:●宿主机●目标机●基于JTAG的ICD仿真器、或调试监控软件、或在线仿真器ICE●运行于宿主机的交叉编译器和链接器、以及开发工具链或软件开发环境●嵌入式操作系统常见的嵌入式系统:移动电话、数码照相机、MP4、数字电视的机顶盒、微波炉、汽车内部的喷油控制系统、防抱死制动系统。

4种电源管理模式:1正常模式:正常运行模式2慢速模式:不加PLL的低时钟频率模式3空闲模式:只停止CPU的时钟4掉电模式:切断所有外设和内核的电源RAM=SRAM+DRAM边界对齐方式:字对齐、半字对齐、字节对齐名词解释:ROM:Read Only Memory是只能读出事先所存的数据的固态半导体存储器,其特性是一旦存储资料就无法改变或删除。

ARM:Advanced RISC Machines先进精简指令集。

ARM公司1991年成立于英国剑桥,是专门从事基于RISC技术芯片设计开发公司,主要出售芯片设计技术的授权。

ARM期末考点

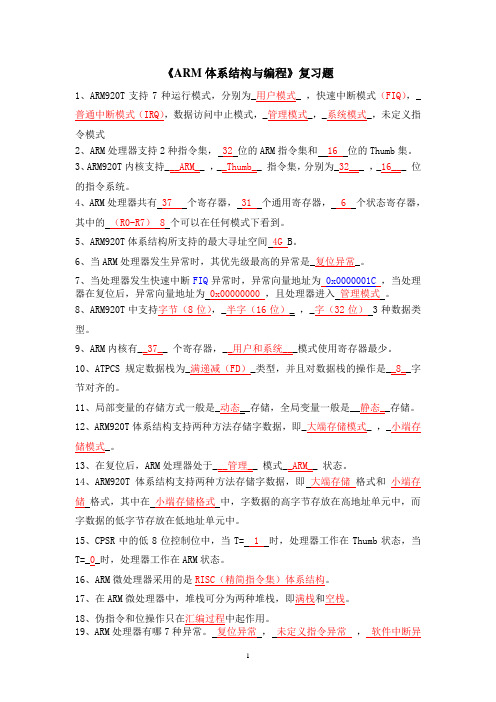

《ARM体系结构与编程》复习题1、ARM920T支持7种运行模式,分别为_用户模式_ ,快速中断模式(FIQ),_普通中断模式(IRQ),数据访问中止模式,_管理模式_,_系统模式_,未定义指令模式2、ARM处理器支持2种指令集,32位的ARM指令集和16 位的Thumb集。

3、ARM920T内核支持___ARM__ ,__Thumb__ 指令集,分别为_32___ ,_16___ 位的指令系统。

4、ARM处理器共有37 个寄存器,31 个通用寄存器, 6 个状态寄存器,其中的(R0-R7) 8个可以在任何模式下看到。

5、ARM920T体系结构所支持的最大寻址空间4G B。

6、当ARM处理器发生异常时,其优先级最高的异常是_复位异常_。

7、当处理器发生快速中断FIQ异常时,异常向量地址为0x0000001C,当处理器在复位后,异常向量地址为0x00000000 ,且处理器进入管理模式。

8、ARM920T中支持字节(8位),_半字(16位)_ ,_字(32位) 3种数据类型。

9、ARM内核有__37__ 个寄存器,__用户和系统___模式使用寄存器最少。

10、ATPCS规定数据栈为_满递减(FD)_类型,并且对数据栈的操作是__8__字节对齐的。

11、局部变量的存储方式一般是_动态__存储,全局变量一般是__静态__存储。

12、ARM920T体系结构支持两种方法存储字数据,即_大端存储模式_ ,_小端存储模式_。

13、在复位后,ARM处理器处于___管理__ 模式__ARM__ 状态。

14、ARM920T体系结构支持两种方法存储字数据,即大端存储格式和小端存储格式,其中在小端存储格式中,字数据的高字节存放在高地址单元中,而字数据的低字节存放在低地址单元中。

15、CPSR中的低8位控制位中,当T= 1 时,处理器工作在Thumb状态,当T=_0_时,处理器工作在ARM状态。

16、ARM微处理器采用的是RISC(精简指令集)体系结构。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

s3c2440中断体系结构:如何用中断?1.中断发生:保存别人的状态如何中断可以事先设置,对程序初始化,使能中断。

中断发生后,进入中断模式2.中断处理分辨中断源进行不同的处理清理工作3.恢复别人的状态过程:外界信号上升沿、下降沿,高电平、低电平都可以设置成信号引脚设置,再进入状态寄存器。

状态寄存器连接屏蔽寄存器进入第二个状态寄存器,储存各种中断,可以储存多个中断进入优先级寄存器,判断中断运行顺序再进入屏蔽使能寄存器和模式寄存器进入优先级寄存器进入cpu处理cpu的处理:进入入口地址 b handleIRQ计算返回地址,被中断处地址保存现场,即各寄存器状态调用处理函数函数运行完后恢复现场函数的处理:分辨终端处理中断清除数据,即清除中断1.中断寄存器arm的七种模式r 用户模式r0-r152.fiq 快中断模式r0-r7专用寄存器r8-r15,3.svc 管理模式专用寄存器r13-r14,4.abt 数据访问终止模式5.sys 系统模式6.und 未定义指令终止模式7.irq 中断模式几种模式的区别:嵌入式的中断:a.不同的寄存器b.不同的权限c.触发条件不一样何时使用几种模式:usr 用户模式:arm处理器正常的程序执行状态fiq 快中断模式:高速数据传输和通道处理svc 管理模式:操作系统使用的保护模式abt 数据访问终止模式:数据或者指令终止时进入,用于虚拟存储或者存储保护sys 系统模式:运行具有特权的操作系统任务und 未定义指令终止模式:未定义的指令执行时进入该模式,用于支持硬件处理器的软件仿真.irq 中断模式:用于通用的中断处理后六种是特权模式,用于处理中断、异常和特殊权限处理用户模式是最常见的模式2.中断中的异常中断是一种异常。

当发生中断时,cpu进入中断模式cpu进入异常入口,异常入口是硬件规定的一个地址运行模式ARM920T 支持7 种运行模式:●用户(usr)):正常ARM 程序执行状态●快中断(fiq)):为支持数据传输或通道处理设计●中断(irq)):用于一般用途的中断处理●管理(svc)):操作系统保护模式●中止(abt ): 数据或指令预取中止后进入●系统(sys)):操作系统的特权用户模式●未定义(und)):执行了一个未定义指令时进入模式的改变可由软件控制,或者由外部中断或进入异常引起。

大部分应用程序都将在用户模式执行。

被称为特权模式的非用户模式,都将进入到中断服务或异常中去,或者访问受保护的资源。

内部寄存器ARM920T 总共有37 个寄存器,其中31 通用32 位寄存器和6 个状态寄存器,但不能在同一时刻对所有的寄存器可见。

处理器状态和运行模式决定了哪些寄存器对程序员可见。

ARM状态时内部寄存器集在ARM 状态,16 个通用寄存器和一个状态寄存器在任意时刻都可见。

在特权(非用户)模式下,将切换到指定模式的分组(banked)寄存器。

图2-3 显示了哪些寄存器在各模式下是可见的:分组寄存器被标记了阴影三角形。

ARM 状态时寄存器被设为包含16 个直接可以访问的寄存器:R0 到R15。

除了R15,其他全部寄存器都为通用寄存器,如可能用于保存数据或地址值。

除此之外,还有第17 个寄存器用于存储状态信息。

FIQ 模式包含7 个分组寄存器,分别映射到R8-14(R8_fiq-R14_fiq)。

在ARM 状态,有很多不需要保存寄存器的FIQ 处理程序。

用户,IRQ,管理中止和未定义模式都包含两个分组寄存器映射到R13 和R14,允许这些模式都都包含私有堆栈指针和链接寄存器。

Thumb 状态时内部寄存器集Thumb 状态时的寄存器集为ARM 状态时的寄存器的分配的一个子集。

程序员能够直接访问8 个通用寄存器R0 至R7,还有程序计数器(PC),一个堆栈指针寄存器(SP),一个链接寄存器(LR)和CPSR。

各自特权模式还分别有分组堆栈指针,链接寄存器和进程保存状态寄存器(SPSR)。

如图2-4 所示。

Thumb 状态访问高寄存器(Hi-Registers )在Thumb 状态,寄存器R8-R15(“Hi registers”)不是标准的寄存器集的一部分。

然而,汇编语言程序员可以受限的对它们的进行访问,可以将它们用于快速暂存。

使用MOV 指令的特殊变量可以将一个值从R0-R7(“Lo register”)范围内的寄存器传送到高寄存器或从高寄存器到第低寄存器。

使用CMP 和ADD 指令也可以对高寄存器的值与寄存器的值进行比较以或相加。

更多内容请参考表3-34。

程序状态寄存器ARM920T 包含了一个当前程序状态寄存器(Current Program Status Register-CPSR),还有5 个用于异常程序处理的程序状态保存寄存器(Saved Program Status Registers-SPSR)。

这些寄存器的功能为:●保存最近已处理的ALU 操作的信息●控制中断的使能与禁止●设置处理器的运行模式图2-6 显示了各位的编排状态代码标志位N,Z,C 和V 位为状态代码标志位。

算术或逻辑操作结果可能会改变这些位,并检验以决定是否应该执行某条指令。

在ARM 状态,所有指令都可能为条件执行:详情见表3-2。

在Thumb 状态,只有分支指令才能条件执行:详情见表3-46。

控制位PSR (包含I,F,T 和M[4:0])的末端8 位,统称为控制位。

当发生异常时将会改变这些位。

如果处理器运行在特权模式,它们也可由软件控制。

异常:程序暂时停止当正常程序流程被暂时停止发生异常,例如响应一个来自外设的中断。

在处理异常前,必须保护当前的处理器状态,以便在完成处理程序后能恢复到原来的程序。

如果同时发生好几个异常,将会按照固定的顺序来分配,见P2-13 的异常优先级。

进入异常行为当处理一个异常时,ARM920T 将会进行以下活动:1. 相应链接寄存器保存下条指令的地址。

如果在ARM 状态进入异常,下条指令的地址将会复制到链接寄存器(当前PC+4 或PC+8,由异常决定。

详情见表2-2)中。

如果在Thumb 状态进入异常,写入链接寄存器的值则为当前PC 偏移一个值,这样异常返回后程序能从正确的位置恢复。

这意味着异常处理不需要确定异常是从什么状态进入的。

例如,在SWI 的情况,无论是在ARM 状态还是Thumb 状态执行SWI,MOVS PC,R14_svc 语句都将返回到下一条指令。

2. 复制CPSR 的内容到相应SPSR 中。

3. 根据异常类型强制将CPSR 模式位设为某一个值。

4. 强制PC 从相关异常向量处取下条指令。

通常也会置位中断禁止标志位,以防止不同的难处理的异常嵌套。

如果一个异常发生时处理器处于Thumb 状态,当装载异常向量地址到PC 时会自动切换到ARM 状态。

离开异常行为:当异常结束,异常处理程序将会:1. 将链接寄存器适当减去一个偏移量并放入到PC 中。

(偏移量由异常类型决定)2. 复制SPSR 的内容返回给CPSR 中。

3. 如果在异常进入时置位了中断禁止标志位异常,清除中断禁止标志位。

注意:不需要在异常结束时切换回Thumb 状态,因为在异常前会立刻保存CPSR 中T 位的值到SPSR 中,并在退出异常时从SPSR 恢复到CPSR 中。

异常进入/ 退出总结表2-2 总结了进入异常时保存在相关R14 中的PC 值和被推荐的退出异常的指令。

注释:1. 此处PC 为含预取中止的BL/SWI/未定义指令取指令的地址。

2. 此处PC 为由于FIQ 或IRQ 抢先而未执行的指令地址。

3. 此处PC 为发生了数据中止的Load 或Store 指令的地址。

4. 当复位时保存在R14_svc 的值将是不可预测的。

快中断FIQFIQ(快中断请求)异常是为支持数据传输或通道处理而设计的,在ARM 状态拥有足够的私有寄存器来消除对寄存器保存的需求(这样最小化了对上下文的切换的开销)。

将nFIQ 输入端拉低可以实现外部产生FIQ。

由ISYNC 输入信号端的状态决定是同步还是异步传输。

当ISYNC 为低电平,认为nFIQ 和nIRQ 为异步,中断前会引起同步周期延迟并影响处理器流程。

无论是从ARM 还是Thumb 状态进入的异常,FIQ 处理时执行SUBS PC,R14_fiq,#4 时,都应该避免中断。

如果设置CPSR 的F 标志位,FIQ 将会被禁止(但主义这不可能在用户模式中发生)。

如果F 标志位为零,ARM920T将在每条指令末检测FIQ 同步发生器的输出是否为低电平。

中断IRQIRQ(中断请求)异常是一个由nIRQ 输入端的低电平产生的一个普通中断。

IRQ 的优先级低于FIQ,当进入了相关的FIQ,会屏蔽IRQ。

除非是在特权(非用户)模式,其他任何时刻都禁止设置CPSR 内的I 位。

无论是从ARM 还是Thumb 状态进入的异常,IRQ 处理时执行SUBS PC,R14_fiq,#4 时,都应该避免中断。

中止中止表示不能完成当前对存储器的访问。

通过外部ABORT 输入端指示的。

ARM920T 在存储器访问周期期间检测中止异常。

有两种类型的中止:●预取中止(Prefetch Abort):发生在指令预取期间●数据中止(Date Abort):发生在数据访问期间如果发生预取中止,将屏蔽预取指并为无效,但并不会立刻带来异常,直到指令到达流水线的执行阶段才发生。

若未执行该指令,将不会发生中止,因为流水线发生了分支。

如果发生数据中止,由指令类型决定其行为:●单一的数据转移指令(LDR,STR)回写到被修改的基址寄存器:中止处理程序必须意识到这点。

●交换指令(SWP)执行失败,就如同没有被执行。

●块数据转移指令(LDM,STM)完成。

如果设置了回写,基址寄存器将被更新。

如果指令会覆盖基址寄存器数据(转移列表中包含基址),覆盖将会被阻止。

表明了中止后所有寄存器的覆盖都会被阻止,特别是R15(通常是最后转移的寄存器)在一个被中止的LDM 指令会被阻止覆盖。

中止机制使得分页虚拟存储器系统可以被实现。

在这样一个系统中允许处理器产生任意地址。

当无法获取某一地址上的数据时,内存管理单元(Memory Management Unit-MMU)将表明产生一个中止。

中止处理程序必须紧接着找出中止原因,使得被请求的数据可用并重试被中止的指令。

应用程序并不需要了解可以使用的内存总量,也不需要关心中止对其状态以任何方式被影响。

当确定中止原因后,处理程序应该不顾状态(ARM 或Thumb)执行下列语句:SUBS PC,R14_abt,#4 ; 预取中止SUBS PC,R14_abt,#8 ; 数据中止这将恢复PC 和CPSR,并重试被中止的指令。

软件中断SWI软件中断指令(Software Interrupt Instruction-SWI)用于进入管理模式,通常请求一个特定的管理功能。