第3章 31ARM处理器工作模式及寄存器介绍

ARM寄存器及功能介绍R0-R15寄存器

ARM寄存器及功能介绍R0-R15寄存器1、ARM 寄存器组介绍ARM 处理器⼀般共有 37 个寄存器,其中包括:(1) 31 个通⽤寄存器,包括 PC(程序计数器)在内,都是 32 位的寄存器。

(2) 6 个状态寄存器,都是 32 位的寄存器。

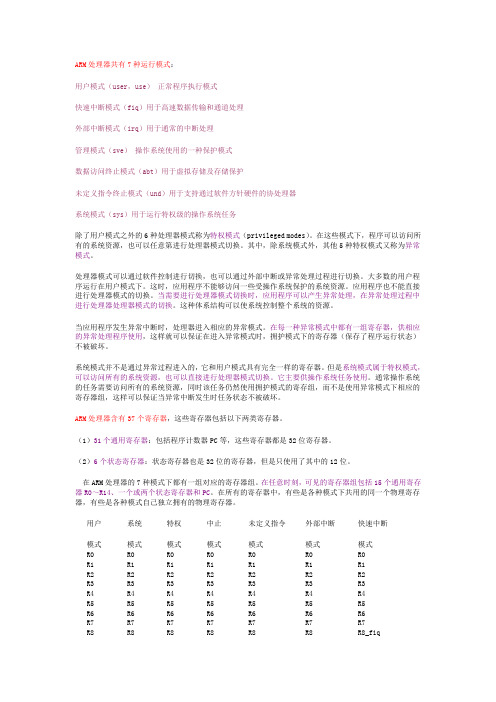

ARM 处理器共有 7 种不同的处理器模式:⽤户模式(User),快速中断模式(FIQ),普通中断模式(IRQ),管理模式(Svc),数据访问中⽌模式(Abort),未定义指令中⽌模式(Und),系统模式(Sys),在每⼀种处理器模式中有⼀组相应的寄存器。

在任意⼀种处理器模式下,可见的寄存器包括 15 个通⽤寄存器(R0~R14)、⼀个或者⼆个状态寄存器以及程序计数器(PC)。

在所有的寄存器中,有些是各模式共⽤同⼀个物理寄存器,有些寄存器是各个模式⾃⼰拥有独⽴的物理寄存器其中 r0~r3 主要⽤于⼦程序间传递参数, r4~r11 主要⽤于保存局部变量,但在 Thumb 程序中,通常只能使⽤ r4~r7 来保存局部变量;r12 ⽤作⼦程序间scratch 寄存器,即 ip 寄存器; r13 通常⽤做栈指针,即 sp; r14 寄存器⼜被称为连接寄存器(lr),⽤于保存⼦程序以及中断的返回地址; r15 ⽤作程序计数器(pc),由于 ARM 采⽤了流⽔线机制,当正确读取了 PC 的值后,该值为当前指令地址加8 个字节,即 PC 指向当前指令的下两条指令地址。

CPSR和SPSR都是程序状态寄存器,其中SPSR是⽤来保存中断前的CPSR中的值,以便在中断返回之后恢复处理器程序状态。

2.CPSR寄存器详解所有处理器模式下都可访问当前程序状态寄存器CPSR。

CPSR中包含条件码标志、中断禁⽌位、当前处理器模式以及其他状态和控制信息。

在每种异常模式下都有⼀个对⽤的程序状态寄存器SPSR。

当异常出现时,SPSR⽤于保存CPSR的状态,以便异常返回后恢复异常发⽣时的⼯作状态。

arm工作模式

arm工作模式ARM工作模式。

ARM处理器是一种广泛应用于嵌入式系统和移动设备中的处理器架构。

它以其低功耗、高性能和灵活性而闻名,是许多设备的首选处理器。

在ARM处理器中,工作模式是其核心概念之一,不同的工作模式可以实现不同的功能和性能。

本文将介绍ARM处理器的工作模式及其特点。

1. 用户模式。

在ARM处理器中,用户模式是最基本的工作模式。

在用户模式下,处理器可以执行大多数指令,但对于一些特权指令和资源的访问会受到限制。

用户模式通常用于运行普通应用程序,保护系统的安全性和稳定性。

2. 特权模式。

特权模式是ARM处理器的特殊工作模式,它具有更高的权限和特权级别。

在特权模式下,处理器可以执行所有指令并访问系统的所有资源,包括控制寄存器和中断控制器等。

特权模式通常用于操作系统内核和驱动程序,以及一些需要直接访问硬件资源的任务。

3. 直接存储器访问(DMA)模式。

DMA模式是用于实现直接存储器访问的工作模式。

在DMA模式下,处理器可以将数据直接传输到存储器中,而无需通过CPU的中间传输。

这种模式可以显著提高数据传输的效率,特别适用于需要大量数据传输的场景,如音频和视频处理。

4. 睡眠模式。

睡眠模式是用于节能的工作模式,在这种模式下,处理器会暂停大部分运行,并且关闭一些不必要的电路和部件,以降低功耗。

当系统处于空闲状态或需要长时间等待时,可以进入睡眠模式以节省能源。

5. 睡眠模式。

睡眠模式是用于节能的工作模式,在这种模式下,处理器会暂停大部分运行,并且关闭一些不必要的电路和部件,以降低功耗。

当系统处于空闲状态或需要长时间等待时,可以进入睡眠模式以节省能源。

6. 睡眠模式。

睡眠模式是用于节能的工作模式,在这种模式下,处理器会暂停大部分运行,并且关闭一些不必要的电路和部件,以降低功耗。

当系统处于空闲状态或需要长时间等待时,可以进入睡眠模式以节省能源。

7. 睡眠模式。

睡眠模式是用于节能的工作模式,在这种模式下,处理器会暂停大部分运行,并且关闭一些不必要的电路和部件,以降低功耗。

关于ARM寄存器组及工作模式知识

关于ARM寄存器组及⼯作模式知识关于ARM寄存器组及⼯作模式知识(周⽅辉)2012/8/10 编改记录⽬录1 参考⽂献 (2)1.1 内部参考⽂献 (2)1.2 外部参考⽂献 (2)2 名词解释 (2)3 ARM核⼯作模式 (2)3.1 程序状态寄存器 (3)3.2 寄存器分组 (4)3.3 何为特权(异常)模式 (6)3.4 各种模式⼯作机制 (7)3.5 各种模式⼯作返回⽤户模式机制 (9)4 ARM核⼯作模式初始化参考代码 (11)1参考⽂献1.1内部参考⽂献内部参考⽂献指的是周⽅辉⾃⽣的百度博⽂中的⽂件。

⽆内部参考⽂献。

1.2外部参考⽂献外部参考⽂献指的是相对于上述内部参考⽂献以外的⽂件。

《ARMv8_ISA_PRD03-GENC-010197-24-0.pdf》《cortex_a8_r3p2_trm.pdf》《CortexA8TechRefManul.pdf》2名词解释CPSR:当前程序状态寄存器,其数值反映出当前程序运⾏的⼀些状态指⽰。

SPSR:保存程序状态寄存器,在程序调⽤等情况下,需要保存⼀下当前程序状态寄存器的值(SPSR<=CPSR),便于⽇后回复。

SP:堆栈指针寄存器,其值⽤于执⾏当前堆栈栈顶(或栈底)位置。

PC:程序指针寄存器,其值⽤于指向要执⾏的程序代码地址。

LR:连接返回寄存器,保存要返回的地址,PC<=LR。

3ARM核⼯作模式常规CPU⼯作核⼼模块都是由:寄存器组和ALU两⼤模块组成,ALU完成数据的加⼯处理,寄存器⽤来保存数据,这些数据是直接参与ALU运算。

ARM的处理器也不例外。

ARM处理器的寄存器分成许多组,不同的组完成不同环境下的⼯作,不过它们都共⽤⼀套ALU数据处理模块。

ARM寄存器⼀般⽤了37个,Cortex A8的ARM核的寄存器多⼤40个。

我们学习ARM⼯作模式需要了解和解决下⾯问题:ARM寄存器为什么要分组?⼜是如何分组?各组与CPU⼯作模式是如何关联?各个组或⼯作模式是如何切换的?我们在学习ARM寄存器分组⼯作模式之前,先来看⼀下很特殊的⼀个寄存器——PSR 程序状态寄存器。

ARM处理器的工作模式

支持硬件协处理器的软件仿真 未定义指令异常响应时进入此模式

(3)用户和系统模式

6

处理器模式 用用户户 (u(surs) r) 系统系统 (sy(sy) s)

快中断 (fiq) 中断 (irq) 管理 (svc)

中止 (abt)

说明

备注

正常程序工作这模两式 种模式都不不能能由直接异切常换到进其入它模,式 用于而支持且操系它作系统们统模使的特式用权是完任务特全等权相与 到模同用 其式的户 它模 模,寄式 式不存类 等似 特受器, 权用组但具。有可以直接切换 支持户高速模数式据传的输限及通制道。处理操作F系IQ异统常在响应该时模进入式此模式

操作系访统问保护。代此码 外,特权模系式统复可位以和软自件由中断的响应时进入此模式

用保于护支切直持换接虚拟处切内理换存和器到/或模别存储式的器,模而式在用。AR户M7模TDM式I没不有能大用处

支持硬件协处理器的软件仿真 未定义指令异常响应时进入此模式

5

(2)异常模式

处理器模式 用户 (usr) 系统 (sys)

7

2.ARM微处理器的处理器改变方式

• ARM微处理器的运行模式可以通过软件改变(特权模式),也可以通过外部中断或异常 处理改变。

• 大多数的应用程序运行在用户模式下,当处理器运行在用户模式下时,某些被保护的 系统资源是不能被访问的。也不能改变模式。除非异常发生。

• 特权模式可以自由地访问系统资源和改变模式。

中止 (abt)

用于支持虚拟内存和/或存储器保护 在ARM7TDMI没有大用处

未定义 (und) 支持硬件协处理器的软件仿真

未定义指令异常响应时进入此模式

4

(1)特权模式

处理器模式 用户 (usr) 系系统统 (sy(ssy)s)

第3章_ARM指令系统

23

3.2 ARM指令的 寻址方式

堆栈寻址和多寄存器寻址有很多相似之处,可以说 堆栈寻址是多寄存器寻址的特例,堆栈操作的指令

也有一一对应的多寄存器访问指令,如下表所示。

递增 满 先增 增值 后增 先减 减值 后减 LDMDA LDMFA STMIB STMFA STMIA LDMIA 空 满 递减 空 LDMIB LDMED

、后索引偏移和自动索引之分。

零偏移----实际上就是寄存器间接寻址 前索引偏移: LDR R2, [R3, #0X12] ; [(R3)+ #0X12]送R2,R3值不变 后索引偏移: STR R2, [R3], #0X12; R2送[R3],R3+0X12送R3 自动索引: LDR R2, [R3,#0X12]!; [(R3)+ #0X12]送R2,R3+0X12送R3

存储器 R2 0X00009000 0X00009000

0X20

R1

0X20

13

3.2 ARM指令的寻址方式

(6)基址变址寻址

基址变址寻址是指操作数的有效地址是由寄存器的内容加

上指令中给出的变址来确定的;

操作数所在存储单元的基地址由寄存器给出,这个寄存器 就叫做基址寄存器。 变址既可以以立即数形式给出,也可以由寄存器来提供。

4

3.2 ARM指令的寻址方式

所谓寻址方式就是人们根据操作数所在位置、数据 类型及其数据结构的不同,人为规定的根据指令中

给出的信息找出操作数有效地址的方式。

根据操作数的种类不同,ARM寻址方式可以分为

数据操作数寻址方式和地址操作数寻址方式两大类

,其中,数据操作数又有立即数、寄存器操作数、 存储器操作数和I/O操作数之分。 操作的对象不同,所用的寻址方式也不同。

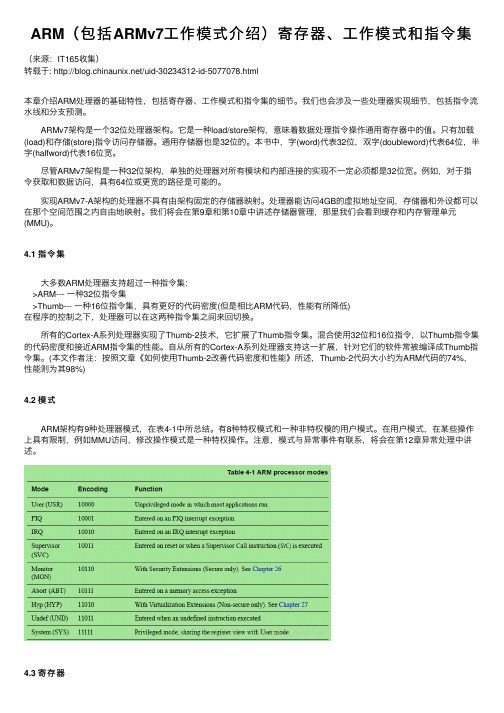

ARM(包括ARMv7工作模式介绍)寄存器、工作模式和指令集

ARM(包括ARMv7⼯作模式介绍)寄存器、⼯作模式和指令集(来源:IT165收集)转载于: /uid-30234312-id-5077078.html本章介绍ARM处理器的基础特性,包括寄存器、⼯作模式和指令集的细节。

我们也会涉及⼀些处理器实现细节,包括指令流⽔线和分⽀预测。

ARMv7架构是⼀个32位处理器架构。

它是⼀种load/store架构,意味着数据处理指令操作通⽤寄存器中的值。

只有加载(load)和存储(store)指令访问存储器。

通⽤存储器也是32位的。

本书中,字(word)代表32位,双字(doubleword)代表64位,半字(halfword)代表16位宽。

尽管ARMv7架构是⼀种32位架构,单独的处理器对所有模块和内部连接的实现不⼀定必须都是32位宽。

例如,对于指令获取和数据访问,具有64位或更宽的路径是可能的。

实现ARMv7-A架构的处理器不具有由架构固定的存储器映射。

处理器能访问4GB的虚拟地址空间,存储器和外设都可以在那个空间范围之内⾃由地映射。

我们将会在第9章和第10章中讲述存储器管理,那⾥我们会看到缓存和内存管理单元(MMU)。

4.1 指令集 ⼤多数ARM处理器⽀持超过⼀种指令集: >ARM--- ⼀种32位指令集 >Thumb--- ⼀种16位指令集,具有更好的代码密度(但是相⽐ARM代码,性能有所降低)在程序的控制之下,处理器可以在这两种指令集之间来回切换。

所有的Cortex-A系列处理器实现了Thumb-2技术,它扩展了Thumb指令集。

混合使⽤32位和16位指令,以Thumb指令集的代码密度和接近ARM指令集的性能。

⾃从所有的Cortex-A系列处理器⽀持这⼀扩展,针对它们的软件常被编译成Thumb指令集。

(本⽂作者注:按照⽂章《如何使⽤Thumb-2改善代码密度和性能》所述,Thumb-2代码⼤⼩约为ARM代码的74%,性能则为其98%)4.2 模式 ARM架构有9种处理器模式,在表4-1中所总结。

ARM中文指令--寄存器和处理器模式

ARM中文指令--寄存器和处理器模式值得拥有的资料是来自平时学习积累总结的有问题的地方肯定有的还请大家批评指正!ARM中文指令--寄存器和处理器模式ARM 处理器有二十七个寄存器其中一些是在一定条件下使用的所以一次只能使用十六个...寄存器 0 到寄存器 7 是通用寄存器并可以用做任何目的不象 80x86 处理器那样要求特定寄存器被用做栈访问或者象 6502 那样把数学计算的结果放置到一个累加器中ARM 处理器在寄存器使用上是高度灵活的寄存器 8 到 12 是通用寄存器但是在切换到 FIQ 模式的时候使用它们的影子(shadow)寄存器寄存器 13 典型的用做 OS 栈指针但可被用做一个通用寄存器这是一个操作系统问题不是一个处理器问题所以如果你不使用栈只要你以后恢复它你可以在你的代码中自由的占用(corrupt)它每个处理器模式都有这个寄存器的影子寄存器寄存器 14 专职持有返回点的地址以便于写子例程当你执行带连接的分支的时候把返回地址存储到 R14 中同样在程序第一次运行的时候把退出地址保存在 R14 中R14 的所有实例必须被保存到其他寄存器中(不是实际上有效)或一个栈中这个寄存器在各个处理器模式下都有影子寄存器一旦已经保存了连接地址这个寄存器就可以用做通用寄存器了寄存器 15 是程序计数器它除了持有指示程序当前使用的地址的二十六位数之外还持有处理器的状态为更清晰一些... 提供下列图表:User 模式 SVC 模式 IRQ 模式 FIQ 模式 APCSR0 ------- R0 ------- R0 ------- R0 a1R1 ------- R1 ------- R1 ------- R1 a2R2 ------- R2 ------- R2 ------- R2 a3R3 ------- R3 ------- R3 ------- R3 a4R4 ------- R4 ------- R4 ------- R4 v1R5 ------- R5 ------- R5 ------- R5 v2R6 ------- R6 ------- R6 ------- R6 v3R7 ------- R7 ------- R7 ------- R7 v4R8 ------- R8 ------- R8 R8_fiq v5R9 ------- R9 ------- R9 R9_fiq v6R10 ------ R10 ------ R10 R10_fiq slR11 ------ R11 ------ R11 R11_fiq fpR12 ------ R12 ------ R12 R12_fiq ipR13 R13_svc R13_irq R13_fiq spR14 R14_svc R14_irq R14_fiq lr------------- R15 / PC ------------- pc最右侧的列是 APCS 代码使用的名字关于 APCS 的详情参见这里程序计数器构造如下:位 31 30 29 28 27 26 25------------2 1 0N Z C V I F 程序计数器 S1 S0对 R15 的详细解释请参见 psr.html下面是你想知道的"模式"比如上面提及的"FIQ"模式用户模式运行应用程序的普通模式限制你的内存访问并且你不能直接读取硬件设备超级用户模式(SVC 模式)主要用于 SWI(软件中断)和 OS(操作系统)这个模式有额外的特权允许你进一步控制计算机例如你必须进入超级用户模式来读取一个插件(podule)这不能在用户模式下完成中断模式(IRQ 模式)用来处理发起中断的外设这个模式也是有特权的导致IRQ 的设备有键盘、VSync (在发生屏幕刷新的时候)、IOC 定时器、串行口、硬盘、软盘、等等...快速中断模式(FIQ 模式)用来处理发起快速中断的外设这个模式是有特权的导致 FIQ 的设备有处理数据的软盘串行端口(比如在 82C71x 机器上的 A5000) 和 EconetIRQ 和 FIQ 之间的区别是对于 FIQ 你必须尽快处理你事情并离开这个模式IRQ 可以被 FIQ 所中断但 IRQ 不能中断 FIQ为了使 FIQ 更快所以有更多的影子寄存器FIQ 不能调用 SWIFIQ 还必须禁用中断如果一个 FIQ 例程必须重新启用中断则它太慢了并应该是 IRQ 而不是 FIQPhew!关于如果变更处理器的模式的详情请参照 psr.htmlARM中文指令--32 位操作这里的许多信息取自 ARM 汇编器手册我现在没有 32 位处理器就只能信任文档了... 这个文档中表述的 UMUL 和 UMLA 只能在32bit 模式下进行是错误的如果你的处理器(比如: StrongARM)可以这么做则它可以在 32bit 或 26bit 下工作...ARM2 和 ARM3 有一个 32 位数据总线和一个 26 位地址总线在以后版本的 ARM 上数据总线和地址总二者都是完全的 32 位宽这解释了为什么一个"32 位处理器"被称为 26 位数据宽度和指令/字大小是 32 位并总是这样但地址总线只是 24 位因为 PC 总是字对齐的一个地址中的低两位总是零所以在 ARM2/ARM3 处理器上这些位持有处理器模式设置尽管实际上只使用了 24 位PC 的有效宽度仍是 26 位在老机器上这没有问题4Mb 内存是基准的一些人升级到 8Mb、和 16Mb 是理论上的限制(Some people upgraded to 8Mb, and 16Mb was the theoretical limit.) 但是 RiscPC 使用一个 26 位程序计数器是不可能的因为 RiscPC 允许安装 258Mb 内存而 26 位只允许你寻址到 %11111111111111111111111100 (或67108860 字节或 64Mb)这附带的解释了对应用任务的28Mb 大小限制;就是希望系统与老的 RISC OS API 相容尽管这个汇编器站点的某些部分覆盖了32 位模式(比如运行在SVC32 下的一个简要的例子!)但多数部分是关于 26 位模式操作的这是为了与 RISC OS 的当前可获得的版本相兼容(就是 RISC OS 2 到 RISC OS 4);我注意到部分例子不适用于 32 位RiscPC、Mico、RiscStation、A7000 等都有能力运行完全的 32 位操作系统;实际上 ARMLinux 就是这样的一个操作系统RISC OS 不是因为 RISC OS 需要至少一个时期保持与现存版本的兼容这是个古老的两分问题(dichotomy)有一个崭新的完全 32 位版本的 RISC OS 版本是美妙的但当你发现许多你的现存软件不能继续运行(so much as load)就不那么美妙了!RISC OS 不是完全的 26 位一些处理程序(handler)需要工作在32 位模式下;限制它的是金钱(就是说谁为完全转换 RISC OS 付钱;谁为用来重建它们的代码的开发工具付钱(PD 在 RISC OS 上是强壮的))和必要性(就是说很多人使用 Impression 而 CC 不再与我们同在;Impression 好象不能在更新的 RISC OS 上工作所以如果人们需要的软件将不能工作那么他们不会认为有升级的必要)为什么这如此重要? 新的 ARM 处理器将不支持 26 位操作尽管做了一些融合(ARM6、ARM7、StrongARM)但气数就要尽了你可以增加一个 26/32 位系统的复杂性或者只用 32 位而得到更简单、更小的处理器我们要么随波逐流要么被甩下... 所以我们别无选择32 位体系ARM 体系在 ARM6 系列中进行了重大变更下面我将描述 26 位和 32 位操作行为的不同之处在 ARM 6 中程序计数器被扩展到完整的 32 位结果是:PSR 从 PC 中分离到自己的寄存器 CPSR(当前的程序状态寄存器)中在改变处理器模式的时候不再与PC 一起保存PSR;现在是每个有特权的模式都有一个额外的寄存器- SPSR (保存的程序状态寄存器) - 用来持有前面模式的PSR增加了使用这些新寄存器的指令除了允许 PC 使用完全的 32 位之外还有进一步的变更就是给 PSR 增加了额外的有特权的模式这些模式用于处理未定义指令和异常终止例外:未定义指令、异常终止、和超级用户不再共享同一个模式去掉了在早期 ARM 上存在的对超级用户的那些限制在ARM6 系列(和以后的其他兼容芯片)中通过设置片上某个控制寄存器来确定这些特征的可获得性可以选择三个处理器配置中的一个:26 位程序和数据空间这个配置强制 ARM 在 26 位地址空间中进行操作在这个配置中只能获得四个26 位模式(参照处理器模式描述);不可能选择任何 32 位模式在所有当前的 ARM6 和 7 系列上复位(reset)时被设置为这个模式26 位程序空间和 32 位数据空间除了禁止地址例外来允许数据传送操作访问完整的 32 位地址空间之外与 26 位程序和地址空间配置相同32 位程序和数据空间这个配置把地址空间扩展成 32 位并介入了对处理器模型的重大变更在这个配置中你可以选择任何 26 位和 32 位处理器模式(参见下面的处理器模式)在配置成 32 位程序和数据空间的时候ARM6 和 ARM7 系列支持十个有所重叠的处理器操作模式:用户模式: 正常的程序执行状态;或 User26 模式: 一个 26 位版本FIQ模式: 设计来支持一个数据传送或通道处理;或 FIQ26 模式: 一个 26 位版本IRQ 模式: 用于通用中断处理;或 IRQ26 模式: 一个 26 位版本SVC 模式: 用于操作系统的保护模式或 SVC26模式: 一个 26 位模式异常终止模式(ABT 模式): 在一个数据或指令预取异常终止(abort)的时候进入的模式未定义模式(UND 模式): 在执行了一个未定义的指令的时候进入的模式当在一个 26 位处理器模式中的时候编程模型倒退成早期的 26 位 ARM 处理器除了下列变动之外它的行为与 ARM2aS 宏单元(macrocell)相同:只在 ARM 被配置为 26 位程序和数据空间的时候它才生成地址例外在其他配置下OS 仍然可以通过使用外部逻辑模拟地址例外的行为比如用一个内存管理单元在超出 64Mbyte 范围的时候生成一个异常终止并把这个异常终止转换成给这个应用程序的一个'地址例外陷入'保持在通用寄存器和程序状态寄存器之间传送数据的新指令可操作在调用了包含 26 位的 ARM 二进制代码的之后操作系统可以使用这些新指令返回到一个 32 位模式当在一个 32 位程序和数据空间配置下的时候所有例外(包括未定义指令和软件中断)把处理器返回到一个32 位模式所以必须修改操作系统来处理它们如果处理器尝试写到在 &0 和 &1F 之间包括二者(就是例外向量)的一个位置则硬件将禁止写操作并生成一个数据异常终止这允许操作系统来截获对例外向量的变动并把向量重定向到一些伪装(veneer)代码上在调用 26 位例外处理程序之前这些伪装代码应该把处理器置于一个 26 位模式中在所有其他方面当在一个 26 位模式下进行操作的时候ARM 表现的如同一个 26 位 ARMCPSR 的相关的位将被组建(incorporated)回到 R15 中来形成 I 和 F 位在位 27 和 26 的 PC/PSR指令集表现的如同增加了 MRS 和 MSR 指令的 ARM2aS 宏单元在 ARM 6(和以后)的 32 位模式下可获得的寄存器有:User26 SVC26 IRQ26 FIQ26 User SVC IRQ ABT UND FIQR0 ----- R0 ----- R0 ----- R0 -- -- R0 ----- R0 ----- R0 ----- R0 ----- R0 ----- R1R1 ----- R1 ----- R1 ----- R1 -- -- R1 ----- R1 ----- R1 ----- R1 ----- R1 ----- R2R2 ----- R2 ----- R2 ----- R2 -- -- R2 ----- R2 ----- R2 ----- R2 ----- R2 ----- R2R3 ----- R3 ----- R3 ----- R3 -- -- R3 ----- R3 ----- R3 ----- R3 ----- R3 ----- R3R4 ----- R4 ----- R4 ----- R4 -- -- R4 ----- R4 ----- R4 ----- R4 ----- R4 ----- R4R5 ----- R5 ----- R5 ----- R5 -- -- R5 ----- R5 ----- R5 ----- R5 ----- R5 ----- R5R6 ----- R6 ----- R6 ----- R6 -- -- R6 ----- R6 ----- R6 ----- R6 ----- R6 ----- R6R7 ----- R7 ----- R7 ----- R7 -- -- R7 ----- R7 ----- R7 ----- R7 ----- R7 ----- R7R8 ----- R8 ----- R8 R8_fiq R8----- R8 ----- R8 ----- R8 ----- R8 R8_fiqR9 ----- R9 ----- R9 R9_fiq R9 ----- R9 ----- R9 ----- R9 ----- R9 R9_fiqR10 ---- R10 ---- R10 R10_fiq R10 ---- R10 ---- R10 ---- R10 ---- R10 R10_fiqR11 ---- R11 ---- R11 R11_fiq R11 ---- R11 ---- R11 ---- R11 ---- R11 R11_fiqR12 ---- R12 ---- R12 R12_fiq R12 ---- R12 ---- R12 ---- R12---- R12 R12_fiqR13 R13_svc R13_irq R13_fiq R13 R13_svc R13_irq R13_abt R13_und R13_fiqR14 R14_svc R14_irq R14_fiq R14 R14_svc R14_irq R14_abt R14_und R14_fiq--------- R15 (PC / PSR) --------- --------------------- R15 (PC) -------------------------------------------- CPSR -----------------------SPSR_svc SPSR_irq SPSR_abt SPSR_und SPSR_fiq简要的说32 位的与 26 位的不同是:PC 是完全的 32 位宽并只用做程序计数器PSR 包含在它自己的寄存器 CPSR 中每个有特权的模式都有一个专有的 SPSR 寄存器用来保存 CPSR这里有两个新的特权模式每个有特权的模式都有 R13 和 R14 的专有复件CPSR 和 SPSR 寄存器CPSR 寄存器(和保存它的 SPSR 寄存器)中的位分配如下:31 30 29 28 --- 7 6 - 4 3 2 1 0N Z C V I F M4 M3 M2 M1 M00 0 0 0 0 User26 模式0 0 0 0 1 FIQ26 模式0 0 0 1 0 IRQ26 模式0 0 0 1 1 SVC26 模式1 0 0 0 0 User 模式1 0 0 0 1 FIQ 模式1 0 0 1 0 IRQ 模式1 0 0 1 1 SVC 模式1 0 1 1 1 ABT 模式1 1 0 1 1 UND 模式关于 N、Z、C、V 标志和 I、F 中断标志请参见(26 位) PSR这在实践中意味着什么?多数 ARM 代码将正确的工作唯一不能工作的是通过摆弄 R15 来设置处理器状态的那些操作不幸的是好象没有简便的方法修理这个问题我检查了一个有潜在问题的9K 程序(一个MODE 7 teletext frame viewer用 C 写的)基本上查找:用 R15 作为目的寄存器的 MOVS 指令以'^'作为后缀并装载 R15 的 LDMFD 指令大约有 64 个指令被归入此类好象有没有什么方式来自动进行转换基本上...系统如何知道哪个是数据哪个是代码实际上一个灵巧的基于规则的程序能够可以做非常准确的猜测但"非常准确的猜测"就足够了吗?没有简单的指令替代一个自动系统可以修补需要的指令并调整(jiggle)周围的代码但这将导致不希望的副作用比如一个 ADR 宏指令(directive)不在范围内(in range)需要难以置信的技巧(It is incredibly hacky)当然最好重新编译或修改源代码这是很不容易的这样小的变更竟有如此严重(far-reaching)的后果ARM中文指令--程序状态寄存器程序状态寄存器MRSMSR直接查看 R15/PSR 在 32-bit 模式下的详情寄存器 15 (26-bit 模式):R15 构造如下:Bit 31 30 29 28 27 26 25------------2 1 0N Z C V I F 程序计数器 S1 S0标志的意义:N Negative 如果结果是负数则置位Z Zero 如果结果是零则置位C Carry 如果发生进位则置位O Overflow 如果发生溢出则置位I IRQ 中断禁用F FIQ 快速中断禁用S1 和 S0 是处理器模式标志:S1 S0 模式0 0 USR - 用户模式0 1 FIQ - 快速中断模式1 0 IRQ - 中断模式1 1 SVC - 超级用户模式在 R15 作为一个指令的第一个操作数的时候只有程序计数器部分是可以获得的所以下列指令把 PC 复制到一个寄存器中并向这个目标寄存器加上 256: ADD R0, R15, #256(对于 BASIC 汇编器 R15 和 PC 的意思是相同的)在 R15 作为第二个操作数的时候所有 32 位都是可以获得的: 程序计数器、标志、和状态下列代码段将标识当前的处理器模式:MOV R0, #3 ; 装载一个位掩码(%11)到 R0 中AND R0, R0, PC ; 把 R15 与 R0 做逻辑与并把结果放入 R0来得到模式状态CMP R0, #3 ; 把模式与 '3' 相比较(SVC)BEQ svc ; 如果等于 SVC 模式分支到 'svc'CMP R0, #2 ; 把模式与 '2' 相比较 (IRQ)BEQ irq ; 如果等于 IRQ 模式分支到 'irq'CMP R0, #1 ; 把模式与 '1' 相比较(FIQ)BEQ fiq ; 如果等于 FIQ 模式分支到 'fiq'CMP R0, #0 ; 把模式与 '0' 相比较(USR)BEQ usr ; 如果等于 USR 模式分支到 'usr'这个例子不遵从 32-bit 体系如何在 32-bit 环境中读当前的模式请参照下面的章节改变处理器的状态:要改变处理器模式、或者任何标志我们需要用想要的标志 EOR(异或)状态标志新状态 = 旧状态 EOR (1 << 28) 可以成为改变 oVerflow 标志的伪码但是我们不能做这个简单的 EORS 操作原因是这将导致随后的两个指令被跳过不要担心指令 TEQ 做一个假装的 EOR (结果不存储到任何地方)把它与 P 后缀组合则把结果的第 0、1、和 26 至 31 位直接写到 R15 的第 0、1、和26 至 31 位这是改变标志的一个简便的方法: TEQP R15, bit_mask如果你处在允许你设置一个标志的一个模式中则你只可以改变这个标志这个例子不遵从 32-bit 体系如何在 32-bit 环境中改变模式请参照下面的章节可以被扩充它来改变处理器模式例如要进入 SVC 模式你可以:MOV R6, PC ; 把 PC 的最初状态存储到 R6 中ORR R7, R6, #3 ; 设置 SVC 模式TEQP R7, #0 ; 把(在 R7 中的)模式标志写入 PC而返回最初的模式是:TEQP R6, #0 ; 把(在 R6 中的)最初的模式写入 PC在改变了模式之后你应该进行一个空操作来允许这个寄存器安定下来比如 MOV R0, R0 之类的东西就可以废弃使用 NV 后缀的指令32 位 PSR如同在32 位操作中描述的那样ARM 3 之后的处理器提供一个 32 bit 地址空间它们把 PSR 移出 R15 并给予 R15 完整的 32 位位域在其中存储当前位置的地址目前除了一些不太可能遇到的情况之外RISC OS 工作在 26 位模式32 位模式是重要的因为 26 位(在老的 PSR 中)把每个应用程序的可寻址内存的最大数量限制为 28Mb这就是不管你安装了多少内存你不能拖动超过28Mb 的下一个槽(drag the Next slot beyond 28Mb)的原因CPSR 寄存器(和保存它的 SPSR 寄存器)中的位分配如下:31 30 29 28 --- 7 6 - 4 3 2 1 0N Z C V I F M4 M3 M2 M1 M00 0 0 0 0 User26 模式0 0 0 0 1 FIQ26 模式0 0 0 1 0 IRQ26 模式0 0 0 1 1 SVC26 模式1 0 0 0 0 User 模式1 0 0 0 1 FIQ 模式1 0 0 1 0 IRQ 模式1 0 0 1 1 SVC 模式1 0 1 1 1 ABT 模式1 1 0 1 1 UND 模式典型的处理器将在 User26、FIQ26、IRQ26 和 SVC26 下操作可以进入一个 32 位模式但要格外小心RISC OS 不希望这样并且如果它发现自己在其中会非常生气!操纵 32 位 PSR 的指令你不能在32 位模式中使用MOVS PC, R14 或LDMFD R13!, {registers, PC}^也不能使用 ORRS PC, R14, #1<<28 来设置 V 标志现在需要使用 MRS 和 MSR复制一个寄存器到 PSR 中MSR CPSR, R0 ; 复制 R0 到 CPSR 中MSR SPSR, R0 ; 复制 R0 到 SPSR 中MSR CPSR_flg, R0 ; 复制 R0 的标志位到 CPSR 中MSR CPSR_flg, #1<<28 ; 复制(立即值)标志位到 CPSR 中复制 PSR 到一个寄存器中MRS R0, CPSR ; 复制 CPSR 到 R0 中MRS R0, SPSR ; 复制 SPSR 到 R0 中指令格式你有两个PSR - CPSR 是当前的程序状态寄存器(Current ProgramStatus Register)而SPSR 是保存的程序状态寄存器(Saved Program Status Register)(前面的处理器模式的 PSR)每个有特权的模式都有自己的 SPSR可获得的 PSR 有:CPSR_all - 当前的SPSR_svc - 保存的SVC(32) 模式SPSR_irq - 保存的IRQ(32) 模式SPSR_abt - 保存的ABT(32) 模式SPSR_und - 保存的UND(32) 模式SPSR_fiq - 保存的FIQ(32) 模式你不能显式的指定把 CPSR 保存到哪个 SPSR 中比如 SPSR_fiq而是必须变更到 FIQ 模式并接着保存到 SPSR换句话说你只能在你所在的模式中改变这个模式的 SPSR使用 _flg 后缀允许你改变标志位而不影响控制位在 user(32) 模式中保护 CPSR 的控制位你只能改变条件标志在其他模式中可获得整个 CPSR你不应该指定 R15 为一个源寄存器或一个目标寄存器最后在 user(32) 模式中你不能尝试访问 SPSR因为它不存在!要设置 V 标志:MSR CPSR_flg, #&10000000这将设置 V 标志但不影响控制位要改变模式:MRS R0, CPSR_all ; 复制 PSRBIC R0, R0, #&1F ; 清除模式位ORR R0, R0, #new_mode ; 把模式位设置为新模式MSR CPSR_all, R0 ; 写回 PSR变更模式现在我们要做的是进入 SVC32 模式并设置 Z 标志接着我们返回 SVC26 模式并'测试'是否设置了 Z RISC OS 不希望发现自己处在 32 位模式中所以我们要禁止所有中断并保持它们这样(keep them that way) 尽管这些代码应该执行的非常快但我们不应当冒任何风险...你可能觉得 32 位模式不是非常有用在当前版本的 RISC OS 下这是事实实际上就我而言32 位模式提供给你的只是:访问大于 28Mb 的区域在 RISC OS 上这不是真的很重要在这个系统里 web 浏览器适合于 1 M 或 2 M而重要的艺术程序为那些非常巨大的图象提供它们自己的虚拟内存系统本文档的最初版本和最初的 ARM 汇编器指南包括...StrongARM 提供了两个指令(UMUL 和 UMLA、IIRC)它们处理 64 位乘法这只能在 32 位模式下获得这是错误的在 26 位模式下可以使用扩展的乘法;MP3 解码器就使用了它!尽管 32 位模式的利益好象不是多的那么惊人新近的处理器(比如 Xscale)不再支持 26 位模式所以 RISC OS 和它的应用程序要在 32 位环境下工作则必须经过修改听起来不是很多但是如果所有补偿/改变 R15 中的 PSR 位的引用都必须被变更为对不在 R15 中的独立的 PSR 的引用这就突然变成一个非常重大的问题了还有你不能继续用一个指令来恢复 PSR 并分支回到调用者现在这需要两个独立的指令为此代码必须重写你不能简单的用另一个指令来修补...ARM中文指令--寄存器装载和存储寄存器装载和存储LDMLDRSTMSTRSWP它们可能是能获得的最有用的指令其他指令都操纵寄存器所以必须把数据从内存装载寄存器并把寄存器中的数据存储到内存中传送单一数据使用单一数据传送指令(STR 和LDR)来装载和存储单一字节或字的数据从/到内存寻址是非常灵活的首先让我们查看指令格式:LDR{条件} Rd, <地址>STR{条件} Rd, <地址>LDR{条件}B Rd, <地址>STR{条件}B Rd, <地址>指令格式这些指令装载和存储 Rd 的值从/到指定的地址如果象后面两个指令那样还指定了'B'则只装载或存储一个单一的字节;对于装载寄存器中高端的三个字节被置零(zeroed)地址可以是一个简单的值、或一个偏移量、或者是一个被移位的偏移量可以还可以把合成的有效地址写回到基址寄存器(去除了对加/减操作的需要)各种寻址方式的示例:译注:下文中的 Rbase 是表示基址寄存器Rindex 表示变址寄存器index 表示偏移量偏移量为 12 位的无符号数用移位选项表示比例因子标准寻址方式 - 用 AT&T 语法表示为 disp(base, index, scale) 用 Intel 语法表示为 [base + index*scale + disp]中的变址(连带比例因子)与偏移量不可兼得STR Rd, [Rbase] 存储 Rd 到 Rbase 所包含的有效地址STR Rd, [Rbase, Rindex] 存储 Rd 到 Rbase + Rindex 所合成的有效地址STR Rd, [Rbase, #index] 存储 Rd 到 Rbase + index 所合成的有效地址index 是一个立即值例如STR Rd, [R1, #16] 将把 Rd 存储到 R1+16STR Rd, [Rbase, Rindex]! 存储 Rd 到 Rbase + Rindex 所合成的有效地址并且把这个新地址写回到 RbaseSTR Rd, [Rbase, #index]! 存储 Rd 到 Rbase + index 所合成的有效地址并且并且把这个新地址写回到 RbaseSTR Rd, [Rbase], Rindex 存储 Rd 到 Rbase 所包含的有效地址把 Rbase + Rindex 所合成的有效地址写回 RbaseSTR Rd, [Rbase, Rindex, LSL #2]存储 Rd 到 Rbase + (Rindex * 4) 所合成的有效地址STR Rd, place 存储 Rd 到 PC + place 所合成的有效地址你当然可以在这些指令上使用条件执行但要注意条件标志要先于字节标志所以如果你希望在结果是等于的时候装载一个字节要用的指令是 LDREQB Rx,(不是 LDRBEQ...)如果你指定预先变址寻址(这里的基址和变址都在方括号中)用是否存在'!'来控制写回操作上面的第4和第5个例子中使用了这个标志你可以使用它来在内存中自动正向或反向移动一个字符串打印例程将变成:.loopLDRB R0, [R1, #1]!SWI "OS_WriteC"CMP R0, #0BNE loop而不是:.loopLDRB R0, [R1]SWI "OS_WriteC"ADD R1, R1, #1CMP R0, #0BNE loop对于过后变址寻址'!'是无效的(这里的变址在方括号外面比如上面的例子6)因为写回是暗含的如同你见到的那样变址可以被移位来实现比例缩放除此之外可以从基址上减去偏移量在这种情况下你可以使用如下代码:LDRB R0, [R1, #-1]尽管你可以存储或装载 PC但你不可以用装载或存储指令来修改 PSR要装载一个被存储的'状态'并正确的恢复它请使用:LDR R0, [Rbase]MOVS R15, R0假如你在有特权的模式下MOVS 将导致 PSR 的位被更改对 PC 使用 MOVS 不遵从 32-bit 体系你需要使用 MRS 和 MSR 来处理 PSR依照 ARM 汇编手册:译注:下文所叙述内容针对的是小端字节序配置对大端字节序配置在手册中另有专门叙述如果提供的地址在一个字边界上则字节装载(LDRB)使用在 0 至 7 位上的数据如果在一个字地址加上一个字节上则使用 8 至 15 位以此类推选择的字节被放入目标寄存器的低端 8 位中并把寄存器中其余的位用零填充字节存储(STRB)在数据总线上重复源寄存器的的低端 8 位 4 次由外部的内存系统来激活适当的字节子系统来存储数据字装载(LDR)或字存储(STR)将生成一个字对齐的地址使用一个非字对齐的地址将有不明显和未规定的结果实际上提示的是你不能使用 LDR 从一个非对齐的地址装载一个字传送多个数据使用多数据传送指令(LDM 和 STM)来装载和存储多个字的数据从/到内存LDM/STM 的主要用途是把需要保存的寄存器复制到栈上如我们以前见到过的 STMFD R13!, {R0-R12, R14}指令格式是:xxM{条件}{类型} Rn{!}, <寄存器列表>{^}'xx'是 LD 表示装载或 ST 表示存储再加 4 种'类型'就变成了 8 个指令:栈其他LDMED LDMIB 预先增加装载LDMFD LDMIA 过后增加装载LDMEA LDMDB 预先减少装载LDMFA LDMDA 过后减少装载STMFA STMIB 预先增加存储STMEA STMIA 过后增加存储STMFD STMDB 预先减少存储STMED STMDA 过后减少存储指令格式汇编器关照如何映射这些助记符注意 ED 不同于 IB;只对于预先减少装载是相同的在存储的时候ED 是过后减少的FD、ED、FA、和 EA 指定是满栈还是空栈是升序栈还是降序栈一个满栈的栈指针指向上次写的最后一个数据单元而空栈的栈指针指向第一个空闲单元一个降序栈是在内存中反向增长(就是说从应用程序空间结束处开始反向增长)而升序栈在内存中正向增长其他形式简单的描述指令的行为意思分别是过后增加(Increment After)、预先增加(Increment Before)、过后减少(Decrement After)、预先减少(Decrement Before)RISC OS 使用传统的满降序栈在使用符合 APCS 规定的编译器的时候它通常把你的栈指针设置在应用程序空间的结束处并接着使用一个 FD (满降序 - Full Descending)栈如果你与一个高级语言(BASIC 或 C)一起工作你将别无选择栈指针(传统上是 R13)指向一个满降序栈你必须继续这个格式或则建立并管理你自己的栈(如果你是死硬派人士那么你可能喜欢这样做!)'基址'是包含开始地址的寄存器在传统的 RISC OS 下它是栈指针 R13但你可以使用除了 R15 之外的任何可获得的寄存器如果你想把复制操作后栈顶的当前的内存地址保存到栈指针中可以寄存器按从最低到最高的编号次序与到从低端到高端的内存之间传送数据并且因为用指令中的一个单一的位来表示是否保存一个寄存器不可能指定某个寄存器两次它的副作用是不能用下面这样的代码:STMFD R13!, {R0, R1}LDMFD R13!, {R1, R0}来交换两个寄存器的内容提供了一个有用的简写要包含一个范围的寄存器可以简单的只写第一个和最后一个并在其间加一个横杠例如 R0-R3 等同与 R0, R1, R2, R3只是更加整齐和理智而已...在把 R15 存储到内存中的时候还保存了 PSR 位。

ARM处理器模式和寄存器介绍

ARM处理器共有7种运行模式:用户模式(user,use)正常程序执行模式快速中断模式(fiq)用于高速数据传输和通道处理外部中断模式(irq)用于通常的中断处理管理模式(sve)操作系统使用的一种保护模式数据访问终止模式(abt)用于虚拟存储及存储保护未定义指令终止模式(und)用于支持通过软件方针硬件的协处理器系统模式(sys)用于运行特权级的操作系统任务除了用户模式之外的6种处理器模式称为特权模式(privileged modes)。

在这些模式下,程序可以访问所有的系统资源,也可以任意第进行处理器模式切换。

其中,除系统模式外,其他5种特权模式又称为异常模式。

处理器模式可以通过软件控制进行切换,也可以通过外部中断或异常处理过程进行切换。

大多数的用户程序运行在用户模式下。

这时,应用程序不能够访问一些受操作系统保护的系统资源。

应用程序也不能直接进行处理器模式的切换。

当需要进行处理器模式切换时,应用程序可以产生异常处理,在异常处理过程中进行处理器处理器模式的切换。

这种体系结构可以使系统控制整个系统的资源。

当应用程序发生异常中断时,处理器进入相应的异常模式。

在每一种异常模式中都有一组寄存器,供相应的异常处理程序使用,这样就可以保证在进入异常模式时,拥护模式下的寄存器(保存了程序运行状态)不被破坏。

系统模式并不是通过异常过程进入的,它和用户模式具有完全一样的寄存器。

但是系统模式属于特权模式,可以访问所有的系统资源,也可以直接进行处理器模式切换。

它主要供操作系统任务使用。

通常操作系统的任务需要访问所有的系统资源,同时该任务仍然使用拥护模式的寄存组,而不是使用异常模式下相应的寄存器组,这样可以保证当异常中断发生时任务状态不被破坏。

ARM处理器含有37个寄存器,这些寄存器包括以下两类寄存器。

(1)31个通用寄存器:包括程序计数器PC等,这些寄存器都是32位寄存器。

(2)6个状态寄存器:状态寄存器也是32位的寄存器,但是只使用了其中的12位。

第三节ARM体系结构

一般的通用寄存器

寄存器类别 寄存器在汇编中的名称

用户

系统

R0(a1)

R1(a2)

R2(a3)其中R0~R7为

R3(a4)

未R分4(v1) 组的寄存器,也

通用寄存器 和程序计数

器

就R是5(v2) 说对于任何处理 R6(v3)

器R模7(v4) 式,这些寄存器 都对应于相同的32位 R8(v5)

管理 (svc) 操作系下统保访护问代码用户模系统式复位的和寄软件存中器断响就应比时进较入方此模式

中止 (abt) 未定义 (und)

用或于存支储便 可持器虚 保,以拟护而使内存且用和操这/ 作个在A系模RM统式7TD的访MI一问没有些一大用特 些处权 受任 控务 的 支软持件硬仿资件真协源处。理器的 未定义指令异常响应时进入此模式

各模式下实际访问的寄存器

用户

系统

管理

中止

未定义

RR00

在汇编语言中寄存

R1

器R0~R13为保存数据

R2

或地址值的通用寄存器。

R3

它们是完全通用的寄存器, R4

不会被体系结构作为特殊

R5

用途,并且可用于任何使

R6

用通用寄存器的指令。

R7

R8

R9

R10

R11

R12

R13

RR1133__ssvc

R13_abt

SSPPSSRR__fifqiq

ARM状态各模式下可以访问的寄存器

寄存器类别 寄存器在汇编中的名称

通用寄存器和 程序计数器

状态寄存器

R0 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13(SP) R14(LR) R15(PC) CPSR SPSR

ARM汇编之寄存器

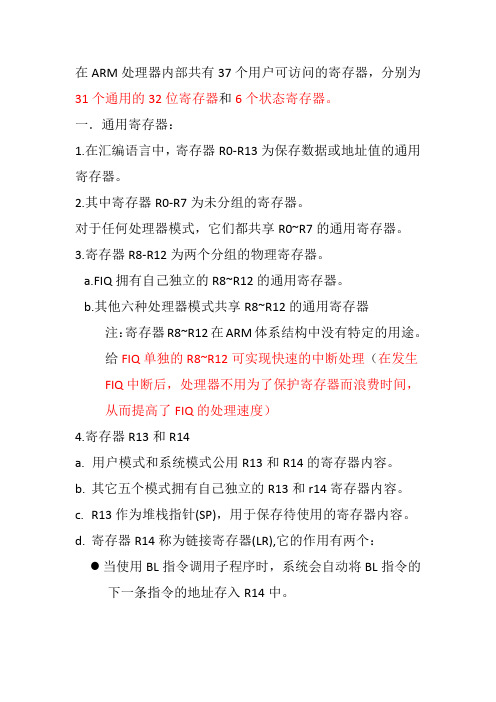

在ARM处理器内部共有37个用户可访问的寄存器,分别为31个通用的32位寄存器和6个状态寄存器。

一.通用寄存器:1.在汇编语言中,寄存器R0-R13为保存数据或地址值的通用寄存器。

2.其中寄存器R0-R7为未分组的寄存器。

对于任何处理器模式,它们都共享R0~R7的通用寄存器。

3.寄存器R8-R12为两个分组的物理寄存器。

a.FIQ拥有自己独立的R8~R12的通用寄存器。

b.其他六种处理器模式共享R8~R12的通用寄存器注:寄存器R8~R12在ARM体系结构中没有特定的用途。

给FIQ单独的R8~R12可实现快速的中断处理(在发生FIQ中断后,处理器不用为了保护寄存器而浪费时间,从而提高了FIQ的处理速度)4.寄存器R13和R14a.用户模式和系统模式公用R13和R14的寄存器内容。

b.其它五个模式拥有自己独立的R13和r14寄存器内容。

c.R13作为堆栈指针(SP),用于保存待使用的寄存器内容。

d.寄存器R14称为链接寄存器(LR),它的作用有两个:当使用BL指令调用子程序时,系统会自动将 BL指令的下一条指令的地址存入R14中。

程序A指令过程中调用程序B程序跳转至标号Lable处,执行程序B.系统将BL Lable指令的下一条指令所在地址存入R14中程序B执行最后,执行语句MOV PC,LR将R14寄存器的内容放入PC处,返回至NEXT处继续执行。

●当发生异常时,系统自动将异常的返回地址放入R14中(有些异常有一个小的固定的偏移量)二.重要的寄存器1.堆栈指针R13R13作为堆栈指针SP。

在ARM指令集中,由于没有以特殊方式使用R13的指令。

(在Thumb)指令集中存在使用R13的指令)每个异常模式都有其自身的R13分组版本,它通常指向由异常模式所专用的堆栈。

在入口处,异常处理程序通常将其他要使用的寄存器值保存到这个堆栈。

通过返回时将这些值重装到寄存器中。

异常处理程序可确保异常发生时的程序状态不会被破坏。

arm工作模式及寄存器解析

2、快速中断模式(FIQ) 用于高速数据传输

3、外部中断模式(IRQ) 用于通常的中断处理

工作模式

4. 管理模式(svc) 操作系统使用的保护模式

5. 数据访问终止模式(abt) 当数据或指令预取终止时进入该模式,可用于虚拟存储及 存储保护。 6. 系统模式(sys) 运行具有特权的操作系统任务。 7. 未定义指令中止模式(und) 当未定义的指令执行时进入该模式,可用于支持硬件

工作模式

ARM微处理器的运行模式可以通过软件改 变,也可以通过外部中断或异常处理改变。

应用程序运行在用户模式下,当处理器运行

在用户模式下时,某些被保护的系统资源是 不能被访问的。

工作模式

除用户模式以外,其余的所有6种模式称之为 非用户模式,或特权模式(Privileged Modes);其中除去用户模式和系统模式以

寄存器(Thumb状态)

寄存器对应

Thumb状态下的寄存器组织与ARM状态下的寄存器组织的 关系: v Thumb状态下和ARM状态下的R0~R7是相同的。 v Thumb状态下和ARM状态下的CPSR和SPSR是相同的。 v Thumb状态下的SP对应于ARM状态下的R13。 v Thumb状态下的LR对应于ARM状态下的R14。

ARM微处理器的指令长度可以是32位(在 ARM状态下),也可以为16位(在Thumb 状态下)。ARM微处理器中支持字节(8 位)、半字(16位)、字(32位)三种数 据类型,其中,字需要4字节对齐(地址的 低两位为0)、半字需要2字节对齐(地址

的最低位为0)。

工作模式

ARM微处理器支持7种工作模式,分别为:

不分组通用寄存器

R0-R7是不分组寄存器。这意味着在所有处 理器模式下,访问的都是同一个物理寄存 器。未分组寄存器没有被系统用于特别的用 途,任何可采用通用寄存器的应用场合都可

ARM寄存器详解

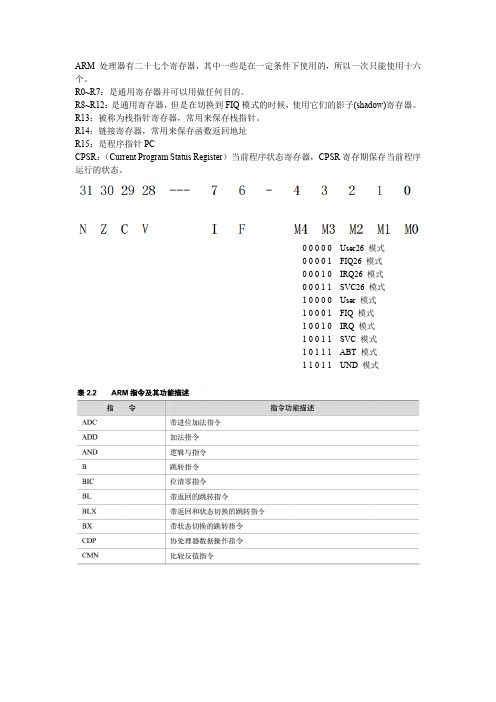

ARM 处理器有二十七个寄存器,其中一些是在一定条件下使用的,所以一次只能使用十六个。

R0~R7:是通用寄存器并可以用做任何目的。

R8~R12:是通用寄存器,但是在切换到FIQ模式的时候,使用它们的影子(shadow)寄存器。

R13:被称为栈指针寄存器,常用来保存栈指针。

R14:链接寄存器,常用来保存函数返回地址R15:是程序指针PCCPSR:(Current Program Status Register)当前程序状态寄存器,CPSR寄存期保存当前程序运行的状态。

0 0 0 0 0 User26 模式0 0 0 0 1 FIQ26 模式0 0 0 1 0 IRQ26 模式0 0 0 1 1 SVC26 模式1 0 0 0 0 User 模式1 0 0 0 1 FIQ 模式1 0 0 1 0 IRQ 模式1 0 0 1 1 SVC 模式1 0 1 1 1 ABT 模式1 1 0 1 1 UND 模式ARM寻址方式1.立即数寻址ARM 指令的立即数寻址是一种特殊的寻址方式,操作数本身就在指令中给出,只要取出指在以上2 条指令中,第2个源操作数即为立即数,实际使用时以“#”符号为前缀。

2.寄存器寻址寄存器寻址就是利用寄存器中的数值作为操作数,这种寻址方式是各类微处理器经常采用的一种方式,也是一种执行效率较高的寻址方式。

如以下的指令。

3.寄存器间接寻址寄存器间接寻址就是以寄存器中的值作为操作数的地址,而操作数本身存放在存储器中。

例如以下指令。

在第 1 条指令中,以寄存器R2 的内容作为操作数的地址,然后与R1 相加,其结果存入寄存器R0中。

第2条指令将以R1 的值为地址的存储器中的内容送到寄存器R0中。

4.基址变址寻址基址变址的寻址方式就是将寄存器(该寄存器一般称作基址寄存器)的内容与指令中给出的地址偏移量相加,从而得到一个操作数的有效地址。

如下面的几条指令所示。

在第1条指令中,将寄存器R1 的内容加上0x3A 形成操作数的有效地址,将该地址处的操作数送到寄存器R0中。

arm的32位指令的格式及个部分功能

ARM的32位指令格式及各部分功能一、ARM的32位指令格式ARM的32位指令格式分为四部分,包括指令操作码、条件码、寄存器和操作数。

1. 指令操作码指令操作码是指令的基本操作类型,为了方便指令的译码和执行,ARM指令集将指令操作码分为几类,包括数据处理指令、分支指令、访存指令等。

不同的指令操作码代表了不同的操作类型,如加法、乘法、移位、与操作等。

2. 条件码条件码用于指定指令在何种条件下执行,如等于零、不等于零、大于、小于等。

通过条件码的设置,可以实现根据不同条件来执行不同的指令,这样可以提高指令的灵活性和效率。

3. 寄存器ARM的32位指令格式中包括多个寄存器字段,用于指定指令的操作对象和操作结果的存放位置。

ARM架构中一般有16个通用寄存器和几个特殊用途的寄存器,不同的寄存器字段代表了不同的寄存器编号。

4. 操作数操作数是指令的操作对象,ARM的32位指令中包括多个操作数字段,用于指定指令的源操作数和目的操作数。

操作数可以是寄存器、立即数或内存位置区域等。

二、各部分功能1. 指令操作码的功能指令操作码代表了指令的操作类型,不同的指令操作码对应了不同的操作,比如数据处理指令可以进行加法、减法、逻辑运算等操作,分支指令可以实现程序的跳转,访存指令可以进行内存的读写操作。

2. 条件码的功能条件码用于指定指令的执行条件,通过设置条件码可以实现根据不同条件来执行不同的指令,这样可以提高程序的执行效率和灵活性。

3. 寄存器的功能寄存器用于存放指令的操作对象和操作结果,ARM的32位指令中包括多个寄存器字段,用于指定指令的源操作数和目的操作数。

寄存器的功能包括存储数据、临时存储和传递参数等。

4. 操作数的功能操作数是指令的操作对象,ARM的32位指令中包括多个操作数字段,用于指定指令的源操作数和目的操作数。

操作数的功能包括指定操作对象、传递参数和存储数据等。

结论ARM的32位指令格式包括指令操作码、条件码、寄存器和操作数四部分,各部分都有特定的功能,通过它们的组合可以实现丰富多样的指令操作和灵活的程序控制。

第3章 ARM处理器

;64位数结果:存放在寄存器R0和R1 位数结果:存放在寄存器 和 位数结果 ;两个 位数:存放在寄存器R2和R3 两个32位数:存放在寄存器 和 两个 位数 ADCS R0,R2,R3 ; 带进位加,结果保存在 和R1寄存器 带进位加,结果保存在R0和 寄存器

3.3.1 算术运算指令

3.SUB指令 . 指令

第3 章

ARM处理器 ARM处理器

ARM既是一种嵌入式处理器体系结构的缩写,也是一 既是一种嵌入式处理器体系结构的缩写, 既是一种嵌入式处理器体系结构的缩写 家公司的名字。目前有数十家公司使用ARM体系结构开发 家公司的名字。目前有数十家公司使用 体系结构开发 自己的芯片,支持的外部设备和功能丰富多样。 自己的芯片,支持的外部设备和功能丰富多样。ARM体系 体系 相比其他的体系具有结构简单、入门快等特点。使用ARM 相比其他的体系具有结构简单、入门快等特点。使用 核心的处理器虽然众多,但是核心都是相同的。因此, 核心的处理器虽然众多,但是核心都是相同的。因此,掌握 的体系结构, 了ARM的体系结构,用不同的处理器只要是基于 的体系结构 用不同的处理器只要是基于ARM核心 核心 都能很快上手。本章的主要内容包括: 都能很快上手。本章的主要内容包括: 微处理器和微控制器的关系 ARM处理器介绍 处理器介绍 ARM体系结构 体系结构 ARM的功能选型 的功能选型

格式: 条件}{S} <dest>, <op_1>, <op_2> 格式:SUB{条件 条件 存器, 存器,op_1和op_2是操作数 和 是操作数 dest = op_1 - op_2 SUB SUB SUB //dest是目的寄 是目的寄

R0, R1, R2 ; R0 = R1 - R2 R0, R1, #256 ; R0 = R1 - 256 R0, R2, R3,LSL#1 ; R0 = R2 - (R3 << 1)

ARM处理器寄存器和运行状态

ARM处理器寄存器和运⾏状态ARM体系的CPU有以下7种⼯作模式: 1、⽤户模式(Usr):⽤于正常执⾏程序;2、快速中断模式(FIQ):⽤于⾼速数据传输;3、外部中断模式(IRQ):⽤于通常的中断处理;4、管理模式(svc):操作系统使⽤的保护模式;5、数据访问终⽌模式(abt):当数据或指令预取终⽌时进⼊该模式,可⽤于虚拟存储以及存储保护;6、系统模式(sys):运⾏具有特权的操作系统任务;7、未定义指令中⽌模式(und):当未定义的指令执⾏时进⼊该模式,可⽤于⽀持硬件;当异常发⽣的时候CPU会进⼊到相应的模式来进⾏处理:异常模式描述复位管理模式复位电平有效时,产⽣复位异常,程序转跳到复位处理程序执⾏未定义指令未定义模式遇到不能处理的指令,产⽣未定义指令异常软件中断管理模式执⾏swi指令产⽣,⽤于⽤户模式下的程序调⽤特权操作指令预存指令中⽌模式处理器预取指令的地址不存在,或者该地址不允许当前指令访问,产⽣指令预取中断异常数据操作中⽌模式处理器预取数据的地址不存在,或者该地址不允许当前指令访问,产⽣指令预取中断异常未使⽤未使⽤未使⽤IRQ IRQ外部中断请求有效,且CPSR中的1位为0时,产⽣IRQ异常FIQ FIQ快速中断请求引脚有效,且CPSR中的F位为0时,产⽣FIQ异常以下是寄存器和运⾏模式对应的关系:R0---R12是普通寄存器,可以任意读写.R13是栈指针寄存器,⽤于保存堆栈指针R14是程序连接寄存器,当执⾏BL⼦程序调⽤指令时,R14中得到R15的备份,⽽当发⽣中断或异常时,R14保存R15的返回值R15是程序计数器(A/C)PSR:(标志位寄存器) T位:1——CPU处于Thumb状态, 0——CPU处于ARM状态; I、F(中断禁⽌位): 1——禁⽌中断, 0——中断使能; ⼯作模式位:可以改变这些位,进⾏模式切换;spsr:程序状态保存寄存器,当切换进⼊某⼀个特权模式时,SPSR保存前⼀个⼯作模式的CPSR值,这样,当返回前⼀个⼯作模式时,可以将SPSR的值恢复到CPSR中。

ARM处理器的工作模式

ARM处理器v4及以上版本有37个32位的寄存

其中31个为通用寄存器;6个为状态寄存器。

– 31个通用寄存器

R0~R15; R13_svc、R14_svc; R13_abt、R14_abt; R13_und、R14_und; R13_irq、R14_irq; R8_fiq-R14_fiq

– 6 个状态寄存器

①系统上电复位后进入管理模式,运行系统初始化 程序,如中断允许/禁止,主时钟设置,SDRAM配置, 各个功能模块初始化等。 ②当执行软件中断指令SWI时,进入管理模式。

1.1.2 ARM处理器的工作模式(4)

• 处理器模式的切换方式:

– 软件控制进行切换。 – 通过外部中断和异常进行切换

处理器启动时的模式转换图

– T控制(标志)位——反映处理器的运行状态

• T=1时,程序运行于Thumb状态 • T=0时,程序运行于ARM状态

– M控制位——决定了处理器的运行模式

• 当发生异常时这些位被改变。 • 如果处理器运行在特权模式,这些位也可以由 程序修改。

1.2.3 ARM9的状态寄存器(4)

3、保留位

CPSR中的其余位为保留位,当改变CPSR中 的条件码标志位或者控制位时,保留位不要改变, 在程序中也不要使用保留位来存储数据。保留位将 用于ARM版本的扩展。

•

从Thumb状态切换到ARM状态

有两种情况ARM处理器自动切换到Thumb状态。 (1)执行BX指令,当操作数寄存器的位[0]为0时,则 微处理器从Thumb状态切换到ARM状态。 (2)当处理器在Thumb状态时发生异常(如IRQ、FIQ、 Undef等),则处理器从Thumb状态自动切换到ARM状态 进行异常处理

1.1 ARM处理器的工作状态和模式(3)

ARM寄存器与处理器模式

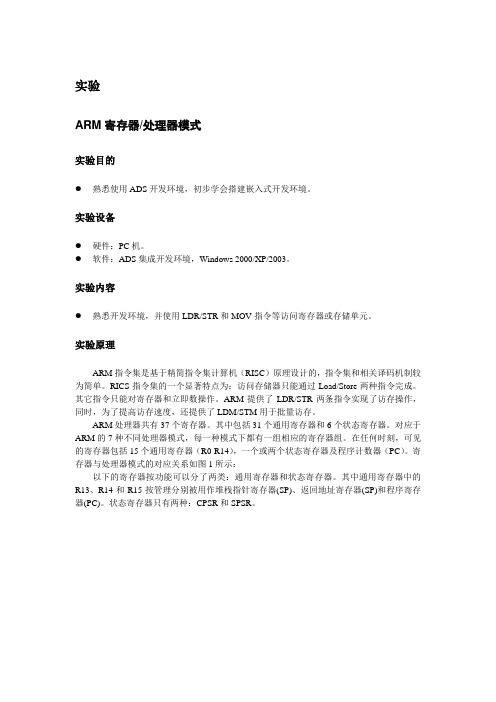

实验ARM寄存器/处理器模式实验目的●熟悉使用ADS开发环境,初步学会搭建嵌入式开发环境。

实验设备●硬件:PC机。

●软件:ADS集成开发环境,Windows 2000/XP/2003。

实验内容●熟悉开发环境,并使用LDR/STR和MOV指令等访问寄存器或存储单元。

实验原理ARM指令集是基于精简指令集计算机(RISC)原理设计的,指令集和相关译码机制较为简单。

RICS指令集的一个显著特点为:访问存储器只能通过Load/Store两种指令完成。

其它指令只能对寄存器和立即数操作。

ARM提供了LDR/STR两条指令实现了访存操作,同时,为了提高访存速度,还提供了LDM/STM用于批量访存。

ARM处理器共有37个寄存器。

其中包括31个通用寄存器和6个状态寄存器。

对应于ARM的7种不同处理器模式,每一种模式下都有一组相应的寄存器组。

在任何时刻,可见的寄存器包括15个通用寄存器(R0-R14),一个或两个状态寄存器及程序计数器(PC)。

寄存器与处理器模式的对应关系如图1所示:以下的寄存器按功能可以分了两类:通用寄存器和状态寄存器。

其中通用寄存器中的R13、R14和R15按管理分别被用作堆栈指针寄存器(SP)、返回地址寄存器(SP)和程序寄存器(PC)。

状态寄存器只有两种:CPSR和SPSR。

图1 ARM处理器模式与寄存器的关系●通用寄存器通用寄存器包括R0~R15,可以分为三类:1.未分组寄存器R0~R7,它们在每个模式下都对应同一个物理寄存器。

2.分组寄存器R8~R14,又称影子寄存器,不同模式下的寄存器对应的物理寄存器不同。

3.程序计数器PC(R15) 。

●程序状态寄存器CPSR 和SPSR 的格式如下:31 30 29 28 27 26 8 7 6 5 4 3 2 1 0N Z C V Q 保留I F T M M M M M 条件码标志:N、Z、C、V。

大多数指令可以测试这些条件码标志以决定程序指令如何执行。

ARM处理器工作模式及寄存器结构

cache内容和内存地址的映射:有全相联映射方式、直接映像方式、组组相

联映像方式。

cache的存储空间小于内存,所以存在cache内容的替换问题,ARM中

cache的替换算法:随机替换和轮转法

5、快速进程上下文切换(fastcontextswitchextension,FCSE)

制;

关于域:最多支持16个域,设置每个域的访问控制特性,可以控制是否从

页表得到访问权限...

3、MPU与MMU差别

MPU只是简单支持MMU一小部分功能:不支持虚拟地址和实地址的映

射;不支持页表;(MMU需要更多硬件来支持相应的功能);

MPU最多可以分为8个域,对相应的域进行B、C、AP的设置;

同样CP15可以控制MPU的功能开关,对于域的设置可以存在地址的重

的/地址或寄存器)、条件、地址变化等等;

3、ARM指令和简化的Thumb指令可以相互跳转

B、BL、BLX、BX带L表示考虑LR寄存器,而X实现不同指令模式的

切换;

4、批量操作地址的方式分类

IA、IB、DA、DB

A:afterB:beforeI:incrementD:decrement

亦即:事后递增事先递增事后递减事先递减四种方式;

二、ARM的存储系统及MMU和MPU的差别与联系

1、ARM的存储系统

CASHE及WRITEBUFFER技术用于缩小内存和处理器之间差距;

存储类型:ROM(FLASH/ROM)+RAM(SRAM、DRAM、SDRAM[

sychronizationDRAM])

ARM采用协处理器CP15来进行存储器的管理;

主要解决多个进程映射虚拟地址映射重叠问题,简单理解增加了进程ID

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Neusoft Institute of Information

3.1.3 寄存器组织

如图 3-1 所示,ARM微处理器共有37个 32位寄存器,其中31个为通用寄存器,6个为 状态寄存器。 这些寄存器不能被同时访问,具体哪些寄 存器是可编程访问的,取决于微处理器的工作 状态及具体的运行模式。 但在任何时候,通用寄存器R0~R14、程 序计数器PC、当前状态寄存器CPSR都是可访 问的。

3.1.1 ARM微处理器的工作状态

从编程的角度看,ARM微处理器的工作状态一般有两种, 并可在两种状态之间切换: •ARM状态,此时处理器执行32位的字对齐的ARM指 令; •Thumb状态,此时处理器执行16位的、半字对齐的 Thumb指令。

December 25, 2018

Neusoft Institute of Information

December 25, 2018

Neusoft Institute of Information

3.1.2 处理器模式

• • • • •

•

•

ARM微处理器支持7种运行模式,分别为: 用户模式(User):正常的程序执行模式。 快速中断模式(Fast Interrupt):用于高速数据传输或通道处理。 外部中断模式(Interrupt):用于通用的中断处理。 管理模式(Supervisor):操作系统使用的保护模式,系统复位 后的缺省模式。 中止模式(Abort):用于虚拟存储或存储器保护。 – 1.指令中止模式(abt):指令预取终止时进入该模式。 – 2.数据访问中止模式(abt):当数据访问终止时进入该模式, 可用于虚拟存储及存储保护。 指令未定义模式(Undefined):支持硬件协处理器指令的软件 仿真 系统模式(System):运行具有特权的操作系统任务。

December 25, 2018

Neusoft Institute of Information

3.1 ARM处理器工作模式及寄存器介绍

3.1.1 ARM微处理器的工作状态 3.1.2 处理器模式 3.1.3 寄存器组织 3.1.4 异常

December 25, 2018

Neusoft Institute of Information

December 25, 2018

Neusoft Institute of Information

处理器启动时的模式转换图

管理模式 (Supervisor)

多种特权模式变化

用户程序的运行模式

复位后的缺 省模式

主要完成各 模式的堆栈 设置,注意 不要进入用 户模式一来自为用户 模式处理器模式

December 25, 2018

• • • 通用寄存器包括R0~R15,可以分为3类: 未分组寄存器R0~R7 分组寄存器R8~R14 程序计数器PC(R15)

December 25, 2018

Neusoft Institute of Information

① 未分组寄存器R0~R7

在所有的运行模式下,未分组寄存器都指 向同一个物理寄存器,它们未被系统用作特殊 的用途,因此,在中断或异常处理进行运行模 式转换时,由于不同的处理器运行模式均使用 相同的物理寄存器,可能会造成寄存器中数据 的破坏,这一点在进行程序设计时应引起注意。

December 25, 2018

Neusoft Institute of Information

对于R13、R14,每个寄存器对应6个不 同的物理寄存器,其中一个是用户模式与系统 模式共用,另外5个物理寄存器对应于其他5种 不同的运行模式。 采用以下记号来区分不同的物理寄存器: R13_<mode> R14_<mode> 其中,mode为以下几种模式之一:usr、 fiq、irq、svc、abt、und。

两种工作状态切换的情况: •在执行Thumb程序段时发生异常中断

在执行Thumb程序段时,处理器处于Thumb状 态,异常中断发生时,处理器自动进入ARM状态。

•程序从中断返回时

如果发生异常中断时,处理器处于Thumb状态, 则中断返回时,处理器会恢复为Thumb状态

•执行BX指令

使用BX指令时,程序可以实现跳转和处理器工作 状态转换。 BX Rn

December 25, 2018

Neusoft Institute of Information

② 分组寄存器R8~R14 对于分组寄存器,它们每一次所访问的物 理寄存器与处理器当前的运行模式有关。 对于R8~R12,每个寄存器对应两个不同 的物理寄存器,当使用fiq模式时,访问寄存器 R8_fiq~R12_fiq;当使用除fiq模式以外的其 他模式时,访问寄存器R8_usr~R12_usr。

December 25, 2018

Neusoft Institute of Information

寄存器R13在ARM指令中常用作堆栈指针, 但这只是一种习惯用法,用户也可使用其他的寄存 器作为堆栈指针。而在Thumb指令集中,某些指令 强制性的要求使用R13作为堆栈指针。 由于处理器的每种运行模式均有自己独立的物 理寄存器R13,在用户应用程序的初始化部分,一 般都要初始化每种模式下的R13,使其指向该运行 模式的栈空间。 这样,当程序的运行进入异常模式时,可以将 需要保护的寄存器放入R13所指向的堆栈,而当程 序从异常模式返回时,则从对应的堆栈中恢复,采 用这种方式可以保证异常发生后程序的正常执行。

December 25, 2018

Neusoft Institute of Information

ARM微处理器的运行模式可以通过软件改变,也 可以通过外部中断或异常处理改变。 大多数的应用程序运行在用户模式下,当处理器 运行在用户模式下时,某些被保护的系统资源是不能 被访问的。 除用户模式以外,其余的所有6种模式称为非用户 模式或特权模式(Privileged Modes); 其中除去用户模式和系统模式以外的5种又称为异 常模式(Exception Modes),常用于处理中断或异常, 以及需要访问受保护的系统资源等情况。

December 25, 2018

Neusoft Institute of Information

1. ARM状态下的寄存器组织

(1) 通用寄存器. (2) 状态寄存器 如图 3-2 所示

December 25, 2018

Neusoft Institute of Information

(1) 通用寄存器.