硬布线控制器控制的CPU设计

硬连线控制器CPU设计

目录目录 (i)摘要 (ii)Abstract (iii)第一章课题背景 (1)1.1 设计目的 (1)1.2 设计原理 (1)第二章设计简介及设计方案论述 (2)2.1 单元电路设计 (2)第三章详细设计 (4)3.1 芯片介绍 (4)3.2 指令系统结构及功能确定 (6)第四章设计结果及分析 (7)4.1 设计结果分析 (7)摘要硬连线控制器是由基本逻辑电路组成的,对指令中的操作码进行译码,并产生相应的时序控制信号的部件,又称组合逻辑控制器。

硬连线控制器由指令部件、地址部件、时序部件、操作控制部件和中断控制部件等组成(参见“中央处理器”条目中的控制器部分)。

其中操作控制部件用来产生各种操作控制命令,它根据指令要求和指令流程,按照一定顺序发出各种控制命令。

操作控制部件的输人信号有:指令译码器的输出信号、时序信号和运算结果标志状态信号等。

设计时根据指令流程、操作时间表得到各种操作控制命令的逻辑表达式,可采用由基本逻辑电路(与门、或门、与非门等)组成的逻辑网络来实现。

也可采用可编程逻辑器件PLD来实现。

PLD的“与”阵列及“或”阵列和操作控制命令的“与一或”逻辑表达式相对应,为设计组合逻辑控制器提供了一种理想器件。

80年代出现的通用阵列逻辑电路〔GAL与PAL(参见专用逻辑集成电路))具有与可编程逻辑器件PLD类似的结构,它不但可编程并且是可擦除的,为设计提供了更大的灵活性。

组合逻辑控制器的最大优点是速度快。

但因其线路复杂而且不规整,不便于调试、维护、修改,也不便于仿真不同的机器的指令集。

关键词:硬连线控制器;基本逻辑AbstractHard wired controller is composed of the basic logic circuits, decodes the instruction in the operation code, andproduce the corresponding sequential control signal components, also called combined logic controller. Hard wired controller by the instruction unit, address components, temporal parts, operation control part and the interrupt controlcomponents etc. (see "the controller part central processor" in entry). The operation control unit is used for generating various operation control command, it according to the instructions and instruction process, according to the order of the control commands issued. The operation of part of the control input signal: the instruction decoderoutput signals, timing signals and operation results indicating the status signal. The design according to theinstruction flow, operation schedule obtained logical expression of various operation control command, can beadopted by the basic logic circuits (and gate, or gate and NAND gate logic network composition etc.) to realize. Can also adopt the programmable logic device PLD to realize. PLD "and" and "or" array and array operation control command "and or" logical expression corresponding, providing an ideal device for the design of combinational logic controller. GAL and PAL generic array logic circuit (80 of the 1980s (see special logic integrated circuit)) withprogrammable logic device structure similar to the PLD, it is not only a programmable and erasable, provides more flexibility to design. The biggest advantage combinational logic controller is fast. But because of the circuit complex and irregular, not easy to debug, maintain, modify, also not easy for machines with different instruction set simulation.Keywords:Hard wired controller;basic logic第一章课题背景自1946年第一台电子计算机问世以来,计算机技术在元件器件、硬件系统结构、软件系统、应用等方面,均有惊人进步,现代计算机系统小到微型计算机和个人计算机,大到巨型计算机及其网络,形态、特性多种多样,已广泛用于科学计算、事务处理和过程控制,日益深入社会各个领域,对社会的进步产生深刻影响。

硬布线控制器(精)

由于采用同步工作方式,长指令和短指令对节拍时间的利用都是 一样的。这对短指令来讲,在时间的利用上是浪费的,因而也降 低了CPU的指令执行速度,影响到机器的速度指标。为了改变 这种情况,在设计短指令流程时可以跳过某些节拍。当然在这种 情况下,节拍信号发生器的电 路相应就要复杂一些。 节拍电位信号的产生电路与节拍脉冲产生电路十分类似,它 可以在节拍脉冲信号时序器的基础上产生,运行中以循环方式工 作,并与节拍脉冲保持同步。 3.微操作控制信号的产生 在微程序控制器中,微操作控制信号由微指令产生,并且可以重 复使用。在硬联线控制器中,某一微操作控制信号由布尔代数表 达式描述的输出函数产生。 设计微操作控制信号的方法和过程是,根据所有机器指令流程图 ,寻找出产生同一个微操作信号的所有条件,并与适当的节拍电 位和节拍脉冲组合,从而写出其布尔代数表达式并进行简化,然 后用门电路或可编程器件来实现。为了防止遗漏,设计时可按信 号出现在指令流程图中的先后次序书写,然后进行归纳和简化。 要特别注意控制信号是电位有效还是脉冲有效,如果是脉冲有效 ,必须加入节拍脉冲信 号进行相“与”。

显然,从指令流程图出发,就可以一个不漏地确定在指令周期中 各个时刻必须激活的所有操作控制信号 .例如,对引起一次主存 读操作的控制信号 C3来说,当节拍电位 M1=l,取指令时被激活; 而当节拍电位 M4=1,三条指令(LDA,ADD,AND)取操作数 时也被激活,此时指令译码器的 LDA,ADD,AND输出均为1, 因此 C3的逻辑表达式可由下式确定: C3=M1+M4(LDA+ADD+AND) 一般来说,还要考虑节拍脉冲和状态条件的约束 ,所以每一个控制 信号Cn=可以由以下形式的逻辑方程来确定 : Cn= (Mi·Tk·Bj· Im) 与微程序控制相比,组合逻辑控制的速度较快.其原因是微程序 控制中每条微指令都要从控存中读取一次,影响了速度,而组合 逻辑控制主要取决于电路延迟 .因此,近年来在某些超高速新型 计算机结构中,又选用了组合逻辑 . 2.指令执行流程 在用硬联线实现的操作控制器中,通常,时序产生器除了产生 节拍脉冲信号外,还应当产生节拍电位信号。因为在一个指令周 期中要顺序执行一系列微操作,需要设置若干节拍电位来定时。 例如前面提到的五条指令的指令周期,其指令流程可用下图来表 示。

中央处理器(2)-硬布线和流水线

(3)同种类型的指令所需要的控制信号大部分相同。 如:所有的算术逻辑运算指令仅在ALU的操作命令及 是否置状态位上不同,其他均完全相同。 (4)在确定指令操作码时,要认真做好分类。 例如,某机有128条指令,7位操作码(OP0~OP6),其中 有十六条算术逻辑运算指令,那么可以令这些指令的三 位操作码完全相等(例如OP0~OP2为001),而OP3~OP6 分别表示16条指令,设命令A是所有算术逻辑指令在cy2 周期中都需产生的,则: A=加法指令· cy2+减法指令· cy2+逻辑加指令 · cy2+…=(加法指令+减法指令+逻辑加指令+…)cy2= OP0· OP1· OP2· cy2

2.硬布线逻辑的实现途径

硬布线逻辑可用PLA(可编程逻辑阵列,地址与存储 区或均可编程)、PAL(可编程阵列逻辑,与可编程、 或不可编程、增加三态输出器件及记忆元件)、GAL (通用阵列逻辑,与或均可编程、输出逻辑宏单元) 或半定制电路门阵列(GA)来实现。

6.4.4 硬布线控制逻辑设计中的若干问题

6.4.3

硬布线控制器的组成

图6.26控制器总框图

1.程序计数器和中断控制逻辑

程序计数器的输入:有四种来源。 (1)开机后的reset信号,将PC置以初始地址; (2)顺序执行指令:由PC+1形成下一条指令地址; (3)转移:由ALU送来转移地址(通过ALU部件计 算有效地址) (4)外来中断请求信号:若CPU响应中断,则由 中断控制逻辑部件产生中断入口地址。

16

硬布线控制逻辑设计中的若干问题

1.指令操作码的代码分配 主要目标:简化控制部分的电路,减少延迟时间。 主要难点: (1)CISC不定长操作码的译码困难; (2)为后续升级系统预留指令位置困难。 2. 确定机器周期、节拍与主频 保证大部分指令在一个周期内完成,部分指令通过如 ‚ready”信号等方式来增加机器周期来完成。

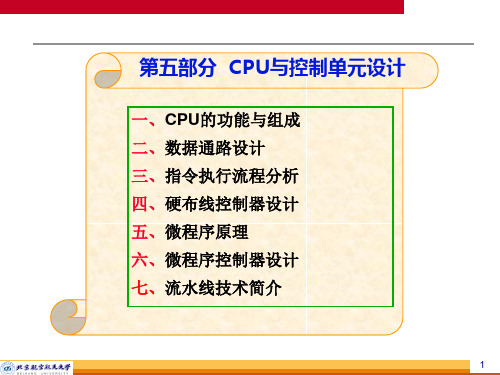

北航 计算机组成原理 第五部分:CPU控制单元设计

IBMDR、MDRDB

DBMER、MERIB

31

2.3 数据通路设计 (11.内部数据缓存)

控制总线(CB) 数据总线(DB) 地址总线(AB)

MAR 内部总线(IB)

MER

MDR

R0 R1 R2 R3

CPU内部

D ALU A

C

存储器

❖ ALU结果保存:增加寄 存器A

PC

❖ ALU数据输入缓存:增 加寄存器D

❖MIPS:百万指令每秒

➢MIPS:Million Instruction Per Second ➢不同指令集的MIPS比较没有实际意义 ➢即使同一台机器,用不同的测试程序测出来的MIPS值也可能不一样。

❖MFLOPS:百万浮点数操作每秒

➢MFLOPS: Million Floating point Operations Per Second ➢可以比较不同机器的浮点运算能力, 但有局限性 ➢MFLOPS不仅和机器有关, 也和所用测试程序有关 ➢MFLOPS与整数. 浮点操作的比例有关

移量(16位)

19

2.2 模型机的指令系统

❖指令类型

➢ 传送类指令:MOV指令,16位或32位指令 ▪ 4种传送类型:立即数寄存器,寄存器寄存器,寄存器 存储器,存储器寄存器

➢ 运算类指令:算术和逻辑运算, 16位或32位指令,RR型指令或 RS型指令,4种类型(以加法运算为例) ▪ 立即数 + 寄存器 寄存器 ▪ 寄存器 + 寄存器 寄存器 ▪ 寄存器 + 存储器 寄存器 ▪ 寄存器 + 寄存器 存储器

➢ 转移类指令 ▪ 条件/非条件转移、转子程序:32位指令,采用相对寻址 ▪ 子程序返回:16位指令

➢ 其它指令:16位指令

计算机组成原理实验 硬布线控制器

采用硬布线控制器的顺序模型处理机设计与调试报告

目录本报告包括以下内容:1. 数据通路图2. 硬布线控制器逻辑模块图3. 硬布线控制器指令周期流程图4. 控制模块HDL语言源程序/原理图(包含说明和注释)5. 测试波形图(以WRM为例)6. 设计说明书7. 设计与调试小结8. 本组成员实验心得数据通路图说明:数据通路是将双端口存储器模块和双端口通用寄存器模块连接在一起形成的。

双端口通用寄存器(RF)由一个ispLSI1016实现,功能相当于四个八位通用寄存器,用于保存参与运算的数据,运算后的结果也要送到RF中保存。

双端口寄存器堆模块的控制信号中,RS1、RS0用于选择从右端口读出的通用寄存器,RD1、RD0用于选择从左端口读出的通用寄存器。

而WR1、WR0用于选择写入的通用寄存器。

LDRi是写入控制信号,当LDRi=1时,数据总线DBUS上的数据在T3写入由WR1、WR0指定的通用寄存器。

左右端口分别与操作数暂存器DR1和DR2相连,RF的右端口通过三态门连接到数据总线DBUS上,因而RF中的数据可以直接通过右端口送到DBUS上。

DR1和DR2各由一片74LS273构成,用于暂存参与运算的数据。

ALU由两片74LS181构成,ALU的输出通过一个三态门发送到数据通路DBUS上。

双端口寄存器使用一片IDT7132(2048×8位),两个端口的地址输入A8-A10引脚接地,因此实际使用的存储容量为256字节。

左端口的数据输出端接在数据总线DBUS,右端口的数据输出接指令总线IBUS。

CEL#、LR/W#、OEL#控制左端口读写操作;CER#、RR/W#、OER#控制右端口读写操作。

CEL#为左端口片选信号,低电平有效;当CEL#=1时,禁止对左端口的读写操作;当LR/W#=0时,左端口进行读写。

OEL#的作用等同于三态门,当OEL#=0时,允许左端口读出的数据送到数据总线DBUS上;当OEL#=1时,禁止左端口的数据放到DBUS 上。

因此将OEL#写作RAM-BUS#。

控制器的功能和工作原理

控制器的功能和⼯作原理⽬录控制器的结构和功能控制单元的输⼊和输出硬布线控制器操作码译码器:把⼀个编码⼀种功能的形式转换成⼀根线对应⼀个功能关于机器周期:机器周期可看作所有指令执⾏过程中的⼀个基准时间。

通常以存取周期作为基准时间,即机器周期。

在存储字长等于指令字长的前提下,取指周期也可看作机器周期。

CPU的控制⽅式CPU的控制⽅式:产⽣不同微操作命令序列所⽤的时序控制⽅式1.同步控制⽅式:整个系统的所有控制信号均来⾃统⼀的时钟信号。

通常以最长的微操作序列和最繁琐的微操作作为标准(⽤最久的那个),采取完全统⼀的、具有相同时间间隔和相同数⽬的节拍作为机器周期来运⾏不同的指令。

同步控制⽅式的有点是控制电路简单,缺点是运⾏速度较慢。

2.异步控制⽅式:异步控制⽅式不存在基准时标信号。

各部件按⾃⾝固有的速度⼯作,通过应答⽅式进⾏联络。

异步控制⽅式的优点是运⾏速度快,缺点是控制电路⽐较复杂。

3.联合控制⽅式:对各种不同的指令的微操作实⾏⼤部分采⽤同步控制、⼩部分采⽤异步控制的办法。

安排微操作时序的原则原则⼀:微操作的先后顺序不得随意更改原则⼆:被控对象不同的微操作,尽量安排在同⼀个节拍内完成原则三:占⽤时间较短的微操作,尽量安排在⼀个节拍内完成,并允许有先后顺序取值周期两个微操作占⽤时间较短,根据原则三安排在同⼀个节拍间址周期执⾏周期中断周期中断周期的三个任务:1. 保存断点2. 形成中断服务程序的⼊⼝地址3. 关中断电路设计组合逻辑设计设计步骤:1. 列出操作时间表2. 写出微操作命令的最简表达式3. 画出逻辑图列出操作时间表微操作信号综合画出逻辑图微操作序列是必会的硬布线⼯作原理:微操作控制信号由组合逻辑电路根据当前的指令码、状态和时许,即使产⽣微程序微程序⼯作原理:事先把微操作控制信号存储在⼀个专门的存储器(控制存储器)中,将每⼀条机器指令编写成⼀个微程序,这些微程序可以存到⼀个控制存储器中,⽤寻址⽤户程序机器指令的办法来寻址每个微程序中的微指令。

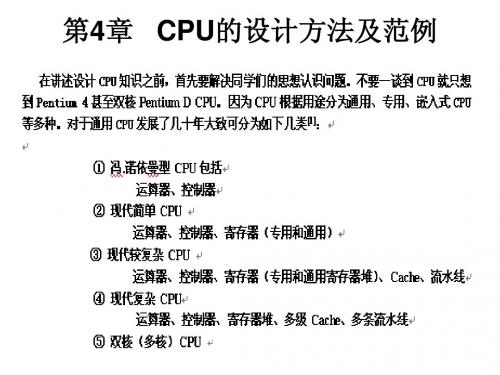

第4章 CPU的设计方法及范例

非常简单CPU不具有应用价值,仅用来说明 设计过程。不过,只要我们能正确设计出只有4条 指令的CPU,就可以设计出拥有40条指令的CPU, 甚至更多·· ·。难道这样还有怀疑吗?当然不能期 望马上就有创新,但这个CPU是拥有自主知识产 权的。或者有些同学会这样想,我以后并非从事 硬件的工作,更不可能从事设计CPU的专业,我 也相信这是事实。但是,这绝对有利于我们掌握 计算机的工作原理,也有利于从事各种软、硬件 开发和计算机科学等领域的研究、教学工作。

图4.9 通用CPU的状态图

其实CPU就是一个复杂的有限状态机 【冯· 诺依曼机的理论是基于图灵(Turing) 机理论的,而图灵机就是一个有限状态 机】。通过确定状态及其对应的微操作, 就可明确CPU为了取数据(或指令),指 令译码和执行指令集中每一条指令所必须 要完成的步骤。 问题:什么是图灵机理论?

1966年美国计算机协会设立“图灵奖”,被视为计算机科学界的最高荣誉

它的“纸带”相当于作业薄,读写头相当于人的眼 睛、手、笔,对于输入集{x1,x2,…xn},r(i, 0)= xi,i= 1,2,..n相当于“抄题”,而映射f 的读写变换相当于人脑判断确定下一步的行为且 指挥手和笔如何去动作和书写。它高度概括地回 答了什么是运算,不但为计算复杂度理论提供了 研究工具,而且为20世纪50年代计算机的设计提 供了思想基础,即Moore机和Mealy机。【注:当 出现状态Sy或Sn时,即得到了Turing 机的运算结 论Yes或No,这时即S(t)∈{ Sy,Sn }时停机】

二、建立数据通路的原理和方法

1.存贮器数据通路的原理

2.CPU内部的数据通路(两种不同的方案)

三、CPU内部寄存器控制信号的定义和确定方法

2.决定每个部件应完成的功能(详见图4.14)

计算机组成原理硬布线控制器课件

的任务处理。

03

人工智能与控制器的融合

随着人工智能技术的不断发展,未来硬布线控制器将与人工智能技术深

度融合。通过集成人工智能算法,控制器能够更好地处理复杂的任务,

提高系统的智能化水平。

THANKS

感谢您的观看

执行速度

硬布线控制器由于采用硬件逻辑 电路实现控制指令的执行,因此 在执行速度上通常比微程序控制

器更快。

设计灵活性

微程序控制器通过微程序实现控 制指令的执行,设计灵活性较高,

而硬布线控制器则相对固定,不 易更改。

实现复杂度

硬布线控制器的实现复杂度相对 较低,因为其控制逻辑通过硬件 电路实现,而微程序控制器则需 要编写和维护微程序代码,实现

硬布线控制器的行为是确定的, 不受软件行为的影响,因此具

有很好的可预测性。

高效能

硬布线控制器能够高效地处理 各种复杂的控制信号,使得计 算机系统能够高效地运行。

缺点

灵活性差

硬布线控制器的行为在设计和 制造时就已经确定,不易更改,

因此灵活性较差。

维护困难

硬布线控制器的设计和制造过 程较为复杂,一旦出现故障, 维护和修复的难度较大。

硬布线控制器的作用

01

02

03

控制指令执行

硬布线控制器负责控制指 令的执行顺序,确保指令 按照正确的顺序和时间进 行。

时序产生

硬布线控制器负责产生计 算机系统所需的时序信号, 如时钟信号等。

输入输出控制

硬布线控制器还负责控制 计算机系统的输入输出操 作,如数据读写等。

硬布线控制器与微程序控制器的比较

状态寄存器

功能

存储机器的当前状态,如中断状态、 操作状态等。

特点

硬布线控制器设计与调试 课程设计..

设计题目:硬布线控制器设计与调试课程名称:计算机组成原理课程设计任课教师:黄岚班级:计算机141学号:1408010112姓名:目录一、课程设计简述: (3)1.教学目的: (3)2.课设任务: (3)3.实验设备简介: (3)3.1、TEC4-A计算机组成原理实验系统[1] (3)3.2、万用表 (5)3.3、PC机 (5)二、总体设计思路: (5)1.指令系统: (5)2.数据通路: (6)3.硬布线控制器的设计原理: (7)三、设计与调试方案: (7)1.设计步骤: (7)1.1.根据数据通路得出指令周期流程图 (7)1.2.根据指令流程图将微信号的输出条件列出: (10)1.3.根据微信号的输出条件写用ABEL语言表示的布尔表达式: (11)2.调试步骤: (14)四、验证性实验: (14)1.课程设计要求的基础实验: (14)预置寄存器及存储单元内容: (14)程序代码: (14)执行结果: (15)2.自备的检验性实验: (15)预置寄存器及存储单元内容: (15)程序代码: (15)执行结果: (15)五、课程设计中遇到的问题及体会: (16)参考文献: (16)硬布线控制器的设计与调试课程设计报告一、课程设计简述:1.教学目的:1)融会贯通计算机组成原理课程和计算机系统结构课程的内容,通过知识的综合运用,加深对计算机系统各模块的工作原理及相互联系的认识,特别是对硬布线控制器的认识。

2)学习运用ISP(在系统编程)技术进行设计和调试的基本步骤和方法,熟悉集成开发软件中设计调试工具的使用,体会ISP技术相对于传统开发技术的优点。

3)培养科学研究的独立工作能力,取得工程设计与组装调试的实践经验。

2.课设任务:1)按给定的数据格式和指令系统,在所提供的器件范围内,设计一台硬布线控制器控制的模型计算机。

2)根据设计图纸,在通用实验台上进行组装,并调试成功。

3)在组装调试成功的基础上,整理出设计图纸和其他文件,包括:A.总框图(数据通路图);B.硬布线控制器逻辑模块图;C.模块ABEL语言源程序(如果有的话);D.硬布线控制流程图;E.元件排列图;F.设计说明书;G.调试小结。

6.6 硬布线控制器

河南科技大学

硬布线控制器

明德

博学

日新

笃行

一、硬布线控制器的设计思想

采用组合逻辑的思想,把微操作信号发生器看作一个产生专门固定时序控 制信号的逻辑电路,该逻辑电路是按照数字逻辑电路的设计原则设计出的一种 由门电路和触发器构成的复杂的树形网络 ,故称为硬布线控制器。

河南科技大学

硬布线控制器

二、硬布线控制器的基本结构

微 操 3. READ=T0+T3·(STR+JZ)

作 信

4.

Y←0=T0

号 的

5.

C0←1=T0

逻 辑

6.

ADD=T0+T5 ·ADD

组 合

7.

ZIN=T0+T5(ADD+AND)

8. ZOUT=T2+T6(ADD+AND)

9. PCIN=T2+T6 ·Z ·JZ

明德

博学

日新

笃行

10. MDROUT=T1+T4(ADD+AND)

T1

MDROUT,IRIN

T2

ZOUT,PCIN

T3

ADDROUT,MARIN,READ

T4

MDROUT,RIIN

Pcout=T0

T3

ADDROUT,MARIN

T4

RIOUT,MDRIN,WRITE

T3

ADDROUT,MARIN,READ

T4

MDROUT,YIN

MARIN =T0+T3 ·JZ

T5

RIOUT,ADD,ZIN

河南科技大学

硬布线控制器 画出逻辑电路图

RIIN =LD ·T4+ T6·(ADD+AND)

实验07 硬布线控制器实验

实验七硬布线控制器实验一、实验目的1、通过实验学习利用VHDL语言进行有限状态机的设计。

2、通过实验了解硬布线控制器的基本工作原理。

二、实验原理1、硬布线控制器本质上是一种由门电路和触发器构成的复杂树形网络,它将输入逻辑信号转换成一组输出逻辑信号,即控制信号。

硬布线控制器的输入信号有:指令寄存器的输出、时序信号和运算结果标志状态信号等;输出的信号就是各个部件需要的各种微操作信号。

2、硬布线控制器的设计思想是:在硬布线控制器中,操作控制器发出的各种控制信号是时间因素和空间因素的函数。

各个操作定时的控制构成了操作控制信号的时间特征,而各种不同部件的操作所需要的不同操作信号则构成了操作控制信号的空间特征。

硬布线控制器就是时间信号和操作信号的组合,产生具有定时特点的控制信号。

3、本实验中用到的机器指令如下:图1 设计指令格式4、根据指令要求,得出用时钟进行驱动的状态机描述,即得出其有限状态机,如图2所示。

S0:空操作,系统复位后的状态S1:PC->AR,PC+1S2:MEM->BUS,BUS->IRS3:R0->BUS,BUS->AS4:R0->BUS,BUS->BS5:A+B->BUS,BUS->R0S6:IN->BUS,BUS->R0S7:R0->BUS,BUS->OUTS8:空操作S9:PC->AR,PC+1S10:MEM->BUS,BUS->PC图2 有限状态机描述三、实验步骤1、建立一个Quartus II工程命名为:Con,并在工程中新建一个VHD文件,与工程同名:Con.vhd2、利用VHDL语言设计了控制器的有限状态机。

其代码如下:LIBRARY IEEE;USE IEEE.std_logic_1164.ALL;ENTITY CONTROLLER ISPORT(RESET : IN STD_LOGIC;T1 : IN STD_LOGIC;INS : IN STD_LOGIC_VECTOR(7 DOWNTO 0);CTRL : OUT STD_LOGIC_VECTOR(16 DOWNTO 0));END CONTROLLER;ARCHITECTURE CONTROLLER_ARCH OF CONTROLLER ISTYPE STATE IS (S10, S9, S8, S7, S6, S5, S4, S3, S2, S1, S0);SIGNAL CUFSM: STA TE;--CTRL:WR,RD,IOM,S3,S2,S1,S0,LDA,LDB,LOAD,LDAR,LDIR,ALU_B,R0_B,LDR0,PC_B,LDPC BEGINPROCESS (T1, RESET, INS)BEGINIF RESET = '0' THENCTRL <= "00000000010011010"; --NOPCUFSM <= S0;ELSIF T1'EVENT AND T1 = '1' THENCASE CUFSM ISWHEN S0 =>CTRL <= "00000000011011001"; --PC->AR,PC+1CUFSM <= S1;WHEN S1 =>CTRL <= "01000000010111010"; --MEM->BUS,BUS->IRCUFSM <= S2;WHEN S2 =>IF INS = "00000000" THEN --ADD INSCTRL <= "00000001010010010"; --R0->BUS,BUS->ACUFSM <= S3;ELSIF INS = "00100000" THEN -- IN INSCTRL <= "01100000010011110"; --IN->BUS,BUS->R0CUFSM <= S6;ELSIF INS = "00110000" THEN -- OUT INSCTRL <= "10100000010010010"; --R0->BUS,BUS->OUTCUFSM <= S7;ELSIF INS = "01010000" THEN -- HLT INSCTRL <= "00000000010011010"; --NOPCUFSM <= S8;ELSIF INS = "11100000" THEN -- JMP INSCTRL <= "00000000011011001"; --PC->AR,PC+1CUFSM <= S9;ELSE -- INV ALID INSCTRL <= "00000000011011001"; --PC->AR,PC+1CUFSM <= S1;END IF;WHEN S3 =>CTRL <= "00000000110010010"; --R0->BUS,BUS->BCUFSM <= S4;WHEN S4 =>CTRL <= "00010010010001110"; --A+B->BUS,BUS->R0CUFSM <= S5;WHEN S5 =>CTRL <= "00000000011011001"; --PC->AR,PC+1CUFSM <= S1;WHEN S6 =>CTRL <= "00000000011011001"; --PC->AR,PC+1CUFSM <= S1;WHEN S7 =>CTRL <= "00000000011011001"; --PC->AR,PC+1CUFSM <= S1;WHEN S8 =>CTRL <= "00000000010011010"; --NOPCUFSM <= S8;WHEN S9 =>CTRL <= "01000000000011011"; --MEM->BUS,BUS->PCCUFSM <= S10;WHEN S10 =>CTRL <= "00000000011011001"; --PC->AR,PC+1CUFSM <= S1;END CASE;END IF;END PROCESS;END CONTROLLER_ARCH ;3、对工程已经编译,将生成的Con.sof文件进行JTAG下载就可以了。

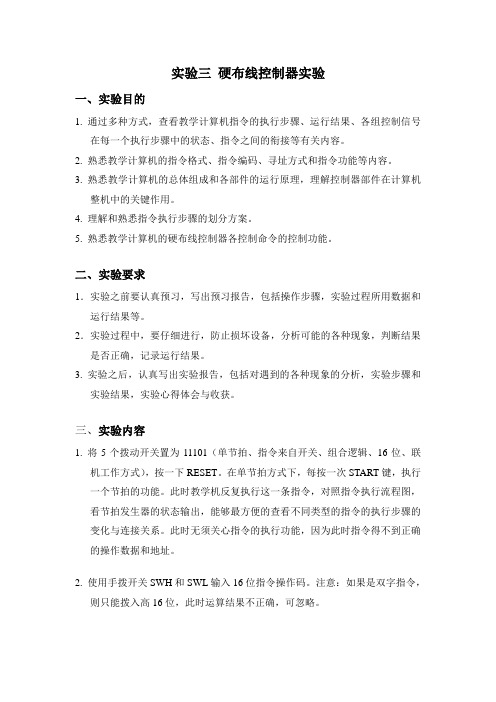

计算机组成原理 实验三 硬布线控制器实验

实验三硬布线控制器实验一、实验目的1. 通过多种方式,查看教学计算机指令的执行步骤、运行结果、各组控制信号在每一个执行步骤中的状态、指令之间的衔接等有关内容。

2. 熟悉教学计算机的指令格式、指令编码、寻址方式和指令功能等内容。

3. 熟悉教学计算机的总体组成和各部件的运行原理,理解控制器部件在计算机整机中的关键作用。

4. 理解和熟悉指令执行步骤的划分方案。

5. 熟悉教学计算机的硬布线控制器各控制命令的控制功能。

二、实验要求1.实验之前要认真预习,写出预习报告,包括操作步骤,实验过程所用数据和运行结果等。

2.实验过程中,要仔细进行,防止损坏设备,分析可能的各种现象,判断结果是否正确,记录运行结果。

3. 实验之后,认真写出实验报告,包括对遇到的各种现象的分析,实验步骤和实验结果,实验心得体会与收获。

三、实验内容1. 将5个拨动开关置为11101(单节拍、指令来自开关、组合逻辑、16位、联机工作方式),按一下RESET。

在单节拍方式下,每按一次START键,执行一个节拍的功能。

此时教学机反复执行这一条指令,对照指令执行流程图,看节拍发生器的状态输出,能够最方便的查看不同类型的指令的执行步骤的变化与连接关系。

此时无须关心指令的执行功能,因为此时指令得不到正确的操作数据和地址。

2. 使用手拨开关SWH和SWL输入16位指令操作码。

注意:如果是双字指令,则只能拨入高16位,此时运算结果不正确,可忽略。

拍。

例如:使用手拨开关SWH和SWL输入MVRD指令的操作码88H(为B组指令),先按RESET键,再依次按START键,看到节拍发生器的状态输出为:0000-0010-0110-0100。

操作序列1:请把ADD、PUSH、LDRA、CALA指令通过开关送给控制器,利用教学机把各自节拍流程找出来,并写在下表中。

操作序列2:请自行从A、B、C、D四组中各选择若干条指令通过开关送给控制器,利用教学机把各自节拍流程找出来,并写在下表中,表格行数可自行增加。

硬布线控制器的设计

课 程 设 计课程设计任务书 2015~2016学年第 1 学期学生姓名: 张祥专业班级: 计科二班指导教师: 杨斐 工作部门: 计算机学院一、课程设计题目 硬布线控制器的设计二、课程设计内容(含技术指标)1.利用QUARTUS 软件设计一个小型CPU 中的硬布线控制器。

总体框图参考下图:操作控制信号格式:执行单元....总体框图如下:(不必设计)教 学 院 计算机学院课程名称 计算机组成原理课程设计题 目 硬布线控制器的设计专 业 计算机科学与技术班 级 二班 姓 名 同组人员 指导教师 杨 斐 2015 年 1 月 5 日该CPU的指令系统包含8条机器指令,分别为ADD、SUB、INC 、AND、OR 、2. 写出每一个操作控制信号的逻辑代数表达式,化简并设计电路。

3. 每输入一条机器指令代码打入IR中,由硬布线控制器得到14位操作控制信号,在发光二极管上显示每一位的值。

三、进度安排1.2015年12月14日,课题讲解,布置任务2.2015年12月15-17日,分析、讨论、进行各子模块的设计设计3.2015年12月18-24日,完成各模块联调,进行测试4.2015年12月25日,成果验收,进行答辩四、基本要求1.能够熟练掌握计算机中硬布线控制器的工作原理及特点;2.掌握硬件描述语言VHDL及原理图设计方法;3.熟练掌握Quartus II软件平台;4.各小组按模块分工,每人独立完成自己负责的模块;5.合作完成最终的硬件下载及调试;6.独立撰写符合要求的课程设计报告。

目录一、概述 ........................................................... 错误!未定义书签。

1.1课程设计的目的 .................................... 错误!未定义书签。

1.2课程设计的要求 .................................... 错误!未定义书签。

硬布线控制器控制的CPU设计

硬布线控制器控制的CPU设计&硬布线控制器控制的CPU设计步骤:1、确定CPU用途;2、设计指令集,同时,设计指令访问寄存器;3、设计CPU状态图;4、建立数据通路;5、设计控制器。

&设计过程:一.确定CPU用途:CPU指令执行包括三个阶段:1、取指令阶段:从存储器取出一条指令;2、指令译码阶段:对取出的指令进行译码,即确定取到的指令是何种指令,然后转移到该种指令的执行阶段;3、指令执阶段:执行指令。

指令执行完毕,又转移到下一条指令的取指令阶段,开始新一轮的循环。

CPU状态图二设计指令集:执行内存有32个存储单元,每个存储单元8位(一个字节);CPU有5根地址线,即A4、…、A0,8根三.指令格式指令格式专用寄存器:1、程序计数器PC:5位;2、地址寄存器AR:5位,接地址总线A[4..0];3、数据寄存器DR:8位,接数据总线D[7..0];4、指令寄存器IR:8位;5、程序状态字寄存器PSW:只有进位C一个标志值,可用C代表PSW。

三.设计CPU状态图5.3.4 取指令和译码周期5.3.5 取指令和指令执行过程四.建立数据通路数据通路:数据在各功能部件之间传送路径。

有两种数据通路设计方案:1、专用数据通路方式:在需要传送数据的部件之间创建一条专门的直接通路 。

特点:数据传输性能高,但硬件设计量大。

2、内部总线方式:所有寄存器的输入端和输出端都连接到一条或多条公共通路上。

特点:结构简单,但可能存在冲突现象控制信号说明ARLD :AR 锁存信号 PCLD :PC 锁存信号PC+1:PC 自加1控制信号 DRLD :DR 锁存信号 ACLD :AC 锁存信号ALU(-):ALU 减法触发信号 IRLD :IR 锁存信号PCBUS :PC 三态输出控制信号 DRBUS :DR 三态输出控制信号 ACBUS :AC 三态输出控制信号 IRBUS :IR 三态输出控制信号MBUS :存储器三态输出控制信号 RD :存储器读信号 WR :存储器写信号寄存器及总线设计CPU 状态及其控制信号T 4T T五.硬布线控制器结构方框图硬布线控制器设计步骤:1、确定指令系统,包括指令格式、功能和寻址方式;2、根据指令系统的要求,确定数据通路结构及时序系统构成;3、分析每条指令的执行过程,写出对应的微操作系列;4、综合每个操作控制信号的逻辑表达式,化简和优化;5、用逻辑电路实现。

计算机组成原理课程设计—硬布线控制器的设计与实现

硬布线控制器的设计与调试教学目的、任务与实验设备教学目的熟练掌握实验5和硬布线控制器的组成原理与应用。

复习和应用数据通路及逻辑表达式。

学习运用ISP (在系统编程)技术进行设计和调试的基本步骤和方法,熟悉集成开发软件中设计调试工具的使用,体会ISP 技术相对于传统开发技术的优点。

教学任务按给定的数据格式和指令系统,在所提供的器件范围内,设计一台硬布线控制器控制的模型计算机。

根据设计图纸,在通用实验台上进行组装,并调试成功。

在组装调试成功的基础上,整理出设计图纸和其他文件。

实验设备C1微操作控制信号结果反馈信息CnSKIPTJ ·····硬布线控制器(组合逻辑网络)ispLSI1032E-70LJ84指令译码模块节拍电位/节拍脉冲发生器指令寄存器W1W4 T1 T1启动停止时钟复位B1 Bn硬布线控制器结构方框图TEC -4计算机组成原理实验系统一台直流万用表一只集成电路建议使用ISP 芯片(一片ispLSI1032)。

采用ISP 器件,则需要一台PC 机运行设计自动化软件(例如ispEXPERT)作设计、编程和下载使用。

总体设计思路(描述指令系统,给数据通路)采用与模型计算机相同的指令系统,即12条机器指令。

实验设计中采用该指令系统的子集:去掉中断指令后的3条机器指令,只保留9条指令。

采用的数据通路和微程序控制器方案相同。

·数据通路图和数据通路控制信号ALUDR1DR2MUX1MUX2RFERM1M2S2S1S0T4RS1、RS0WR1、WR0RD1、RD0WRD(T2)SW_BUS#LDER(T4)AR2MUX3AR1RAM数据端口指令端口CERCEL#LRW(T3)LDAR2(T2)M3LDAR1(T4)AR1_INCIARIAR_BUS#LDIARPCALU2R4MUX4LDR4(T2)M4IRLDIR(T4)RS1、RS0控制器INSDBUSC控制信LDPC(T4)RD1、RD0WR1、WR0..LDDR2(T3)DBUSDBUSLDDR1(T3)RS_BUS#ALU_BUSSW0— SW7B 端口A 端口PC_ADDA 端口B 端口PC_INC控制器的设计思路硬布线控制器能够实现控制功能,关键在于它的组合逻辑译码电路。

单周期和多周期专用CPU设计【开题报告】

毕业设计开题报告计算机科学与技术单周期和多周期专用CPU设计一、选题的背景与意义随着信息技术的迅猛发展,计算机技术也在不断革新,而计算机已经成为了人们日常生活中不断或缺的一个组成部分,在经济全球化和网络普及化的今天,计算机对于人们的影响也越来越大,而作为计算机的核心设备,CPU也在不停地更新换代并越来越受到人们的关注和重视,多线程,多核心理论的产生,使得CPU的革新速度又得到进一步的提升。

本课题旨在通过对硬布线控制器知识的分析,对单、多周期CPU设计进行探究,熟练掌握CPU内部线路,实现其功能。

中央处理器(Central Processing Unit,CPU),是电子计算机的主要设备之一。

其功能主要是解释计算机指令以及处理计算机软件中的数据。

所谓的计算机的可编程性主要是指对CPU的编程。

CPU,往往采用硬布线逻辑实现。

硬布线控制器又称组合逻辑控制器,它将控制部件做成产生专门固定时序控制信号的逻辑电路,产生各种控制信号。

硬布线控制器又称组合逻辑控制器,以使用最少元件和取得最高操作速度为设计目标。

硬布线控制的功能由逻辑门组合实现。

硬布线控制逻辑主要取决于电路延时,因而在超高速机器中,对影响速度的关键部分如核心部件CPU,往往采用硬布线逻辑实现。

近年来,在一些新型计算机系统中,例如,RISC(精简指令系统计算机)中,一般都选用硬布线逻辑电路。

,与微程序控制器相比,硬布线控制的速度较快。

其原因是微程序控制中每条微指令都要从控制存储器中读取一次,影响了速度,而硬布线控制主要取决于电路延迟。

另外,随着新一代机器及VLSI技术的发展与不断进步,硬布线逻辑设计思想又得到了重视,现代新型计算机体系结构RISC 中多采用硬布线控制逻辑。

另外我们还需要了解EDA技术,它是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

利用EDA 工具,可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬布线控制器控制的CPU设计

&硬布线控制器控制的CPU设计步骤:

1、确定CPU用途;

2、设计指令集,同时,设计指令访问寄存器;

3、设计CPU状态图;

4、建立数据通路;

5、设计控制器。

&设计过程:

一.确定CPU用途:

CPU指令执行包括三个阶段:

1、取指令阶段:从存储器取出一条指令;

2、指令译码阶段:对取出的指令进行译码,即确定取到的指令是何种指令,然后转移到该种指令的执行阶段;

3、指令执阶段:执行指令。

指令执行完毕,又转移到下一条指令的取指令阶段,开始新一轮的循环。

CPU状态图二设计指令集:

执行

内存有32个存储单元,每个存储单元8位(一个字节);CPU有5根地址线,即A4、…、A0,8根

三.指令格式

指令格式

专用寄存器:

1、程序计数器PC:5位;

2、地址寄存器AR:5位,接地址总线A[4..0];

3、数据寄存器DR:8位,接数据总线D[7..0];

4、指令寄存器IR:8位;

5、程序状态字寄存器PSW:只有进位C一个标志值,可用C代表PSW。

三.设计CPU状态图

5.3.4 取指令和译码周期

5.3.5 取指令和指令执行过程

四.建立数据通路

数据通路:数据在各功能部件之间传送路径。

有两种数据通路设计方案:

1、专用数据通路方式:在需要传送数据的部件之间创建一条专门的直接通路 。

特点:数据传输性能高,但硬件设计量大。

2、内部总线方式:所有寄存器的输入端和输出端都连接到一条或多条公共通路上。

特点:结构简单,但可能存在冲突现象

控制信号说明

ARLD :AR 锁存信号 PCLD :PC 锁存信号

PC+1:PC 自加1控制信号 DRLD :DR 锁存信号 ACLD :AC 锁存信号

ALU(-):ALU 减法触发信号 IRLD :IR 锁存信号

PCBUS :PC 三态输出控制信号 DRBUS :DR 三态输出控制信号 ACBUS :AC 三态输出控制信号 IRBUS :IR 三态输出控制信号

MBUS :存储器三态输出控制信号 RD :存储器读信号 WR :存储器写信号

寄存器及总线设计

CPU 状态及其控制信号

T 4T T

五.

硬布线控制器结构方框图

硬布线控制器设计步骤:

1、确定指令系统,包括指令格式、功能和寻址方式;

2、根据指令系统的要求,确定数据通路结构及时序系统构成;

3、分析每条指令的执行过程,写出对应的微操作系列;

4、综合每个操作控制信号的逻辑表达式,化简和优化;

5、用逻辑电路实现。

操作控制信号

控制信号时间表

各控制信号逻辑表达式:

<1>.PCBUS=T1 < 2>.ARLD=T1+(SUB+LOAD+STORE)·T4 <3>.RD=T2+(SUB+LOAD)·T5 <4>.MBUS=T2+(SUB+LOAD)·T5

<5>.DRLD=T2+(SUB+LOAD)·T5 <6>.PC+1=T2

<7>.DRBUS=T3+(LOAD+STORE)·T6 <8>.IRLD= T3

<9>.IRBUS=T4 <10>.PCLD=(JMPC·C+JMP)·T4

<11>.ALU(+)=SUB·T6 <12>.ACLD=( SUB+LOAD)·T6

<13>.ACBUS=STORE·T5 <14>.aWR=STORE·T6

操作控制信号的逻辑实现图。