ISE约束UCF编辑的操作介绍

ISE约束

ISE约束--UCF编辑的入门介绍[zz]From: /yq000cn/blog/70-01/185475_6dce2.html摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。

Xilinx FPGA设计约束的分类Xilinx定义了如下几种约束类型:• “Attributes and Constraints”• “CPLD Fitter”• “Grouping Constraints”• “Logical Constraints”• “Physical Constraints”• “Mapping Directives”• “Placement Constraints”• “Routing Directives”• “Synthesis Constraints”• “Timing Constraints”• “Configuration Constraints”通过编译UCF(user constraints file)文件可以完成上述的功能。

还是用实例来讲UCF的语法是如何的。

图1 RTL Schematic图1 是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA管脚。

1: NET "pin_sysclk_i" LOC = AD12 | TNM_NET = pin_sysclk_i;2: TIMESPEC TS_pin_sysclk_i = PERIOD "pin_sysclk_i" 15 ns HIGH 50 %; 3:#4: NET "pin_plx_lreset_n_i" LOC = B18;5:#6: NET "pin_plx_lhold_i" LOC = C17;7: NET "pin_plx_lholda_o" LOC = D17 | SLEW = FAST;8:#9: NET "pin_plx_ads_n_i" LOC = E18;10:NET "pin_plx_ads_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 11:#12: NET "pin_plx_lw_r_n_i" LOC = E9;13:NET "pin_plx_lw_r_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 14:#15: NET "pin_plx_blast_n_i" LOC = D18;16:NET "pin_plx_blast_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 17:#18: NET "pin_plx_lad_io<0>" LOC = AD13 | SLEW = FAST | TNM = LAD;19: NET "pin_plx_lad_io<1>" LOC = AC13 | SLEW = FAST | TNM = LAD;20: NET "pin_plx_lad_io<2>" LOC = AC15 | SLEW = FAST | TNM = LAD;21: NET "pin_plx_lad_io<3>" LOC = AC16 | SLEW = FAST | TNM = LAD;22: NET "pin_plx_lad_io<4>" LOC = AA11 | SLEW = FAST | TNM = LAD;23: NET "pin_plx_lad_io<5>" LOC = AA12 | SLEW = FAST | TNM = LAD;24: NET "pin_plx_lad_io<6>" LOC = AD14 | SLEW = FAST | TNM = LAD;25: NET "pin_plx_lad_io<7>" LOC = AC14 | SLEW = FAST | TNM = LAD;26: NET "pin_plx_lad_io<8>" LOC = AA13 | SLEW = FAST | TNM = LAD;27: NET "pin_plx_lad_io<9>" LOC = AB13 | SLEW = FAST | TNM = LAD;28: NET "pin_plx_lad_io<10>" LOC = AA15 | SLEW = FAST | TNM = LAD; 29: NET "pin_plx_lad_io<11>" LOC = AA16 | SLEW = FAST | TNM = LAD; 30: NET "pin_plx_lad_io<12>" LOC = AC11 | SLEW = FAST | TNM = LAD; 31: NET "pin_plx_lad_io<13>" LOC = AC12 | SLEW = FAST | TNM = LAD; 32: NET "pin_plx_lad_io<14>" LOC = AB14 | SLEW = FAST | TNM = LAD; 33: NET "pin_plx_lad_io<15>" LOC = AA14 | SLEW = FAST | TNM = LAD; 34: NET "pin_plx_lad_io<16>" LOC = D12 | SLEW = FAST | TNM = LAD;35: NET "pin_plx_lad_io<17>" LOC = E13 | SLEW = FAST | TNM = LAD;36: NET "pin_plx_lad_io<18>" LOC = C16 | SLEW = FAST | TNM = LAD;37: NET "pin_plx_lad_io<19>" LOC = D16 | SLEW = FAST | TNM = LAD;38: NET "pin_plx_lad_io<20>" LOC = D11 | SLEW = FAST | TNM = LAD;39: NET "pin_plx_lad_io<21>" LOC = C11 | SLEW = FAST | TNM = LAD; 40: NET "pin_plx_lad_io<22>" LOC = E14 | SLEW = FAST | TNM = LAD; 41: NET "pin_plx_lad_io<23>" LOC = D15 | SLEW = FAST | TNM = LAD; 42: NET "pin_plx_lad_io<24>" LOC = D13 | SLEW = FAST | TNM = LAD; 43: NET "pin_plx_lad_io<25>" LOC = D14 | SLEW = FAST | TNM = LAD; 44: NET "pin_plx_lad_io<26>" LOC = F15 | SLEW = FAST | TNM = LAD; 45: NET "pin_plx_lad_io<27>" LOC = F16 | SLEW = FAST | TNM = LAD; 46: NET "pin_plx_lad_io<28>" LOC = F11 | SLEW = FAST | TNM = LAD; 47: NET "pin_plx_lad_io<29>" LOC = F12 | SLEW = FAST | TNM = LAD; 48: NET "pin_plx_lad_io<30>" LOC = F13 | SLEW = FAST | TNM = LAD; 49: NET "pin_plx_lad_io<31>" LOC = F14 | SLEW = FAST | TNM = LAD; 50: TIMEGRP "LAD" OFFSET = IN 6.4 ns AFTER "pin_sysclk_i" HIGH;51: TIMEGRP "LAD" OFFSET = OUT 3.1 ns BEFORE "pin_sysclk_i" HIGH; 52:#53: NET "pin_plx_ready_n_o" LOC = F18 | SLEW = FAST;54: NET "pin_plx_ready_n_o" OFFSET = OUT 4.2 ns BEFORE "pin_sysclk_i" HIGH;55:#56: NET "pin_plx_bterm_n_o" LOC = D10 | SLEW = FAST;57: NET "pin_plx_bterm_n_o" OFFSET = OUT 4.2 ns BEFORE "pin_sysclk_i" HIGH;58:#59: NET "pin_led_o<0>" LOC = D22;60: NET "pin_led_o<1>" LOC = C22;61: NET "pin_led_o<2>" LOC = E21;62: NET "pin_led_o<3>" LOC = D21;63: NET "pin_led_o<4>" LOC = C21;64: NET "pin_led_o<5>" LOC = B24;65: NET "pin_led_o<6>" LOC = C20;66: NET "pin_led_o<7>" LOC = B23;表1. UCF example对上面的UCF文件进行一些注释:该UCF文件主要是完成了管脚的约束、时钟的约束,以及组的约束。

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

ISE软件使用说明

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

ISE 约束文件的基本操作

按:早就想研究一下fpga约束设置,现在总算有时间静下心来看看了1.约束文件的概念FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF 文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF 文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。

本节主要介绍UCF文件的使用方法。

UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx 约束文件编辑器进行编辑。

NCF约束文件的语法和UCF文件相同,二者的区别在于: UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。

PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。

一般情况下,用户约束都应在UCF文件中完成,不建议直接修改 NCF 文件和PCF文件。

2.创建约束文件约束文件的后缀是.ucf,所以一般也被称为UCF文件。

创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。

第一种方法:新建一个源文件,在代码类型中选取“Implem entation Constrains File”,在“File Name”中输入“one2two_ucf”。

单击“Next”按键进入模块选择对话框,选择模块“one2two”,然后单击“Next”进入下一页,再单击“Finish”按键完成约束文件的创建。

第二种方法:在工程管理区中,将“Source for”设置为“Synthesis/Implementation”。

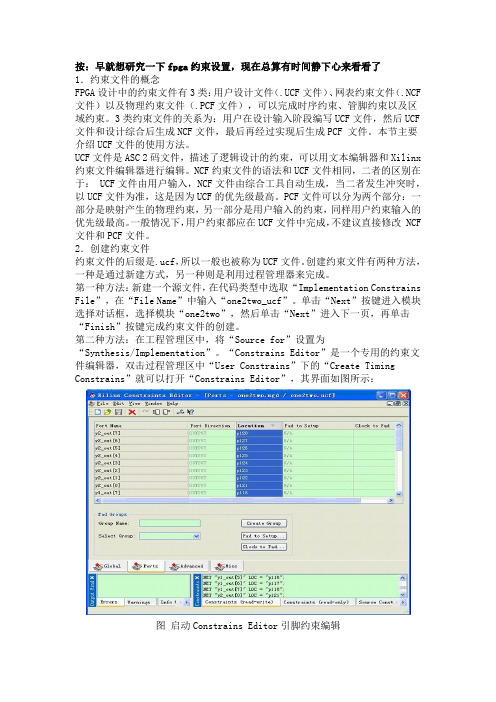

“Constrains Editor”是一个专用的约束文件编辑器,双击过程管理区中“User Constrains”下的“Create T iming Constrains”就可以打开“Constrains Editor”,其界面如图所示:图启动Constrains Editor引脚约束编辑在“Ports”选项卡中可以看到,所有的端口都已经罗列出来了,如果要修改端口和FPGA管脚的对应关系,只需要在每个端口的“Location”列中填入管脚的编号即可。

ISE约束UCF编辑的操作介绍

摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。

Xilinx FPGA设计约束的分类Xilinx定义了如下几种约束类型:• “Attributes and Constraints”• “CPLD Fitter”• “Grouping Constraints”• “Logical Constraints”• “Physical Constraints”• “Mapping Directives”• “Placement Constraints”• “Routing Directives”• “Synthesis Constraints”• “Timing Constraints”• “Configuration Constraints”通过编译UCF(user constraints file)文件可以完成上述的功能。

还是用实例来讲UCF的语法是如何的。

图1 RTL Schematic图1 是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA管脚。

1: NET "pin_sysclk_i" LOC = AD12 | TNM_NET = pin_sysclk_i;2: TIMESPEC TS_pin_sysclk_i = PERIOD "pin_sysclk_i" 15 ns HIGH 50 %; 3:#4: NET "pin_plx_lreset_n_i" LOC = B18;5:#6: NET "pin_plx_lhold_i" LOC = C17;7: NET "pin_plx_lholda_o" LOC = D17 | SLEW = FAST;8:#9: NET "pin_plx_ads_n_i" LOC = E18;10:NET "pin_plx_ads_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 11:#12: NET "pin_plx_lw_r_n_i" LOC = E9;13:NET "pin_plx_lw_r_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 14:#15: NET "pin_plx_blast_n_i" LOC = D18;16:NET "pin_plx_blast_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 17:#18: NET "pin_plx_lad_io<0>" LOC = AD13 | SLEW = FAST | TNM = LAD;19: NET "pin_plx_lad_io<1>" LOC = AC13 | SLEW = FAST | TNM = LAD;20: NET "pin_plx_lad_io<2>" LOC = AC15 | SLEW = FAST | TNM = LAD;21: NET "pin_plx_lad_io<3>" LOC = AC16 | SLEW = FAST | TNM = LAD;22: NET "pin_plx_lad_io<4>" LOC = AA11 | SLEW = FAST | TNM = LAD;23: NET "pin_plx_lad_io<5>" LOC = AA12 | SLEW = FAST | TNM = LAD;24: NET "pin_plx_lad_io<6>" LOC = AD14 | SLEW = FAST | TNM = LAD;25: NET "pin_plx_lad_io<7>" LOC = AC14 | SLEW = FAST | TNM = LAD;26: NET "pin_plx_lad_io<8>" LOC = AA13 | SLEW = FAST | TNM = LAD;27: NET "pin_plx_lad_io<9>" LOC = AB13 | SLEW = FAST | TNM = LAD;28: NET "pin_plx_lad_io<10>" LOC = AA15 | SLEW = FAST | TNM = LAD; 29: NET "pin_plx_lad_io<11>" LOC = AA16 | SLEW = FAST | TNM = LAD; 30: NET "pin_plx_lad_io<12>" LOC = AC11 | SLEW = FAST | TNM = LAD; 31: NET "pin_plx_lad_io<13>" LOC = AC12 | SLEW = FAST | TNM = LAD; 32: NET "pin_plx_lad_io<14>" LOC = AB14 | SLEW = FAST | TNM = LAD; 33: NET "pin_plx_lad_io<15>" LOC = AA14 | SLEW = FAST | TNM = LAD; 34: NET "pin_plx_lad_io<16>" LOC = D12 | SLEW = FAST | TNM = LAD;35: NET "pin_plx_lad_io<17>" LOC = E13 | SLEW = FAST | TNM = LAD;36: NET "pin_plx_lad_io<18>" LOC = C16 | SLEW = FAST | TNM = LAD;37: NET "pin_plx_lad_io<19>" LOC = D16 | SLEW = FAST | TNM = LAD;38: NET "pin_plx_lad_io<20>" LOC = D11 | SLEW = FAST | TNM = LAD;39: NET "pin_plx_lad_io<21>" LOC = C11 | SLEW = FAST | TNM = LAD;40: NET "pin_plx_lad_io<22>" LOC = E14 | SLEW = FAST | TNM = LAD;41: NET "pin_plx_lad_io<23>" LOC = D15 | SLEW = FAST | TNM = LAD; 42: NET "pin_plx_lad_io<24>" LOC = D13 | SLEW = FAST | TNM = LAD; 43: NET "pin_plx_lad_io<25>" LOC = D14 | SLEW = FAST | TNM = LAD; 44: NET "pin_plx_lad_io<26>" LOC = F15 | SLEW = FAST | TNM = LAD; 45: NET "pin_plx_lad_io<27>" LOC = F16 | SLEW = FAST | TNM = LAD; 46: NET "pin_plx_lad_io<28>" LOC = F11 | SLEW = FAST | TNM = LAD; 47: NET "pin_plx_lad_io<29>" LOC = F12 | SLEW = FAST | TNM = LAD; 48: NET "pin_plx_lad_io<30>" LOC = F13 | SLEW = FAST | TNM = LAD; 49: NET "pin_plx_lad_io<31>" LOC = F14 | SLEW = FAST | TNM = LAD; 50: TIMEGRP "LAD" OFFSET = IN 6.4 ns AFTER "pin_sysclk_i" HIGH;51: TIMEGRP "LAD" OFFSET = OUT 3.1 ns BEFORE "pin_sysclk_i" HIGH; 52:#53: NET "pin_plx_ready_n_o" LOC = F18 | SLEW = FAST;54: NET "pin_plx_ready_n_o" OFFSET = OUT 4.2 ns BEFORE "pin_sysclk_i" HIGH;55:#56: NET "pin_plx_bterm_n_o" LOC = D10 | SLEW = FAST;57: NET "pin_plx_bterm_n_o" OFFSET = OUT 4.2 ns BEFORE "pin_sysclk_i" HIGH;58:#59: NET "pin_led_o<0>" LOC = D22;60: NET "pin_led_o<1>" LOC = C22;61: NET "pin_led_o<2>" LOC = E21;62: NET "pin_led_o<3>" LOC = D21;63: NET "pin_led_o<4>" LOC = C21;64: NET "pin_led_o<5>" LOC = B24;65: NET "pin_led_o<6>" LOC = C20;66: NET "pin_led_o<7>" LOC = B23;表1. UCF example对上面的UCF文件进行一些注释:该UCF文件主要是完成了管脚的约束、时钟的约束,以及组的约束。

ISE软件的使用

大

学

80ns

信

电

系

100ns

实

验

中

120ns 140ns

心

160ns

180ns

三、Xilinx FPGA开发流程

浙

江

大

学

信

电

系

实

验

中

心

四、 实验步骤(采用Verilog HDL语言)

1. 复制文件

将光盘中的lab2\counter文件夹复制到硬盘上,本例复 制到E盘。

信息 显示窗口

浙

源文件 处理窗口

验

中

心

6、电路代码综合

浙

江

大

学

信

电

系

实

在Sources窗口,选择Synthesis/Implementation, 并选中文件conter.v。 在Processes窗口中双击“Synthesize-XST”进行综 合。 用鼠标点击“+Synthesize-XST”的“+”号,展开菜 单,并双击“View RTL Schematic”。 综合结果如下图:

•参数n:分频比 •参数counter_bit:实现n分频 需要计数器位数。

≥ log 2 n

浙

江

大

学

信

电

系

实

验

中

心

(2)四位双向环形计数器

module counter ( input wire clk , input wire reset_n , input wire slow_cnt, always @(posedge clk) input wire direction, if (~reset_n) temp <= 4'b1110; output wire [ 3 : 0 ] count_out); else if (en) wire cout1,cout2,en; case ( {direction,temp}) wire[25:0] en_cnt; 5'b0_0111: temp<= 4'b1011; assign en= ~slow_cnt || cout2 5'b0_1011: temp<= 4'b1101; div_n #(128,7) div_128( 5'b0_1101: temp<= 4'b1110; .cout(cout1), 5'b0_1110: temp<= 4'b0111; 128分频器实例: .cin(1'b1), 5'b1_0111: temp<= 4'b1110; n=128,counter_bit=7 .clk(clk)); 5'b1_1011: temp<= 4'b0111; div_n #(390625,19) div_390625( 5'b1_1101: temp<= 4'b1011; .cout(cout2), 5'b1_1110: temp<= 4'b1101; 390625 分频器实例: .cin(cout1), default: temp<= 4'b1110; n=390625 , .clk(clk)); endcase counter_bit=19 reg[3:0] temp; assign count_out=temp;

ise管脚约束设置参数详解

ise管脚约束设置参数详解以ISE管脚约束设置参数详解概述ISE(Integrated Software Environment)是Xilinx公司开发的一款用于设计和实现FPGA(Field-Programmable Gate Array)的软件工具。

在使用ISE进行FPGA设计时,管脚约束是非常重要的一部分,它用于指定FPGA芯片上的输入输出引脚的功能和连接关系,以确保设计的正确性和可靠性。

本文将详细介绍ISE管脚约束设置参数的相关知识。

1. 管脚约束的作用管脚约束是将设计的逻辑电路与FPGA芯片上的引脚进行连接的关键步骤。

通过正确设置管脚约束参数,可以确保逻辑电路与硬件之间的正确通信,同时还可以优化电路性能和资源利用率。

在ISE中,管脚约束的设置包括输入输出管脚的引脚类型、电平标准、时钟频率等多个方面。

2. 管脚约束的设置方法在ISE中,可以使用UCF(User Constraints File)文件或XDC (Xilinx Design Constraints)文件来进行管脚约束的设置。

UCF 文件是ISE早期版本使用的约束文件格式,而XDC文件是ISE 14.1及以后版本引入的新约束文件格式。

下面将分别介绍这两种约束文件的设置方法。

2.1 UCF文件的设置方法UCF文件是一种文本文件,可以使用任何文本编辑器进行编辑。

UCF文件中的每一行都对应着一个管脚的约束设置。

以下是UCF文件的一些常用约束参数及其设置方法:- NET:用于定义逻辑电路中的信号名称;- LOC:用于定义信号连接到FPGA芯片上的具体引脚位置;- IOSTANDARD:用于定义引脚的电平标准;- SLEW:用于定义引脚的输出斜率控制;- DRIVE:用于定义引脚的驱动能力;- PULLUP:用于定义引脚的上拉电阻;- PULLDOWN:用于定义引脚的下拉电阻。

通过在UCF文件中逐行设置这些约束参数,可以完成对管脚的约束设置。

ISE使用指南中

4.3.2 基于ISE的仿真在代码编写完毕后,需要借助于测试平台来验证所设计的模块是否满足要求。

ISE提供了两种测试平台的建立方法,一种是使用HDL Bencher的图形化波形编辑功能编写,另一种就是利用HDL语言。

由于后者使用简单、功能强大,所以本节主要介绍基于Verolog语言的测试平台建立方法。

1.测试波形法在ISE中创建testbench波形,可通过HDL Bencher修改,再将其和仿真器连接起来,再验证设计功能是否正确。

首先在工程管理区将Sources for设置为Behavioral Simulation,然后在任意位置单击鼠标右键,在弹出的菜单中选择“New Source”命令,然后选中“Test Bench WaveForm”类型,输入文件名为“test_bench”,点击Next进入下一页。

这时,工程中所有Verilog Module的名称都会显示出来,设计人员需要选择要进行测试的模块。

由于本工程只有一个模块,所以只列出了test,如图4-30所示。

图4-30 选择待测模块对话框用鼠标选中test,点击“Next”后进入下一页,直接点击“Finish”按键。

此时HDL Bencher程序自动启动,等待用户输入所需的时序要求,如图4-31所示。

图4-31 时序初始化窗口时钟高电平时间和时钟低电平时间一起定义了设计操作必须达到的时钟周期,输入建立时间定义了输入在什么时候必须有效,输出有效延时定义了有效时钟延时到达后多久必须输出有效数据。

默认的初始化时间设置如下:∙时钟高电平时间(Clock High Time):100ns∙时钟低电平时间(Clock Low Time):100ns∙输入建立时间(Input Setup):15ns∙输出有效时间(Output Valid):15ns∙偏移时间(Offset):100ns单击“OK”按钮,接受默认的时间设定。

测试矢量波形显示如图4-32所示。

ISE操作说明

ISE操作说明1、双击打开ISE,选择“file->new project”新建一个工程。

2、修改工程保存路径并输入工程名,然后单击next。

3、选定芯片型号如下图所示。

然后一直单击next直到finish。

4、将源文件拷贝到新建的工程中。

5、单击synthesize进行综合。

6、进行引脚分配。

点开User Constraints,双击Assign Package Pins,弹出如下窗口,单击Yes。

7、弹出以下窗口。

8、按以下窗口进行管脚分配。

9、关闭窗口并保存窗口内容。

10、单击Implement Design 进行编译、布局、布线。

11、单击Generate Programing File生成下载文件。

12、单击Configure Device(iMAPCE),进入下载界面。

13、单击finish14、单击Bypass15、选择对应的模块,把**.bit文件加载进来16、加载完成之后会弹出一个警告,单击OK17、右键单击最后一个模块,选择program18、如图选择,单击OK,就可以下载了19、下载完成后,会出现如下图所示的窗口显示program succeeded。

20、以上操作是直接将二进制文件下载到FPGA中,掉电之后将丢失。

为使其重新上电时可自动配置,需要将配置文件下载到prom中保存。

因此,首先要生成prom配置文件。

双击Generate PROM、ACE or JTAG File,进入生成prom配置文件界面。

21、选择“Prepare a PROM File”,单击next。

22、键入要生成的PROM 名称,如下图所示。

23、单击add,添加prom器件。

单击next,直到finish。

24、单击ok。

25、选择二进制文件26、单击No。

27、单击ok。

28、单击Generate File,生成配置文件29、双击Baundary Scan,然后单击重新进行JTAG链扫描。

手把手课堂-赛灵思FPGA设计时序约束指南

手把手课堂:赛灵思FPGA设计时序约束指南作者:Austin Lesea,首席工程师 Xilinx Inc. Austin.lesea@作为赛灵思用户论坛的定期访客(见),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。

为帮助FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果。

何为时序约束?为保证设计的成功,设计人员必须确保设计能在特定时限内完成指定任务。

要实现这个目的,我们可将时序约束应用于连线中——从某 FPGA 元件到 FPGA 内部或 FPGA 所在 PCB 上后续元件输入的一条或多条路径。

在 FPGA 设计中主要有四种类型的时序约束:PERIOD、OFFSET IN、OFFSET OUT 以及 FROM: TO(多周期)约束。

PERIOD 约束与建组每个同步设计要有至少一个PERIOD 约束(时钟周期规格),这是最基本的约束类型,指定了时钟周期及其占空比。

若设计中有不止一个时钟,则每个时钟都有自己的 PERIOD 约束。

PERIOD约束决定了我们如何进行布线,来满足设计正常工作的时序要求。

为简化时序约束应用过程,常常可将具有类似属性的连线分组为一组总线或一组控制线。

这样做有助于完成正确为设计约束定义优先级这一关键步骤。

设计约束优先次序排列若设计有多重约束,则需进行优先次序排列。

一般来说,约束的一般性越强,其优先级越低。

相反,约束的针对性越强,其优先级越高。

举例来说,时钟网络上的某个一般性 PERIOD 约束将被特定网络的具有更高优先级的 FROM: TO 约束所覆盖。

特定 FROM: TO(或 FROM: THRU:TO)约束在时钟域内任意网络中的重要性均高于一般性约束。

为便于进行约束的优先级排列,可运行赛灵思时序分析器(ISE® Design Suite 中的静态时序分析工具),并生成时序规格迭代报告,即常说的 .tsi 报告。

ISE软件使用说明

说明这个说明主要介绍了使用开发板可能使用到的3个工具,主要以串口功能的实现作为例子,讲述了ISE, Plantform和EDK的使用方法以及操作的基本流程。

ISE的使用一.启动Xilinx ISE:开始Æ所有程序ÆXilinx ISE 7.1iÆProject Navigator二.新建/打开一个工程:如果已经有了工程,则在FileÆOpen Project弹出的对话框里面选择你的工程。

如果没有合适的工程就需要通过FileÆNew Project来新建一个工程。

具体操作步骤如下:分别在Project Name和Project Location里面填写您想要创建的工程的名称和路径。

在Top-Level Module Type的下拉菜单里面选择您的工程的顶层模块的类型。

本次串口通信的实验的顶层为原理图,所以选择Schematic。

然后点击下一步:在这个对话框的上半部分选择您使用的芯片的族(Spartan3),型号(xc3s400),封装(pq208)和速度(-4)。

下面选择您要使用编译和综合的软件,建议使用ISE自带的软件,一是使用简便,二是Xilinx公司对自己的FPGA了解程度比第三方要高很多,所以使用Xilinx公司自己的软件有的时候会获得意想不到的收获。

具体参数选择如图,然后单击下一步:在这个对话框里面新建工程里面的文件,这步也可以放到后面来实现,这里我们先选择下一步:这一步用来添加已经存在的文件,同样,我们在后面实现这步。

点击下一步:在最后这个对话框里面显示了我们即将建立的工程的详细信息,确认无误以后点击完成,ISE将为您创建一个名字为uart_test的工程:三.为刚创建的工程添加源文件:1.添加已经存在的源文件:选中屏幕右上的xc3s400-4pq208,单击ProjectÆAdd Source,在弹出的对话框里面选择您已经存在的程序文件(.v .vhd)。

ISE使用指导

ISE的使用说明启动桌面上名为Project Navigator的ISE软件图标,进入ISE开发系统如图所示。

在上拉菜单file栏打开,单击New project选项,开始新建一项工程。

如果想打开已有的ISE工程文件(文件格式为*.npl),则单击open project选项。

下面我们将以一个包括了24进制和60进制计数器的复合计数器的VHDL程序为例,来说明ISE的具体使用。

首先单击New project选项,出现如图所示对话框:在Project name一栏填上工程文件名,我们在此工程名命名为counter,放在目录F:\teacher_li 下。

下一步,进行可编程器件型号的选择以及设计流程的设置。

在器件型号栏有Device family ,Device (型号),封装,speed grade,可以根据实验平台所用的可编程逻辑器件分别设置相应选项。

对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了New Project Information的设置。

如图所示:单击“完成”按钮,进入到如下对话框:在Source in Project一栏,选择菜单Module View选项,在工程名counter的图标位置单击右键,出现如下对话框。

New Project :新建一项文件,单击ew Project图标,出现的对话框包括了以下选项:新建IP核,电路设计,状态机,新建测试波形,用户文档,V erilog编写文件,V erilog测试文件,VHDL库,VHDL编写文件,VHDL包,VHDL测试平台。

Add Source :添加一项已经存在的文件。

本例中,首先选择VHDL Module项,我们file name命名为count。

下一步,进行管脚信号名称,位数和方向的设置。

如下所示:设置好相关管脚后,下一步:单击“完成”。

上面对话框就是VHDL Module的编写界面,我们在此文档编写了如下的VHDL代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following lines to use the declarations that are-- provided for instantiating Xilinx primitive components.--library UNISIM;--use UNISIM.VComponents.all;entity count isPort ( reset: in std_logic;flag : in std_logic;clk: in std_logic;counter:out std_logic_vector(5 downto 0));end count;architecture Behavioral of count issignal count:std_logic_vector(5 downto 0);signal flag1:std_logic;begincounter<=count;process(reset,clk)beginif reset='1' thencount<="000000";flag1<='0';elsif clk'event and clk='1' thenflag1<=flag;--flag状态切换时,将计数器清零;if (flag='0' and flag1='1') or (flag='1' and flag1='0') thencount<="000000";elsif flag='0' and flag1='0' then -- flag='0' ,则进行24进制计数if count<23 thencount<=count+1;elsif count>=23 thencount<="000000";end if;elsif flag='1' and flag1='1' then -- flag='1' , 则进行60进制计数if count<59 thencount<=count+1;elsif count>=59 thencount<="000000";end if;end if;end if;end process;end Behavioral;在界面的Processes for Source一栏,是一系列综合工具。

Xilinx-ISE的ucf文件分析

Xilinx-ISE中约束的设计1.Xilinx-ISE中的约束文件1.1约束的分类利用FPGA进行系统设计常用的约束主要分为3类。

(1)时序约束:主要用于规范设计的时序行为,表达设计者期望满足的时序条件,知道综合和布局布线阶段的优化算法等。

(2)布局布线约束:主要用于指定芯片I/O引脚位置以及指导软件在芯片特定的物理区域进行布局布线。

(3)其它约束:指目标芯片型号、接口位置、电气特性等约束属性。

1.2约束的主要作用(1)提高设计的工作效率对很多数字电路设计来说,提高工作频率是非常重要的,因为高的工作频率意味着高效的电路处理能力,通过附加约束可以控制逻辑的综合、映射、布局和布线,以减少逻辑和布线的延迟,从而提高工作效率。

(2)获得正确的时序分析报告几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或者是布局布线后的时序分析报告,从而对设计的性能做出评估。

静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。

(3)指定FPGA引脚位置与电气标准FPGA的可编程性使电路板设计加工和FPGA设计可以同时进行,而不必等FPGA引脚位置的完全确定,从而节约了系统开发时间。

电路板加工完成后,设计者要根据电路板的走线对FPGA加上引脚位置约束,以保证FPGA与电路板正确连接。

另外通过约束还可以指定I/O引脚所支持的接口标准和其他电气特性。

为了满足日新月异的通信发展,Xilinx新型FPGA可以通过I/O引脚约束设置支持,诸如AGP、BLVDS、CTT、GTL、GTLP、HSTL、LDT、LVCMOS、LVDCI、LVDS、LVPECL、LVDSEXT、LVTTL、PCI、PCIX、SSTL、ULVDS等丰富的I/O接口标准。

(4)利于模块化设计通过区域约束还能在FPGA上规划各个模块的实现区域,通过物理布局布线约束完成模块化设计等。

ISE 约束文件的基本操作

ISE 约束文件的基本操作1.约束文件的概念FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。

本节主要介绍UCF文件的使用方法。

UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。

NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。

PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。

一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。

2.创建约束文件约束文件的后缀是.ucf,所以一般也被称为UCF文件。

创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。

第一种方法:新建一个源文件,在代码类型中选取“Implementation Constrains File”,在“File Name”中输入“one2two_ucf”。

单击“Next”按键进入模块选择对话框,选择模块“one2two”,然后单击“Next”进入下一页,再单击“Finish”按键完成约束文件的创建。

第二种方法:在工程管理区中,将“Source for”设置为“Synthesis/Implementation”。

“Constrains Editor”是一个专用的约束文件编辑器,双击过程管理区中“User Constrains”下的“Create Timing Constrains”就可以打开“Constrains Editor”,其界面如图所示:图启动Constrains Editor引脚约束编辑在“Ports”选项卡中可以看到,所有的端口都已经罗列出来了,如果要修改端口和FPGA管脚的对应关系,只需要在每个端口的“Location”列中填入管脚的编号即可。

ISE管脚约束设置参数详解5页word文档

ISE管脚约束设置参数详解(原创)ISE管脚约束设置参数详解在ISE中,打开User Constraints中的Assign Package Pins就可以对设定的管脚进行约束。

打开了Xilinx PACK-[Design Object List-I/O Pin]其中参数设置如下I/O Name——IO管脚名称,对应于module里输入输出管脚。

I/O Direction——设定输入(Input)还是输出(Output)管脚。

Loc——位于芯片的位置。

Bank——管脚位于的Bank块,当指定了Loc后,bank也就确定了。

FROM:Spartan-3E FPGA 系列数据手册P19I/O Std.——I/O管脚的电平标准。

每个bank都可以随意设置为该器件支持的电平标准,不同的电平标准在一个bank中要注意它们的电平要一致,比如都为3.3v,电平可以为LVTTL、LVCO MS33。

From:Spartan-3E FPGA 系列数据手册P16~17下面介绍一下常见逻辑电平标准现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPEC L、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。

下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

voh(输出电压反转为高电平)VO-H。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。

所以后来就把一部分“砍”掉了。

也就是后面的LVT TL。

LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。

Xilinx ISE 13 笔记04 引脚约束的实现

第四引脚约束和时序约束的实现引脚约束:将顶层设计的逻辑端口和FPGA的物理引脚进行映射,步骤如下:(1)在Design面板下的View的单选按钮,将其从前面的Simulation,切换到Implementation。

(2)在Hierarchy面板窗口中,选择top文件名,右击,New Source…(3)出现New Source Wizard窗口,文件类型:Implementation Constraints File,文件名:top(4)Finish,Hierarchy中出现top.ucf文件。

(5)在Hierarchy窗口中,选择top,然后在Processes窗口下,选择User Constraints 选项,展开,选择I/O Pin Planning(PlanAhead)-Post-Synthesis选项,双击(6)出现ISE Project Navigator对话框,由于已经生成.ucf文件,选择Yes(7)出现对话框,单击OK。

(8)出现PlanAhead工具主界面(第一次等很久…),Close。

下面准备在PlanAhead软件中实现I/O引脚位置的约束,查板子原理图和引脚约束文件。

步骤如下:(1)对应每个信号行,在Site栏下,分别输入FPGA引脚的名字,然后在I/O Std 栏下,输入LVCOMS33,作为设计中所有I/O引脚的标准。

注意:也可以采用下面的方法,约束I/O引脚的位置。

如下图,在I/O Ports窗口中选中需要约束的端口,然后用鼠标将其拖拽到Package窗口所显示器件的相应的封装的位置,如此重复,知道为顶层设计的每个端口都分配了FPGA的引脚位置。

然后为每个引脚分配I/O Std为LVCMOS33。

当在FPGA映射了相应的位置后,在工具栏选择放大按钮,可以在所分配FPGA 引脚内看到“-||-”符号。

(2)保存,退出PlanAhead工具界面(3)在Hierarchy窗口中,选择top.ucf文件,然后在Processes窗口中,选择User Constraints,展开,双击Edit Constraints(Text)选项。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。

Xilinx FPGA设计约束的分类Xilinx定义了如下几种约束类型:• “Attributes and Constraints”• “CPLD Fitter”• “Grouping Constraints”• “Logical Constraints”• “Physical Constraints”• “Mapping Directives”• “Placement Constraints”• “Routing Directives”• “Synthesis Constraints”• “Timing Constraints”• “Configuration Constraints”通过编译UCF(user constraints file)文件可以完成上述的功能。

还是用实例来讲UCF的语法是如何的。

图1 RTL Schematic图1 是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA管脚。

1: NET "pin_sysclk_i" LOC = AD12 | TNM_NET = pin_sysclk_i;2: TIMESPEC TS_pin_sysclk_i = PERIOD "pin_sysclk_i" 15 ns HIGH 50 %; 3:#4: NET "pin_plx_lreset_n_i" LOC = B18;5:#6: NET "pin_plx_lhold_i" LOC = C17;7: NET "pin_plx_lholda_o" LOC = D17 | SLEW = FAST;8:#9: NET "pin_plx_ads_n_i" LOC = E18;10:NET "pin_plx_ads_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 11:#12: NET "pin_plx_lw_r_n_i" LOC = E9;13:NET "pin_plx_lw_r_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 14:#15: NET "pin_plx_blast_n_i" LOC = D18;16:NET "pin_plx_blast_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 17:#18: NET "pin_plx_lad_io<0>" LOC = AD13 | SLEW = FAST | TNM = LAD;19: NET "pin_plx_lad_io<1>" LOC = AC13 | SLEW = FAST | TNM = LAD;20: NET "pin_plx_lad_io<2>" LOC = AC15 | SLEW = FAST | TNM = LAD;21: NET "pin_plx_lad_io<3>" LOC = AC16 | SLEW = FAST | TNM = LAD;22: NET "pin_plx_lad_io<4>" LOC = AA11 | SLEW = FAST | TNM = LAD;23: NET "pin_plx_lad_io<5>" LOC = AA12 | SLEW = FAST | TNM = LAD;24: NET "pin_plx_lad_io<6>" LOC = AD14 | SLEW = FAST | TNM = LAD;25: NET "pin_plx_lad_io<7>" LOC = AC14 | SLEW = FAST | TNM = LAD;26: NET "pin_plx_lad_io<8>" LOC = AA13 | SLEW = FAST | TNM = LAD;27: NET "pin_plx_lad_io<9>" LOC = AB13 | SLEW = FAST | TNM = LAD;28: NET "pin_plx_lad_io<10>" LOC = AA15 | SLEW = FAST | TNM = LAD; 29: NET "pin_plx_lad_io<11>" LOC = AA16 | SLEW = FAST | TNM = LAD; 30: NET "pin_plx_lad_io<12>" LOC = AC11 | SLEW = FAST | TNM = LAD; 31: NET "pin_plx_lad_io<13>" LOC = AC12 | SLEW = FAST | TNM = LAD; 32: NET "pin_plx_lad_io<14>" LOC = AB14 | SLEW = FAST | TNM = LAD; 33: NET "pin_plx_lad_io<15>" LOC = AA14 | SLEW = FAST | TNM = LAD; 34: NET "pin_plx_lad_io<16>" LOC = D12 | SLEW = FAST | TNM = LAD;35: NET "pin_plx_lad_io<17>" LOC = E13 | SLEW = FAST | TNM = LAD;36: NET "pin_plx_lad_io<18>" LOC = C16 | SLEW = FAST | TNM = LAD;37: NET "pin_plx_lad_io<19>" LOC = D16 | SLEW = FAST | TNM = LAD;38: NET "pin_plx_lad_io<20>" LOC = D11 | SLEW = FAST | TNM = LAD;39: NET "pin_plx_lad_io<21>" LOC = C11 | SLEW = FAST | TNM = LAD;40: NET "pin_plx_lad_io<22>" LOC = E14 | SLEW = FAST | TNM = LAD;41: NET "pin_plx_lad_io<23>" LOC = D15 | SLEW = FAST | TNM = LAD; 42: NET "pin_plx_lad_io<24>" LOC = D13 | SLEW = FAST | TNM = LAD; 43: NET "pin_plx_lad_io<25>" LOC = D14 | SLEW = FAST | TNM = LAD; 44: NET "pin_plx_lad_io<26>" LOC = F15 | SLEW = FAST | TNM = LAD; 45: NET "pin_plx_lad_io<27>" LOC = F16 | SLEW = FAST | TNM = LAD; 46: NET "pin_plx_lad_io<28>" LOC = F11 | SLEW = FAST | TNM = LAD; 47: NET "pin_plx_lad_io<29>" LOC = F12 | SLEW = FAST | TNM = LAD; 48: NET "pin_plx_lad_io<30>" LOC = F13 | SLEW = FAST | TNM = LAD; 49: NET "pin_plx_lad_io<31>" LOC = F14 | SLEW = FAST | TNM = LAD; 50: TIMEGRP "LAD" OFFSET = IN 6.4 ns AFTER "pin_sysclk_i" HIGH;51: TIMEGRP "LAD" OFFSET = OUT 3.1 ns BEFORE "pin_sysclk_i" HIGH; 52:#53: NET "pin_plx_ready_n_o" LOC = F18 | SLEW = FAST;54: NET "pin_plx_ready_n_o" OFFSET = OUT 4.2 ns BEFORE "pin_sysclk_i" HIGH;55:#56: NET "pin_plx_bterm_n_o" LOC = D10 | SLEW = FAST;57: NET "pin_plx_bterm_n_o" OFFSET = OUT 4.2 ns BEFORE "pin_sysclk_i" HIGH;58:#59: NET "pin_led_o<0>" LOC = D22;60: NET "pin_led_o<1>" LOC = C22;61: NET "pin_led_o<2>" LOC = E21;62: NET "pin_led_o<3>" LOC = D21;63: NET "pin_led_o<4>" LOC = C21;64: NET "pin_led_o<5>" LOC = B24;65: NET "pin_led_o<6>" LOC = C20;66: NET "pin_led_o<7>" LOC = B23;表1. UCF example对上面的UCF文件进行一些注释:该UCF文件主要是完成了管脚的约束、时钟的约束,以及组的约束。