AMBA总线详细介绍

AMBAAXI总线详解

AXI 总线协议资料整理第一部分:1、AXI 简介:AXI (Adva need eXte nsible In terface 是一种总线协议,该协议是ARM 公司提出的AMBA( Advanced Microcontroller Bus Architecture)3.0 协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。

它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。

AXI 是AMBA 中一个新的高性能协议。

AXI 技术丰富了现有的AMBA标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

2、AXI 特点:单向通道体系结构。

信息流只以单方向传输,简化时钟域间的桥接,减少门数量。

当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。

通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。

地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

第二部分:本部分对AXI1.0 协议的各章进行整理。

第一章本章主要介绍AXI 协议和AXI 协议定义的基础事务。

1 、AXI 总线共有5 个通道分别是read address channel、write address channel 、read data channel、write data channe、l write response ehanne。

每一个AXI传输通道都是单方向的。

2、每一个事务都有地址和控制信息在地址通道( address channel 中,用来描述被传输数据的性质。

3、读事务的结构图如下:Figure 1 -1 Channel architecture of reads 4、写事务的结构图如下:Figure 1-2 Channel architecture of writes 5、这5条独立的通道都包含一个信息信号和一个双路的VALD、READY握手机制。

AMBA_总线_介绍

SEP3203

2

目录

AMBA总线概述 AHB APB 不同IP之间的互连

3

系统总线简介

系统芯片中各个模块之间需要有接口来连接 总线作为子系统之间共享的通信链路 优点

低成本 方便易用

缺点

会造成性能瓶颈

4

AMBA介绍

Advanced Microcontroller Bus Architecture

end case;

Default_Slave logic

case HTRANS is when IDLE|BUSY => HRESP <= OKAY; when others => HRESP <= ERROR;

end case;

18

AHB信号

19

基本AHB信号

HRESETn

低电平有效

HADDR[31:0]

▪ HADDR must be aligned to a multiple of data size as given by HSIZE

32

BURST传输

AHB Burst 操作

4beat、8beat、16beat、单个字节传输、未定义长度 的传输 支持incrementing和wrapping两种burst传输

AMBA 3.0

AMBA Advanced eXtensible Interface (AXI)

6

一个典型的AMBA系统

处理器和其它主设备/从设备都是可以替换的

7

AHB

高速总线,高性能 流水线操作 可支持多个总线主设备(最多16个) 支持burst传输 总线带宽:8、16、32、64、128bits 上升沿触发操作 对于一个新设计建议使用AHB

stm32的总线AMBA、AHB、APB

stm32的总线AMBA、AHB、APBAMBAAMBA(Advanced Microprocessor Bus Architecture)是ARM公司提出的一种开放性的SoC 总线标准,现在已经广泛的应用于RISC的内核上了。

AMBA定义了一种多总线系统(mulTIlevel busing system),包括系统总线和等级稍低的外设总线。

AMBA支持32位、64位、128位的数据总线,和32位的地址总线,同时支持byte和half-word设计。

它定义了两种总线:AHB(Advanced High-performance Bus)先进的高性能总线,也叫做ASB (Advanced System Bus)。

APB(Advanced peripheral Bus)先进的外设总线AHB和ASB其实是一个东西,是高速总线,主要负责嵌入式处理器、DMA控制器、Memory等等的接口。

APB是低速总线,主要负责外设接口AHB和APB之间是通过Bridge(桥接器)链接的Bus Bridges总所周知,一个系统中的各个模块之间相互通信是通过总线,总线的作用,就是把数据和地址从设备A搬运到设备B上,如果说设备A和设备B具有一致性(原文是under discussion,这里我不知道怎么翻译比较好,暂且翻译为一致性),那么设备A和设备B可以直接挂在同一个总线上,并直接解读总线上的数据。

但是,如果设备A和设备B不具有一致性,那么设备A和设备B就必须挂在两条不同的总线上,这时候我们就需要一个翻译,把设备A上的总线上的数据和地址转换成设备B可以解析的格式,然后放到设备B的总线上,这个翻译就是Bus Bridge,下面这幅图就形象的说明了Bus Bridge在AHB和APB之间的作用。

AHB链接的设备的数据传输速度是比APB设备传输的速度快很多的,也就是说,这里的这个Bus Beidge所起的作用就是缓冲这里可以看到AHB主要是链接在了系统的内核以及存储管理上面的,APB则主要分布给我外设。

浅析AMBA规范以及AMBA5AHB接口和AMBA3APB接口

浅析AMBA规范以及AMBA5AHB接口和AMBA3APB接口一、AMBA简介1、AMBA (Advanced Microprocessor Bus Architecture):ARM® AMBA® 协议是用于连接和管理片上系统 (SoC) 中功能模块的开放标准和片上互连规范。

它有助于首次开发带有大量控制器和外设的多处理器设计。

AMBA 基于CHI™、ACE™、AXI™、AHB™、APB™ 和ATB™ 等规范为 SoC 模块定义了共同的框架结构,这有助于设计的重复使用。

2、AHB (Advanced High-Performance Bus):主要用于单片机中的系统总线。

主要用于Cortex-M家族的处理器。

3、APB (Advanced Peripheral Bus):用于低带宽的外设之间的连接。

4、ATB (Advanced Trace Bus):用于在芯片间传输 trace 数据。

5、ACE (AXI Coherency Extensions):用于智能手机中的big.LITTLE™ 系统。

主要用于Cortex-A15、Cortex-A17、Cortex-A7架构的处理器。

6、AXI (Advanced eXtensible Interface):用得最多的AMBA 接口,在复杂的片上系统中至多连接100个主、从模块。

主要用于Cortex-A、Cortex-R、Mali v500、Mali T760系列的处理器。

7、CHI (Coherent Hub Interface):用于许多服务器与网络应用程序所需要的高可扩展性的片上系统。

主要用于Cortex-A72、Cortex-A57、Cortex-A53架构的处理器。

二、AMBA 5 AHB 接口1、概览:AMBA AHB总线接口适用于高性能的综合设计。

它定义了主模块(Cortex™-M 内核、DMA 存储器、DMA 外设、以太网 DMA、USB OTG HS DMA等)、连接组件和从模块(内部 Flash、内部 SRAM、AHB-APB 总线桥、APB 外设、FSMC等)之间的接口。

AMBA AHB APB 概述

AHB Decoder

• AHB系统中有一个核心地址译码器,它提供HSELx信号到各 个AHB Slave; • Decoder本身只负责位地址译码,为纯组合逻辑电路; • Slave只有在HSELx和HREADY都为High才采样地址/控制信号; • AHB地址线有32条,为简化译码器译码时间,AHB Spec.规 定每个Slave的最小地址空间为1KB,因此译码器最多只需 要对22条地址线进行译码。

HWRITE & HSIZE[2:0]

• Transfer Direction、Transfer Size由Master发出: – HWRITE为HIGH,Master在data phase将数据通过write data bus(HWDATA[31:0])发往Slave – HWRITE为LOW,Slave在data phase将数据通过read data bus (HRDATA[31:0])发往Master

允许某个主设备控制总线 发起一个请求给仲 裁器

驱动地址和控 制信号

仅选中的从设备响应地 址/控制信号

拉高HREADY信号,总线 传输完成

AHB Transfer

• Basic transfer – Address phase

• 传输address和control signal

– Data phase

• 传输write/read data和response signal

• 传输在data phase时若一个clock cycle无法完成传 输,Slave可通过拉低HREADY信号延长传输,传输 结束时状态由Slave HRESP信号反映。

Master sample the data

Master release address and control

AMBA总线介绍

AMBA 总线介绍

先进的微控制器总线体系结构AMBA 规范定义了三种总线:

(1)AHB(Advanced High-performance Bus):用于连接高性能系统模块。

它支持突发数据传输方式及单个数据传输方式,所有时序参考同一个时钟沿;

(2)ASB(Advanced System Bus):用于连接高性能系统模块,它支持突发数据传输模式;

(3)APB(Advance Peripheral Bus):是一个简单接口支持低性能的外围接口。

一个典型的基于AMBA 的微控制器同时集成AHB(或ASB )和APB 接口,如根据AMBA 的规范,连接AHB/ASP 和APB 的APB 桥的唯一功能是提供更简单的接口。

任何由低性能外围设备产生的延迟会由连接高性能

(AHB/ASP)总线的桥反映出来。

桥本身仿佛是一个简单APB 总线的主设备,它

访问与之相连的从设备,并且通过高性能总线上控制信号的子集控制它们。

下

面给出AHB、ASP 和APB 的主要特征。

AHB

AHB 是先进的系统总线。

它主要的目的就是连接高性能、高吞吐率的设备,例如CPU、DMA 和DSP。

它的主要特性:

●高性能新一代总线;

●多控制器;

●分段传输;

●单周期总线控制权移交;

●没有三态实现方式;

●32~128 位总线宽;。

AMBAAXI总线详解

AXI总线协议资料整理第一部分:1、AXI简介:AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。

它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。

AXI 是AMBA 中一个新的高性能协议。

AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

2、AXI 特点:单向通道体系结构。

信息流只以单方向传输,简化时钟域间的桥接,减少门数量。

当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。

通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。

地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

第二部分:本部分对AXI1.0协议的各章进行整理。

第一章本章主要介绍AXI协议和AXI协议定义的基础事务。

1、AXI总线共有5个通道分别是read address channel、write address channel 、read data channel 、write data channel、write response channel。

每一个AXI传输通道都是单方向的。

2、每一个事务都有地址和控制信息在地址通道(address channel)中,用来描述被传输数据的性质。

3、读事务的结构图如下:4、写事务的结构图如下:5、这5条独立的通道都包含一个信息信号和一个双路的V ALD、READY握手机制。

amba协议手册

AMBA协议手册一、AMBA概况AMBA(Advanced Microcontroller Bus Architecture)协议,又被称为AMBA 2.0,是一种针对高性能、高吞吐量嵌入式系统设计的总线协议。

它定义了在一个或多个嵌入式处理器和多个外设之间的高效通信方式,广泛应用于各类芯片和集成电路中。

AMBA为微控制器、数字信号处理器(DSP)以及通信和消费电子等多种应用提供了优秀的性能表现。

二、AMBA版本历史AMBA的发展经历了几个重要的版本,每个版本都增加了新的特性和功能。

1.AMBA 1.0:这个版本主要定义了简单的主从设备间的通信方式,包括数据传输和地址协议。

2.AMBA 2.0:在AMBA 2.0中,引入了更复杂的特性,如猝发传输和更高级的地址和数据传输控制。

3.AMBA 3.0:这个版本引入了新的特性,如外部总线的对齐和分区、扩展的地址空间和数据字节宽度的动态调整。

4.AMBA 4.0:随着芯片设计的不断发展和系统性能的持续提高,AMBA 4.0为高带宽总线传输和高频率时钟提供了支持。

三、AMBA组成部分AMBA协议主要包括以下组成部分:1.AXI(Advanced eXtensible Interface):AXI是一种高性能、高吞吐量的总线接口,用于连接主设备和从设备。

它支持多个通道的数据传输,每个通道都有数据写和数据读两个通道。

2.ACE(Advanced Coherency Enhanced):ACE是AMBA的一种扩展,提供了更高级的内存一致性保证,确保在多处理器系统中数据的一致性。

3.APB(Advanced Peripheral Bus):APB是一种简单、低速的总线接口,主要用于连接低速外设。

它基于传统的Peripheral Bus,但提供了更高的性能和更小的芯片面积。

4.AHB(Advanced High-performance Bus):AHB是一种高性能的总线接口,主要用于连接高性能的处理器和高速存储器。

AMBA总结

AMBA(Advanced Microcontroller Bus Architecture),即高级微控制器总线体系。

目前,AMBA总线标准一共有四套版本,各个版本的协议都沿用至今。

1)第一套AMBA 1.0总线。

2)第二套AMBA 2.0总线。

3)第三套AMBA 3.0 AXI总线。

4)第四套AMBA4.0总线。

➢AMBA1.0只包含ASB总线和APB总线,这时候的总线协议都是三态总线,但是三态总线要设计者花很多的精力去注意时钟。

➢AMBA2.0总线新增了AHB总线,并且采用了分享型的互连结构,增加了新的特性。

➢为了顺应快速发展的SoC技术,ARM公司推出了具有更强灵活性的AMBA3.0 AXI总线。

➢2010年ARM公司发布了SoC片上总线标准的新版本AMBA4.0总线,由AXI4、AXI4-Lite、AXI4-Stream三种标准构成。

AMBA4.0规范是多家企业共同为行业而设定的,包括业界领先的OEM厂商、半导体及EDA供应商等。

AMBA4.0规范的特殊设计将使嵌入式系统达到过去只有台式电脑、笔记本电脑和网络设备才能达到的水准。

1AMBA 2.0版本标准2.0版AMBA标准定义了三种不同的总线:●AHB(Advanced High-performance Bus)高级高性能总线;●ASB(Advanced System Bus)高级系统总线;●APB(Advanced Peripheral Bus)高级外设总线。

典型的基于AMBA总线的系统框图如图:大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。

主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。

另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。

AMBA、AHB、APB总线简介

AMBA、AHB、APB总线简介作者adamzhao日期2006-11-1619:33:00AMBA简介随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。

数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。

在基于IP复用的SoC设计中,片上总线设计是最关键的问题。

为此,业界出现了很多片上总线标准。

其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。

AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

AMBA片上总线AMBA2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。

AHB 的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。

AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。

下面将简要介绍比较重要的AHB和APB总线。

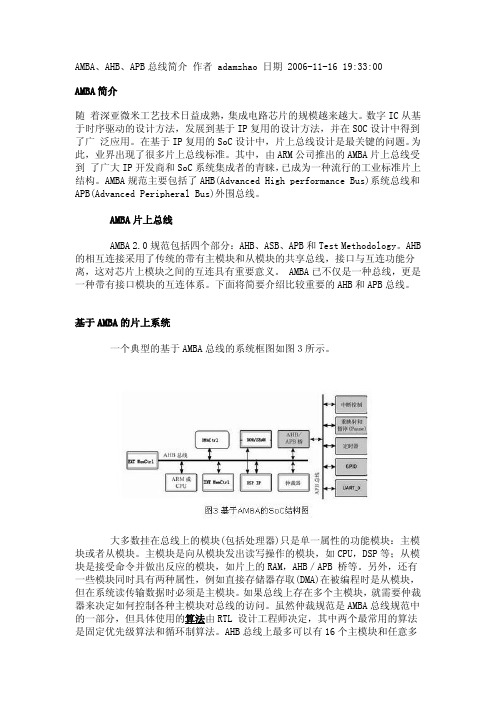

基于AMBA的片上系统一个典型的基于AMBA总线的系统框图如图3所示。

大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。

主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB桥等。

另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。

虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。

AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。

先进的微控制器总线体系结构AMBA规范定义了三种总线

种总线

先进的微控制器总线体系结构 AMBA 规范定义了三种总线: (1)AHB(Advanced High-performance Bus):用于连接高性能系统模 块。它支持突发数据传输方式及单个数据传输方式,所有时序参考同一个时 钟沿; (2)ASB(Advanced System Bus):用于连接高性能系统模块,它支持 突发数据传输模式; (3)APB(Advance Peripheral Bus):是一个简单接口支持低性能的外 围接口。 一个典型的基于 AMBA 的微控制器同时集成 AHB(或 ASB )和 APB

接口,如图 2 所示。ASB 总线是旧版的系统的总线,而新版的 AHB 总线增 强了对性能、综合及时序验证的支持。APB 总线通常用作的局部的第二总线, 作为 AHB 或 ASB 上的单个从属模块。 图 28 AMBA 总线结构图 根据 AMBA 的规范,连接 AHB/ASP 和 APB 的 APB 桥的唯一功能是 提供更简单的接口。任何由低性能外围设备产生的延迟会由连接高性能 (AHB/ASP)总线的桥反映出来。桥本身仿佛是一个简单 APB 总线的主设 备,它访问与之相连的从设备,并且通过高性能总线上控制信号的子集控制 它们。下面给出 AHB、ASP 和 APB 的主要特征。 AHB AHB 是先进的系统总线。它主要的目的就是连接高性能、高吞吐率的设 备,例如 CPU、DMA 和 DSP。它的主要特性: ● 高性能新一代总线;● 多控制器;● 分段传输;● 单周期总线控制权 移交;● 没有三态实现方式;● 32~128 位总线宽;● 包含一种访问保护机 制,用来区别特权访问和无特权访问模式,或指令和数据提取等;● 突发传 输模式最大为 16 节;● 访问空间限制在 32 位;● 提供为较慢设备使用而扼

001AMBA总线概述

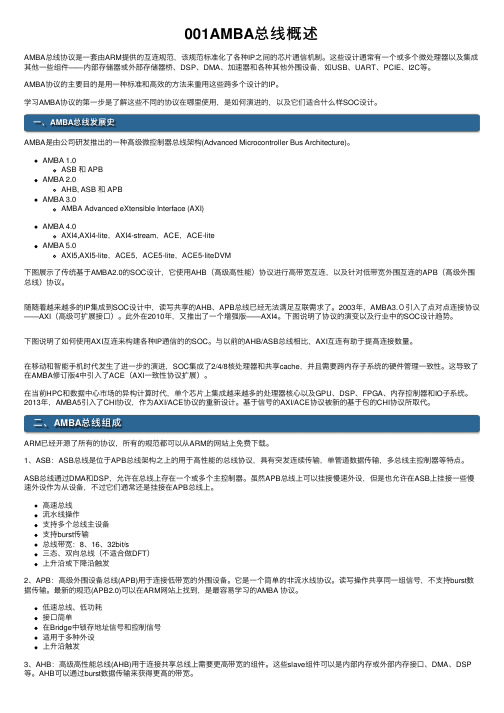

001AMBA总线概述AMBA总线协议是⼀套由ARM提供的互连规范,该规范标准化了各种IP之间的芯⽚通信机制。

这些设计通常有⼀个或多个微处理器以及集成其他⼀些组件——内部存储器或外部存储器桥、DSP、DMA、加速器和各种其他外围设备,如USB、UART、PCIE、I2C等。

AMBA协议的主要⽬的是⽤⼀种标准和⾼效的⽅法来重⽤这些跨多个设计的IP。

学习AMBA协议的第⼀步是了解这些不同的协议在哪⾥使⽤,是如何演进的,以及它们适合什么样SOC设计。

⼀、AMBA总线发展史AMBA是由公司研发推出的⼀种⾼级微控制器总线架构(Advanced Microcontroller Bus Architecture)。

AMBA 1.0ASB 和 APBAMBA 2.0AHB, ASB 和 APBAMBA 3.0AMBA Advanced eXtensible Interface (AXI)AMBA 4.0AXI4,AXI4-lite,AXI4-stream,ACE,ACE-liteAMBA 5.0AXI5,AXI5-lite,ACE5,ACE5-lite,ACE5-liteDVM下图展⽰了传统基于AMBA2.0的SOC设计,它使⽤AHB(⾼级⾼性能)协议进⾏⾼带宽互连,以及针对低带宽外围互连的APB(⾼级外围总线)协议。

随随着越来越多的IP集成到SOC设计中,读写共享的AHB、APB总线已经⽆法满⾜互联需求了。

2003年,AMBA3.0引⼊了点对点连接协议——AXI(⾼级可扩展接⼝)。

此外在2010年,⼜推出了⼀个增强版——AXI4。

下图说明了协议的演变以及⾏业中的SOC设计趋势。

下图说明了如何使⽤AXI互连来构建各种IP通信的的SOC。

与以前的AHB/ASB总线相⽐,AXI互连有助于提⾼连接数量。

在移动和智能⼿机时代发⽣了进⼀步的演进,SOC集成了2/4/8核处理器和共享cache,并且需要跨内存⼦系统的硬件管理⼀致性。

AMBA总线详细介绍

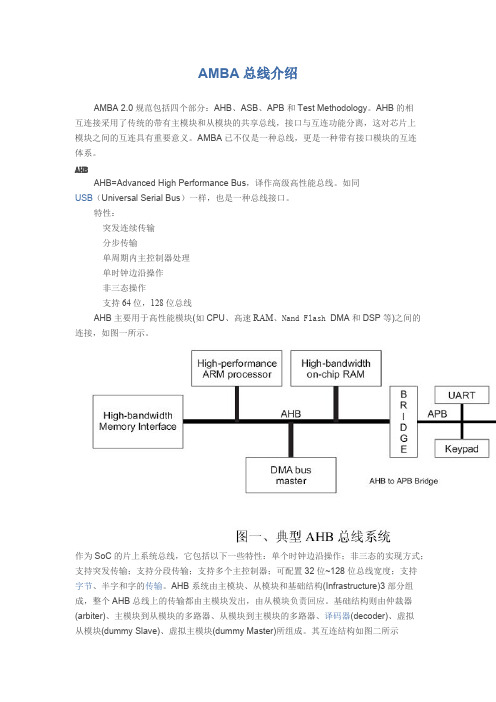

AMBA总线介绍AMBA 2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。

AHB的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。

AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。

AHBAHB=Advanced High Performance Bus,译作高级高性能总线。

如同USB(Universal Serial Bus)一样,也是一种总线接口。

特性:突发连续传输分步传输单周期内主控制器处理单时钟边沿操作非三态操作支持64位,128位总线AHB主要用于高性能模块(如CPU、高速RAM、Nand Flash DMA和DSP等)之间的连接,如图一所示。

作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作;非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;可配置32位~128位总线宽度;支持字节、半字和字的传输。

AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

基础结构则由仲裁器(arbiter)、主模块到从模块的多路器、从模块到主模块的多路器、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummy Master)所组成。

其互连结构如图二所示AHB主控制器:主控制器可以通过地址和控制信息,可以进行初始化,读,写操作。

在同一时间,总线上只能有一个主控制器。

AHB从设备:从设备通常是指在其地址空间内,响应主控制器发出的读写控制操作的被动设备。

通过操作的成功与否反馈给其主控制器,完成数据的传输控制。

AHB仲裁器:仲裁器根据用户的配置,确保在总线上同一时间只有一个主控制器拥有总线控制权限。

AHB总线上只能有一个仲裁器。

AHB译码器:译码器解析在总线上传输的地址和控制信息。

AMBA总线介绍

4. 对Verilog、VHDL;VCS、NC、VSIM不用纠结过于表象的东西

5. 多交流,在项目中的技术提升是最快的

END

renge@

AMBA总线介绍

对待同一个问题,随着技术水平的深入会有新的理解和领悟。 (不断的总结和提高) 对数字工程师的建议: 1. RTL只是很小一部分。软件的语言,硬件的思维(时序,电路) 2. 一定要了解数字设计流程(R2N,Flow FM/DC/PT/PTPX/CDC/DFT…) shell,make…

AMBA总线介绍

AMBA

ARM

= Advanced Microcontroller Bus Architecture 一种先进的微控制器总线架构 是一家公司的名字/英国/安谋/IP 指代一类处理器/RISC/ARM7,ARM9,Cortex A,R,M 1 公交车 3 集线器 2 汇流排 4 总线 • 提供设备间的数据通路 • 物流,高速公路 • Bus-Matrix 问题:总线和接口的区别? 系统总线: 连接系统模块与系统外设的 模块: Master, Slave (CPU,DMA) 外设: peripheral (GPIO)

AHB主设备接口

6

AHB从设备接口

7

Tips:

把AMBA协议当成是参考书,把项目当做教科书。 (learn from doing, practise makes perfect)

不要过于抠协议的细节,有些不理解的内容很正常; (RE,VI,setup/hold,blocking/non-blocking,latch) (试图掌握一个命令的全部选项相当于去背一本字典,毫无意义)

BUS

常见总线: I2C, UART ,SPI

复杂总线: USB,RMII/MII

AMBA总线介绍

计算机基本知识AMBA总线介绍一:背景介绍ARM公司定义了AMBA(Advanced Microcontroller Bus Architecture)总线规范,它是一组针对基于ARM核的、片上系统之间通信而设计的标准协议。

因为ARM处理器的广泛使用而拥有众多第三方支持,被ARM公司90%以上的合作伙伴采用。

在AMBA总线规范中,定义了AHB ,APB ,ASB这3种总线。

最初的AMBA总线是ASB和APB。

在它的第二个版本中,ARM引入了AHB。

(l)AHB:Advanced High Performace Bus,用于高性能系统模块的连接,支持突发模式数据传输和事务分割;(2)ASB:Advanced System Bus,也用于高性能系统模块的连接,支持突发模式数据传输,这是较老的系统总线格式,后来由AHB总线替代;(3)APB:Advanced PeriPheral Bus,用于较低性能外设的简单连接,一般是接在AHB或ASB系统总线上的第二级总线。

图1 典型的基于AMBA总线的系统[1]一个以AMBA 为架构的SOC,图1是个典型的系统架构,一般来说包含了high-performance 的system bus –AHB以及low speed, low power 的peripheral bus - APB 。

System bus 是负责连接例如ARM 之类的embedded processor 以及DMA controller,on-chip memory 和其他interface,或其他需要high bandwidth的模块。

而peripheral bus 则是用来连接系统的外围慢速模块,其协议规则相对AHB来说较为简单,它以AHB之间则通过Bridge 相连,期望能減少system bus 的loading。

二:结构以及仲裁原理1 .AHB BusAHB System是由Master,Slave,Infrastructure 三部分所组成。

AMBA总线详细介绍

AMBA总线详细介绍AMBA(Advanced Microcontroller Bus Architecture)总线是一种用于处理器与外设之间进行通信的开放标准总线架构。

它由英国ARM公司于1996年推出,目的是为了提供一种灵活且可扩展的总线结构,使移动设备和嵌入式系统能够更高效地与外设进行通信。

本文将详细介绍AMBA总线的结构、功能和特性。

AMBA总线架构由三个主要部分组成:AMBA Advanced High-performance Bus(AHB)、AMBA Advanced Peripheral Bus(APB)和AMBA Advanced System Bus(ASB)。

这三个总线分别用于不同级别的连接和通信。

AHB总线用于连接高性能外设和高性能处理器,APB总线用于连接低带宽的外设和低功耗处理器,而ASB总线则用于连接多个AHB和APB总线。

首先,我们来详细了解AHB总线。

AHB总线由一条主总线(Main Bus)和多个高性能外设总线(High-performance Interface)组成。

主总线用于连接处理器、内存和其他高速外设,主要负责高速数据传输和多个高性能外设的控制。

而高性能外设总线则用于连接具有高性能要求的外设,用于数据传输和控制。

AHB总线的主要特点是支持总线仲裁、多主设备访问和高性能操作。

总线仲裁是指当多个主设备同时请求总线访问时,通过总线仲裁器(Arbiter)按照一定的优先级规则进行访问控制。

多主设备访问是指多个主设备可以同时访问总线,通过轮流分配总线周期给每个主设备,提高了总线的利用率。

高性能操作是指AHB总线支持多种高性能操作,如突发传输(Burst Transfer)、分立传输(Split Transfer)和非顺序传输(Non-sequential Transfer)等,能够提供更高的数据传输效率。

接下来,我们了解APB总线。

APB总线主要用于连接低带宽的外设和低功耗处理器,适用于对性能要求相对较低的外围设备。

amba总线知识点

amba总线知识点AMBA总线是一种用于系统级互连的接口标准,广泛应用于嵌入式系统中。

本文将从AMBA总线的基本概念、AMBA协议层次结构、AMBA总线的特点和应用领域等方面进行介绍。

一、AMBA总线的基本概念AMBA(Advanced Microcontroller Bus Architecture)总线是由ARM公司提出的一种开放式、非专利的总线标准,用于连接微处理器、外设和存储器等IP核。

它提供了一种灵活、高效的互联方案,使得不同的IP核可以在系统中自由组合和交互。

二、AMBA协议层次结构AMBA总线采用了分层的结构,包括主控制器、互连器和从设备。

主控制器负责发起总线事务,互连器负责将总线事务从一个主控制器传输到另一个主控制器,从设备则是总线的终端节点。

在AMBA协议中,主要包括APB(Advanced Peripheral Bus)、ASB(Advanced System Bus)和AXI(Advanced eXtensible Interface)三种总线。

APB是低速外设总线,主要用于连接低带宽的外设;ASB是高性能系统总线,适用于连接嵌入式处理器和高带宽外设;AXI是最新的AMBA协议,具有高度可扩展性和灵活性,用于连接高性能和复杂的系统。

三、AMBA总线的特点1. 灵活性:AMBA总线允许系统设计人员根据需求选择不同的AMBA总线协议,以满足不同的系统性能和带宽要求。

2. 可扩展性:AMBA总线支持多主控制器和多从设备,可以灵活地扩展系统的功能和规模。

3. 高性能:AMBA总线采用了高效的总线交互协议和高速的数据传输方式,能够满足复杂系统的高性能需求。

4. 易于集成:AMBA总线标准化了不同IP核之间的互连方式,简化了系统设计和集成的工作。

5. 支持低功耗:AMBA总线通过控制总线时钟和电源管理等方式,实现了对系统功耗的优化。

四、AMBA总线的应用领域AMBA总线广泛应用于嵌入式系统中,特别是在SOC(System on Chip)设计中得到了广泛的应用。

amba总线 latency 定义

AMBA(Advanced Microcontroller Bus Architecture)总线是ARM公司提出的一种开放式、高性能的总线标准,常用于嵌入式系统中。

在AMBA总线中,latency(延迟)通常指的是数据从一个设备传输到另一个设备所需的时间,具体定义如下:1. 传输延迟:AMBA总线上的传输延迟是指数据或信号从一个AMBA总线的主设备传输到从设备(或相反)所需的时间。

这包括了信号传输、寻址和响应等过程中所耗费的时间。

2. 处理延迟:除了传输延迟外,AMBA总线上的处理延迟还包括了数据在从设备内部进行处理(如缓存、寄存器等)所需的时间。

这个延迟通常取决于从设备的性能和处理能力。

AMBA总线是一种用于连接嵌入式系统不同功能模块(如处理器、内存、外设等)的开放式总线标准。

在AMBA总线中,latency(延迟)可以分为以下几个方面的定义和优化:1. 传输延迟:AMBA总线上的传输延迟包括了信号从一个设备传输到另一个设备所需的时间。

具体包括以下几个阶段:- 请求发起:当主设备发送请求时,信号需要经过总线来到达目标从设备。

这个过程涉及总线中的传输延迟,包括信号的传输速度和总线的带宽。

- 寻址:一旦请求到达目标从设备,目标设备需要解析请求并确定具体的寻址信息,以确定数据的来源或目标地址。

这个解析过程可能需要一定的时间。

- 响应返回:从设备接收到请求后,需要进行相应的操作,并将结果或响应发送回主设备。

这个过程也会产生一定的延迟。

降低传输延迟的方法包括提高总线的工作频率、增加总线的带宽、优化总线协议和信号传输机制等。

例如,采用更高速的总线规范(如AMBA AXI),使用更快的总线时钟频率,以及采用高性能的总线接口和物理层技术(如串行化)等。

2. 处理延迟:除了传输延迟外,AMBA总线上的处理延迟还包括了数据在从设备内部进行处理所需的时间。

这个延迟取决于从设备的性能和处理能力,例如从设备内部的存储器读写延迟、计算或操作的执行时间等。

amba手册

amba手册

AMBA(Advanced Microcontroller Bus Architecture)是一种高级微控制器总线架构,它定义了高性能嵌入式微控制器的通信标准。

以下是AMBA手册的主要内容:

一、AMBA概述

AMBA是一种总线架构,用于连接和通信各种IP核和外设。

它不是芯片与外设之间的接口,而是ARM内核与芯片上其他元件进行通信的接口。

AMBA包括多种总线类型,如AHB、ASB、APB和AXI等,这些总线类型提供了不同的性能和功能。

二、AMBA的应用

AMBA被广泛应用于各类芯片和集成电路中,包括微控制器、数字信号处理器(DSP)以及通信和消费电子等多种应用。

它为这些应用提供了优秀的性能表现。

三、AMBA的版本历史

AMBA协议手册介绍了AMBA版本的历史,从最初的AMBA 到现在的AMBA ,每一版都进行了改进和扩展,以适应不断发展的微控制器和集成电路技术。

四、AMBA的总线类型

AMBA手册详细介绍了各种总线类型,包括AHB、ASB、APB和AXI等。

每种总线类型都有其特点和适用范围,可以根据实际需求选择适合的总线类型。

五、AMBA的IP核和外设

AMBA手册还介绍了各种IP核和外设,这些是构成微控制器和集成电路的基本元件。

手册中详细描述了每个IP核和外设的特点和功能,以及如何使用它们来实现高性能的嵌入式系统。

总的来说,AMBA手册是一本非常全面的参考资料,它详细介绍了AMBA 的各个方面,包括概述、应用、版本历史、总线类型、IP核和外设等。

对于从事嵌入式系统设计和开发的人员来说,这是一本非常有价值的参考资料。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AMBA总线介绍AMBA 2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。

AHB的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。

AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。

AHBAHB=Advanced High Performance Bus,译作高级高性能总线。

如同USB (Universal Serial Bus)一样,也是一种总线接口。

特性:突发连续传输分步传输单周期内主控制器处理单时钟边沿操作非三态操作支持64位,128位总线AHB主要用于高性能模块(如CPU、高速RAM、Nand Flash DMA和DSP等)之间的连接,如图一所示。

作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作;非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;可配置32位~128位总线宽度;支持字节、半字和字的传输。

AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

基础结构则由仲裁器(arbiter)、主模块到从模块的多路器、从模块到主模块的多路器、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummy Master)所组成。

其互连结构如图二所示AHB主控制器:主控制器可以通过地址和控制信息,可以进行初始化,读,写操作。

在同一时间,总线上只能有一个主控制器。

AHB从设备:从设备通常是指在其地址空间内,响应主控制器发出的读写控制操作的被动设备。

通过操作的成功与否反馈给其主控制器,完成数据的传输控制。

AHB仲裁器:仲裁器根据用户的配置,确保在总线上同一时间只有一个主控制器拥有总线控制权限。

AHB总线上只能有一个仲裁器。

AHB译码器:译码器解析在总线上传输的地址和控制信息。

AHB总线上只能有一个译码器。

任一时间周期只有一个Master可以接入总线,对其指定Slav e进行读写操作。

总线统一规划slave的地址,译码器根据地址选择哪slav e与master进行数据通信。

授权访问机制通过多路选择器实现:Arbiter将获得授权的master序号传输给地址和写数据多路,以选择哪个master接入总线;地址译码器根据master需要访问的地址选择master,并为写数据多路提供控制信号以选通相应的slave。

AHB总线通过DMA和DSP,允许在总线上存在一个或多个主控制器。

虽然APB总线上可以挂接慢速外设,但是也允许在AHB上挂接一些慢速外设作为从设备,不过它们通常还是挂接在APB总线上。

针对Soc设计中IP复用问题提出了一种新的解决办法。

传统的方法是将特定功能模块的非标准接口标准化为AHB主/从设备接口。

本文提出了一种新的基于ARM的Soc通用平台设计寄存器总线标准接口,这种设计使整个系统的结构清晰,增强系统的通用性与系统中功能模块的可移植性。

ASBASB总线主要用于高性能系统模块。

ASB是可用于AHB不需要的高性能特性的芯片设计上可选的系统总线。

ASB也支持高性能处理器,片上内存,片外内存提供接口和慢速外设。

ASB总线是位于APB总线架构之上的用于高性能的总线协议,它有如下特点:突发连续传输单管道数据传输多总线主控制器ASB总线通过DMA和DSP,允许在总线上存在一个或多个主控制器。

虽然APB总线上可以挂接慢速外设,但是也允许在ASB上挂接一些慢速外设作为从设备,不过它们通常还是挂接在APB总线上。

APBAPB总线接口协议是AMBA协议层次结构中的一部分,它是高度优化的连接低功耗外设的精简接口。

APB看起来是一个本地的二级总线接口协议,用作AHB,ASB总线协议的从设备接口。

APB桥是从控制器模块用来保证不同总线数据的有效传输和不同总线上控制信号的转发处理。

APB应该用于连接低带宽,且不需求高性能数据传输的外设。

最新的APB 总线协议规定了所有的信号传递都发生在时钟的上升沿。

这样设计有以下优势:易于实现高频率操作performance is independent of the mark-space ratio of the clock 通过单时钟操作简化静态时序no special considerations are required for automatic test insertion 许多ASIC库在上升沿寄存器有更好的选择简化整合的时钟模拟器上述的优势也说明APB总线可以更好的链接最新的AHB总线接口。

APB总线协议包含一个APB桥,它用来将AHB,ASB总线上的控制信号转化为APB 从设备控制器上可用信号。

APB总线上所有的外设都是从设备,这些从设备有以下特点:接收有效的地址和控制访问当APB上的外设处于非活动状态时,可以将这些外设处于0功耗状态译码器可以通过选通信号,提供输出时序(非锁定接口)访问时可执行数据写入APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。

其特性包括:两个时钟周期传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号。

1)系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。

2)当有传输要进行时,PSELx=1,PENABLE=0,系统进入SETUP状态,并只会在SETUP 状态停留一个周期。

当PCLK的下一个上升沿时到来时,系统进入ENABLE 状态。

3)系统进入ENABLE状态时,维持之前在SETUP 状态的PADDR、PSEL、PWRITE 不变,并将PENABLE置为1。

传输也只会在ENABLE状态维持一个周期,在经过SETUP 与ENABLE状态之后就已完成。

之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

转换大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。

主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。

另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。

虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。

AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。

APB 桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。

其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

特性总结AHB特性:高性能,数据传输,多总线主控制器,突发连续传输,分步传输ASB特性:高性能,数据传输,多总线主控制器,突发连续传输APB特性:低功耗,寻址控制,支持简单接口协议,支持多种外设APB通过桥接高带宽、高性能总线,提供基本的微控制器二级总线,通常该总线上的外设有以下特点:支持映射寄存器接口对带宽没有很高的要求通过编程实现对外设进行控制AMBA、AHB、APB总线简介作者 adamzhao 日期 2006-11-16 19:33:00AMBA简介随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。

数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。

在基于IP复用的SoC设计中,片上总线设计是最关键的问题。

为此,业界出现了很多片上总线标准。

其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。

AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

AMBA片上总线AMBA 2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。

AHB 的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。

AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。

下面将简要介绍比较重要的AHB和APB总线。

基于AMBA的片上系统一个典型的基于AMBA总线的系统框图如图3所示。

大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。

主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。

另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。

虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL 设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。

AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。

APB 桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。

其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生 APB外围设备的选择信号,从而实现AHB协议到APB 协议的转换。

==================================================================================================================================AHB简介AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC 的片上系统总线,它包括以下一些特性:单个时钟边沿操作;非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;可配置32位~128位总线宽度;支持字节、半字节和字的传输。

AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

基础结构则由仲裁器(arbiter)、主模块到从模块的多路器、从模块到主模块的多路器、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummy Master)所组成。