半导体芯片封装之贴片键合概述-聂仁勇

芯片封装键合技术

芯片封装键合技术芯片封装键合技术是电子行业中的关键技术之一。

它将芯片与封装材料紧密结合,为芯片提供保护和连接功能。

通过键合技术,芯片能够与外部电路进行稳定可靠的连接,实现信号传输和电力供应。

本文将从键合技术的原理、应用和发展前景三个方面进行探讨。

我们来了解一下芯片封装键合技术的原理。

键合技术主要包括金线键合和焊球键合两种方式。

金线键合是将金线通过高温和高压的方式与芯片的金属引脚进行焊接,实现电信号的传输和电力的供应。

焊球键合则是将焊球与芯片的金属引脚相连接,通过熔接的方式实现信号和电力的传输。

这两种键合方式都需要高精度的设备和工艺控制,以确保键合的可靠性和稳定性。

芯片封装键合技术在电子产品中的应用非常广泛。

几乎所有的电子产品都需要使用芯片,而芯片封装键合技术则是保证芯片与外部电路连接的关键环节。

无论是手机、电脑还是家用电器,都离不开芯片封装键合技术的支持。

而随着物联网、人工智能等新兴技术的快速发展,对芯片封装键合技术的需求也越来越高。

因此,芯片封装键合技术的应用前景非常广阔。

让我们展望一下芯片封装键合技术的发展趋势。

随着电子产品的功能不断增强和体积不断缩小,对芯片封装键合技术的要求也越来越高。

未来的发展方向主要包括高密度键合技术、无铅焊接技术和可靠性测试技术等方面。

高密度键合技术能够在有限的空间内实现更多的引脚连接,从而提高芯片的集成度和性能。

无铅焊接技术则是为了减少对环境的污染,提高产品的可持续性。

可靠性测试技术则是为了确保芯片封装键合的质量,提高产品的可靠性和寿命。

芯片封装键合技术在电子行业中起着至关重要的作用。

它不仅保证了芯片与外部电路的可靠连接,还为电子产品的功能实现提供了基础支持。

随着科技的不断进步,芯片封装键合技术也在不断创新和发展,为电子行业的进步做出了重要贡献。

相信在不久的将来,芯片封装键合技术将会取得更大的突破和发展,为人们的生活带来更多的便利和创新。

键合技术概述

引言概述在现代电子技术领域,键合技术是一项关键技术,广泛应用于集成电路、光电子器件、微电子封装等领域。

键合技术的目的是将两个或多个物体通过键合技术放置在一起,以实现电子设备的电连接、信号传递和机械强度的提供。

本文将深入探讨键合技术的原理、分类、应用以及未来发展方向。

正文内容1. 键合技术原理1.1 金属键合技术原理金属键合技术是一种通过热压、焊接或化学反应等方式将两个金属材料永久性连接在一起的技术。

其原理主要基于金属材料的导电性和可塑性,在一定温度和压力下,金属材料之间的分子间力使得两者相互结合。

1.2 硅键合技术原理硅键合技术是应用于微电子封装领域的一种关键技术。

其原理基于硅材料在特定温度和压力下的化学反应,通过硅键合技术可以将芯片与载体物理上固定在一起,并且电连接的同时形成较强的机械支撑。

2. 键合技术分类2.1 金属键合技术分类金属键合技术可以进一步分为焊接、压合和电极化学键合等几类。

焊接是通过热源将两个金属材料熔接在一起,而压合是通过压力将两个金属材料加工成密封形状,并形成固态连接。

电极化学键合则是通过电流和化学反应将两个金属材料连接在一起。

2.2 硅键合技术分类硅键合技术主要可以分为金属键合和焊接键合两类。

金属键合是通过金属材料在高温下的化学反应将芯片与载体连接在一起,而焊接键合则是通过焊料在高温下熔化并冷却形成连接。

3. 键合技术应用3.1 集成电路封装键合技术在集成电路封装中发挥着至关重要的作用。

通过键合技术,可以将芯片与封装基板连接在一起,实现电连接和信号传递,同时提供机械支撑。

不同的键合技术可以适用于不同的封装器件,如BGA、CSP、COB等。

3.2 光电子器件制备光电子器件是利用光与电之间的相互关系进行信息处理和传输的设备。

键合技术在光电子器件制备中起到重要的作用。

例如,在激光器的制备过程中,通过键合技术可以将激光芯片与泵浦源键合在一起,实现光的放大和产生。

而在光通信领域,键合技术也被用于激光二极管和光纤的连接。

芯片封装键合技术

芯片封装键合技术芯片封装键合技术是现代电子工业中一项重要的关键技术。

它是将芯片与封装基板进行连接的过程,用于保护芯片并提供电气连接。

芯片封装键合技术的发展对电子产品的性能和可靠性起着决定性的影响。

键合技术主要包括金线键合和焊球键合两种方式。

金线键合是通过使用金属线将芯片与封装基板连接起来,常用于高性能和高集成度的芯片封装。

而焊球键合则是利用金属焊球将芯片与封装基板连接,适用于尺寸较大的芯片封装。

芯片封装键合技术的发展离不开材料的不断创新。

以金线键合为例,传统的键合技术主要使用铜线,但随着封装密度的提高和芯片尺寸的缩小,铜线的导电性能和可靠性逐渐无法满足需求。

因此,新一代的键合材料如金、银、铝等金属线材开始被广泛应用。

这些新材料具有更好的导电性能和可靠性,可以满足高性能芯片的要求。

键合技术的发展还促进了封装工艺的进步。

随着芯片尺寸的不断缩小,键合工艺也变得更加复杂和精细。

传统的键合方式往往需要手工操作,容易出现误差和不稳定性。

而现代的自动化键合设备可以实现高精度和高效率的键合过程,大大提高了生产效率和产品质量。

芯片封装键合技术在电子工业中的应用广泛。

它不仅用于传统的消费电子产品如手机、平板电脑等,还广泛应用于汽车电子、航空航天、医疗器械等领域。

在这些领域,芯片封装键合技术的可靠性和稳定性尤为重要,因为任何一个小小的键合失效都可能导致严重的后果。

随着科技的不断进步,芯片封装键合技术也在不断发展。

未来,我们可以期待更小型化、高性能和高可靠性的键合技术的出现。

这将进一步推动电子产品的发展,为人们的生活带来更多便利和乐趣。

芯片封装键合技术作为现代电子工业中的重要关键技术,对电子产品的性能和可靠性起着决定性的影响。

它的发展离不开材料和工艺的创新,以及自动化设备的应用。

芯片封装键合技术在各个领域的应用也越来越广泛,为人们的生活带来了巨大的便利和乐趣。

相信随着科技的不断进步,芯片封装键合技术将继续发展,为电子产品的发展注入新的活力。

晶圆键合机键合过程-概述说明以及解释

晶圆键合机键合过程-概述说明以及解释1.引言1.1 概述概述部分的内容如下:晶圆键合机是一种在半导体工艺中广泛应用的关键设备,用于将不同材料的芯片或器件键合在一起。

键合是指通过一定的方法将电子元件或半导体芯片与载体材料进行连接,以实现电路的组合和封装。

在半导体工艺中,晶圆键合机发挥着至关重要的作用。

它通过将两个或多个电子设备组合在一起,实现了器件之间的电气和机械连接。

键合过程中的关键步骤包括选择合适的键合技术、准确放置待键合的芯片和载体、控制键合力和温度,并确保键合界面的质量和可靠性。

晶圆键合机的工作原理主要包括传输、定位、加热、压力控制等关键步骤。

传输系统负责将芯片和载体分别从其它工艺步骤中传送到键合位置;定位系统用于准确的芯片和载体对准;加热系统提供适当的温度以促进键合过程;压力控制系统则确保适当的连接力度。

这些步骤的精确控制对于键合质量的保证至关重要。

晶圆键合机在现代半导体工业中有着广泛的应用。

它被广泛用于芯片封装、光电子器件制造、LED制造、传感器制造等领域。

其应用前景非常广阔,随着电子产品的发展和多功能化需求的增加,晶圆键合机的需求量也在不断增长。

未来,随着半导体技术的不断发展和新材料的出现,晶圆键合机也将不断得到改进和升级。

高密度键合、低温键合、新材料键合等新技术的应用,将进一步提高键合过程的精度和可靠性,以满足更高的工艺要求。

综上所述,晶圆键合机在半导体工艺中具有重要作用。

本篇文章将对晶圆键合机的基本原理、工作流程以及关键要点进行详细介绍,并展望了该技术的应用前景和发展趋势。

1.2 文章结构文章结构部分的内容可以包括如下内容:文章结构部分旨在介绍本文的整体结构安排,让读者能够清晰地了解文章的组织架构和内容安排。

本文按以下章节展开:第一章引言:本章主要对晶圆键合机键合过程进行引言,包括对整个主题的概述、文章的结构和目的。

第二章正文:本章主要讲述晶圆键合机键合过程的基本原理、工作流程和关键要点。

晶圆级封装结构及其制造方法[发明专利]

![晶圆级封装结构及其制造方法[发明专利]](https://img.taocdn.com/s3/m/bb0ff4290c22590102029dfc.png)

专利名称:晶圆级封装结构及其制造方法专利类型:发明专利

发明人:廖宗仁

申请号:CN201310058953.9

申请日:20130225

公开号:CN103681534A

公开日:

20140326

专利内容由知识产权出版社提供

摘要:本发明揭露一半导体封装结构,该结构包含一晶粒、复数条焊线、一封胶体以及复数个第一外部连接端子。

晶粒包含一有源表面及一背表面;各焊线的一第一端连接晶粒的背表面,相对于第一端的一第二端与有源表面电连接;封胶体覆盖晶粒的背表面及焊线,其中各焊线的局部未被覆盖。

第一外部连接端子设置于封胶体之上,并分别包覆未被封胶体覆盖的焊线且电连接焊线。

申请人:南茂科技股份有限公司

地址:中国台湾新竹

国籍:CN

代理机构:北京市铸成律师事务所

代理人:孟锐

更多信息请下载全文后查看。

用于半导体封装工艺中的芯片键合解析2024

引言概述:半导体封装工艺中的芯片键合是将芯片与封装基板连接的关键步骤,其质量与性能直接影响着芯片和封装器件的可靠性和稳定性。

本文将详细阐述芯片键合解析的相关内容,主要包括键合材料的选择、键合过程的分析、键合参数的调控、键合质量的检测和键合故障的分析。

正文内容:1. 键合材料的选择1.1 材料特性的分析键合材料应具备良好的导电性、尺寸稳定性、耐高温性以及与芯片和封装基板的匹配性。

本部分将对键合材料的导电性、热膨胀系数、熔点以及界面相容性进行详细分析。

1.2 材料的选择原则基于材料特性的分析,我们需要根据芯片和封装基板的特性选择合适的键合材料。

在综合考虑导电性、尺寸稳定性和热膨胀系数的基础上,应选择熔点适中的键合材料,并考虑其与芯片和封装基板之间的界面相容性。

2. 键合过程的分析2.1 键合方式的选择芯片键合主要包括焊接键合和金线键合两种方式。

本部分将详细比较这两种键合方式的优缺点,并针对不同的芯片和封装要求给出相应的选择建议。

2.2 键合条件的控制在进行芯片键合过程中,键合条件的控制十分重要。

本部分将详细阐述温度、压力和时间对键合质量的影响,并提供合理的键合条件控制策略。

3. 键合参数的调控3.1 焊点形状的调控键合焊点形状的调控对芯片键合质量具有重要作用。

本部分将详细阐述焊点形状调控的方法,包括键合力的调整、金线直径的选择以及焊点面积的控制等。

3.2 变形与应力的控制芯片键合过程中容易出现变形和应力集中等问题,影响键合质量。

本部分将详细阐述键合过程中变形和应力的产生原因,并给出相应的控制方法,如加强键合支撑、优化键合布局等。

4. 键合质量的检测4.1 键合强度的检测键合强度是评价键合质量的重要指标之一。

本部分将详细介绍键合强度的测试方法,如剪切测试、拉伸测试和超声波检测等。

4.2 金线位置和质量的检测除了键合强度,金线位置和质量也是评价键合质量的重要指标。

本部分将阐述金线位置的检测方法,如显微镜观察和光学检测等,并介绍金线质量的检测方法,如电阻测试和尺寸测量等。

半导体芯片封装之贴片键合概述-聂仁勇

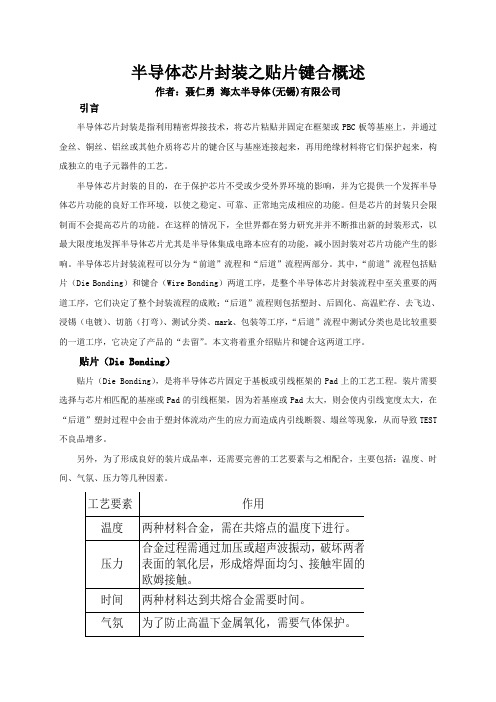

半导体芯片封装之贴片键合概述作者:聂仁勇海太半导体(无锡)有限公司引言半导体芯片封装是指利用精密焊接技术,将芯片粘贴并固定在框架或PBC板等基座上,并通过金丝、铜丝、铝丝或其他介质将芯片的键合区与基座连接起来,再用绝缘材料将它们保护起来,构成独立的电子元器件的工艺。

半导体芯片封装的目的,在于保护芯片不受或少受外界环境的影响,并为它提供一个发挥半导体芯片功能的良好工作环境,以使之稳定、可靠、正常地完成相应的功能。

但是芯片的封装只会限制而不会提高芯片的功能。

在这样的情况下,全世界都在努力研究并并不断推出新的封装形式,以最大限度地发挥半导体芯片尤其是半导体集成电路本应有的功能,减小因封装对芯片功能产生的影响。

半导体芯片封装流程可以分为“前道”流程和“后道”流程两部分。

其中,“前道”流程包括贴片(Die Bonding)和键合(Wire Bonding)两道工序,是整个半导体芯片封装流程中至关重要的两道工序,它们决定了整个封装流程的成败;“后道”流程则包括塑封、后固化、高温贮存、去飞边、浸锡(电镀)、切筋(打弯)、测试分类、mark、包装等工序,“后道”流程中测试分类也是比较重要的一道工序,它决定了产品的“去留”。

本文将着重介绍贴片和键合这两道工序。

贴片(Die Bonding)贴片(Die Bonding),是将半导体芯片固定于基板或引线框架的Pad上的工艺工程。

装片需要选择与芯片相匹配的基座或Pad的引线框架,因为若基座或Pad太大,则会使内引线宽度太大,在“后道”塑封过程中会由于塑封体流动产生的应力而造成内引线断裂、塌丝等现象,从而导致TEST 不良品增多。

另外,为了形成良好的装片成品率,还需要完善的工艺要素与之相配合,主要包括:温度、时间、气氛、压力等几种因素。

因此装片工序有两大质量要求:产品质量要求和工艺质量要求。

装片的产品质量要求:芯片与引线框架的连接机械强度高,导热性能好(△VBE小)和导电性能好(V CEsat 小),装配平整,焊料厚度适中,定位准确,能满足键合的需要,能承受键合或塑封时可能有的高温,保证器件在各种条件下使用都具有良好的可靠性。

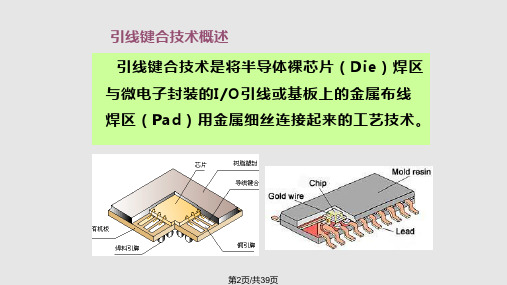

集成电路芯片封装技术芯片互连技术.pptx

第8页/共39页

WB线材及其可靠度

键合对金属材料特性的要求: 可塑性好,易保持一定形状,化学稳定性好;

尽量少形成金属间化合物,键合引线和焊盘金 属间形成低电阻欧姆接触。

柯肯达尔效应:两种扩散速率不同的金属交互 扩散形成缺陷:如Al-Au键合后,Au向Al中迅 速扩散,产生接触面空洞。通过控制键合时间 和温度可较少此现象。

冲制标准定位传送孔 Cu箔清洗 Cu箔叠层 Cu箔涂光刻胶(双面)

刻蚀形成Cu线图样 导电图样Cu镀锡退火

第19页/共39页

内引线键合 (ILB)

内引线键合是将裸芯片组装到TAB载带上的技术,通常采 用热压焊方法。焊接工具是由硬质金属或钻石制成的热电极。 当芯片凸点是软金属,而载带Cu箔引线也镀这类金属时,则 用“群压焊”。

第26页/共39页

倒装芯片键合技术

倒装芯片键合(FCB)是指将裸芯片面朝下,芯片焊区与 基板焊区直接互连的一种键合方法:通过芯片上的凸点直接 将元器件朝下互连到基板、载体或者电路板上。而WB和TAB 则是将芯片面朝上进行互连的。由于芯片通过凸点直接连接 基板和载体上,倒装芯片又称为DCA(Direct Chip Attach )

连主要工艺方法,用于下列封装: ·陶瓷和塑料BGA、SCP和MCP ·陶瓷和塑料封装QFP ·芯片尺寸封装 (CSP)

第3页/共39页

WB技术作用机理

提供能量破坏被焊表面的氧化层和污染物,使焊区金 属产生塑性变形,使得引线与被焊面紧密接触,达到原子 间引力范围并导致界面间原子扩散而形成焊合点。引线键 合键合接点形状主要有楔形和球形,两键合接点形状可以 相同或不同。

芯片封装键合技术

芯片封装键合技术芯片封装键合技术是现代电子领域中不可或缺的一项技术,它是将芯片与封装基板连接在一起的重要工艺。

封装键合技术的发展,不仅大大提高了芯片的可靠性和性能,也为电子产品的小型化、高性能化提供了有力支持。

我们来了解一下芯片封装键合技术的基本原理。

芯片封装键合技术是通过将芯片与封装基板进行连接,实现芯片与封装基板之间的信号传输与电力供应。

在封装键合过程中,通常会使用金线或铜线将芯片与封装基板的导电线路连接起来。

这些金线或铜线需要经过精确的定位和焊接,以确保连接的可靠性和稳定性。

芯片封装键合技术的发展经历了多个阶段。

最早期的键合技术是采用金线键合,该技术在芯片封装过程中使用金线作为连接材料,具有良好的导电性能和可靠性。

随着电子行业的快速发展,铜线键合技术逐渐取代了金线键合技术,成为主流的封装键合技术。

铜线键合技术相比金线键合技术具有更高的导电性能和更低的电阻,能够满足高性能电子产品的需求。

在芯片封装键合技术中,除了金线或铜线的选择外,还需要考虑键合的方式。

一般来说,芯片封装键合技术主要包括焊线键合和焊球键合两种方式。

焊线键合是通过焊接金线或铜线来实现芯片与封装基板的连接,适用于封装密度较低的芯片。

而焊球键合则是通过焊接小球形的金属颗粒来实现连接,适用于封装密度较高的芯片。

芯片封装键合技术的应用范围非常广泛。

从智能手机、平板电脑到汽车电子、医疗设备,几乎所有的电子产品都离不开芯片封装键合技术的支持。

通过高精度的键合技术,可以实现电子产品的小型化和高性能化,满足人们对电子产品体验的不断追求。

总的来说,芯片封装键合技术是现代电子领域中不可或缺的一项技术。

它通过将芯片与封装基板连接在一起,实现了芯片与封装基板之间的信号传输和电力供应。

随着电子行业的不断发展,芯片封装键合技术也在不断创新与进步,为电子产品的小型化、高性能化提供了坚实的基础。

无论是智能手机还是汽车电子,都离不开芯片封装键合技术的支持,它已成为电子产品制造的重要工艺之一。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

半导体芯片封装之贴片键合概述作者:聂仁勇海太半导体(无锡)有限公司引言半导体芯片封装是指利用精密焊接技术,将芯片粘贴并固定在框架或PBC板等基座上,并通过金丝、铜丝、铝丝或其他介质将芯片的键合区与基座连接起来,再用绝缘材料将它们保护起来,构成独立的电子元器件的工艺。

半导体芯片封装的目的,在于保护芯片不受或少受外界环境的影响,并为它提供一个发挥半导体芯片功能的良好工作环境,以使之稳定、可靠、正常地完成相应的功能。

但是芯片的封装只会限制而不会提高芯片的功能。

在这样的情况下,全世界都在努力研究并并不断推出新的封装形式,以最大限度地发挥半导体芯片尤其是半导体集成电路本应有的功能,减小因封装对芯片功能产生的影响。

半导体芯片封装流程可以分为“前道”流程和“后道”流程两部分。

其中,“前道”流程包括贴片(Die Bonding)和键合(Wire Bonding)两道工序,是整个半导体芯片封装流程中至关重要的两道工序,它们决定了整个封装流程的成败;“后道”流程则包括塑封、后固化、高温贮存、去飞边、浸锡(电镀)、切筋(打弯)、测试分类、mark、包装等工序,“后道”流程中测试分类也是比较重要的一道工序,它决定了产品的“去留”。

本文将着重介绍贴片和键合这两道工序。

贴片(Die Bonding)贴片(Die Bonding),是将半导体芯片固定于基板或引线框架的Pad上的工艺工程。

装片需要选择与芯片相匹配的基座或Pad的引线框架,因为若基座或Pad太大,则会使内引线宽度太大,在“后道”塑封过程中会由于塑封体流动产生的应力而造成内引线断裂、塌丝等现象,从而导致TEST 不良品增多。

另外,为了形成良好的装片成品率,还需要完善的工艺要素与之相配合,主要包括:温度、时间、气氛、压力等几种因素。

因此装片工序有两大质量要求:产品质量要求和工艺质量要求。

装片的产品质量要求:芯片与引线框架的连接机械强度高,导热性能好(△VBE小)和导电性能好(V CEsat 小),装配平整,焊料厚度适中,定位准确,能满足键合的需要,能承受键合或塑封时可能有的高温,保证器件在各种条件下使用都具有良好的可靠性。

装片的工艺质量要求:芯片位置正确;芯片无沾污、无碎裂、无划伤、无倒装、无误装、无扭转;引线框架无污染、无气泡、无氧化、无变形;焊料熔融良好,无氧化、无漏装、无结球、无翘片、无空洞。

良好的成品率不但要有合适的工艺条件,而且要有理想的合金材料,理想的材料应有以下特点:1、在半导体晶片中的溶解度高,这样制成的欧姆接触电阻就小;2、具有较低的蒸气压,即在合金温度下不应大量蒸发;3、熔点应低于芯片表面的铝与半导体的合金温度,否则会影响器件的电参数;4、机械性能良好,要有延展性而且热膨胀性能与半导体材料、衬底材料的热膨胀性能相接近或相匹配;但装片的方式又多种多样,目前比较主流的方式主要有以下4种,分别是:树脂粘接(分导电或非导电树脂)、共晶焊接、银浆或银泥烧结和铅锡合金焊接。

1)树脂粘接(分导电或非导电树脂)常用的树脂由环氧、聚酰亚胺、酚醛、聚胺树脂及有机硅树脂组成作为粘接剂,加入银粉的称导电树脂(或导电胶);有的加入氧化铝粉填充料,导热性好,绝缘性也好,称非导电树脂(或非导电胶),适用于集成电路与小功率的晶体管。

树脂粘接会产生一系列的问题:生产过程中因芯片放置不当(如翘片等)形成空洞率(如图1所示)过高(后面章节即将介绍到的合金焊料装片更容出现这样的情况);空洞率过高直接导致热阻偏大、高应力;树脂滴在引脚上造成搭桥现象,引起内连接问题,在内引线键合时造成框架翘曲,使得一边内引线应力大,一边内引线应力小。

图1-a 装片空洞率不合格样品图1-b 装片空洞率较小合格样品(空洞大、集中)(空洞小、分散且少)树脂粘接装片后需要进行固化处理,环氧树脂粘贴剂的固化条件一般是150℃,固化时间为半小时(此数据为KEC-W TO-220IS-4的参数);聚酰亚胺粘贴剂的固化温度要高一些,时间也更长;不同粘贴剂的固化工艺条件都不尽相同,需要相关的实验来确定。

2)共晶焊接共晶焊接是利用芯片背面的金硅合金和基座或引线框架上镀的金属(银层)在高温氮保护和400~440℃高温下形成合金的办法固定芯片,这种方法需要有相应的背面蒸金的芯片才能进行焊接,导电导热性能都很好,适用于较小尺寸的芯片。

特别适用于功率三极管芯片,这样的装片方式比合金焊料装片方式更有助于工作中芯片的散热。

芯片背面不同的合金材料在装片过程中芯片周围将出现不同的溢料现象,五层背金、六层背金芯片的周围没有合金溢出痕迹,而AuGe背金芯片的周围则有明显的合金溢出痕迹。

(图2)图a 五层背金、六层背金图b AuGe背金图2 不同合金背金现象共晶焊接装片工艺也存在一定的缺陷,因为共晶装片是要靠机械手向下的压力才能有好的共晶出现的,如果装片的机械手上吸嘴的截面与芯片不平行,则会导致芯片的受力不均,从而出现芯片一边已与银形成合金粘牢,另一边未粘牢的现象。

3)银浆或银泥烧结银浆或银泥烧结是利用银浆或银泥中的氧化银,高温下分解还原成银来固定芯片,导电和导热性能均较好。

适用于小功率晶体管和结深较浅的超高频或微波小功率晶体管。

银浆或银泥烧结方式装片也需采用氮气保护,烧结温度为380~400℃,这种方法最大的特点是成本低、效率高,但高低温热性能、电耐久性、工艺重复性差。

4)铅锡合金焊接铅锡合金焊接是利用铅锡合金作焊料,把背面已蒸金(银)或镀镍的芯片,焊接在镀银或镀镍的基座或引线框架上,这种装片方式的导电导热性比共晶都要稍差些,但成本更低,适用于中大功率晶体三极管及集成电路。

现在,随着欧盟等一些地区或国家相继加大了对环保的投入,大力发展无铅绿色环保产品。

为了顺应历史发展趋势,科学家们研制出了新型的合金焊料,即在原有的铅锡合金的基础上,用一定比例的“锑+银”或“锑+镍+磷”来替代铅。

而且后两者比前者有着巨大的优势:首先,是达到了绿色环保的目的。

其次,后两者形成的合金熔点比前者要低100℃左右,节约了大量的电力能源,符合目前国家正在大力倡导的节能减排要求。

第三,后两者可以直接与裸铜在氢氮混合保护气体下焊接,这样就无需再在铜材上镀银或镍,简化了基座或引线框的生产工序,节约了大量资源,减少了成本,也减轻了对环境的污染。

第四,后两者在高温、保护气氛下的流动性、浸润性比前者要好,有助于装片空洞率的降低,提高产品的成品率。

(图3显示了装片后两种焊料的不同状态)图a 理想的装配图b 非理想的装配图3 两种焊料的不同状态键合(Wire Bonding)键合就是用金丝、铜丝或铝丝将半导体器件芯片表面的电极引线与底座或引线框架外引线相连接起来。

键合的目的是把半导体器件芯片表面的电极与引线框架的外引线连接起来(如图4)。

图4 键合的实例照片与装片相对应的是,键合也有其相应的工艺要素,分别是超声功率、压力、时间、温度(相对于金、铜丝键合而言)。

它们各自的作用见表2.表2 键合工艺要素及其作用因此键合工序也有两大质量要求:产品质量要求和工艺质量要求。

键合的产品质量要求:内引线与芯片和外引线要形成低电阻欧姆接触,压点的位置准确,结合力要强;内引线要有足够的电流容量,抗拉强度要强,有理想的压点和弧度。

键合的工艺质量要求:配线正确(线径、根数、极性)、无漏键、无错键;压点位置正确、形状理想,无键偏、无根切、无虚焊;弧度合理,无塌丝、无拉丝、无尾丝;测克强度符合要求。

良好的成品率不但要有合适的工艺条件,而且要有理想的引线材料,理想的材料应有下特点:1、能与半导体材料形成低电阻的欧姆接触;2、化学性能稳定,不会形成有害的化合物;3、与半导体材料之间的结合力强;4、电阻率低,具有良好的导电性能;5、可塑性好,容易焊接;6、在键合过程中能保持一定的几何形状。

通过以上分析,理想的引线材料有:1、纯铝丝2、硅铝丝3、金丝目前,主要的键合技术有:热压键合(Thermocompression Bonding T/C Bonding)(T:330~350 ℃)、热超声波键合(Thermosonic Bonding, T/S Bonding)(T:250℃左右)和超声波键合(Ultrasonic Bonding, U/S Bonding)(T:常温)三种。

1) 热压键合热压焊接的原理:首先,由于金属丝和芯片上的铝层同时受热受压,接触面便产生塑性形变并破坏了界面的氧化膜,使两者接触面几乎接近原子引力范围,金属丝表面原子与铝层表面原子之间产生吸引力而达到键合的目的。

其次,是由于金属丝和铝层表面的不平整,加压后高低不平处相互填充而产生弹性嵌合作用,使两者紧密结合在一起。

因此加压后接触面积越大,结合牢固度也越好。

热压焊和电阻焊、锡焊、铜焊的区别:热压焊和电阻焊的区别在于热压焊时没有电流通过材料。

热压焊与锡焊和铜焊的区别是热压焊不用助熔剂或第三种材料热压焊接是利用加热和加压力,使金属丝和芯片的铝层焊在一起,将芯片的电极引线和管座相应电极外引线连接起来。

2) 热超声波键合热超声键合是利用加热、加压力和加超声的方法,三者相结合使金属丝和芯片的铝层焊在一起,将芯片的电极引线和管座相应电极外引线连接起来。

主要适用于金丝或铜丝等材质较软、线径较细的引线材料。

下面以相关图例介绍一下热超声键合的相关原理(以“金丝球焊”为例)。

一、金丝球焊的分解过程(图5):【图5金丝球焊的分解过程】二、金丝球焊过程(图6):【图6金丝球焊过程】三、金丝球焊合格焊点形状与不合格焊点形状的对比(图7):图a 合格的球焊点图b 楔焊点形状图c 不合格的球焊点图d 楔焊点形状【图7金丝球焊合格焊点形状与不合格焊点形状的对比】四、理想的金丝球焊弧度形状(图8)【图8 理想的金丝球焊弧度形状】以上大致介绍了热超声键合的相关原理及相关技术参数间的关系等。

3)超声波键合超声波键合是利用加压力和加超声的方法,两者相结合使金属丝和芯片的铝层焊在一起,将芯片的电极引线和管座相应电极外引线连接起来。

主要适用于铝丝。

铝丝键合与金丝球焊相比,除了能提高质量和保证器件在高温下稳定可靠工作以外,还具有:1、不需加温,在常温下即可进行。

这对器件本身的特性不会的影响,而且能提高焊接速度。

2、不必加电流,不会发生熔化,也不需要用焊剂,所以对材料的物理、化学性能没有任何影响,也不会形成任何化合物而影响器件的可靠性。

(电阻焊、锡焊)3、可根据不同需要,改变键合条件来焊接粗细不等的铝丝和宽的铝带。

4、焊接强度高于金丝焊接。

5、材料成本低。

下面以相关图例介绍一下超声波键合的相关原理(以铝丝键合技术为例)。

一、铝丝键合的过程(图9):【图9铝丝键合的过程】三、铝丝键合合格压点与不合格压点形状的比较(V型槽劈刀)(图10)图图a 合格图b 不合格【图10 铝丝键合压点形状】4)键合常见的质量问题及可能原因一、键合常见的质量问题:1、虚焊;2、断丝;3、塌丝;4、键偏;5、键合应力过大损伤硅片。