第6章(中央处理器)2012

第六章中央银行支付清算服务讲述案例

支付时隔降至最低(甚至为零)

RTGS系统处理所有支付清算均是不可

变更和无条件的终局性的清算

39

RTGS系统设计4种支付信息发送和资金

清算流程,对支付时隔的长度及支付 风险控制有不同的影响:

40

1、V型结构 付款行先将完整的支付信息传送给中 央银行,央行完成资金汇划清算后, 再将完整的支付信息发送收款行。如

同业间清算(包括联行清算)是金 融机构之间为实现客户委办业务和

自身需要所进行的债权债务清偿和

资金划转。

28

第二节 中央银行的支付清算运作

一、中央银行在一国支付清算体系 中的地位

作为支付体系的使用者 作为支付体系的成员 作为支付服务的提供者 作为公共利益的保护人

29

中清 央算 银中 行的 支地 付位

58

纽约清算所同业银行支付系统 (CHIPS)

CHIPS是世界上最大的私营支付清算系统,属

于纽约清算所协会所有并经营。

CHIPS 是一个著名的国际大额美元支付清算系

统。1970年纽约清算所建立了中央计算机转换 系统CHIPS,并于同年4月投入运行,为同业银 行提供自动化资金转移服务。经过几十年的运 行,CHIPS已经成为跨国美元交易的主要清算 中心。目前95%的国际美元交易通过其进行支 付清算。

中央银行拥有并经营 私营清算机构拥有并经营

按支付系统 服务对象

大额支付系统 小额支付系统 (零售支付系统 )

按支付系统 服务地区

境内支付系统 国际性支付系统

(三)中央银行支付清算服务 中央银行支付清算服务即指中央银行

作为一国支付清算体系的参与者和管理者,

通过一定的方式、途径,使金融机构之间

的债权和债务清偿及资金转移顺利完成并

计算机组成原理第六章课件白中英版

66MHz的Pentium,基本非流水线总线周期

64÷2×66×106 bps=264 MB/S

66MHz的Pentium,2-1-1-1猝发读周期

32÷5×66×106 B/S=422.4 MB/S

【例1】(1)某总线在一个总线周期中并行传送4个字 节的数据,假设一个总线周期等于一个总线时钟周期, 总线时钟频率为33MHz,则总线带宽是多少?

STROBE*(选通)信号

•输出低有效,才能使打印机接收数据

ACK*(响应)信号

•打印机接收数据结束回送负脉冲响应信号

BUSY(忙状态)信号

•打印机忙于处理接收到的数据,不能接收新的数据

6.3.3 总线数据传送模式

读数据传送:数据由从设备到主设备 写数据传送:数据由主设备到从设备 猝发传送(数据块传送)

演示

每个数据位都需要单独一条传输线。二进制数 “0”或“1”在不同的线上同时进行传送

串行通信

串行通信:将数据分解成二进制位用一条信号 线,一位一位顺序传送的方式

串行通信的优势:用于通信的线路少,因而在 远距离通信时可以极大地降低成本

通信协议(通信规程):收发双方共同遵守

解决传送速率、信息格式、位同步、字符同步、 数据校验等问题

发送8位数据:59H=01011001B,偶校验、两个停止位

6.3.1 总线的仲裁

主设备(Master):控制总线完成数据传输 从设备(Slave):被动实现数据交换 总线仲裁:决定当前控制总线的主设备

•集中仲裁:中央仲裁器负责 •分布仲裁:比较各个主设备仲裁号决定

某一时刻,只能有一个主设备控制总线, 其它设备此时可以作为从设备

6.1中央处理器的结构与功能-计算机系统原理-刘均-清华大学出版社

6.1.2中央处理器的基本结构

在CPU内部,有寄存器组、运算器和控 制器等。

(1)寄存器组

◦ 每一个CPU内部都会设置一些寄存器,用于 保存运算数据或运算结果。在图6.1所示的 计算机中,n个寄存器名称为R0~Rn-1。这些 寄存器需要有数据输入输出的控制信号。 数据输入寄存器的控制信号定义为Rnin,数 据输出寄存器的控制信号定义为Rnout。

6.1中央处理器的结构与功能

计算机系统中,中央处理器(Central Processing Unit,CPU)是计算机工作的指挥 和控制中心。中央处理器是由运算器和控制 器两大部分组成的。控制器的主要功能是从 内存取出指令,对指令进行译码,产生相应 的操作控制信号,控制计算机的各个部件协 调工作。运算器接受控制器的命令进行操作 ,完成所有的算术运算和逻辑运算。控制器 是整个系统的操控中心。在控制器的控制之 下,运算器、存储器和输入、输出设备等部 件构成一个有机的整体。

6.1.2中央处理器的基本结构

(2)运算器

运算器包括算术逻辑单元ALU和暂存器。ALU完成各 种算术运算和逻辑运算。暂存器用于暂存ALU运算的 数据和结果。在图6.1所示的计算机中,Y是ALU的输 入暂存器,存放一个需要ALU运算的数据。Z是ALU的 输出暂存器,存放ALU运算后的结果。暂存器Y有2个 控制信号,数据输入Y的控制信号定义为Yin,数据输 出Y的控制信号定义为Yout。暂存器Z有2个控制信号 ,数据输入Z的控制信号定义为Zin,数据输出Z的控 制信号定义为Zout。ALU有多种运算,控制信号比较 多,图6.1所示计算机中简化这些控制信号,其中+表 示ALU加法控制信号,-表示ALU减法控制信号,1->C0 表构

存储器地址寄存器MAR用来保存当前 CPU所访问的内存单元地址。由于CPU 和内存之间有速度差异,所以必须使用 地址寄存器来保存地址信息,直到内存 读写操作完成。存储器数据寄存器MDR 是CPU和主存及外部设备之间信息传送 的中转站。当通过数据总线向存储器或 外部设备存取数据时,数据暂时存放在 MDR中,因此也称为数据缓冲器。

计算机组成原理(蒋本珊)第六章

第六章1.控制器有哪几种控制方式?各有何特点?解:控制器的控制方式可以分为3种:同步控制方式、异步控制方式和联合控制方式。

同步控制方式的各项操作都由统一的时序信号控制,在每个机器周期中产生统一数目的节拍电位和工作脉冲。

这种控制方式设计简单,容易实现;但是对于许多简单指令来说会有较多的空闲时间,造成较大数量的时间浪费,从而影响了指令的执行速度。

异步控制方式的各项操作不采用统一的时序信号控制,而根据指令或部件的具体情况决定,需要多少时间,就占用多少时间。

异步控制方式没有时间上的浪费,因而提高了机器的效率,但是控制比较复杂。

联合控制方式是同步控制和异步控制相结合的方式。

2.什么是三级时序系统?解:三级时序系统是指机器周期、节拍和工作脉冲。

计算机中每个指令周期划分为若干个机器周期,每个机器周期划分为若干个节拍,每个节拍中设置一个或几个工作脉冲。

3.控制器有哪些基本功能?它可分为哪几类?分类的依据是什么?解:控制器的基本功能有:(1)从主存中取出一条指令,并指出下一条指令在主存中的位置。

(2)对指令进行译码或测试,产生相应的操作控制信号,以便启动规定的动作。

(3)指挥并控制CPU 、主存和输入输出设备之间的数据流动。

控制器可分为组合逻辑型、存储逻辑型、组合逻辑与存储逻辑结合型3类,分类的依据在于控制器的核心———微操作信号发生器(控制单元CU)的实现方法不同。

4.中央处理器有哪些功能?它由哪些基本部件所组成?解:从程序运行的角度来看,CPU 的基本功能就是对指令流和数据流在时间与空间上实施正确的控制。

对于冯·诺依曼结构的计算机而言,数据流是根据指令流的操作而形成的,也就是说数据流是由指令流来驱动的。

中央处理器由运算器和控制器组成。

5.中央处理器中有哪几个主要寄存器?试说明它们的结构和功能。

解:CPU 中的寄存器是用来暂时保存运算和控制过程中的中间结果、最终结果及控制、状态信息的,它可分为通用寄存器和专用寄存器两大类。

计算机组成原理第6章

第6章中央处理器

图 6-6 指令周期与 CPU 周期的包含关系

第6章中央处理器

6. 1. 4 指令执行流程 指令的执行是从取指周期开始的。取指周期主要完成从

内存取出要执行的指令,并使指针指向下一条指令,即 PC=PC+ “ 1 ”,这里的“ 1 ”表示当前这条指令的实际字长。 取指完成后,对指令进行译码,再转入具体的指令执行过程。 指令在执行过程中如果采用间接寻址方式,还需要增加间址 周期,如图 6-5 所示。

第6章中央处理器

3. 时序控制 每一条指令在执行的过程中,必须在规定的时间给出各 部件所需操作控制的信号,才能保证指令功能的正确执行。 因此,时序控制就是定时地给出各种操作信号,使计算机系统 有条不紊地执行程序。 4. 数据加工 数据加工是指对数据进行算术运算、逻辑运算或其他处 理。

第6章中央处理器

第6章中央处理器

图 6-7 所示是一个采用总线结构将运算器、寄存器连 接起来的控制器内部数据通路。其各部件与内部总线 IBUS 和系统总线 ABUS 、 DBUS 的连接方式如图中所示,图中的 “ o ”为控制门,在相应控制信号(信号名称标在“o ”上)的控 制下打开,建立各部件之间的连接。GR 是通用寄存器组, X 和 Z 是两个暂存寄存器。

第6章 中央处理器

教学内容安排•第一章绪论•第二章数码系统•第三章运算方法和运算器•第四章存储系统•第五章指令系统•第六章中央处理器•第七章输入输出设备•第八章输入输出系统第六章中央处理器•6.1CPU的组成及功能• 6.2指令的执行过程• 6.3微程序控制器• 6.4中断系统•*6.5流水结构教学重点和难点•cpu的功能和组成、指令的执行过程和中断系统第六章中央处理器 6.1 CPU的组成与功能•中央处理器(CPU)–是计算机的大脑,计算机的运算、控制都是由它来处理的。

它的发展非常迅速,其主要功能就是控制各部件的协调工作–CPU的四个主要功能:指令控制、操作控制、时间控制、数据加工。

第六章中央处理器 6.1 CPU的组成与功能•CPU的组成–由两个主要部分组成:控制器和运算器。

这两部分功能不同,配合工作。

–运算器的功能:执行所有的算术运算、执行所有的逻辑运算。

–控制器功能有:1、从内存中取出一条指令,并指出下一条指令在内存中的位置。

2、对指令进行译码或测试,并产生相应的操作控制信号。

3、指挥并控制CPU、内存和输入/输出设备之间数据流动的方向。

第六章中央处理器 6.1 CPU的组成与功能•运算器部分–在控制器的控制下完成各种算术和逻辑运算。

第六章中央处理器 6.1 CPU的组成与功能•运算器组成–ALU(由全加器组成),输入:累加器、暂存器,输出:内部数据总线–寄存器:1、通用寄存器组2、标志寄存器3、专用寄存器第六章中央处理器 6.1 CPU的组成与功能•控制器部分–程序计数器PC:功能:完成指令控制、操作控制、时序控制第六章中央处理器 6.1 CPU的组成与功能•控制器组成–程序计数器PC:存放待执行指令在存储器中的地址。

任何程序执行前,应将程序的首地址置入PC中,通常,PC内容顺序加1;遇到转移指令,将转移的目标地址置入PC,即可实现程序转移。

–指令寄存器IR:存放从存储器中取出的待执行的指令。

–指令译码器ID:暂存在IR中的指令,其操作码部分经译码后才能识别当前要执行指令的性质,ID的功能也在于此。

第6章中央处理器(终)

第6章 中央处理器

本章学习内容

• 6.1中央处理器的功能和组成 • 6.2 控制器的组成和实现方法 • 6.3 时序系统与控制方式 • 6.4 微程序控制原理 • 6.5 控制单元的设计 • 6.6 流水线技术 • 6.7 精简指令系统计算机RISC

4

第6章 中央处理器

本章学习要求

• 理解:CPU的功能和主要寄存器

内频=外频×倍频

18

第6章 中央处理器

4.前端总线频率

前端总线通常用FSB表示,它是CPU和外界 交换数据的最主要通道,主要连接主存、显卡等 数据吞吐率高的部件,因此前端总线的数据传输 能力对计算机整体性能作用很大。

在Pentium 4出现之前,前端总线频率与外频 是相同的,因此往往直接称前端总线频率为外频。 随着计算机技术的发展,需要前端总线频率高于 外频,因此采用了QDR(Quad Date Rate)技术 或者其他类似的技术,使得前端总线频率成为外 频的2倍、4倍甚至更高。

CPU 的 字 长 是 指 在 单 位 时 间 内 同 时 处理的二进制数据的位数。CPU按照其处 理信息的字长可以分为:8位CPU、16位 CPU、32位CPU以及64位CPU等。

16

第6章 中央处理器

2.内部工作频率

内部工作频率又称为内频或主频,它是衡

量CPU速度的重要参数。在其他性能指标相同 时,CPU的主频越高,CPU的速度也就越快。 内部时钟频率的倒数是时钟周期,这是CPU中

pro、Pentium Ⅱ/Ⅲ每个时钟周期可以执行3条

或更多的指令。

17

第6章 中央处理器

3.外部工作频率

外部工作频率,也叫前端总线频率或系统 总线时钟频率,它是由主板为CPU提供的基准 时钟频率。由于正常情况下,CPU总线频率和 主存总线频率相同,所以也是CPU与主存交换 数据的频率。

第6章-并行输入输出接口

数据

状态 控制

CPU

I/O 接口 „

Rn

外设

图6-1

I/O接口的基本结构

根据I/O接口的功能,接口电路的典型结构如图6-1所示。接口作为 一个“桥梁”,一边连着系统总线,另一边连着外部设备,是CPU与 外设进行信息交换的中转站。

正如上图所示,每个接口部件都包含一组寄存器,CPU与外设之间 进行数据传输时,各种不同的信息(数据信息、状态信息和控制信息) 进入不同的寄存器。

数据总线(DB ) 中央 处理器 CP U 控制总线(C B ) 地址总线(AB ) I/O 接口 I/O 接口

内存储器

I/O 设备

图1-1

I/O 设备

微机系统结构示意图

一. I/O接口的定义

伴随着计算机技术的飞速发展,各种功能繁多的外设不断出现。这些 外设的组成及工作原理千差万别(机械式、电子式、光电式),所采用的 信号形式也各不相同(数字量、模拟量、开关量),工作速度差异也很大 (高速、中速、低速),„ „ 。由于它们的多样性和复杂性,使得这些 外设不可能像存储器那样直接连在系统总线上,CPU也无法直接对所有外 设进行管理与控制。因此,CPU与外设之间必须有某个中间环节,这就是

2. 独立编址方式 这种方式中,内存地址空间和I/O端口地址是相对独立的。比 如在8086/8088CPU中,其内存地址是从00000H~FFFFFH连续的 1M字节,而I/O地址范围从0000H ~FFFFH ,它们相互独立,互不 影响。同时,设置了专门的IN、OUT等I/O指令。 优点: 不占用内存空间;访问I/O端口的指令格式较短,速度 快,程序可读性强。 缺点:需设置专用指令,这些指令功能较弱; CPU的I/O 控制 逻辑相对比较复杂。

第6章(725)

第6章 中央处理器(CPU)

32

(10) PUSH R0 这条指令实现将寄存器R0中的数据压入到堆栈中。与该

指令相应的执行周期的微操作序列为:

第6章 中央处理器(CPU)

33

(11) POP R0 这条指令实现将堆栈栈顶的数据弹出至寄存器R0中。与

该指令相应的执行周期的微操作序列为:

第6章 中央处理器(CPU)

转地址)。

(4) 重复过程(1)~(3),直到将程序中的所有指令执行完毕 为止。

第6章 中央处理器(CPU)

4

从另一个角度看,指令流和数据流是在主存与CPU内部 寄存器组之间流动的(见图6.1), 所以对这些指令流和数据流

的有效管理也是CPU的基本功能。

第6章 中央处理器(CPU)

5

图 6.1

处理器与主存之间的通信

第6章 中央处理器(CPU)

9

图 6.3

指令周期及CPU操作

第6章 中央处理器(CPU)

10

6.1.3 微操作 1. 微操作与微命令

在指令周期内的CPU行为实际是由一系列微操作(μop)定

义的,这些微操作是将CPU行为或功能分解后的CPU最基本 的操作,分属于不同的指令子周期(CPU周期)。图6.4示出 了一个程序执行的分解过程,它描述了指令周期、CPU周期、 微操作之间的关系。

第6章 中央处理器(CPU)

27

(5) SUB R0,(X) 这条指令实现寄存器R0中的被减数减去存储器地址X间 接寻址的存储单元中的减数、将差值传送至寄存器R0中的功 能。与该指令相应的执行周期的微操作序列为:

第6章 中央处理器(CPU)

28

(6) IN R0,P 这条指令实现从I/O地址为P的I/O设备(接口)中输入数据

第 6 章 控制器原理

2013-12-4

19

• 在CPU中可以单独设置程序计数器,也可以指 定通用寄存器中的某一个作为PC使用。 • 程序顺序执行时的PC增量可以通过PC本身的 计数逻辑实现,也可以由运算器的ALU实现。 不同机器,实现方法可有所不同。

2013-12-4

20

• (2) 指令寄存器 IR • 指令寄存器用于存放当前正在执行的指令。 • 当指令从主存取出后,经MDR传送到指令寄存器 中,以便实现对一条指令执行的全部过程的控制。

2013-12-4

24

• (3)时序信号发生器 • 时序信号发生器用于产生机器所需的各种时序 信号,以便控制有关部件在不同的时间完成不 同的微操作。 • 不同的机器,有着不同的时序信号。在同步控 制的机器中,一般包括周期、节拍、脉冲等三 级时序信号。

2013-12-4

25

3.微操作控制信号形成部件

2013-12-4 26

4.中断控制逻辑(中断机构)

• 用于实现异常情况和特殊请求的处理。

2013-12-4

27

5.程序状态寄存器 PSR

• 程序状态寄存器:用于存放程序的工作状态 (如管态、目态等)和指令执行的结果特征(如 结果为零、结果溢出等),把它所存放的内容 称为程序状态字(PSW)。PSW表明了系统的基本 状态,是控制程序执行的重要依据。不同的机 器,PSW的格式及内容不完全相同。

• 微操作控制信号形成部件:根据指令部件提供 的操作控制电位、时序部件所提供的各种时序 信号以及有关的状态条件,产生机器所需要的 各种微操作控制信号。 • 不同的指令,完成不同的功能,需要不同的微 操作控制信号序列。每条指令都有自己对应的 微操作序列。控制器必须根据不同的指令,在 不同的时间,产生并发出不同的微操作控制信 号,控制有关部件协调工作,完成指令所规定 的任务。

第6章MCS-51单片机的内部资源

6.2.3 中断的控制

MCS-51单片机中断系统中有两个特殊功能寄存器:中断 屏蔽寄存器IE和中断优先级寄存器IP。用户通过对这两 个特殊功能寄存器的编程设置,可以灵活地控制每个中 断源的中断允许或禁止以及中断优先级。 1. 中允控制

所谓中允控制是中断源的中断请求能否被CPU检测到, 即确定中断请求是否允许送达CPU。MCS-51单片机中没 有专门的开中断和关中断指令,对各个中断源的允许和 屏蔽是由内部的中断允许寄存器IE的各位来控制的。中 断允许寄存器IE的字节地址为A8H,可以进行位寻址。 IE的位定义格式如图6-4所示。

对于电平触发方式,只要P3.2(或P3.3)引脚为低电平, IE0(或IE1)就置1,请求中断,CPU响应后不能够由硬 件自动将IE0(或IE1)清零。如果在中断服务程序返回 时,P3.2(或P3.3)引脚还为低电平,则又会中断,这样 就会出现一次请求,中断多次的情况。为避免这种情况, 只有在中断服务程序返回前撤消P3.2(或P3.3)的中断请 求信号,即使P3.2(或P3.3)为高电平。通常通过下图63所示外电路来实现。

3.中断允许与中断屏蔽

当中断源提出中断请求,CPU检测到后是否立即进行中 断处理呢?结果不一定。CPU要响应中断,还受到中断 系统多个方面的控制,其中最主要的是中断允许和中断 屏蔽的控制。如果某个中断源被系统设置为屏蔽状态, 则无论中断请求是否提出,都不会响应;当中断源设置 为允许状态,又提出了中断请求,则CPU才会响应。另 外,当高优先级中断正在响应时,也会屏蔽同级中断和 低优先级中断。

串行口中断TI、RI

(3)软硬件结合清“0” 低电平触发的外部中断标志位IE0、IE1

6.2.4 中断响应

1. 中断响应条件 中断响应是有条件的,并不是查询到的所有中断请求都 能被立即响应。MCS-51单片机的CPU在每个机器周期会 顺序检查每一个中断源,在机器周期的S6阶段采样并按 优先级顺序处理所有被激活了的中断请求,如果没有被 下述条件所阻止,将在下一个机器周期的状态P1(S1) 响应激活了的最高级中断请求。 (1) 无同级或高级中断正在处理。 (2) 现行指令执行到最后一个机器周期且已结束。 (3) 若现行指令为RETI或访问IE、IP的指令时,执行完该 指令且紧随其后的另一条指令也已执行完毕。 如果存在上述条件之一,CPU将丢弃中断查询结果,不 能对中断请求进行响应。

6第六讲_中央处理器(1-4)_指令周期

指令周期

用方框图语言表示指令周期 在进行计算机设计时,可以采用方框图语言来表示一条指令的指令周 期。 一个方框代表一个CPU周期,方框中的内容表示数据通路的操作或某种 控制。 一个菱形符号代表某种判别或测试,不过时间上它依附于它前面一个 方框的CPU周期,而不单独占用一个CPU周期。 符号“~”代表一个公操作。

21

c

指令寄存器 IR

000 000024 021 地址寄存器AR

JMP 21

c

缓冲寄存器DR 数据总线DBUS

地址总线ABUS

注意 执行“JMP 21”指令时,我们此处所给的四条指 令组成的程序进入了死循环,除非人为停机,否则这 个程序将无休止地运行下去,因而内存单元40中的和 数将一直不断地发生变化。 当然,我们此处所举的转移地址21是随意的,仅仅用来 说明转移指令能够改变程序的执行顺序而已。

—分析指令

—按指令规定内容执行指令

不同指令的操作步骤数 和具体操作内容差异很大

—检查有无中断请求

若无,则转入下一条指令的执行过程

形 成 下 一 条 指 令 地 址

指令周期的基本概念

1. 指令周期:CPU每取出并执行一条指令,都要完成一系列 的操作,这一系列操作所需用的时间通常叫做一个指令 周期。 2. 机器周期:机器周期也称为CPU周期。通常用内存中读取 一个指令字的最短时间来规定CPU周期。指令周期常常用 若干个CPU周期数来表示,

第五章 中央处理器

CPU的功能和组成 指令周期

CPU的功能和组成

什么是CPU?

所谓中央处理器是控制计算机来自动完成取出指令 和执行指令任务的部件。它是计算机的核心部件,通常简 称为CPU。

CPU的基本组成

计算机组成原理第六章中央处理器(含答案)

第六章中央处理器6.1 CPU组成与功能随堂测验1、控制CPU内数据通路传送的部件是()(单选)A、程序控制器B、时序产生器C、指令译码器D、操作控制器2、下列可能是CPU组成部件的是( )(多选)A、程序计数器PCB、指令寄存器IRC、累加器ACD、算术逻辑运算单元ALU3、下列属于CPU功能的是()(多选)A、算术逻辑运算功能B、存储控制功能C、操作控制功能D、异常控制功能4、下列关于程序计数器的下列描述中,正确的是()(多选)A、指令执行过程中会保存当前正在执行的指令地址B、指令执行过程中会保存下一条指令的地址C、其值不一定按PC+“1”的方式改变D、CPU中可以没有PC6.2 数据通路随堂测验1、下列关于数据通路的叙述中,正确的是()(多选)A、数据通路是指令周期内信息传输的路径B、不同指令执行使用的数据通路可以不同C、同一指令在执行的不同阶段使用的数据路径不同D、不同数据路径不能使用相同的功能部件2、下图是数据通路中反映时间关系的原理图。

下列关于该图中几个时间关系描述的描述中,正确的是()(多选)A、建立时间setup 指触发器时钟到来之前数据应该保持稳定不变时间,否则数据不能在该时钟有效时被打入触发器B、保持时间hold 指触发器时钟到来之后数据应该保持稳定不变时间,否则数据不能在该时钟有效时被打入触发器C、CLk-to-Q是指时钟有效之后新输入的值稳定出现在输出端所经历的时延D、由此可知该电路的时钟最后最小值为setup + hold + Clk-to-Q3、下列关于数据通路结构及其影响的描述中,正确的是()(多选)A、常用的数据通路有专用通路和共享通路两种B、相同指令在不同数据通路结构下数据路径不同C、完成相同指令在不同数据通路结构下需要的控制信号不同D、相同指令在不同数据通路结构下执行的效率不同6.4 数据通路实例随堂测验1、下图为单总线结构数据通路实例关于该数据通路的下列描述中,正确的是() (多选)A、PC +“1" 的数据通路为PC -> X -> ALU ->Z -> PCB、取指令的数据通路为:PC -> AR -> MEM -> DR -> IRC、所有控制寄存器向总线数据的控制信号,如R2out, Zout等都一定不能同时有效D、所有控制从总线向寄存器输入的控制信号,如Xin,R2in等一定不能同时有效2、下图为另一种单总线结构的CPU原理图假定PCout 兼有使PC +”1"的功能,围绕该图的下列描述中,正确的是()(多选)参考答案如下:A、实现PC + "1"的数据通路是PC -> PCB、取指令的数据通路为:PC-> AR -> 主存-> DR -> IRC、PCout、DRout 、IRA out 及bus1->BUS 都一定不能同时有效D、某采用简洁寻址的指令其执行阶段的数据通路一定包含: IR -> AR ->主存->DR->AR->主存->DR3、下图为基于专用通路的CPU结构围绕该图的下列描述中,正确的是()(多选)A、取指令的数据通路为PC-> 指令寄存器B、完成PC 增量操作的数据通路为:PC-> PC+1 部件-> PCBranch ->MUX1->PCC、由于使用了专题通路结构和多路选择器,所有功能部件的输出将不再有数据冲突D、图中PC 既是指令地址寄存器也是数据地址寄存器6.1D、ABCD、ACD、ABC6.2ABC、ABC、ABCD6.4ABC、ABCD、ABC。

中央处理器

数据寄存器 DR

+ - ALU=A ALU=B

A

B

ALU

⊕ ⊙

∧ ∨

PC→AB

AR→AB DR→DB DB→DR PC→AB

ALU→GR

内部控制信号

ADS M/IO W/R

ALU→DR

ALU→AR

地址寄存器 AR

AR→AB

数据总线 DB

地址总线 AB

控制总线 CB

6.3 指令的执行 6.3 指令的执行

CLK2

指令译码器

DR→ALU(A) DB→IR ALU→PC DR→ALU(B)

脉冲源

NZVC

时序控制信号形成部件

数据寄存器 DR

+ - ALU=A ALU=B

A

B

ALU

⊕ ⊙

∧ ∨

PC→AB

AR→AB DR→DB DB→DR PC→AB

ALU→GR

内部控制信号

ADS M/IO W/R

ALU→DR

(1)ADD rs,rs1指令的微操作流程图 (1)ADD rs,rs1指令的微操作流程图

PC→ A B A D S(T 1) , M / IO =1 , W/ R =0

D B → IR , P C + 1

rs1 → G R (rs1) → A LU (A )

rs → G R

(rs) → A LU (B)

时钟周期 T

机器周期 M1

机器周期 M2 指令周期

机器周期 M3

机器周期 M4

2.指令的执行 2.指令的执行

(1)指令的执行过程 ① 取指令 根据指令计数器PC提供的地址从主存储器中读取现行指令,送到主存数 据缓冲器MDR中。然后再送往CPU内的指令寄存器IR中。同时改变指 令计数器的内容,使之指向下一条指令地址或紧跟现行指令的立即数或 地址码。 ② 取操作数 如果是无操作数指令则可直接进入下一个过程。如果需要操作数则根据寻 址方式计算地址,然后到存储器中去取操作数。如果是双操作数指令则 需两个取数周期; ③ 执行操作 根据操作码完成相应的操作并根据目的操作数的寻址方式存结果。

计算机组成原理(第六章)

• • • • 中央处理器(CPU)由运算器和控制器组成。 运算器主要用来完成各种算术和逻辑运算功能; 寄存器:用来存放中间结果、缓冲作用 控制器是全机的指挥中心,在在它的控制下,计算机总是遵循“取指令, 执行指令,取下条指令,执行下条指令…”这样周而复始地工作直到停机 为止。 控制器对指令的执行过程的控制有三种方式: – 同步控制方式

• 现代计算机系统广泛采用的方式 • 基本思想:将每个指令周期分成多个机器周期,每个机器周期中再分成 多个节拍,于是各条指令可取不同的机器周期数作为各自的指令周期。 如简单指令包含一个机器周期,复杂指令可包含多个机器周期。 • 这种方式不浪费很多时间,控制上又不十分复杂。

二、控制器的功能与组成 1、控制器的功能

WE M

RD M

RD M

ZF=1?

IR(ADR)→PC

写入操作

读出操作

AC+MDR→AC

读出操作

AC∩MDR→AC

0→启停逻辑

第六章 中央处理器 (10)

四、时序部件

– 指令的执行过程严格按照指令操作流程图所规定的时序定时; – 时序部件用来产生必要的时序信号为机器周期和节拍信号定时; – 根据组成计算机各部件的器件特性,时序信号通常采用“电位-脉 冲”制。 – 时序部件的构成

C0~C31

译码器

Hale Waihona Puke XXXXX 控制字段源部件地址

目标部件地址

地址字段

第六章 中央处理器 (19)

(2)、微指令的地址字段 – 微程序有两种不同的顺序控制方式:断定方式和增量方式。两种方 式下地址字段的设置不同。 – 断定方式

• 微指令在CM可不顺序存放 • 外部测试条件的考虑

计算机组成原理知识点

计算机组成原理知识点第一章:概论1、电子计算机:电子模拟计算机(连续变化的物理量)和电子数字计算机(离散的数字量)。

2、计算机的发展历史:根据电子元器件的不同,分为若干个代:电子管,晶体管,小、中规模的集成电路,大、超大规模的集成电路,甚大规模的集成电路,极大规模的集成电路。

3、冯诺伊曼存储程序的概念:5大组成部分,二进制,存储与程序控制4、计算机的组成框图:5、计算机的主要部件:输入设备,输出设备,存储器,运算器,控制器6、计算机总线结构:单总线和双总线7、计算机系统:硬件和软件8、计算机的主要性能指标:机器字长、数据通路宽度、主存容量、运算速度第二章:数据的机器层次表示1、无符号数和有符号数:2、原码表示法:[X]=X/2n-X;补码表示法:[X]=X/M+X;反码表示法:[X]=X/(2-2-n)+X3、模和同余的概念:4、三种码制之间的相互转换:5、机器数的定点表示法:定点整数和定点小数:6、浮点表示法:N=M×r E;浮点数的表示范围,规格化浮点数。

7、ASCII字符编码,汉字国标码,汉字区位码,汉字机内码8、十进制数的编码:8421码,2421码,余3码9、数据校验码:奇偶校验码,海明校验码,第三章:指令系统1、指令的基本格式:操作码字段+地址码字段(一、二、三、四和零)地址2、指令操作码的定长编码和变长编码:3、编址方式:编址单位:字、字节、位;指令中地址码的位数与主存容量和最小寻址单位有关。

4、指令寻址和数据寻址:分为:顺序寻址和跳跃寻址(直接、相对和间接)。

5、数据寻址的方式:立即寻址(立即数)、寄存器寻址(寄存器地址)、直接寻址(主存中有效地址)、间接寻址(又分一级和多级,需要多次访问主存)、寄存器间接寻址(主存地址放在寄存器中)、变址寻址(变址寄存器与指令给出的形式地址A相加)、基址寻址(基址寄存器的内容与指令给出的位移量D相加)、相对寻址(程序计数器的基准地址与指令给出的位移量D相加)、页面寻址(分为基页寻址:0与给出地址拼接和当前页寻址,PC的高位地址与给出的地址拼接)、自增型寄存器简址和自减型寄存器简址(寄存器内容自动增量修改,指向下一个地址和自动减量修改)、扩展变址方式(变址和间址相结合:一种先进行变址运算,其结果作为间接寻址;先进行间接寻址,然后再与变址值进行运算)、基址变址寻址(基址寄存器中的值、变址寄存器中的值和位移量三者相加得到)6、堆栈分为:硬堆栈和软堆栈7、指令类型:数据传送类指令、运算类指令:算术运算、逻辑运算、移位;程序控制类指令(转移指令、子程序调用指令、返回指令)、输入输出类指令(独立编址、统一编址)第四章:数值的机器运算1、加法器:全加器、进位的产生和传递。

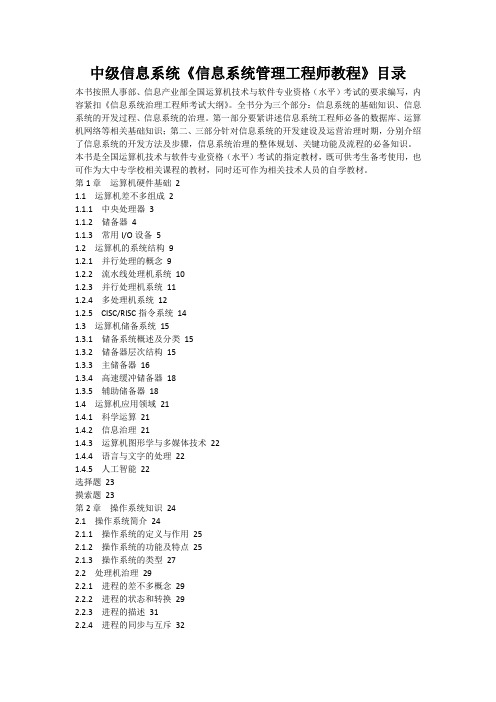

中级信息系统《信息系统管理工程师教程》目录

中级信息系统《信息系统管理工程师教程》目录本书按照人事部、信息产业部全国运算机技术与软件专业资格(水平)考试的要求编写,内容紧扣《信息系统治理工程师考试大纲》。

全书分为三个部分:信息系统的基础知识、信息系统的开发过程、信息系统的治理。

第一部分要紧讲述信息系统工程师必备的数据库、运算机网络等相关基础知识;第二、三部分针对信息系统的开发建设及运营治理时期,分别介绍了信息系统的开发方法及步骤,信息系统治理的整体规划、关键功能及流程的必备知识。

本书是全国运算机技术与软件专业资格(水平)考试的指定教材,既可供考生备考使用,也可作为大中专学校相关课程的教材,同时还可作为相关技术人员的自学教材。

第1章运算机硬件基础21.1 运算机差不多组成21.1.1 中央处理器31.1.2 储备器41.1.3 常用I/O设备51.2 运算机的系统结构91.2.1 并行处理的概念91.2.2 流水线处理机系统101.2.3 并行处理机系统111.2.4 多处理机系统121.2.5 CISC/RISC指令系统141.3 运算机储备系统151.3.1 储备系统概述及分类151.3.2 储备器层次结构151.3.3 主储备器161.3.4 高速缓冲储备器181.3.5 辅助储备器181.4 运算机应用领域211.4.1 科学运算211.4.2 信息治理211.4.3 运算机图形学与多媒体技术221.4.4 语言与文字的处理221.4.5 人工智能22选择题23摸索题23第2章操作系统知识242.1 操作系统简介242.1.1 操作系统的定义与作用252.1.2 操作系统的功能及特点252.1.3 操作系统的类型272.2 处理机治理292.2.1 进程的差不多概念292.2.2 进程的状态和转换292.2.3 进程的描述312.2.4 进程的同步与互斥322.2.5 死锁342.3 储备治理352.3.1 储备器的层次352.3.2 地址转换与储备爱护362.3.3 分区储备治理372.3.4 分页式储备治理382.3.5 分段式储备治理的差不多原理40 2.3.6 虚拟储备治理差不多概念422.4 设备治理422.4.1 I/O硬件原理432.4.2 I/O软件原理442.4.3 Spooling 系统462.4.4 磁盘调度472.5 文件治理472.5.1 文件与文件系统482.5.2 文件名目492.5.3 文件的结构和组织512.5.4 文件的共享和爱护542.6 作业治理552.6.1 作业及作业治理的概念552.6.2 作业调度562.6.3 多道程序设计57选择题57摸索题58第3章程序设计语言593.1 程序设计语言基础知识593.1.1 程序设计语言差不多概念593.1.2 程序设计语言的差不多成分60 3.2 程序编译、说明系统643.2.1 程序的编译及说明643.2.2 编译程序差不多原理643.2.3 说明程序差不多原理64选择题66摸索题66第4章系统配置和方法674.1 系统配置技术674.1.1 系统架构674.1.2 系统配置方法694.1.3 系统处理模式734.1.4 系统事务治理764.2 系统性能784.2.1 系统性能定义和指标784.2.2 系统性能评估794.3 系统可靠性804.3.1 可靠性定义和指标804.3.2 运算机可靠性模型80选择题82摸索题82第5章数据结构与算法835.1 数据结构与算法简介835.1.1 什么是数据结构835.1.2 数据结构差不多术语845.1.3 算法描述845.1.4 算法评判865.1.5 算法与数据结构的关系865.2 线性表875.2.1 线性表的定义和逻辑结构875.2.2 线性表的顺序储备结构885.2.3 线性表的链式储备结构905.3 栈和队列905.3.1 栈的定义和实现905.3.2 表达式求值935.3.3 队列935.4 数组和广义表965.4.1 数组965.4.2 广义表的定义和储备结构975.5 树和二叉树995.5.1 树的定义995.5.2 树的储备结构1005.5.3 树的遍历1025.6 图1035.6.1 图的定义和术语1035.6.2 图的储备结构1035.6.3 图的遍历104选择题105摸索题105第6章多媒体基础知识1076.1 多媒体技术概论1076.1.1 多媒体技术差不多概念1076.1.2 多媒体关键技术和应用1086.2 多媒体压缩编码技术1106.2.1 多媒体数据压缩的差不多原理1106.2.2 多媒体数据压缩的差不多编码方法111 6.2.3 编码的国际标准1126.3 多媒体技术应用1136.3.1 数字图像处理技术1136.3.2 数字音频处理技术1176.3.3 多媒体应用系统的创作120选择题121摸索题121第7章网络基础知识1227.1 网络的基础知识1227.1.1 运算机网络的概念和分类1227.1.2 运算机网络的组成1247.2 运算机网络体系结构与协议1257.2.1 运算机网络体系结构1267.2.2 TCP/IP协议1287.3 运算机网络传输1297.3.1 数据通信模型1297.3.2 数据通信编码1317.3.3 传输介质1337.3.4 多路复用技术1347.3.5 数据交换技术1357.3.6 差错操纵与流量操纵1367.4 运算机局域网1377.4.1 局域网的介质访问操纵方式1377.4.2 局域网的组网技术1397.5 网络的治理与治理软件1417.5.1 网络的治理1417.5.2 网络治理软件1437.6 网络安全1447.6.1 运算机网络的安全问题1447.6.2 数据的加密与解密1457.6.3 防火墙技术1467.6.4 网络安全协议1477.7 网络性能分析与评估1487.7.1 服务质量QoS 1487.7.2 服务等级协议(SLA:service-level agreement)148 7.7.3 流量治理1497.7.4 网络性能评判指标体系1497.8 因特网基础知识及其应用1507.8.1 IP地址和子网掩码1517.8.2 DNS和代理服务器1537.8.3 万维网服务1547.8.4 因特网其他服务156摸索题159第8章数据库技术1608.1 数据库技术基础1608.1.1 数据库系统概述1608.1.2 数据模型1618.1.3 数据库系统结构1648.2 关系数据库的数据操作1668.2.1 关系数据库1668.2.2 关系运算1688.2.3 关系数据库标准语言(SQL)1718.3 数据库治理系统1808.3.1 数据库治理系统概述1808.3.2 数据库系统的操纵功能181 选择题187摸索题188第9章安全性知识1899.1 安全性简介1899.1.1 安全性差不多概念和特点189 9.1.2 安全性要素1899.2 访问操纵和鉴别1909.2.1 鉴别1909.2.2 访问操纵的一样概念1919.2.3 访问操纵的策略1919.3 加密1929.3.1 保密与加密1929.3.2 加密与解密机制1929.3.3 密码算法1939.3.4 密钥及密钥治理1949.4 完整性保证1949.4.1 完整性概念1949.4.2 完整性保证策略1959.5 可用性保证1969.5.1 事故响应与事故复原1969.5.2 减少故障时刻的高可用性系统1979.6 运算机病毒的防治与运算机犯罪的防范1979.6.1 运算机病毒概念1979.6.2 运算机病毒的防治1989.6.3 运算机犯罪的防范1999.7 安全分析1999.7.1 识别和评估风险1999.7.2 操纵风险2009.8 安全治理2009.8.1 安全治理政策法规2019.8.2 安全机构和人员治理2019.8.3 技术安全治理2019.8.4 网络治理2029.8.5 场地设施安全治理203选择题203摸索题203第二篇信息系统开发过程第10章信息系统开发的基础知识20610.1 信息系统概述20610.1.1 信息系统的概念20610.1.2 信息系统的结构20710.1.3 信息系统的要紧类型21310.1.4 信息系统对企业的阻碍21510.2 信息系统工程概述21710.2.1 信息系统工程的概念21710.2.2 信息系统工程的研究范畴21810.2.3 信息系统工程的差不多方法21810.3 信息系统开发概述21910.3.1 信息系统的开发时期21910.3.2 信息系统开发方法222选择题227摸索题227第11章信息系统开发的治理知识22811.1 信息系统项目22811.1.1 项目的差不多概念22811.1.2 信息系统项目的概念22911.2 信息系统中的项目治理23011.3 信息系统开发的治理工具23411.3.1 Microsoft Project 98/2000 23411.3.2 P3/P3E 23511.3.3 ClearQuest 236摸索题237第12章信息系统分析23812.1 系统分析的任务23812.2 系统分析的步骤24012.3 结构化分析方法24112.3.1 结构化分析方法的内容24112.3.2 结构化分析方法的工具24212.4 系统说明书25912.4.1 系统说明书的内容25912.4.2 系统说明书的审议26212.5 系统分析工具——统一建模语言(UML)263 12.5.1 统一建模语言(UML)的概述26312.5.2 统一建模语言(UML)的内容26512.5.3 统一建模语言(UML)的建模过程270 12.5.4 统一建模语言(UML)的应用271摸索题272第13章信息系统设计27413.1 系统设计概述27413.1.1 系统设计的目标27413.1.2 系统设计的原则27513.1.3 系统设计的内容27613.2 结构化设计方法和工具27713.2.1 结构化系统设计的差不多原则277 13.2.2 系统流程图27813.2.3 模块27913.2.4 HIPO技术27913.2.5 操纵结构图28113.2.6 模块结构图28113.3 系统总体设计28213.3.1 系统总体布局方案28313.3.2 软件系统结构设计的原则286 13.3.3 模块结构设计28713.4 系统详细设计29413.4.1 代码设计29413.4.2 数据库设计29613.4.3 输入设计30013.4.4 输出设计30313.4.5 用户接口界面设计30413.4.6 处理过程设计30713.5 系统设计说明书30913.5.1 系统设计引言30913.5.2 系统总体技术方案310选择题313摸索题314第14章信息系统实施31514.1 系统实施概述31514.1.1 系统实施时期的特点31514.1.2 系统实施的要紧内容31614.1.3 系统实施的方法31714.1.4 系统实施的关键因素31714.2 程序设计方法31914.2.1 程序设计基础知识31914.2.2 结构化程序设计32314.2.3 面向对象的程序设计32514.2.4 可视化程序设计32614.3 系统测试32714.3.1 系统测试概述32714.3.2 测试的原则32914.3.3 测试的方法33014.3.4 测试用例设计33214.3.5 系统测试过程33914.3.6 排错调试34814.3.7 系统测试报告34914.4 系统的试运行和转换35014.5 人员培训351选择题352摸索题352第15章信息化与标准化35315.1 信息化战略和策略35315.1.1 信息化35315.1.2 国家信息化35415.1.3 企业信息化35515.1.4 我国信息化政策法规356 15.2 信息化趋势35915.2.1 远程教育36015.2.2 电子商务36015.2.3 电子政务36115.3 企业信息资源治理36215.3.1 信息资源治理的含义362 15.3.2 信息资源治理的内容363 15.3.3 信息资源治理的组织363 15.3.4 信息资源治理的人员363 15.4 标准化基础36415.4.1 标准化的进展36415.4.2 标准化的定义36615.4.3 标准化的过程模式36715.4.4 标准化的级别和种类368 15.5 标准化应用37015.5.1 标准的代号和编号37015.5.2 信息技术标准化37215.5.3 标准化组织373摸索题375第三篇信息系统的治理第16章系统治理规划37816.1 系统治理的定义37816.1.1 治理层级的系统治理要求378 16.1.2 运作层级的系统治理要求381 16.2 系统治理服务38316.2.1 为何引入IT服务理念383 16.2.2 服务级别治理38416.3 IT财务治理38516.3.1 为何引入IT财务治理38516.3.2 IT部门的角色转换38616.3.3 IT财务治理流程38616.4 制定系统治理打算38816.4.1 IT部门的职责及定位38816.4.2 运作方的系统治理打算389 16.4.3 用户方的系统治理打算390摸索题391第17章系统治理综述39217.1 系统运行39217.1.1 系统治理分类39217.1.2 系统治理规范化39317.1.3 系统运作报告39317.2 IT部门人员治理39417.2.1 IT组织及职责设计39417.2.2 IT人员的教育与培训39617.2.3 第三方/外包的治理39617.3 系统日常操作治理39817.3.1 系统日常操作概述39817.3.2 操作结果治理及改进40017.3.3 操作人员的治理40017.4 系统用户治理40017.4.1 统一用户治理40017.4.2 用户治理的功能40217.4.3 用户治理的方法40317.4.4 用户治理报告40417.5 运作治理工具40417.5.1 运作治理工具的引入40417.5.2 自动化运作治理的益处405 17.5.3 运行治理工具功能及分类406 17.6 成本治理40817.6.1 系统成本治理范畴40817.6.2 系统预算及差异分析40817.6.3 TCO总成本治理41017.7 计费治理41017.7.1 计费治理的概念41017.7.2 计费治理的策略41117.7.3 计费定价方法41117.7.4 计费数据收集41217.8 系统治理标准简介41417.8.1 ITIL标准41417.8.2 COBIT标准41517.8.3 HP ITSM参考模型和微软MOF 416 17.9 分布式系统的治理41617.9.1 分布式系统的问题41617.9.2 分布式环境下的系统治理417 17.9.3 分布式系统中的安全治理418 摸索题419第18章资源治理42018.1 资源治理概述42018.1.1 资源治理概念42018.1.2 配置治理42018.2 硬件治理42118.2.1 硬件治理的范畴42118.2.2 硬件配置治理42218.2.3 硬件资源爱护42318.3 软件治理42418.3.1 软件治理的范畴42418.3.2 软件生命周期和资源治理424 18.3.3 软件构件治理42518.3.4 软件分发治理42618.3.5 文档治理42718.3.6 软件资源的合法爱护427 18.4 网络资源治理42818.4.1 网络资源治理的范畴428 18.4.2 网络资源治理与爱护428 18.4.3 网络配置治理42918.4.4 网络治理43118.4.5 网络审计支持43118.5 数据治理43318.5.1 数据生命周期43318.5.2 信息资源治理43318.5.3 数据治理43418.5.4 公司级的数据治理43418.5.5 数据库审计支持43618.6 设施和设备治理43618.6.1 电源设备治理43618.6.2 空调设备治理43718.6.3 通信应急设备治理43718.6.4 楼宇治理43818.6.5 防护设备治理43818.6.6 信息系统安全性措施标准439摸索题439第19章故障及问题治理44019.1 故障治理概述44019.1.1 概念和目标44019.1.2 故障治理的范畴44019.2 故障治理流程44119.2.1 故障监视44219.2.2 故障调研44319.2.3 故障支持和复原处理445 19.2.4 故障分析和定位445 19.2.5 故障终止44719.2.6 故障处理跟踪44719.3 要紧故障处理44819.3.1 故障的差不多处理448 19.3.2 主机故障复原措施448 19.3.3 数据库故障复原措施450 19.3.4 网络故障复原措施451 19.4 问题操纵与治理45119.4.1 概念和目标45219.4.2 相关逻辑关系45219.4.3 问题治理流程45319.4.4 问题操纵45419.4.5 错误操纵45719.4.6 问题预防45819.4.7 治理报告459选择题460摸索题460第20章安全治理46120.1 概述46120.1.1 安全策略46120.1.2 安全治理措施46220.1.3 安全治理系统46320.1.4 安全治理范畴46420.1.5 风险治理46520.2 物理安全措施46620.2.1 环境安全46620.2.2 设施和设备安全467 20.2.3 介质安全46920.3 技术安全措施47120.3.1 系统安全措施47120.3.2 数据安全性措施474 20.4 治理安全措施47620.4.1 运行治理47620.4.2 防犯罪治理47720.5 相关的法律法规47820.6 安全治理的执行47920.6.1 安全性治理指南480 20.6.2 入侵检测48020.6.3 安全性强度测试481 20.6.4 安全性审计支持481选择题482摸索题482第21章性能及能力治理48321.1 系统性能评判48321.1.1 性能评判概述48321.1.2 性能评判指标48321.1.3 设置评判项目48721.1.4 性能评判的方法和工具488 21.1.5 评判结果的统计与比较491 21.2 系统能力治理49121.2.1 能力治理概述49221.2.2 能力治理活动49221.2.3 设计和构建能力数据库493 21.2.4 能力数据监控49621.2.5 能力分析诊断49721.2.6 能力调优和改进49821.2.7 实施能力变更49921.2.8 能力治理的高级活动项目499 21.2.9 能力打算、考核和报告500 选择题501摸索题501第22章系统爱护50222.1 概述50222.1.1 系统爱护的任务和内容502 22.1.2 系统爱护的方法50222.2 制定系统爱护打算50322.2.1 系统的可爱护性50322.2.2 系统爱护的需求50422.2.3 系统爱护打算50522.2.4 系统爱护的实施形式507 22.3 爱护工作的实施50722.3.1 执行爱护工作的过程507 22.3.2 软件爱护50922.3.3 硬件爱护510选择题511摸索题511第23章新系统运行及系统转换512 23.1 制定打算51223.1.1 系统运行打算51223.1.2 系统转换打算51223.2 制定系统运行体制51323.3 系统转换测试与运行测试513 23.3.1 系统转换测试51323.3.2 运行测试51623.4 系统转换51723.4.1 系统转换打算51723.4.2 系统转换的执行52023.4.3 系统转换评估52123.5 开发环境治理52123.5.1 开发环境的配置52223.5.2 开发环境的治理52223.5.3 系统发行及版本治理523摸索题523第24章信息系统评判52424.1 信息系统评判概述52424.1.1 信息系统评判的概念和特点52424.1.2 信息系统的技术性能评判52524.1.3 信息系统的治理效益评判52524.1.4 信息系统成本的构成52524.1.5 信息系统经济效益来源52624.1.6 信息系统经济效益评判的方法527 24.1.7 信息系统的综合评判52824.2 信息系统评判项目52824.2.1 建立评判目标52824.2.2 设置评判项目53024.3 评判项目的标准53124.3.1 性能评判标准53124.3.2 运行质量评判标准53324.3.3 系统效益评判标准53424.4 系统改进建议535摸索题536第25章系统用户支持53725.1 用户角度的项目53725.2 用户支持53725.3 用户咨询53825.4 关心服务台54025.5 人员培训服务542摸索题543参考文献544。

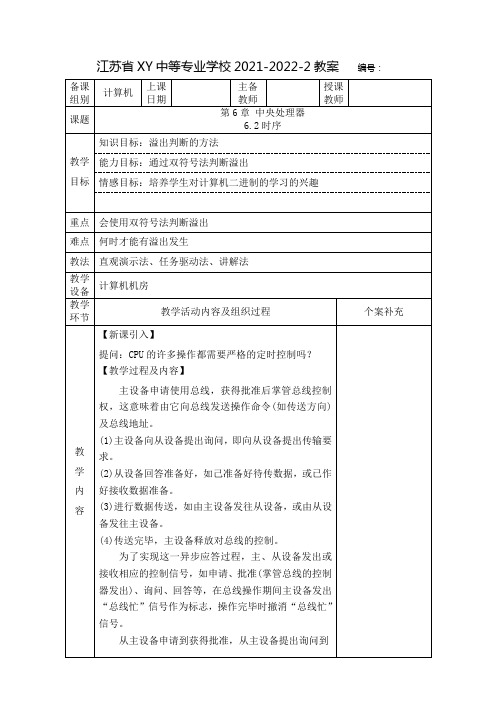

中职计算机原理教案:时序

时钟周期提供了一项操作所需的时间分段,但有的操作如打入寄存器,还需严格的定购脉冲,以确定在哪一时刻打入。时钟周期的切换也需要严格的同步定时。常见的设计是在每个时钟周期的末尾发一次工作脉冲,脉冲前沿可用来打入运算结果(或传送),脉冲后沿则实现周期的切换。也有的计算机在一个时钟周期中先后发出几个工作脉冲,有的脉冲位于时钟周期前端,可用作清除脉冲;有的脉冲位于中部,用作控制外围设备的输入/输出脉冲;有的脉冲位于尾部,前沿用作CPU内部的打入,后沿用作实现周期切换。

(3)时钟周期(节拍)

一个工作周期的操作可能需要分成几步完成,例如按变址方式读取操作数,先要进行变址运算才能访存读取。所以在同步控制方式中,时序系统需按固定时间分段设置时钟周期。每个时钟周期(又称为一拍)完成一步操作,如一次传送、加减等,这是时序系统中最基本的时间分段。各时钟周期长度相同,一个工作周期可根据其需要,由若干个时钟周期组成。不同工作周期,或不同指令中的同一种工作周期,其时钟周期数目可以不同。

教学设备

计算机机房

教学环节

教学活动内容及组织过程

个案补充

提问:CPU的许多操作都需要严格的定时控制吗?

【教学过程及内容】

主设备申请使用总线,获得批准后掌管总线控制权,这意味着由它向总线发送操作命令(如传送方向)及总线地址。

(1)主设备向从设备提出询问,即向从设备提出传输要求。

(2)从设备回答准备好,如己准备好待传数据,或已作好接收数据准备。

实际应用中的一些变化

教师讲解:

在实际应用中,同步控制方式又有许多变化,甚至引入异步应答关系,可以看成是两种控制方法的结合。不同指令所需的执行时间可能不同,甚至差别较大,为它们规定同样的时间显然是不恰当的。常见的作法是让它们占用不同的时钟周期数目,以满足各自的需要,而又比较紧凑。最短的指令只需一个时钟周期,较长的指令则占用多个时钟周期。如果每个时钟周期长度较小,则时间安排就比较紧凑而经济。当然,一个时钟周期能完成CPU内部最长的数据通路操作。这是同步控制方式的一种实际应用形态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数据通路的设计

状态标志寄存器(PSW) 状态标志寄存器用来存放程序状态字的。程序状态字的各位表征 程序和机器运行的状态,是参与控制程序执行的重要依据之一。它主 要包括两部分内容:一是状态标志,如:进位标志(CF)、结果为零 标志(ZF)等,大多数指令的执行将会影响到这些标志位;二是控制 标志,如:中断标志、陷阱标志等。

时序部件:

时序部件能产生一定的时序信号,以保证机器的各功能部件有节奏地进行 信息传送、加工及信息存储。时序部件包括: ⑴脉冲源 ⑵启停控制逻辑 ⑶节拍信号发生器

数据通路的设计

控制单元所需部件

数据通路的设计

控制单元所需部件

数据通路的设计

系统所需全部功能部件:

数据通路的设计

2.将选择的功能的部件连起来

数据通路的设计

执行阶段所需部件

数据通路的设计

执行阶段所需部件

数据通路的设计

控制单元(CU)

根据IR的内容(指令),PSW的内容(状态信息)以及时序 线路的内容,产生控制整个计算机系统所需的各种控制信号.

微操作信号发生器:

一条指令的取出和执行可以分解成很多最基本的操作,这种最基本 的不可再分割的操作称为微操作。微操作信号发生器用来发出微操 作序列。

数据通路的设计

中央处Байду номын сангаас器的操作:

数据通路的设计

数据通路的设计

数据通路的设计

计算机系统设计与实现内容提要

二.计算机系统设计与实现 指令系统设计

数据通路的设计

指令流程设计 指令流程设计 控制部分的实现

指令流程设计

分析各周期应产生的控制信号

以流程图的形式描述指令的操作过程,就得到 指令操作流程图. 指令流程设计的结果是将指令的执

3. 执行周期(EXEC)

(1) SUB AX,BX

指令流程设计

(2) MOV AX,BX

(3) MOV AX, [BP]

不同的指令执行周期完成的操作不同

指令流程设计

(4) MOV AX,#8000 (5)ADD AX,BUF[BX]

(6) JMP LL

指令流程设计

将系统各指令各周期综合起来形成系统指令流程图

Elements storing address of Instruction (Register PC)

数据通路的设计

⑵ 指令寄存器(IR) 指令寄存器用来存放从存储器中取出的指令。当指令从主存取出暂存于 指令寄存器之后,在执行指令的过程中,指令寄存器的内容不允许发生变化 ,以保证实现指令的全部功能。 ⑶ 存储器数据寄存器(DR) 存储器数据寄存器用来暂时存放由主存储器读出的一条指令或一个数据 字;反之,当向主存存入一条指令或一个数据字时,也暂时将它们存放在存 储器数据寄存器中。 ⑷ 存储器地址寄存器(AR) 存储器地址寄存器用来保存当前CPU所访问的主存单元的地址。由于主 存和CPU之间存在着操作速度上的差别,所以必须使用地址寄存器来保持地 址信息,直到主存的读/写操作完成为止。 当CPU和主存进行信息交换,无论是CPU向主存存/取数据时,还是CPU从 主存中读出指令时,都要使用存储器地址寄存器和数据寄存器。

本章采用CISC

X86 架构指令体系结构为例

具体设计见附件一

计算机系统设计与实现内容提要

二.计算机系统设计与实现 指令系统设计

数据通路的设计 数据通路的设计

指令流程设计 控制部分的实现

数据通路的设计

1.选择完成预定功能的部件

取指令 计算下条指令地址

取指令

数据通路的设计

⑴ 程序计数器 (PC) 程序计数器用来存放正在执行的指令地址或接着要执行的下条指令地址

指令流程设计

2.分析取数阶段

指令流程设计

3.执行阶段

计算机的基本工作过程可以概括成为取指令、分析取数、执 行指令,然后再取下一条指令,……。如此周而复始,直至 遇到停机指令或外来的干预为止。

指令流程设计

指令流程设计实例

(1) SUB AX,BX (2) MOV AX,BX (3) MOV AX, [BP] (4) MOV AX,#8000

行过程以指令流程图的形式表示出来.

指令操作过程:

指令流程设计

指令执行步骤回顾

1.取指令阶段

取指令阶段完成的任务是将现行指令从主存中取出来并送至指令寄存器中去。具体的操作为: ①将程序计数器(PC)中的内容送至存储器地址寄存器(MAR)。 (PC)→MAR ②由控制单元(CU)经控制总线(CB)向主存发读命令。 Read ③从主存中取出的指令通过数据总线(DB)送到存储器数据寄存器(MDR)。 M(MAR) →MDR ④将MDR的内容送至指令寄存器(IR)中。 (MDR)→IR ⑤将PC的内容递增,为取下一条指令做好准备。 (PC)+1→PC 以上这些操作对任何一条指令来说都是必须要执行的操作, 所以称为公共操作

连接方法:

☆ 在所有需要传送数据的部件之间创建一条直接通路。

(专用数据通路) ☆ 在CPU内部创建一条总线(bus)各部件之间通过 该

(建立数据通路)

总线传送数据。 (总线方式数据通路)

本例用总线方式

数据通路的设计

并部件连接起来

X86

架构 总线方式

数据通路的设计

数据通路的设计

3.数据流动信号分析

译码取操作数

• Then we need to:

执行

• Finally we need to:

计算下条指令地址

控制策略概述

中央处理器概述

Θ

单周期控制方案(Singlecycle)

Θ

多周期控制方案(Multi-cycle)

Θ

流水线控制方案(Pipeline)

例: MIPS 的Load , Store 和R型指令

Θ时间控制:对各种操作实施时间上的控制

Θ数据加工:对数据进行算数运算和逻辑运算处理

控制器的功能就是控制指令的正确执行

中央处理器概述

指令的执行过程

How to execute instructions

MIPS instructions

• First we need to:

取指令

• Then we need to:

控制部分的实现

实现控制部件有两种方式:

组合逻辑控制

微程序控制 本模型机例子选择微程序法实现控制器

有关微程序概念见课件的附录二部分

微程序控制器的实现

1.微命令编码

(控制信号的存储方式)

模型机系统数据通路中共有以下 68 位控制信号:

微程序控制器的实现

采用字段直接编译法:

分段原则:凡是将数据送到内部总线的信号 XX →IB,互斥, 分为一组, 同一部件的同一操作是互斥的,分为一组. 如,ADD,SUB,AND 等 外部芯片的读写操作互斥分为一组.如 MMRD ,MMWR ,IORD,IOWR 等 微命令编码设计如下:

一.中央处理器(CPU)概述 二.计算机系统设计与实现

中央处理器概述部分内容提要

一.中央处理器(CPU)概述 中央处理器(CPU)的功能 指令的执行过程 控制策略概述

中央处理器概述

中央处理器(CPU)的功能

中央处理器(CPU)对整个计算机系统的运行极为重要,控制器是核心 单元.CPU 具有以下四方面的功能: Θ指令控制:程序顺序的控制 Θ操作控制:按指令含义完成各种操作动作

PC→IB, ARin AR → AB,MMRD ,+2PC

DB → DR,DRin DB → IB,AXin

PC→IB, Sin DR → IB,ADD ,Tin T→IB, PCin

指令流程设计

对整个指令系统进行指令流程综合:

1.取指周期(FIC)

指令流程设计

2. 取操作数周期(FDC)

指令流程设计

一条指令的取出和执行可以分解成很多最基本的操作,这种最基本的不可 再分割的操作称为微操作。微操作信号发生器用来发出微操作序列。

时序部件:

时序部件能产生一定的时序信号,以保证机器的各功能部件有节奏地进行信息传 送、加工及信息存储。时序部件包括: ⑴脉冲源 脉冲源用来产生具有一定频率和宽度的时钟脉冲信号,为整个机器提供基准信号。 ⑵启停控制逻辑 启停控制逻辑的作用是根据计算机的需要,可靠地开放或封锁脉冲,控制时序信 号的发生或停止,实现对整个机器的正确启动或停止。 ⑶节拍信号发生器 节拍信号发生器又称脉冲分配器。脉冲源产生的脉冲信号,经过节拍信号发生 器后产生出各个机器周期中的节拍信号,用以控制计算机完成每一步微操作。

第六章

Central Processing Unit (CPU)

中央处理器

Homework

第6章 中央处理器部分作业:

6-13, 6-14 , 6-18

本章主要参考文献: 计算机组成原理考研指导 ,徐爱萍,清华大学出版社

中央处理器内容提要

中央处理器(CPU)是整个计算机的核心,它包括运算器和控 制器。 控制器是计算机系统的指挥中心,它把运算器、存储器、输 入/输出设备等部件组成一个有机的整体,然后根据指令的要求指挥 全机的工作。本章着重讨论CPU的功能和组成,控制器的工作原理和 实现方法。

微程序控制器的实现

选以下指令为例进行部分指令微命令编码:

SUB AX,BX

MOV AX,[BP]

MOV AX,#8000

JMP LL

微程序控制器的实现

(1) SUB AX,BX 指令流程

注:微命令23位,写成以上6位 16进制数时最后一位无效

微命令编码:

微程序控制器的实现