通用的Verilog HDL 奇数偶数分频器

Verilog实现任意分频

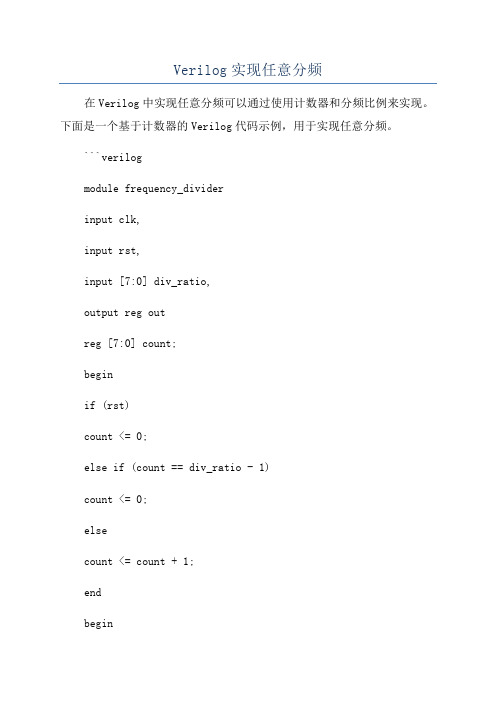

Verilog实现任意分频在Verilog中实现任意分频可以通过使用计数器和分频比例来实现。

下面是一个基于计数器的Verilog代码示例,用于实现任意分频。

```verilogmodule frequency_dividerinput clk,input rst,input [7:0] div_ratio,output reg outreg [7:0] count;beginif (rst)count <= 0;else if (count == div_ratio - 1)count <= 0;elsecount <= count + 1;endbeginif (rst)out <= 0;else if (count == div_ratio - 1)out <= ~out;endendmodule```在以上代码中,我们定义了一个名为"`frequency_divider`"的模块,该模块具有以下输入和输出:- `clk`:时钟信号- `rst`:复位信号- `div_ratio`:分频比例,使用8位二进制表示,范围为0到255- `out`:输出信号我们使用一个8位计数器(`count`)来进行分频。

每当计数器达到分频比例减1时,输出信号取反。

例如,如果分频比例为1,则输出信号将与时钟信号同步;如果分频比例为2,则输出信号将是时钟信号的一半频率;如果分频比例为4,则输出信号将是时钟信号的四分之一频率,以此类推。

需要注意的是,以上示例代码仅展示了分频的基本原理,并未考虑输入和输出信号的时序问题,如使 `div_ratio` 在运行时可更改、输出信号的不稳定性等。

针对具体应用需求,可以根据实际情况做出适当的修改和调整。

希望以上内容对您有所帮助!。

verilog奇偶分频、一段式、两段式、三段式状态机

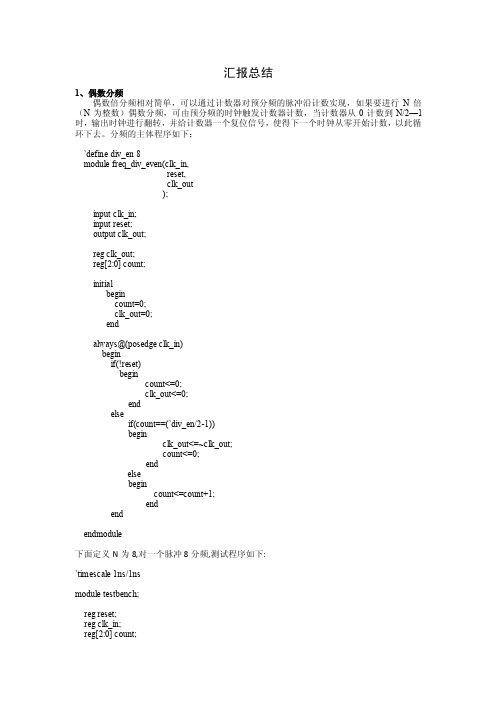

汇报总结1、偶数分频偶数倍分频相对简单,可以通过计数器对预分频的脉冲沿计数实现,如果要进行N倍(N为整数)偶数分频,可由预分频的时钟触发计数器计数,当计数器从0计数到N/2—1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数,以此循环下去。

分频的主体程序如下:`define div_en 8module freq_div_even(clk_in,reset,clk_out);input clk_in;input reset;output clk_out;reg clk_out;reg[2:0] count;initialbegincount=0;clk_out=0;endalways@(posedge clk_in)beginif(!reset)begincount<=0;clk_out<=0;endelseif(count==(`div_en/2-1))beginclk_out<=~clk_out;count<=0;endelsebegincount<=count+1;endendendmodule下面定义N为8,对一个脉冲8分频,测试程序如下:`timescale 1ns/1nsmodule testbench;reg reset;reg clk_in;reg[2:0] count;wire clk_out;freq_div_even test(.clk_in(clk_in),.reset(reset),.clk_out(clk_out));initialbeginreset=0;clk_in=0;#5 reset=1;endalways #10 clk_in=~clk_in;endmodule波形图如下:2、奇数分频对于对占空比没有特殊要求的奇数分频,需要对上升沿和下降沿脉冲进行计数,利用下降沿产生的波形移相半个输入脉冲的作用,最后用错位“异或”法实现。

在verilog中,求平均数,奇数和偶数的处理方法

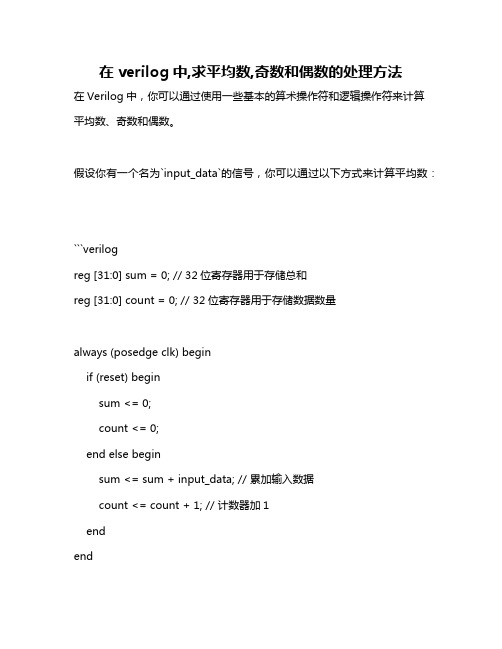

在verilog中,求平均数,奇数和偶数的处理方法在Verilog中,你可以通过使用一些基本的算术操作符和逻辑操作符来计算平均数、奇数和偶数。

假设你有一个名为`input_data`的信号,你可以通过以下方式来计算平均数:```verilogreg [31:0] sum = 0; // 32位寄存器用于存储总和reg [31:0] count = 0; // 32位寄存器用于存储数据数量always (posedge clk) beginif (reset) beginsum <= 0;count <= 0;end else beginsum <= sum + input_data; // 累加输入数据count <= count + 1; // 计数器加1endend// 计算平均数reg [31:0] average;always (posedge clk) beginif (reset) beginaverage <= 0;end else beginaverage <= sum / count; // 计算平均数,注意这里需要整数除法 endend```对于奇数和偶数的处理,你可以使用简单的逻辑操作符:```verilogreg [31:0] is_odd; // 存储是否为奇数的标志位reg [31:0] is_even; // 存储是否为偶数的标志位always (posedge clk) beginif (reset) beginis_odd <= 0;is_even <= 0;end else beginif (input_data % 2 == 1) begin // 如果输入数据是奇数is_odd <= 1; // 设置奇数标志位end else begin // 如果输入数据是偶数is_even <= 1; // 设置偶数标志位endendend```请注意,这些代码示例仅供参考,你可能需要根据具体的应用场景和硬件平台进行适当的修改。

verilogHDL分频器(奇数分频和偶数分频)

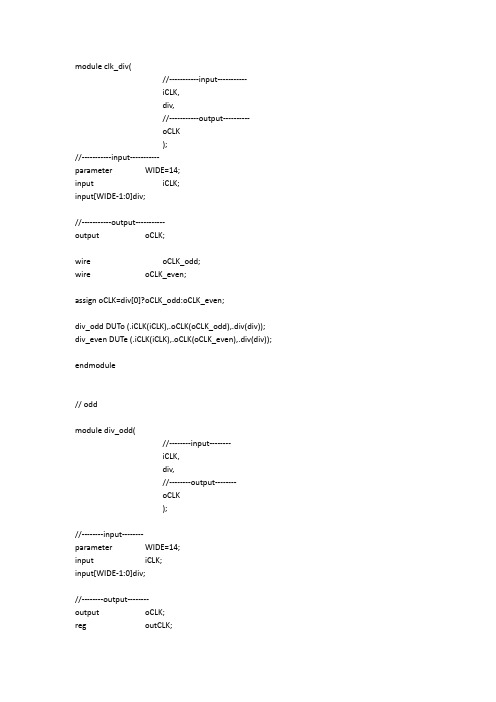

module clk_div(//-----------input-----------iCLK,div,//-----------output----------oCLK);//-----------input-----------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//-----------output-----------output oCLK;wire oCLK_odd;wire oCLK_even;assign oCLK=div[0]?oCLK_odd:oCLK_even;div_odd DUTo (.iCLK(iCLK),.oCLK(oCLK_odd),.div(div)); div_even DUTe (.iCLK(iCLK),.oCLK(oCLK_even),.div(div));endmodule// oddmodule div_odd(//--------input--------iCLK,div,//--------output--------oCLK);//--------input--------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//--------output--------output oCLK;reg outCLK;/*=========================== solve 1=========================== reg cout;reg[WIDE-1:0] cnt;initial cnt=0;wire inCLK;reg cc;initial cc=0;always @(posedge cout)cc<=~cc;assign inCLK = iCLK^cc;always @(posedge inCLK)beginif(cnt<(div[WIDE-1:1]))begincnt<=cnt+1;cout<=1'b0;endelsebegincnt<=0;cout<=1'b1;endendalways @(negedge iCLK)outCLK <= cout;assign oCLK=cc;*///======================== //solve 2//======================== reg[WIDE-1:0] cnt_a;initial cnt_a=0;reg[WIDE-1:0] cnt_b;initial cnt_b=0; reg cout_a;reg cout_b;always @(negedge iCLK)beginelse if(cnt_a<=(div[WIDE-1:1]))begincnt_a=cnt_a+1;cout_a=1'b1;endelse if(cnt_a>(div[WIDE-1:1])&&cnt_a<(div[WIDE-1:0]-1))begincout_a=1'b0;cnt_a=cnt_a+1;endelsebegincnt_a=0;endendalways @(posedge iCLK)beginif(cnt_b<=(div[WIDE-1:1]))begincnt_b=cnt_b+1;cout_b=1'b1;endelse if(cnt_b>(div[WIDE-1:1])&&cnt_b<(div[WIDE-1:0]-1))begincout_b=1'b0;cnt_b=cnt_b+1;endelsebegincnt_b=0;endendassign oCLK = cout_a&cout_b;endmodule//evenmodule div_even(//--------input--------iCLK,div,//--------output--------oCLK);//--------input--------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//--------output--------output oCLK;reg oCLK;initial oCLK = 1'b0;reg[WIDE-1:0] cnt;initial oCLK = 0;always @(posedge iCLK)beginif(cnt<(div[WIDE-1:1]-1))cnt <= cnt + 1;elsebegincnt <= 0;oCLK <= ~oCLK;endendendmodule//============================//testbench//============================/*module clk_div_test;//-----------input-----------parameter WIDE=14;reg iCLK;reg[WIDE-1:0] div;//-----------output-----------wire oCLK;clk_div cc(.iCLK(iCLK),.div(div),.oCLK(oCLK));always #20 iCLK = ~iCLK;initialbeginiCLK = 0;div=14'd7;#1000 $stop;endendmodule*/module clk_div14bits(clk,a,clkout);input clk,a;output clkout;reg clkout;wire oCLK1,oCLK2;clk_div cc1(.div(14'd8),.iCLK(iCLK),.oCLK(oCLK1)); clk_div cc2(.div(14'd9),.iCLK(iCLK),.oCLK(oCLK2));always @(a or posedge clkin)beginif(a==1)clkout=oCLK1;elseclkout=oCLK2;endendmodule//测试代码//testbenchmodule clk_div14bits_test;//-----------input-----------parameter WIDE=14;reg clk;reg[WIDE-1:0] div;//-----------output-----------wire oCLK;clk_div14bits cc3(.clk(clk),.a(a),.clkout(clkout)); always #20 clk = ~clk;initialbeginiCLK = 0;div=14'd7;#1000 $stop;EndModelsim仿真结果1.七分频2.四分频。

实验六Verilog设计分频器计数器电路

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

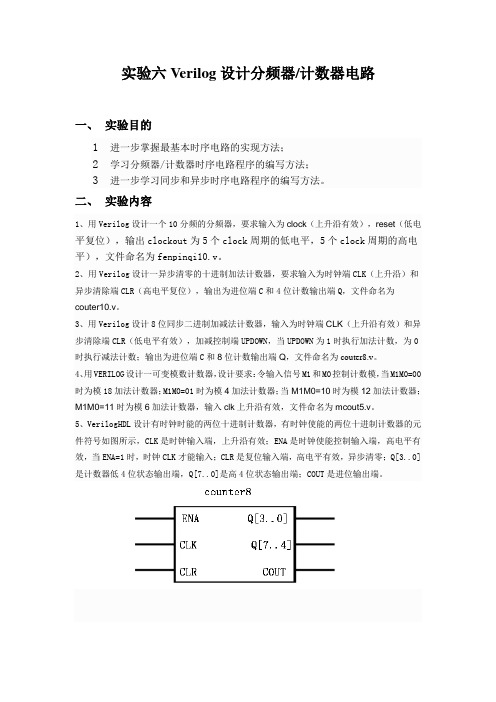

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

用Verilog语言实现奇数倍分频电路3分频5分频7分频

用Verilog语言实现奇数倍分频电路3分频5分频7分频Verilog是一种硬件描述语言(HDL),用于描述数字电路的行为和结构。

使用Verilog语言实现奇数倍分频电路可以分为以下几个步骤:1.定义输入和输出端口通过module关键字定义一个模块,并指定输入和输出端口的信号。

```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7x```2.定义局部变量和计数器定义一个局部变量和一个计数器,用于跟踪时钟周期并确定何时输出。

```verilogreg [2:0] count;```3.实现分频逻辑使用always块,根据计数器的值判断何时输出,并在输出端口上更新信号。

```verilogif (count == 3'b000) beginout_3x <= !out_3x;endif (count == 3'b001) beginout_5x <= !out_5x;endif (count == 3'b010) beginout_7x <= !out_7x;endcount <= count + 1;end```4.结束模块使用endmodule关键字结束模块定义。

```verilogendmodule完整的Verilog代码如下:```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7xreg [2:0] count;if (count == 3'b000) begin out_3x <= !out_3x;endif (count == 3'b001) begin out_5x <= !out_5x;endif (count == 3'b010) begin out_7x <= !out_7x;endcount <= count + 1;endmodule```以上代码实现了一个奇数倍分频电路,其中输入时钟信号为`clk`,输出分别是3倍分频的信号`out_3x`,5倍分频的信号`out_5x`和7倍分频的信号`out_7x`。

verilog时钟分频设计

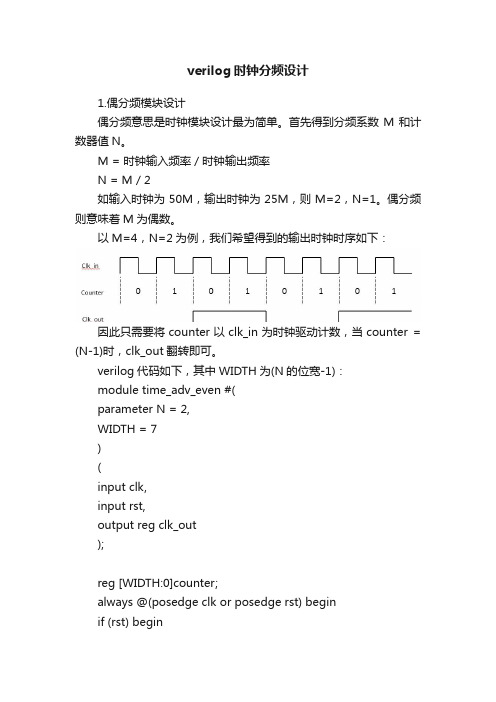

verilog时钟分频设计1.偶分频模块设计偶分频意思是时钟模块设计最为简单。

首先得到分频系数M和计数器值N。

M = 时钟输入频率 / 时钟输出频率N = M / 2如输入时钟为50M,输出时钟为25M,则M=2,N=1。

偶分频则意味着M为偶数。

以M=4,N=2为例,我们希望得到的输出时钟时序如下:因此只需要将counter以clk_in为时钟驱动计数,当counter = (N-1)时,clk_out翻转即可。

verilog代码如下,其中WIDTH为(N的位宽-1):module time_adv_even #(parameter N = 2,WIDTH = 7)(input clk,input rst,output reg clk_out);reg [WIDTH:0]counter;always @(posedge clk or posedge rst) beginif (rst) begin// resetcounter <= 0;endelse if (counter == N-1) begincounter <= 0;endelse begincounter <= counter + 1;endendalways @(posedge clk or posedge rst) beginif (rst) begin// resetclk_out <= 0;endelse if (counter == N-1) beginclk_out <= !clk_out;endendendmoduletestbench测试8分频即N=4,ISE仿真结果如下:2.奇分频模块设计奇分频需要通过两个时钟共同得到。

首先得到分频系数M和计数器值N。

M = 时钟输入频率 / 时钟输出频率N = (M-1) / 2如输入时钟为50M,输出时钟为10M,则M=5,N=2。

奇分频则意味着M为奇数。

用Verilog+HDL语言设计分频器和32位计数器

i<i+1l

end

cs)∥有片选信号

end endrnodule

begin if(addr)

aceuh<2data}

该模块已通过软件仿真,符合设计要求。并已将程序下载到FPGA芯片,在电路板上与 系统进行联调,已证明设计达到预期功能,正式投入使用。

参 考 文 献

1夏宇闻.复杂数字电路与系统的VerilogHDL设计技术.北京t北京航空航天大学出版杜,1999.1—86 2阎石鼓字电子技术基础.北京:高等教育出版社.1 997.224--295 3束万焘·罗 车,吴顺军.CPI,D技术及其盥用西安:西安电子科技大学出版社,1999.30】oo

end end

output

elkl.c}//输出时钟和计数进位信号

j

wirte[15

reg

பைடு நூலகம்

O]data—reg·dataI

c,clkl{

if(i>=119) 计数值的高16位数和低

begin

∥对输人时钟进行J20分频

reg[1 5:O]aceub.aecul;

1

6位数

j<=0; clkl<=~clkl;

第23卷第6期 2002年1 1月

微计算机应用

MICROCOMPUTER APPLICATIONS

Vol

23.N。.6

Nov-,2002

用Ver|log

HDL语言设计分频器和32位计数器

谈艳云 罗志强

100083)

仍局

(北京航空航天大学电子工程东北京

擅要t介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片.

+PLUS

II仿真正是一种实用的EDA软件,它具有原理图输入和文本输入(采用硬件描述语

VERILOG 分频原理

VERILOG 分频原理众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

因此很多招聘单位在招聘时往往要求应聘者写一个分频器(比如奇数分频)以考核应聘人员的设计水平和理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

分频器电路的Verilog设计

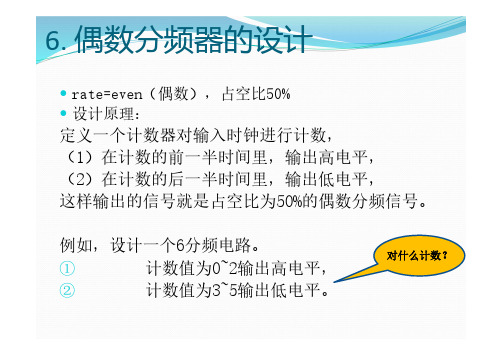

6. 偶数分频器的设计rate=even(偶数),占空比50%设计原理:定义一个计数器对输入时钟进行计数,(1)在计数的前一半时间里,输出高电平,(2)在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

例如,设计一个6分频电路。

对什么计数?①计数值为0~2输出高电平,②计数值为3~5输出低电平。

上升沿计数一个计数周期0112分频module divder_even(clkin,clkout);parameter n=2;input clkin;output clkout;integer cnt;reg clkout;always@(posedge clkin)beginif(cnt<n-1) cnt<=cnt+1;else cnt<=0;endalways@(cnt)beginif(cnt<n/2) clkout<=1'b1;else clkout<=1'b0;end endmodule计数过程判断赋值过程module divder_even(clkin,clkout);parameter n=2;input clkin;output clkout;integer cnt;reg clkout;always@(posedge clkin)beginif(cnt==n/2-1)begincnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule 2分频分析4分频分析二分频四分频知识小结1.移位寄存器的verilog描述。

2.偶数分频的verilog描述。

作业1.设计一个5位串入并出的移位寄存器。

Clear :同步清零;clkin :时钟输入;databit :位输入y[4..0]并行数据输出;2.设计一个4位并入串出的移位寄存器Clear :同步清零;clkin :时钟输入(移位);dataIn :并行数据输入,y :串行数据输出。

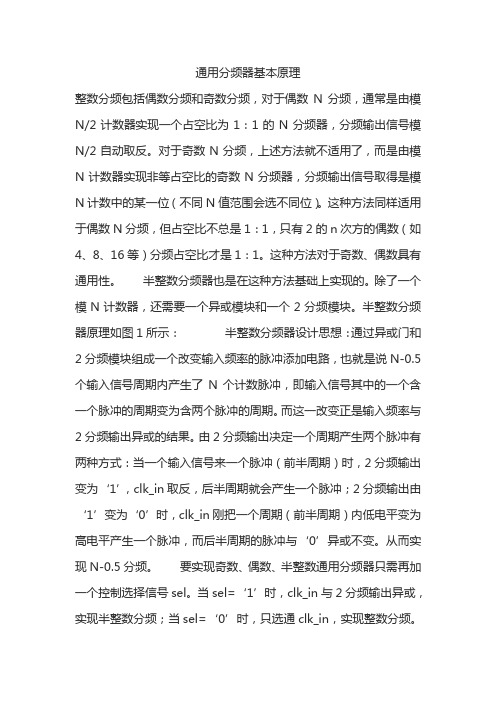

通用分频器基本原理

通用分频器基本原理整数分频包括偶数分频和奇数分频,对于偶数N分频,通常是由模N/2计数器实现一个占空比为1:1的N分频器,分频输出信号模N/2自动取反。

对于奇数N分频,上述方法就不适用了,而是由模N计数器实现非等占空比的奇数N分频器,分频输出信号取得是模N计数中的某一位(不同N值范围会选不同位)。

这种方法同样适用于偶数N分频,但占空比不总是1:1,只有2的n次方的偶数(如4、8、16等)分频占空比才是1:1。

这种方法对于奇数、偶数具有通用性。

半整数分频器也是在这种方法基础上实现的。

除了一个模N计数器,还需要一个异或模块和一个2分频模块。

半整数分频器原理如图1所示:半整数分频器设计思想:通过异或门和2分频模块组成一个改变输入频率的脉冲添加电路,也就是说N-0.5个输入信号周期内产生了N个计数脉冲,即输入信号其中的一个含一个脉冲的周期变为含两个脉冲的周期。

而这一改变正是输入频率与2分频输出异或的结果。

由2分频输出决定一个周期产生两个脉冲有两种方式:当一个输入信号来一个脉冲(前半周期)时,2分频输出变为‘1’,clk_in 取反,后半周期就会产生一个脉冲;2分频输出由‘1’变为‘0’时,clk_in 刚把一个周期(前半周期)内低电平变为高电平产生一个脉冲,而后半周期的脉冲与‘0’异或不变。

从而实现N-0.5分频。

要实现奇数、偶数、半整数通用分频器只需再加一个控制选择信号sel。

当sel=‘1’时,clk_in与2分频输出异或,实现半整数分频;当sel=‘0’时,只选通clk_in,实现整数分频。

通用分频器原理如图2所示:Verilog语言的实现本设计采用层次化的设计方法,首先设计通用分频器中各组成电路元件,然后通过元件例化的方法,调用各元件,实现通用分频器。

1、选择异或门模块half_select:modulehalf_select(sel,a,b,c);outputc;inputsel,a,b; xoru1(w,a,b); assignc=sel?w:a; (当sel=‘1’时,clk_in与2分频输出异或,实现半整数分频;当sel=‘0’时,只选通clk_in,实现整数分频。

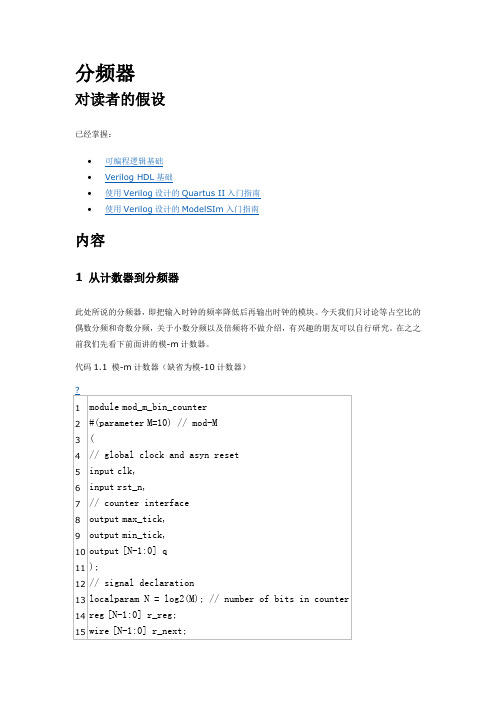

分频器

分频器对读者的假设已经掌握:∙可编程逻辑基础∙Verilog HDL基础∙使用Verilog设计的Quartus II入门指南∙使用Verilog设计的ModelSIm入门指南内容1 从计数器到分频器此处所说的分频器,即把输入时钟的频率降低后再输出时钟的模块。

今天我们只讨论等占空比的偶数分频和奇数分频,关于小数分频以及倍频将不做介绍,有兴趣的朋友可以自行研究。

在之之前我们先看下前面讲的模-m计数器。

代码1.1 模-m计数器(缺省为模-10计数器)根据这个模-m计数器,我们再写一个testbench。

代码1.2 模m-计数器的testbench(重新配置为模-10计数器)但是我在使用Quartus II + Modelsim_Altera仿真的时候出现了下面的错误提示。

代码2的第10行,变量N未定义,然后第11行用N来索引的q数组也没有定义。

奇怪了,我在Quartus II都能综合通过,而且RTL视图也是正确的,为什么Modelsim_Altera就不可以这样定义呢?咳,把常量(localparam)换成参数(parameter)即可。

代码1.3 改进后的模-m计数器(重新配置为模-10计数器)修改完,在Quartus II 里再综合一下。

接下来就是按照[文档].艾米电子 - 使用Verilog 设计的Quartus II入门指南再做一次仿真。

告诉大家一个技巧,如果执行完一次RTL 级或门级的仿真,那么Quartus II 会为我们的主模块及其testbench生成do 文件的。

这样假如有错误,就无需重新启动Modelsim_Altera ,只需重新load 一下do 文件即可。

(路径格式:Quarter II 工程文件夹\simulation\modelsim \mod_m_bin_counter_run_msim_rtl_verilog.do ) 下面看下RTL 级仿真波形。

下面讨论一下如何测量波形的长度,我们注意两个工具。

使用VHDL进行分频器设计

使用VHDL 进行分频器设计作者:ChongyangLee摘要使用VHDL 进行分频器设计作者:ChongyangLee本文使用实例描述了在FPGA/CPLD 上使用VHDL 进行分频器设计,包括偶数分频、非50%占空比和50%占空比的奇数分频、半整数(N+0.5)分频、小数分频、分数分频以及积分分频。

所有实现均可通过Synplify Pro 或FPGA 生产厂商的综合器进行综合,形成可使用的电路,并在ModelSim 上进行验证。

目录概述 (1)计数器 (1)普通计数器 (1)约翰逊计数器 (3)分频器 (4)偶数分频器 (4)奇数分频器 (6)半整数分频器 (9)小数分频器 (11)分数分频器 (15)积分分频器 (18)概述分频器是数字电路中最常用的电路之一,在FPGA 的设计中也是使用效率非常高的基本设计。

基于FPGA 实现的分频电路一般有两种方法:一是使用FPGA 芯片内部提供的锁相环电路,如ALTERA 提供的PLL (Phase Locked Loop),Xilinx 提供的DLL(Delay Locked Loop);二是使用硬件描述语言,如VHDL、Verilog HDL 等。

使用锁相环电路有许多优点,如可以实现倍频;相位偏移;占空比可调等。

但FPGA 提供的锁相环个数极为有限,不能满足使用要求。

因此使用硬件描述语言实现分频电路经常使用在数字电路设计中,消耗不多的逻辑单元就可以实现对时钟的操作,具有成本低、可编程等优点。

计数器计数器是实现分频电路的基础,计数器有普通计数器和约翰逊计数器两种。

这两种计数器均可应用在分频电路中。

普通计数器最普通的计数器是加法(或减法)计数器。

下面是加法计数器的VHDL实现,其Synplify Pro下的RTL View如图1所示。

--file Name: ripple.vhd--Description: 带复位功能的加法计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ripple isgeneric (width: integer := 4);port(clk, rst: in std_logic;cnt: out std_logic_vector(width - 1 downto 0));end ripple;architecture a of ripple issignal cntQ: std_logic_vector(width - 1 downto 0);beginprocess(clk, rst)beginif (rst = '1') thencntQ <= (others => '0');elsif (clk'event and clk = '1') thencntQ <= cntQ + 1;end if ; end process ;cnt <= cntQ;end a;代码 1 加法计数器 VHDL 代码图 1 加法计数器 RTL 视图加法计数器的Test Bench 代码如下所示,在ModelSim 下进行功能仿真,仿真 波形结果如图 2所示。

奇数分频器VHDL设计

奇数分频器1 引言分频器在CPLD/FPGA设计中使用频率非常高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源,但是对于要求奇数倍分频、小数倍分频的应用场合却往往不能满足要求。

硬件工程师希望有一种灵活的设计方法,根据需要,在实验室就能设计分频器并马上投入使用,更改频率时无需改动原器件或电路板,只需重新编程,在数分钟内即可完成。

对于偶数分频,使用一模N计数器模块即可实现,即每当模N计数器从0开始计数至N时,输出时钟进行翻转,同时使计数器复位,使之从0开始重新计数,以此循环即可实现。

但对于奇数分频,实现50%的占空比却是比较困难的。

下面给出占空比50%的奇数分频器的设计源程序和仿真结果。

2 VHDL程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;--添加库ENTITY fdiv IS --设计实体PORT( clk,reset : IN STD_LOGIC;--端口说明preset: IN INTEGER;--preset:分频预置数clkout : OUT STD_LOGIC);- -clkout :分频后得到的时钟END fdiv;ARCHITECTURE behave OF fdiv IS--设计构造体SIGNAL s1,s2 : STD_LOGIC;--内部信号s1,s2 SIGNAL cnt : INTEGER RANGE 0 TO preset-1;--模为preset的计数信号BEGINP1: PROCESS(clk,reset) --计数器BEGINIF reset='1' THENcnt<=0;ELSIF clk'event AND clk='1' THENIF cnt=0 THENcnt<=preset-1;ELSEcnt<=cnt-1;END IF;END IF;END PROCESS;P2: PROCESS(clk,reset) --信号1 BEGINIF reset='1' THENs1<='1';ELSIF clk'event AND clk='1' THENIF cnt=0 THEN --计数信号为0时,S1翻转s1<=NOT s1;ELSEs1<=s1;END IF;END IF;END PROCESS;P3: PROCESS(clk,reset) --信号2 BEGINIF reset='1' THENs2<='1';ELSIF clk'event AND clk='0' THENIF cnt=(preset-1)/2 THEN --计数信号为N时,S2翻转s2<=NOT s2;ELSEs2<=s2;END IF;END IF;END PROCESS;clkout<= s1 XOR s2; -- 异或输出END BEHA VE;程序说明:以上程序实现任意奇数为PRESET的50%占空比分频,计数器CNT的模值为PRESET,计数器是为了控制信号S1和信号S2,使两信号保持恒定的时间差。

基于Verilog HDL数字频率计的设计

EDA设计课程论文题目基于Verilog HDL数字频率计的设计学院通信学院专业班级学生姓名大彬哥指导教师大陆会2013年5月17日EDA设计基础实验论文摘要频率是常用的物理量, 在实际测量过程中总是尽可能地把被测参量转换成频率参量进行测量。

例如工程中用振弦式方法测量力、时间测量、速度控制等, 都可转化为频率测量。

随着科学技术与计算机应用的不断发展, 以单片机作为核心的测量控制系统层出不穷。

在被测信号中, 较多的是模拟和数字开关信号, 此外还经常遇到以频率为参数的测量信号, 例如流量、转速、晶体压力传感器以及经过参变量一频率转换后的信号等等。

因此, 频率测量是电子测量技术中最基本的测量之一。

电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法,如周期测频法。

直接测频法适用于高频信号的频率测量,间接测频法适用于低频信号的频率测量。

本文运用现代电子设计工具, 采用V er ilogHDL语言在CPLD器件上实现了简易数字频率计的设计。

在10Hz ~ 100MHz 频率测量范围内, 该频率计能根据输入被测频率信号, 自动调整测试量程进行测试并给出测试结果的BCD 码及七段LED 译码显示。

具有体积小、可靠性高、功耗低的特点。

关键词:数字频率计 Verilog_HDL 分频计数IEDA设计基础实验论文AbstractFrequency is a common physical quantities, in actual measurement process is always possible, the measured parameters are converted into the frequency parameter measurement. For example, engineering with vibrating method for measuring force, measurement of time, velocity control, can all be converted into frequency measurement. With the development of science and technology and the continuous development of computer applications, to single-chip microcomputer as the core control system for measuring the emerge in an endless stream. In the measured signal, more is analog and digital switch signal, in addition also frequently encountered with a frequency parameter measurement signal, such as flow rate, rotational speed, crystal pressure sensor and the variable frequency converted signal and so on. Therefore, the frequency measurement is the electronic measurement technology in the most fundamental measurement of.Electronic counter frequency measurement in two ways : one is the direct frequency measurement Law, or within a certain time gates of measured signal pulse number; two is the indirect frequency measurement Law, such as cycle frequency measurement method. Direct frequency measurement Law is applicable to the high frequency signal frequency measurement, indirect frequency measurement Law is applicable to low-frequency signals in the frequency measurement. The use of modern electronic design tool, using V Er ilogHDL language in CPLD device achieves simple digital frequency meter design. In the10Hz100MHz frequency measurement range, the frequency meter according to input the measured frequency signal, automatic adjustment and test range tested and the test results are given in the BCD code and the seven LED decoding display. Has the advantages of small volume, high reliability, low power consumption.Keywords: digital frequency meter Verilog_HDL frequency countingIIEDA设计基础实验论文目录摘要 (I)ABSTRACT (II)第1章绪论 (1)1.1数字频率计概况 (1)1.2本文研究内容 (1)1.3目的与意义 (2)第2章系统设计方案 (3)2.1数字频率计总体设计方案 (3)2.1.1 放大整形 (3)2.1.2 SW1、SW2、SW3按键 (3)2.1.3 标准时钟 (3)2.1.4 LED显示模块 (3)2.2系统的参数 (4)2.2.1 频率测量 (4)2.2.2 频率测量方法 (4)2.2.3 功能及技术指标 (4)第3章数字频率计的基本原理 (6)3.1计数模块COUNTER (6)3.2门控模块GATE_CONTROL (6)3.3分频模块FDIV (7)3.4寄存器模块FLIP_LATCH (7)3.5多路选择模块DATA_MUX (8)3.6动态位选模块DISPSELECT (9)3.7BCD译码模块DISPDECODER (11)第4章数字频率计软件设计 (15)4.1软件实现功能综述 (15)4.2多路选择模块DATA_MUX的设计 (15)4.2.1 多路选择模块data_mux的接口电路 (15)4.2.2 多路选择模块data_mux程序设计 (16)4.3动态位选模块DISPSELECT的设计 (17)4.3.1 动态位选模块dispselec的接口电路 (17)4.3.2 动态位选模块dispselec的程序设计 (17)IIIEDA设计基础实验论文4.4BCD译码模块DISPDECODER的设计 (18)4.4.1 BCD译码模块dispdecoder的接口电路 (18)4.4.2 BCD译码模块dispdecoder的程序设计 (19)第5章数字频率计系统的仿真分析 (23)5.1系统原理图 (23)5.2多路选择模块DATA_MUX的仿真分析 (24)5.3动态位选模块DISPSELEC的仿真分析 (25)5.4BCD译码模块DISPDECODER的仿真分析 (25)5.5软硬件调试 (26)结论 (28)参考文献 (29)IVEDA设计基础实验论文第1章绪论1.1数字频率计概况频率是常用的物理量, 在实际测量过程中总是尽可能地把被测参量转换成频率参量进行测量。

Verilog实现三分频的多种方法(附有代码)

用Verilog语言实现奇数倍分频电路 3分频 5分频 7分频分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去,这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,占空比不限定时,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

分频的verilog语言实现

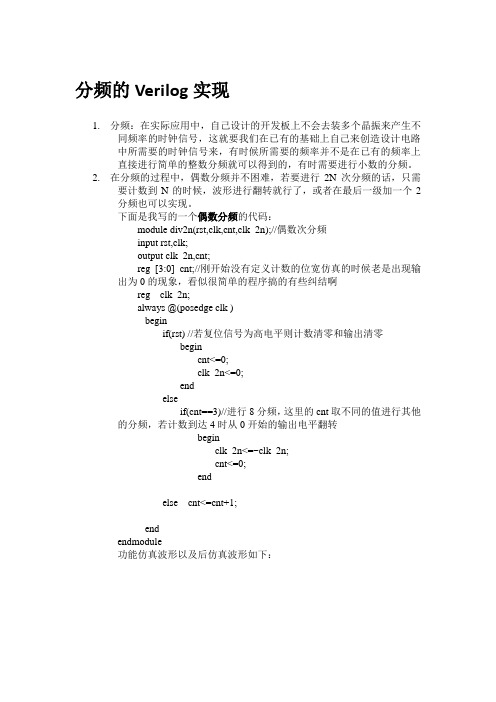

分频的Verilog实现1.分频:在实际应用中,自己设计的开发板上不会去装多个晶振来产生不同频率的时钟信号,这就要我们在已有的基础上自己来创造设计电路中所需要的时钟信号来,有时候所需要的频率并不是在已有的频率上直接进行简单的整数分频就可以得到的,有时需要进行小数的分频。

2.在分频的过程中,偶数分频并不困难,若要进行2N次分频的话,只需要计数到N的时候,波形进行翻转就行了,或者在最后一级加一个2分频也可以实现。

下面是我写的一个偶数分频的代码:module div2n(rst,clk,cnt,clk_2n);//偶数次分频input rst,clk;output clk_2n,cnt;reg [3:0] cnt;//刚开始没有定义计数的位宽仿真的时候老是出现输出为0的现象,看似很简单的程序搞的有些纠结啊reg clk_2n;always @(posedge clk )beginif(rst) //若复位信号为高电平则计数清零和输出清零begincnt<=0;clk_2n<=0;endelseif(cnt==3)//进行8分频,这里的cnt取不同的值进行其他的分频,若计数到达4时从0开始的输出电平翻转beginclk_2n<=~clk_2n;cnt<=0;endelse cnt<=cnt+1;endendmodule功能仿真波形以及后仿真波形如下:从后仿真中可以明显的看出输出时钟信号和输入的标准信号有延迟时间,在计数寄存器中出现了相邻两个数之间的竞争,但是没有出现在时钟的上升沿,不会引起最后实现的错误!奇数分频:若奇数分频中不考虑占空比的话,分频代码可以按照偶数分频的思路来写,但是大多数情况下需要考虑的是使占空比设计为50%。

若要进行奇数次的分频而且要求占空比为50%可以采用:用两个计数器,一个由输入时钟下降沿触发,一个由输入时钟的上升沿触发,最后将两个计数器的输出进行相或,就可得到。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于Verilog HDL的分频器设计

Verilog HDL的分频器设计作者:nyj

文中的第一个模块为通用的偶分频模块,第二个模块为通用的奇分频模块,2个模块分频占空比都为1:1,使用时只需将相应模块中parameter DIV_N = N; 中的N改为想要的分频数即可。

/********************************************

**File name: Divide_Frequency_module

**Author: nyj

**Version:

**Data: 11/7/17

**Description: Even divide FPGA CLK frequency

**********************************************/

module Divide_Frequency_module

(

input CLK_In,

input RSTn,

output CLK_Out

);

/*****************************************/

parameter DIV_N = N;

/***********************************************/

reg [DIV_N:0] count;

reg clk_N;

always @ ( posedge CLK_In or negedge RSTn )

begin

if(!RSTn)

begin

count <= 1'b0;

clk_N <= 1'b0;

end

else if( count == DIV_N/2 - 1'b1)

begin

count <= 1'b0;

clk_N <= ~clk_N;

else

count <= count + 1'b1;

end

/***********************************************/ assign CLK_Out = clk_N;

/*************************************************/ endmodule

module Divide_Frequency_module

(

input CLK_In,

input RSTn,

output CLK_Out

);

/*****************************************/ parameter DIV_N = N;

/***********************************************/ reg [DIV_N:0] count_p;

always @ ( posedge CLK_In or negedge RSTn )

begin

if(!RSTn)

count_p <= 1'b0;

else if( count_p == DIV_N - 1'b1)

count_p <= 1'b0;

else

count_p <= count_p + 1'b1;

end

/***********************************************/ reg [DIV_N:0] count_n;

always @ ( negedge CLK_In or negedge RSTn)

if(!RSTn)

count_n <= 1'b0;

else if(count_n == DIV_N - 1'b1)

count_n <= 1'b0;

else

count_n <= count_n + 1'b1;

end

/************************************************/ reg clk_N_p;

always @ ( posedge CLK_In or negedge RSTn )

begin

if(!RSTn)

clk_N_p <= 1'b0;

else if(count_p <= DIV_N/2)

clk_N_p <= 1'b1;

else

clk_N_p <= 1'b0;

end

/***********************************************/

reg clk_N_n;

always @ ( negedge CLK_In or negedge RSTn )

begin

if(!RSTn)

clk_N_n <= 1'b0;

else if(count_n <= DIV_N/2)

clk_N_n <= 1'b1;

else

clk_N_n <= 1'b0;

end

/***************************************************/ assign CLK_Out = (clk_N_p & clk_N_n) ? 1'b1 : 1'b0;

/*************************************************/ endmodule。