逐次逼近型AD原理及应用

AD转换器原理(逐次比较式、双积分式)

T1 T2 Ui Ur

(2.3)

2.3式所明:T2与输入电压的平均值 U i 成正比 设时钟周期为T0,计数器容量为N1,则T1=N1To、T2=N2To,2.3式可改写为

N1 N2 Ui Ur

(2.4)

2.4式所明:N2与输入电压的平均值 U i 成正比( N2 ∝ U i )

N2 ∝ Ui关系的演示

阶段T1结束,积分器输出

1 U 01 RC

t2

t1

U i dt

T1 Ui RC

(2.1)

3.定值积分阶段T2:在 t2 时刻令S1断开的同时,使与Ui极性相反的基准电 压接入积分器。本例设Ui为正值,则令S3闭合,于是积分器开始对基准电压UR 定值积分,积分器输出从U01值向零电平斜变,同时,计数器也重新从零计数, 当积分输出达到零电平时刻(即t3),比较器翻转,此时控制电路令计数器关门, 计数器保留的计数值为N2。定值积分阶段T2结束时,积分器输出电平为零, 则有

2.定时积分阶段----第一次积分,S1接通 特点:定时积分T1固定, UO1∝(正比于) Ui 双积分式A/D转换器原理概述

3.定值积分阶段----第二次积分,S3/S4接通 特点:定值积分(反向),N2∝UO1∝Ui

(假定输入电压增加为2Ui)

①

积分器输出电压还是负向 积分,积分时间T1不变, 但是,斜率将增加一倍。

在T2期间,积分器反向 积分的斜率不变(因UR不 变),但是,返回到零点的 时间T2将增加一倍。 由于T2增加一倍,因而 在T2期间的计数值N2也 将增加一倍。 N2T0

②

③

1.预备阶段Leabharlann ---复零,S4接通双积分式A/D转换器原理概述

结果表示逐次逼近型AD转换器原理框图

比较判断

8g<13g 12g<13g

砝码去留

留 留

结果表示

1 1

3

4

8g+4g+2g

8g+4g+1g

14g>13g

13g=13g

去

留

0

1

上页

下页

返回

第 7章

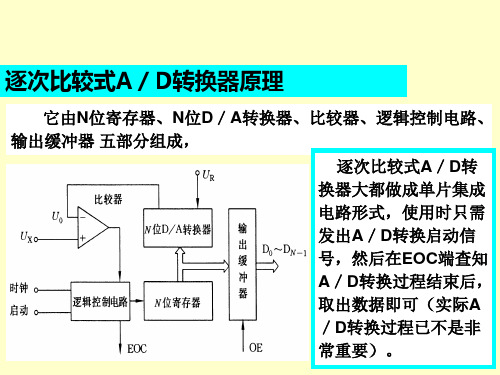

逐次逼近型A/D转换器原理框图

输出数字量

输 出 寄存器 节 拍 脉 冲 发 生 器 模拟信号输入 电 压 比 较 器

CP

逐次逼 近寄存器

D/A

拍 时钟 脉 脉冲 冲 发 生 器

C

C0 C1 C2 C3

0 • C3 • C 0

GND D9 D8 D7 D6 D5

4

5 6 7 8

RF UREF UDD D0 D1 D2 D3 D4

引脚功能 Iout1、Iout2:电流输出端 GND:接地端 D9~D0:数字信号输入端 UDD:电源输入端,5 ~ 10V

UREF:基准电源,–10V ~ +10V

RF:反馈信号输入端

CC7520 外部引脚图

上页

下页

返回

第 7章

CC7520 D/A转换器应用电路

UREF

15

UDD

14 16

D0 D1 D9 ……

13 12

CC7520

4 3

1

2

_ +

+

U0

UREF UO= – 210

(D9 29+D8 28+…+D121+D020)

上页 下页 返回

第 7章

程控三角波/方波发生器

逐次逼近型AD

逐次逼近型AD————————————————————————————————作者:————————————————————————————————日期:逐次逼近型ADC其工作原理可用天平秤重过程作比喻来说明。

若有四个砝码共重15克,每个重量分别为8、4、2、1克。

设待秤重量Wx = 13克,可以用下表步骤来秤量:首先把待称重的重物放在托盘上,在另外一边的托盘上首先放上8克的砝码,8克砝码小于待测物体总重13克,所以保留该砝码;第二步将4克砝码放在托盘上,砝码总重为8+4=12克,小于待测物体总重,所以也保留;第三步将2克砝码放在托盘上,砝码总重为8+4+2=14克,大于待测物体总重,所以将2克砝码撤除;第四步将1克砝码放在托盘上,砝码总重为13克,等于待测物体总重,所以保留;最后得到待测物体为13克。

AD的转换过程与上述过程类似,每次加载砝码的过程受到一个时钟脉冲CP的控制,在AD中不存在砝码,而是采用DA转换器的输出做为上面例子中砝码的重量,而比较器就是天平。

其工作流程框图如下图所示:今以四位逐次逼近型ADC为例(设输入电压Ux=5.52 V,D/A转换器的参考电压UR=-8 V),分析其转换过程。

第一个脉冲CP到来时,使逐次逼近寄存器的最高位d3置1,其余位为0,即寄存器状态d3d2d1d0=1000,由式(9.4.1)得D/A转换器的输出电压为因Uo<Ux,故比较器输出低电平,d3位置的1被保留。

第二个脉冲CP到来时,使逐次逼近寄存器的次高位d2置1,后两位为0,即寄存器状态d3d2d1d0=1100,此时D/A转换器的输出电压Uo=8/16×12=6 V,因Uo>Ux,故比较器输出高电平,d2位置的1被取消变为0。

第三个脉冲CP到来时,d1置1,此时寄存器状态d3d2d1d0=1010,D/A转换器的输出电压Uo=8/16×10=5 V,因Uo<Ux,故比较器输出低电平,d1位置的1被保留。

AD转换

模拟电压输入 1LSB

模拟电压输入 1/2LSB

5

3、偏移误差

偏移误差是指输入信号为零时,输出信号不为零的 值,所以有时又称为零值误差。假定ADC没有非线 性误差,则其转换特性曲线各阶梯中点的连线必定 是直线,这条直线与横轴相交点所对应的输入电压 值就是偏移误差。

积分器输出

VIN

时钟

T1 T T2

t

3

三、A/D转换器的主要技术指标 1、分辨率 ADC的分辨率是指使输出数字量变化一个 相邻数码所需输入模拟电压的变化量。常用 二进制的位数表示。例如12位ADC的分辨率 就是12位,或者说分辨率为满刻度FS的 1/2 1 2 。一个10V满刻度的12位ADC能分辨输 入电压变化最小值是10V×1/ 2 1 2 =2.4mV。

ADC_CONTR寄存器

ADC_RES、 ADC_RESL寄存器

ADC中断控制寄存器

ADC典型应用电路

电压基准源

ADC实现按键输入功能

10VIN 20VIN AG

CE STS

-5V~+5V -10V~+10V

23

采用双极性输入方式,可对±5V或±10V的模拟信号

进行转换。当AD574A与80C31单片机配置时,由于 AD574A输出12位数据,所以当单片机读取转换结果 时,应分两次进行:当A0=0时,读取高8位;当A 0=1时,读取低4位。

需三组电源:+5V、VCC(+12V~+15V)、

VEE(-12V~-15V)。由于转换精度高,所 提供电源必须有良好的稳定性,并进行充分滤波, 以防止高频噪声的干扰。 低功耗:典型功耗为390mW。

结果表示逐次逼近型AD转换器原理框图

上页

下页

返回

第 7章

*7.3 模拟开关和采样-保持电路

7.3.1 模拟开关 7.3.2 采样-保持(S/H)电路

上页

下页

返回

第 7章

7.3.1 模拟开关

模拟开关用于传输模拟信号,它主要由控制电 路和开关电路两部分组成。 构成方式:双极型晶体管电路 MOS场效应晶体管

主要介绍由CMOS传输门构成的模拟开关和集 成多路模拟开关。

拍 时钟 脉 脉冲 冲 发 生 器

C

C0 C1 C2 C3

0 • C3 • C 0

2

•

• •

• •

SD J

K RD

Q1 C

1 0

•

比较器

+ +

C1

0 •

•

SD J

C0 0

K RD

Q2 C

•

•

SD J

K RD

Q3 • C

四 1 0 位 D/A 1 0 转 换 1 器

U0

U+ 0 1

1

U+ 0 1

Ui=5.52V J K

+ A2 + UO2

UREF

D9 D8 D7 D0

15 4 5 6

+15V

14 16

DZ

_ +

C

R2 20k R1

CC7520

3

1

2

A1 +

UO1

பைடு நூலகம்……

13

U01

上页

下页

返回

第 7章

7.2 模/数(A/D)转换器

概述 7.2.1 逐次逼近型A/D转换器

*7.2.2 双积分型A/D转换器

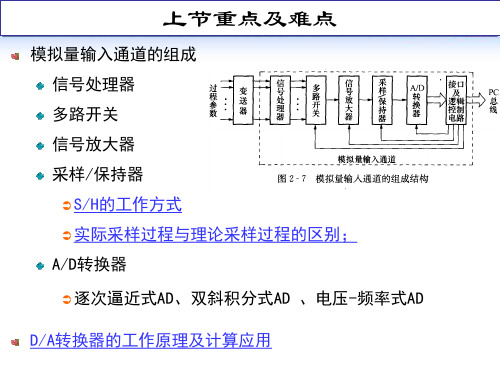

常用的几种类型的ADC基本原理及特点

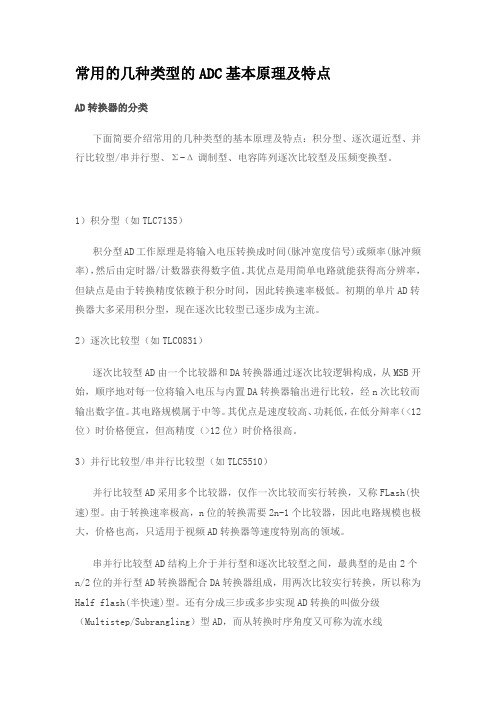

常用的几种类型的ADC基本原理及特点AD转换器的分类下面简要介绍常用的几种类型的基本原理及特点:积分型、逐次逼近型、并行比较型/串并行型、Σ-Δ调制型、电容阵列逐次比较型及压频变换型。

1)积分型(如TLC7135)积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。

其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。

初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。

2)逐次比较型(如TLC0831)逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。

其电路规模属于中等。

其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

3)并行比较型/串并行比较型(如TLC5510)并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。

由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。

串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。

还有分成三步或多步实现AD转换的叫做分级(Multistep/Subrangling)型AD,而从转换时序角度又可称为流水线(Pipelined)型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。

这类AD速度比逐次比较型高,电路规模比并行型小。

4)Σ-Δ(Sigma?/FONT>delta)调制型(如AD7705)Σ-Δ型AD由积分器、比较器、1位DA转换器和数字滤波器等组成。

图4.21逐次逼近式AD转换器原理框图

A/D转换器A/D转换器是用来通过一定的电路将模拟量转变为数字量。

模拟量可以是电压、电流等电信号,也可以是压力、温度、湿度、位移、声音等非电信号。

但在A/D转换前,输入到A/D 转换器的输入信号必须经各种传感器把各种物理量转换成电压信号。

A/D转换后,输出数字信号可以有8位、10位、12位和16位等。

AD转换器的工作原理主要介绍3种:逐次逼近法双积分法电压频率转化法1 逐次逼近法:逐次逼近式A/D是比较常见的一种A/D转换电路,转换的时间为微秒级。

采用逐次逼近法的A/D转换器是由一个比较器、D/A转换器、缓冲寄存器及控制逻辑电路组成,如图4.21所示。

基本原理是从高位到低位逐位试探比较,好像用天平称物体,从重到轻逐级增减砝码进行试探。

图4.21 逐次逼近式A/D转换器原理框图逐次逼近式A/D转换器原理框图逐次逼近法转换过程是:初始化时将逐次逼近寄存器各位清零;转换开始时,先将逐次逼近寄存器最高位置1,送入D/A转换器,经D/A转换后生成的模拟量送入比较器,称为Vo,与送入比较器的待转换的模拟量Vi进行比较,若V,该位1被保留,否则被清除。

然后再置逐次逼近寄存器次高位为1,将寄存器中新的数字量送D/A转换器,输出的Vo再与Vi比较,若VoVi,该位1被保留,否则被清除。

重复此过程,直至逼近寄存器最低位。

转换结束后,将逐次逼近寄存器中的数字量送入缓冲寄存器,得到数字量的输出。

逐次逼近的操作过程是在一个控制电路的控制下进行的。

2双积分法:采用双积分法的A/D转换器由电子开关、积分器、比较器和控制逻辑等部件组成。

如图4.22所示。

基本原理是将输入电压变换成与其平均值成正比的时间间隔,再把此时间间隔转换成数字量,属于间接转换。

图4.22 双积分式A/D转换的原理框图双积分法A/D转换的过程是:先将开关接通待转换的模拟量Vi,Vi采样输入到积分器,积分器从零开始进行固定时间T的正向积分,时间T到后,开关再接通与Vi极性相反的基准电压VREF,将VREF输入到积分器,进行反向积分,直到输出为0V时停止积分。

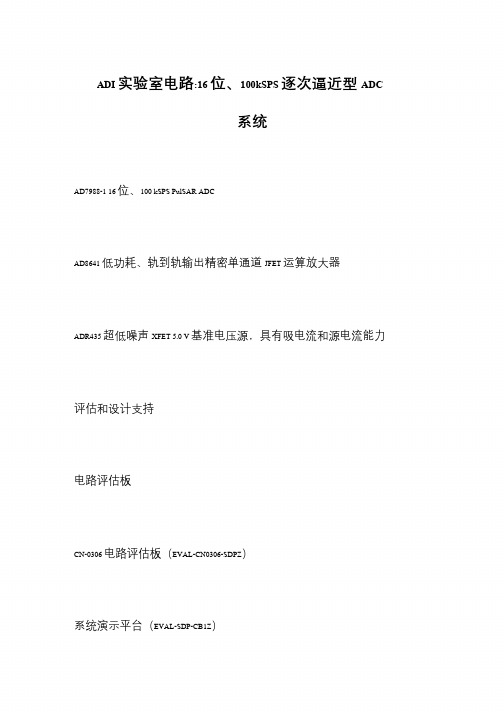

ADI实验室电路-16位、100kSPS逐次逼近型ADC系统

优势。

通常,选择高性能逐次逼近型ADC的驱动放大器处理宽范围的输入频

率。然而,当某个应用需要更低的采样速率时,便可节省大量功耗,因为降

低采样速率会相应地降低ADC功耗。

若要完全利用通过降低ADC采样速率使功耗下降的优势,则需要使用低

带宽、低功耗放大器。例如,推荐80MHz的ADA4841-1运算放大器(10V

AD7988-1是一款16位、100kSPSSARADC,其低功耗可随采样速率调整,

100kSPS时功耗为0.7mW。除了低功耗,它还具有业界领先的交流性能:

SNR=91dB,THD=-114dBc。

驱动放大器采用AD8641低功耗、精密器件,其电源电流为200μA,

增益带宽积为3MHz。AD8641可采用5V至26V的电源供电。ADC的基准

dBc)差不多。超过1kHz会加剧失真,因此不建议在更高的输入频率下使用

该电路,而由于较长的建立时间,亦不建议在多路复用器应用中使用该放大

器。注意,相对于正电源电压而言,AD8641需要至少2V的输入裕量。输

出级以轨到轨方式工作。

ADI实验室电路:16位、100kSPS逐次逼近型ADC

系统

AD7988-116位、100kSPSPulSARADC

AD8641R435超低噪声XFET5.0V基准电压源,具有吸电流和源电流能力

评估和设计支持

电路评估板

CN-0306电路评估板(EVAL-CN0306-SDPZ)

放大器(10V时功耗为2mW)可提供出色的信噪比(SNR)和总谐波失真

(THD)性能,并且在100kSPS时可将总系统功耗从17.35mW降低至7.35

2.3 逐次逼近式AD与双积分AD解析

(010…0)小,即必在001…1——000…0之间,此时 反馈比较, 次高位应为0; 确定1/4搜索范围 若U ≥U ,说明模拟量输入电压比寄存器输出的数码

IN F

(010…0)大,即必在011…1 ——010…0之间,此时

次高位应为1 ;

解:U OUT U REF 解:U OUT U REF

D 1 1 1 1 1 1 10 ( 1 1 0 0 ) 10 ( 0 0) 7.25V 2n 2 22 23 24 2 4 D 1 1 1 1 1 1 1 10 ( 1 1 1 0 ) 10 ( 0) 8.75V 2n 2 22 23 24 2 4 8

《计算机控制系统》 第二章 过程通道

D/A转换器工作原理

对 n 位D/A转换器而言,当输 入数字量为 D=Dn-1…D1D0 时, 其输出电压为

U OUT

沈阳工程学院动力系 崔长春

U REF D n 1 1 0 ( D 2 D 2 D 2 ) U n -1 1 0 REF n 2n 2

《计算机控制系统》 第二章 过程通道

沈阳工程学院动力系 崔长春

自编2-2:四位D/A转换器,基准电压为10V,当输入数 字量D为1001时,其输出的模拟量为多少? (作业)

解:U OUT U REF

D 2n

1 1 1 1 10 (1 0 2 0 3 1 4 ) 2 2 2 2 1 1 10 ( 0 0 ) 2 16 5.625V

沈阳工程学院动力系 崔长春

1、S/H的作用 在采样时刻,采集过程变量; 保持A/D的输入值在转换时间内不变;

常用的几种类型的ADC基本原理及特点

常用的几种类型的ADC基本原理及特点AD转换器的分类下面简要介绍常用的几种类型的基本原理及特点:积分型、逐次逼近型、并行比较型/串并行型、Σ-Δ调制型、电容阵列逐次比较型及压频变换型。

1)积分型(如TLC7135)积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。

其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。

初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。

2)逐次比较型(如TLC0831)逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。

其电路规模属于中等。

其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

3)并行比较型/串并行比较型(如TLC5510)并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。

由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。

串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。

还有分成三步或多步实现AD转换的叫做分级(Multistep/Subrangling)型AD,而从转换时序角度又可称为流水线(Pipelined)型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。

这类AD速度比逐次比较型高,电路规模比并行型小。

4)Σ-Δ(Sigma/FONT>del ta)调制型(如AD7705)Σ-Δ型AD由积分器、比较器、1位DA转换器和数字滤波器等组成。

逐次逼近型AD原理及应用

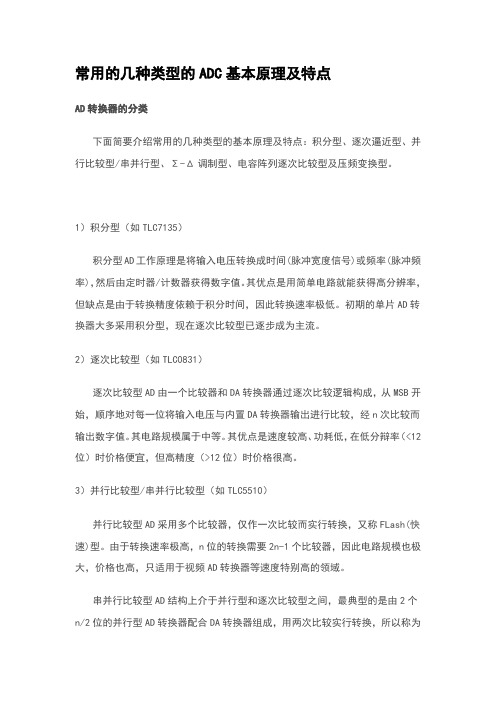

逐次逼近型AD原理及应用AD转换的基本原理和技术(逐次逼近型)1、转换方式直接转换ADC2.电路结构逐次逼近ADC包括n位逐次比较型A/D转换器如图1所示。

它由控制逻辑电路、时序产生器、移位寄存器、D/A转换器及电压比较器组成。

图1逐次比较型A/D转换器框图3、工作原理逐次逼近转换过程和用天平称物重非常相似。

天平称重物过程是,从最重的砝码开始试放,与被称物体行进比较,若物体重于砝码,则该砝码保留,否则移去。

再加上第二个次重砝码,由物体的重量是否大于砝码的重量决定第二个砝码是留下还是移去。

照此一直加到最小一个砝码为止。

将所有留下的砝码重量相加,就得此物体的重量。

仿照这一思路,逐次比较型A/D转换器,就是将输入模拟信号与不同的参考电压作多次比较,使转换所得的数字量在数值上逐次逼近输入模拟量对应值。

对11.10.1的电路,它由启动脉冲启动后,在第一个时钟脉冲作用下,控制电路使时序产生器的最高位置1,其他位置0,其输出经数据寄存器将1000……0,送入D/A转换器。

输入电压首先与D/A器输出电压(VREF/2)相比较,如v1≥VREF/2,比较器输出为1,若vI 设图11.10.1电路为8位A/D转换器,输入模拟量vA=6.84V,D/A转换器基准电压VREF=10V。

根据逐次比较D/A转换器的工作原理,可画出在转换过程中CP、启动脉冲、D7~D0及D/A转换器输出电压vO的波形,如图11.10.2所示。

由图11.10.2可见,当启动脉冲低电平到来后转换开始,在第一个CP作用下,数据寄存器将D7~D0=10000000送入D/A转换器,其输出电压v0=5V,vA与v0比较,vA>v0存1;第二个CP到来时,寄存器输出D7~D0=11000000,v0为7.5V,vA再与7.5V比较,因vA<7.5V,所以D6存0;输入第三个CP时,D7~D0=10100000,v0=6.25V;vA再与v0比较,……如此重复比较下去,经8个时钟周期,转换结束。

逐位逼近式AD转换原理图一个n位AD转换器的模数转换表达式

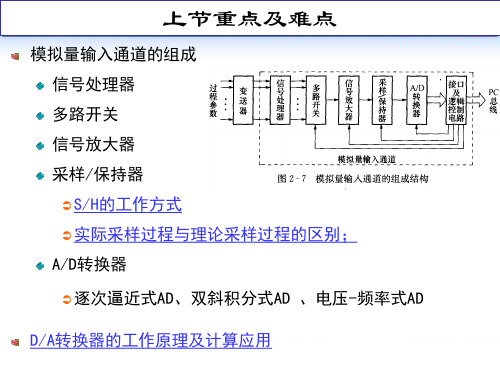

①传感器 — 将非电量转换为电信号。

②多路开关(MUX) — 分时切换各路 模拟量与采样/保持器的通路。

系统 ③放大器(IA)— 多为程控放大器, 对模拟信号进行放大。 配置

④采样/保持器(S/H)—保持模拟信号 电压。 ⑤A/D转换器— 将模拟信号转换为数字 信号。 ⑥接口电路 — 将数字信号进行整形电 平调整。

采样保持电路(S/H)

由MOS管采样开关T、保持电容Ch和运放构 成的跟随器三部分组成。

Vin

采样控制

T

Ch

S(t)

-

+

Vout

采样控制信号S(t)=1时,T导通,Vin向Ch充电,Vc和Vout跟

踪Vin变化,即对Vin采样。S(t)=0时,T截止,Vout将保持前一 瞬间采样的数值不变。

1、信号采样的过程

B、A=001时,通道S通;……当C、B、A = 111时,通道S7

选通。其结构图如图7-2-9所示,其真值表如下表所示。

Sm A 译 码 驱 动 电 平 转 换 B C INH

S0 S1 S2 S3 S4 S5 S6 S7

组成:逻辑电平转换、二进制译码器及 图2 -3 CD4051结构原理图 8个开关电路。 图7-2-9 CD4051结构图

S闭和 S断开

t

Vfo

频率输出 (三极管 T状态) T截止 T导通

t

T1

T

(a) 电路原理图

(b) 波形图

图7-2-8 电荷平衡式V/F转换原理

由积分器、比较器和整形电路构成的 VFC电路,把模拟电压变换成相应频率的 脉冲信号,其频率正比于输入电压值, 然后用频率计测量。VFC能快速响应,抗 干扰性能好,能连续转换,适用于输入 信号动态范围宽和需要远距离传送的场 合,但转换速度慢。

逐次逼近ADC原理

模数转换器其本质就是一个编码的过程,由于传输到数模转换器的自然信号随着时间的变化而变化。

为了实现对模拟信号的处理和储存,我们必须对信号进行编码,为此,我们选择了最基本,也是最实用的编码——2进制编码。

首先,模拟信号通过滤波器,过滤掉高频信号,得到我们需要的信号。

然后经过采样和保持电路采集模拟信号当中某一段时间的信号值,这一段时间一方面决定了采样频率的大小,另外一方面也是后面的电路结构所消耗掉的总的时间。

这段时间内得到的采样值传输到比较器当中,比较器的另外一个输入信号由数模转换器和寄存器共同作用来给出。

比如我们这次的电源电压是2V,比较器的输入电压范围是0~2V,因此采样与保持电路的电压输入范围也是0~2V。

我们的比较精度是10位,也就是比较器要在一个采样周期内进行10次比较。

最开始的时候,寄存器将这10位的2进制数字信号都置0。

然后进行第一位,也就是最高位的比较,这时数模转换器将输入电压范围的中值,也就是1V,传输给比较器的一个输入端口,比较器的另外一个输入端口来自采样与保持电路。

当采样电压高于中值1V时,寄存器的最高位由0变为1,同时逻辑控制单元控制数模转换器的下一个输入到比较器端口的电压为1V到2V的中值处,也就是1.5V,将1.5V传入到比较器的输入端口,和采样信号进行比较,输出第二位的数字信号。

以此类推,可以得到10位的数字信号。

当采样电压低于中值电压1V时,寄存器的最高位仍然为0,同时逻辑控制单元控制数模转换器的下一个输入到比较器端口的电压为0~1V的中值处,也就是0.5V,将0.5V穿入到比较器的输入端口,和采样信号进行比较,输出第二位的数字信号。

以此类推,进行10次这样的比较便可以得到10位编译模拟信号的数字信号。

ADC架构II:逐次逼近型ADC

MT-021 指南

ADC架构II:逐次逼近型ADC

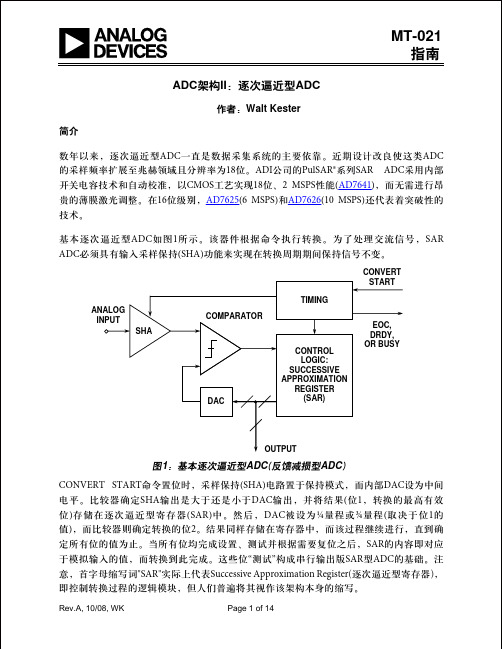

作者:Walt Kester 简介 数年以来,逐次逼近型ADC一直是数据采集系统的主要依靠。近期设计改良使这类ADC 的采样频率扩展至兆赫领域且分辨率为18位。ADI公司的PulSAR®系列SAR ADC采用内部 开关电容技术和自动校准,以CMOS工艺实现18位、2 MSPS性能(AD7641),而无需进行昂 贵的薄膜激光调整。在16位级别,AD7625(6 MSPS)和AD7626(10 MSPS)还代表着突破性的 技术。 基本逐次逼近型 ADC如图 1所示。该器件根据命令执行转换。为了处理交流信号, SAR ADC必须具有输入采样保持(SHA)功能来实现在转换周期期间保持信号不变。

Pቤተ መጻሕፍቲ ባይዱge 4 of 14

MT-021

TEST IS X ≥ 32 ?

X

ASSUME X = 45

YES

RETAIN 32

1

IS X ≥ (32 +16) ?

NO

REJECT 16

0

IS X ≥ (32 +8) ? IS X ≥ (32 +8 + 4) ? IS X ≥ (32 +8 + 4 + 2) ? IS X ≥ (32 +8 + 4 + 2 + 1) ? TOTALS: X = 32 + 8 + 4 + 1 = 4510 =

Page 5 of 14

MT-021

1947年,贝尔电话实验室的Goodall在某篇论文中描述了实施逐次逼近型ADC的更好方法 (参考文献3)。此ADC具有5位分辨率并以8 kSPS的速率对声音通道进行采样。首先对语音 信号进行采样,并将对应电压存储在电容上。然后,将其与大小等于满量程电压一半的基 准电压进行比较。如果大于基准电压,则MSB登记为"1",并从存储电容减去大小等于½量 程的电荷量。如果电容上的电压小于½量程,那么不会移除任何电荷,并且位登记为"0"。 MSB判断完成之后,针对第二位继续该循环,不过此时基准电压为¼量程。该过程持续到 所有位判断完成为止。这种电荷再分配概念类似于现代开关电容DAC。 Schelleng和Goodall设计的ADC均采用二进制加权基准电压加减过程来执行SAR算法。虽然 存在DAC功能,但并未使用传统的二进制加权DAC来执行。1953年,H. R. Kaiser et. al.(参 考文献4)和B. D. Smith(参考文献5)设计的ADC采用真正的二进制加权DAC来产生输入信号 的模拟逼近,这与现代SAR ADC相似。Smith还指出,通过使用非均匀加权DAC可以实现 非线性ADC传递函数。这项技术构成了早期PCM系统中所用压缩扩展语音频带编解码器 的基础。(请参见“教程MT-018:有意为之的非线性DAC”。)在这项非线性ADC技术面世之 前,采用的是线性ADC,并使用二极管/电阻网络来执行压缩和扩展功能,而二极管/电阻 网络必须单独进行校准且必须保持在恒温条件下,以免出现漂移误差(参考文献6)。 当然,在讨论ADC历史时,如果没有提到EPSCO公司(现在为Analogic, Incorporated)Bernard M. Gordon做出的划时代工作,那么肯定就不完整。Gordon在1955年的专利申请(参考文献 7)中描述了一种全真空管11位、50 kSPS逐次逼近型ADC,这代表着完整转换器的首款商用 产品(见图5)。DATRAC采用19" × 26" × 15"外壳设计,功耗为数百瓦,当时售价约为 $8000.00。 在稍后一项专利中(参考文献 8), Gordon详细描述了执行逐次逼近型算法所需的逻辑模 块。稍后在上世纪70年代中,National Semiconductor和Advanced Micro Devices实施了SAR 逻辑功能——备受欢迎的2502/2503/2504系列IC逻辑芯片。在上世纪70和80年代,这些芯 片几乎成为所有模块式和混合型逐次逼近型ADC必不可少的构建模块。

逐次逼近式AD与双积分AD

1.设D4 1, D 10000 则U f 10 (1 0 0 0

2.设D3 1, D 01000

3.设D2 1, D 01100

4.设D1 1, D 01110

1 2 1 4 1 8 1 1 0 ) 5V 4.7V 16 32

同理,当假设已确定最高位 《计算机控制系统》 第二章 过程通道

沈阳工程学院动力系 崔长春

Dn-1=1时:

③确定次高位 Ⅰ)设定SAR中的次高位为“1”, 其余位为“0”,即D=110…0, 送往D/A转换成电压UF;

则 U F U REF (1 1 1 1 1 3 1 2 0 3 0 n ) U REF 2 2 2 2 4 找出了第二个中间值

则D1 1

1 1 则Vf 10 ( 0 0) 7.5V Vi 则D2 0 2.设D2 1, D 1100 2 4 1 1 3.设D3 1, D 1010 则Vf 10 ( 0 0) 6.25V Vi 则D3 0 2 8

4.设D4 1, D 1001 则Vf 10 ( 1 0 0 1 ) 5.625V Vi

2 16

则D 4 1

∴D=1001,这里误差为0.375v

《计算机控制系统》 第二章 过程通道

沈阳工程学院动力系 崔长春

自编2-3:4位逐位逼近式A/D转换器,满量程为10V,

3、电压-频率式A/D

模拟信号→频率F →数字量; 接口电路简单,转换速率较慢,精度较高; 适合远距离的数据传送。

《计算机控制系统》 第二章 过程通道 1、逐位逼近式A/D

逐次逼近式ad转换器工作原理

逐次逼近式ad转换器工作原理

逐次逼近式AD转换器是一种常用的模拟信号数字化方法。

其基本原理是将模拟信号分成若干个量化等级,逐步逼近实际值,最终得到数字信号。

具体来说,AD转换器将待转换的模拟信号与一个内部参考电压进行比较,并将其转换为一个二进制数。

为了提高转换精度,逐次逼近式AD转换器采用了逐步逼近的方法,即首先将待转换的信号与参考电压的一半进行比较,然后根据比较结果确定信号在参考电压的哪一半范围内,再将区间一分为二,重复上述过程,直到达到所需的精度为止。

该方法具有转换速度快、精度高、易于实现等优点,被广泛应用于各种电子设备中。

- 1 -。

逐次逼近型ADC

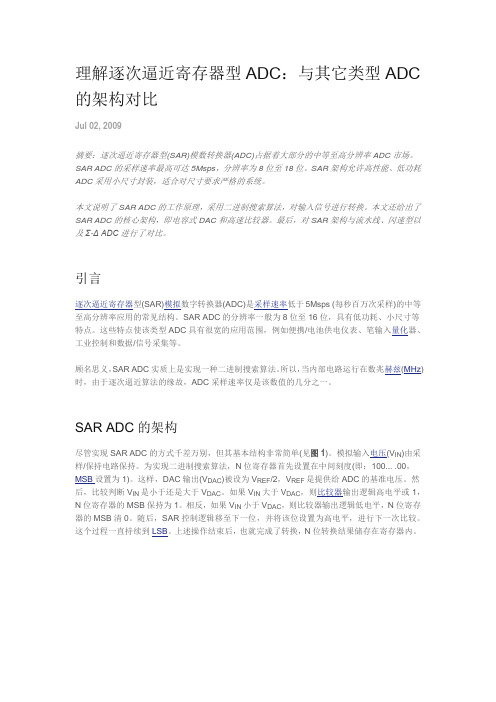

理解逐次逼近寄存器型ADC:与其它类型ADC 的架构对比Jul 02, 2009摘要:逐次逼近寄存器型(SAR)模数转换器(ADC)占据着大部分的中等至高分辨率ADC市场。

SAR ADC的采样速率最高可达5Msps,分辨率为8位至18位。

SAR架构允许高性能、低功耗ADC采用小尺寸封装,适合对尺寸要求严格的系统。

本文说明了SAR ADC的工作原理,采用二进制搜索算法,对输入信号进行转换。

本文还给出了SAR ADC的核心架构,即电容式DAC和高速比较器。

最后,对SAR架构与流水线、闪速型以及Σ-Δ ADC进行了对比。

引言SAR ADC的架构尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(V IN)由采样/保持电路保持。

为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100 (00)MSB设置为1)。

这样,DAC输出(V DAC)被设为V REF/2,V REF是提供给ADC的基准电压。

然后,比较判断V IN是小于还是大于V DAC。

如果V IN大于V DAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。

相反,如果V IN小于V DAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。

随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。

这个过程一直持续到LSB。

上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

图1. 简单的N位SAR ADC架构图2给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。

本例中,第一次比较表明V IN < V DAC。

所以,位3置为0。

然后DAC被置为01002,并执行第二次比较。

由于V IN > V DAC,位2保持为1。

DAC置为01102,执行第三次比较。

根据比较结果,位1置0,DAC又设置为01012,执行最后一次比较。

最后,由于V IN > V DAC,位0确定为1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD转换的基本原理和技术(逐次逼近型)

1、转换方式

直接转换ADC

2.电路结构

逐次逼近ADC包括n位逐次比较型A/D转换器如图1所示。

它由控制逻辑电路、时序产生器、移位寄存器、D/A转换器及电压比较器组成。

图1逐次比较型A/D转换器框图

3、工作原理

逐次逼近转换过程和用天平称物重非常相似。

天平称重物过程是,从最重的砝码开始试放,与被称物体行进比较,若物体重于砝码,则该砝码保留,否则移去。

再加上第二个次重砝码,由物体的重量是否大于砝码的重量决定第二个砝码是留下还是移去。

照此一直加到最小一个砝码为止。

将所有留下的砝码重量相加,就得此物体的重量。

仿照这一思路,逐次比较型

A/D转换器,就是将输入模拟信号与不同的参考电压作多次比较,使转换所得的数字量在数值上逐次逼近输入模拟量对应值。

对11.10.1的电路,它由启动脉冲启动后,在第一个时钟脉冲作用下,控制电路使时序产生器的最高位置1,其他位置0,其输出经数据寄存器将1000……0,送入D/A转换器。

输入电压首先与D/A器输出电压(VREF/2)相比较,如v1≥VREF/2,比较器输出为1,若vI<VREF/2,则为0。

比较结果存于数据寄存器的Dn-1位。

然后在第二个CP作用下,移位寄存器的次高位置1,其他低位置0。

如最高位已存1,则此时vO=(3/4)VREF。

于是v1再与(3/4)VREF相比较,如v1≥(3/4)VREF,则次高位Dn-2存1,否则Dn-2=0;如最高位为0,则vO=VREF/4,与vO比较,如v1≥VREF/4,则Dn-2位存1,否则存0……。

以此类推,逐次比较得到输出数字量。

为了进一步理解逐次比较A/D转换器的工作原理及转换过程。

下面用实例加以说明。

设图11.10.1电路为8位A/D转换器,输入模拟量vA=6.84V,D/A转换器基准电压VREF=10V。

根据逐次比较D/A转换器的工作原理,可画出在转换过程中CP、启动脉冲、D7~D0及D/A转换器输出电压vO的波形,如图11.10.2所示。

由图11.10.2可见,当启动脉冲低电平到来后转换开始,在第一个CP作用下,数据寄存器将D7~D0=10000000送入D/A转换器,其输出电压v0=5V,vA与v0比较,vA>v0存1;第二个CP到来时,寄存器输出D7~D0=11000000,v0为7.5V,vA再与7.5V比较,因vA<7.5V,所以D6存0;输入第三个CP时,D7~D0=10100000,v0=6.25V;vA再与v0比较,……如此重复比较下去,经8个时钟周期,转换结束。

由图中v0的波形可见,在逐次比较过程中,与输出数字量对应的模拟电压v0逐渐逼近vA值,最后得到A/D转换器转换结果D7~D0为10101111。

该数字量所对应的模拟电压为 6.8359375V,与实际输入的模拟电压 6.84V的相对误差仅为0.06%。

图11.10.28位逐次比较型A/D转换器波形图

4、特点

(1)转换速度:(n+1)Tcp.速度快。

(2)调整VREF,可改变其动态范围。

5、转换器电路举例

常用的集成逐次比较型A/D转换器有ADC0808/0809系列(8位)、AD575(10位)、AD574A(12位)等。

例11.10.14位逐次比较型A/D转换器的逻辑电路如图11.10.3所示。

图中5移位寄存器可进行并入/并出或串入/串出操作,其F为并行置数端,高电平有效,S为高位串行输入。

数寄存器由D边沿触发器组成,数字量从Q4~Q1输出,试分析电路的工作原理。

图11.10.34位逐次比较型A/D转换器的逻辑电路解:电路工作过程如下:

当启动脉冲上升沿到来后,FF0~FF4被清零,Q5置1,Q5的高电平开启G2门,时钟CP 脉冲进入移位寄存器。

在第一个CP脉冲作用下,由于移位寄存器的置数使能端F已有0变为1,并行输入数据ABCDE置入,QAQBQCQDQE=01111。

QA的低电平是数据寄存器的最高位置1,即Q4Q3Q2Q1=1000。

D/A转换将数字量1000转换为模拟电压vO,送入比较器C与输入模拟电压

v1比较,若输入电压vI>vO,则比较器C输出vC为1,否则为0。

比较结果送D4~D1。

第二个CP脉冲到来后,移位寄存器的串行输入端S为高电平,QA由0变1,同是最高位QA的0移至次高位QB。

于是数据寄存器的Q3由0变1,这个正跳变作为有效触发信号加到FF4的CP端使vC的电平得以在Q4保存下来。

此时,由于其他触发器无正跳变脉冲,vC的信号对它们不起作用。

Q3变为1后建立了新的D/A转换器的数据,输入电压在与其输出电压vO相比较,比较结果在第三个时钟脉冲作用下存于Q3……。

如此进行,直到QE由1变0,使Q5由1变0后将G2封锁,转换完毕。

于是电路的输出端D3D2D1D0得到与输入电压v1成正比的数字量。

由以上分析可见,逐次比较型A/D转换器完成一次转换所需的时间与其位数和时钟脉冲频率有关,位数愈少,时钟频率愈高,转换所需时间越短。

这种A/D转换器具有转换速度较快,精度高的特点。