(内存基本知识)DRAM工作原理

DRAM基本结构与原理(一)

DRAM基本结构与原理(⼀)DRAM基本结构与原理(⼀)东南⼤学ASIC⼯程中⼼ matlinsas@DRAM(Dynamic Random Access Memory),即动态随机存储器,也就是我们常说的计算机内存,在现代计算机系统和SOC系统中有很重要的作⽤。

本⽂主要对DRAM中的⼀些基本原理进⾏总结,⽬的是为了更好理解DDRC(Double Data Rata DRAM controller)中的时序关系与时序参数。

⼀.DRAM基本电路结构2.1基本存储单元cell2.1.1 3T1C与1T1CDRAM基本电路结构如图所⽰:图中的基本结构单元是1T1C(1 Transistor -1 Capacitor)。

其⼯作的⼤致原理是:当Word Line选通时,晶体管导通,从⽽可以从Bit Line上读取存储在电容器上的位信息。

⽽在早期的DRAM中的基本结构却不是这样的,⽽是3T1C(3 Transistor -1 Capacitor)如下图所⽰:使⽤三个晶体管作为开关,这样设计的优点是:当读取存储在电容上的位信息时,不会影响电容上的电荷,从⽽读后不需要对单元进⾏precharge。

关于precharge的原理在下⽂会有详细介绍,这⾥我们只要了解3T1C的结构读存储器不会破坏其存储在DRAM中的信息。

但是由于1T1C的结构⽐3T1C的结构⾯积节省很多,因此现代DRAM中常⽤的还是1T1C结构。

此外由DRAM基本电路结构图,我们可以知道DRAM的信息是存储在在电容当中,⽽电容中的电荷会因为漏电流存在原因⽽逐渐漏掉,因此需要不断refresh(刷新),这也是DRAM称为动态的原因。

例如,90nm⼯艺下,DRAM的cell单元的电容量是30pf,它的漏电流是1fA,漏光的时间是随着温度的变化⽽变化的。

现在的DRAM的刷新时间⼀般是32ms或者64ms。

2.1.2 堆电容(Stacked Capacitor)与沟电容(Trench Capacitor)下⾯我们从更底层来了解DRAM存储电容,关于存储电容在现代业界也没有统⼀,仍然存在两⼤阵营,分别是堆电容(Stacked Capacitor)与沟电容(Trench Capacitor),像三星这样的⼤公司使⽤是前者。

DRAM基本工作原理

DRAM基本工作原理

DRAM(Dynamic Random Access Memory)是一种动态随机存取存储器,也是最常见的存储器类型。

它主要用于计算机的主存储器,是主存储器最

重要的部分。

这种存储器把数据储存在带有金属覆盖物的静电存储元件中,这些存储元件可以通过电信号来获取、存储和更新数据。

DRAM的原理是由一系列晶体管、电容器和其他电路元件组成的电路

组成的,这种电路可以存储一个单独的位。

当电路收到一个表示电位的输

入时,它向电容器中输入电荷,然后电荷被电容器储存起来,并在栅极电

位上产生一个表示电位的信号。

用来交换数据的线路不是直接连接到存储

单元上,而是收发器或控制器控制的,使数据交换更加有效,以满足不断

变化的条件。

DRAM存储器利用内在的晶体管组件,由功率支持能转换电荷,它们

可以改变字节的位值,将数据保存在字节中并保存在晶体管组件中。

DRAM

存储器具有快速读取和写入速度,以及可容纳大量的数据。

DRAM存储器主要利用一个由晶体管和电容器组成的小元件,它称为

一个存储单元,来将数据进行处理。

在一个存储单元中,晶体管由一个门,一个源极和一个漏极组成。

它们之间的连接有收发器和控制器。

当一个电

信号传递给这个存储单元的时候,数据就会被处理。

DRAM内存原理.

DRAM内存原理1. 内存基础不管你信不信,RDRAM (Rambus、DDR SDRAM甚至是EDO RAM它们在本质上讲是一样的。

RDRAM、DDR RAM、SDRAM、EDO RAM都属于DRAM(Dynamic RAM,即动态内存。

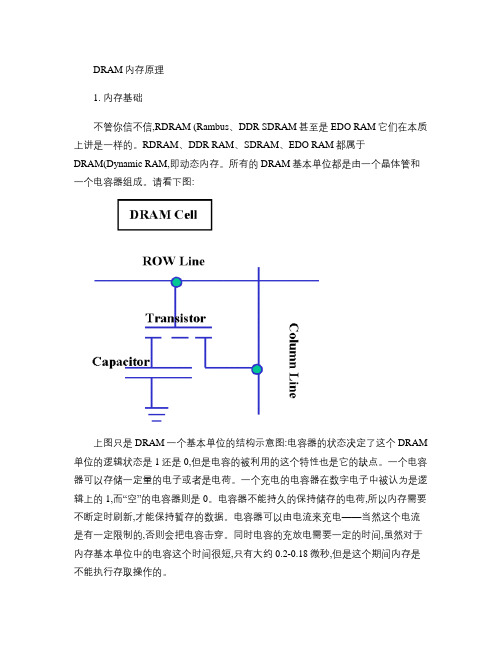

所有的DRAM基本单位都是由一个晶体管和一个电容器组成。

请看下图:上图只是DRAM一个基本单位的结构示意图:电容器的状态决定了这个DRAM 单位的逻辑状态是1还是0,但是电容的被利用的这个特性也是它的缺点。

一个电容器可以存储一定量的电子或者是电荷。

一个充电的电容器在数字电子中被认为是逻辑上的1,而“空”的电容器则是0。

电容器不能持久的保持储存的电荷,所以内存需要不断定时刷新,才能保持暂存的数据。

电容器可以由电流来充电——当然这个电流是有一定限制的,否则会把电容击穿。

同时电容的充放电需要一定的时间,虽然对于内存基本单位中的电容这个时间很短,只有大约0.2-0.18微秒,但是这个期间内存是不能执行存取操作的。

DRAM制造商的一些资料中显示,内存至少要每64ms刷新一次,这也就意味着内存有1%的时间要用来刷新。

内存的自动刷新对于内存厂商来说不是一个难题,而关键在于当对内存单元进行读取操作时保持内存的内容不变——所以DRAM单元每次读取操作之后都要进行刷新:执行一次回写操作,因为读取操作也会破坏内存中的电荷,也就是说对于内存中存储的数据是具有破坏性的。

所以内存不但要每64ms 刷新一次,每次读操作之后也要刷新一次。

这样就增加了存取操作的周期,当然潜伏期也就越长。

SRAM,静态(StaticRAM不存在刷新的问题,一个SRAM基本单元包括4个晶体管和2个电阻。

它不是通过利用电容充放电的特性来存储数据,而是利用设置晶体管的状态来决定逻辑状态——同CPU中的逻辑状态一样。

读取操作对于SRAM不是破坏性的,所以SRAM不存在刷新的问题。

SRAM不但可以运行在比DRAM高的时钟频率上,而且潜伏期比DRAM短的多。

计算机内存条 工作原理

计算机内存条工作原理计算机内存条工作原理计算机内存条是计算机中重要的硬件组件之一,用于存储和访问计算机程序和数据。

它是计算机的临时存储器,能够在计算机运行时快速读取和写入数据。

本文将详细介绍计算机内存条的工作原理。

一、内存条的基本结构计算机内存条通常由一组动态随机存取存储器(DRAM)芯片组成,这些芯片被安装在一个电路板上。

每个DRAM芯片由许多存储单元组成,每个存储单元可以存储一个位(0或1)。

这些存储单元按矩阵形式排列,每个单元通过一个地址进行访问。

二、内存条的工作原理1. 读取数据当计算机需要读取内存中的数据时,首先会将数据的地址发送到内存控制器。

内存控制器会解码地址,并将其发送到相应的DRAM芯片。

DRAM芯片根据地址找到对应的存储单元,并将存储单元中的数据读取出来。

读取的数据通过数据总线传输到内存控制器,然后再传输到计算机的处理器或其他设备。

2. 写入数据当计算机需要将数据写入内存时,首先会将数据和地址发送到内存控制器。

内存控制器将地址发送到相应的DRAM芯片,并将数据写入到对应的存储单元中。

写入的数据通过数据总线传输到内存控制器,然后再传输到DRAM芯片。

3. 刷新操作DRAM芯片中的存储单元是有限的,数据需要定期刷新以保持其有效性。

在DRAM芯片中,每个存储单元都有一个电容器来存储数据,电容器会逐渐丧失电荷,导致数据丢失。

为了防止数据丢失,DRAM芯片需要定期刷新电容器中的电荷。

内存控制器会发送刷新命令给DRAM芯片,使其刷新存储单元中的数据。

4. 内存条的速度和容量内存条的速度通常以时钟速度来表示,例如DDR4-3200。

时钟速度越高,内存条的读写速度越快。

内存条的容量通常以GB(千兆字节)为单位,例如8GB、16GB等。

内存条的容量决定了计算机可以同时存储和处理的数据量。

5. 内存条的类型目前常见的内存条类型有DDR3、DDR4等。

不同类型的内存条在工作电压、传输速度和时序等方面有所不同。

计算机内存条 工作原理

计算机内存条工作原理计算机内存条工作原理计算机内存条是计算机中重要的硬件组件之一,用于存储和访问计算机的数据和指令。

它是计算机的临时存储设备,可以快速读取和写入数据,为计算机的正常运行提供必要的支持。

本文将详细介绍计算机内存条的工作原理。

一、内存条的基本结构计算机内存条通常由多个内存芯片组成,每个芯片都包含许多存储单元,每个存储单元可以存储一个二进制位(0或1)。

内存芯片通过电路连接到计算机的总线系统,可以与其他硬件组件进行数据交换。

二、内存条的存储方式内存条存储数据的方式可以分为两种:随机存取存储器(RAM)和只读存储器(ROM)。

1. 随机存取存储器(RAM)RAM是内存条的主要存储方式,它可以读取和写入数据。

RAM分为静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)两种。

- 静态随机存取存储器(SRAM):SRAM使用触发器作为存储单元,每个存储单元由6个晶体管组成,可以存储一个二进制位。

SRAM的读取速度快,但占用空间大,成本较高,一般用于高速缓存等需要快速访问的场景。

- 动态随机存取存储器(DRAM):DRAM使用电容作为存储单元,每个存储单元由一个电容和一个晶体管组成,可以存储一个二进制位。

DRAM的读取速度较慢,但占用空间小,成本较低,一般用于主存等大容量存储的场景。

2. 只读存储器(ROM)ROM是一种只能读取数据而不能写入数据的存储方式。

ROM的数据是在制造过程中被固化的,无法修改。

计算机启动时,BIOS(基本输入输出系统)中的固化程序就存储在ROM中。

ROM的优点是数据的持久性和稳定性,但缺点是无法进行数据的修改。

三、内存条的读写操作内存条的读写操作是计算机进行数据交换的基础。

计算机通过总线系统与内存条进行通信,实现数据的读取和写入。

1. 读取操作计算机向内存条发送读取指令后,内存条根据指令从存储单元中读取数据,并将数据通过总线传输给计算机的其他硬件组件。

读取操作的速度取决于内存条的读取速度和总线的传输速度。

DRAM的基本工作原理

DRAM的基本工作原理DRAM(动态随机存取存储器)是一种常用的半导体存储器,它的基本工作原理是利用电容器来存储和读取数据。

DRAM被广泛应用于计算机、智能手机和其他电子设备中。

DRAM由许多存储单元组成,每个存储单元通常由一个电容器和一个传输门(access transistor)组成。

电容器存储比特信息,传输门用于读取和写入数据。

选择阶段:首先,内存控制器根据需要确定要访问的存储单元的地址。

然后,通过行地址(Row Address)信号激活一个特定的行,使得行内的所有存储单元电容器的电荷分布重构。

读取阶段:读取数据时,将目标行的列地址(Column Address)信号打开,将内存中存储单元的电荷通过传输门放大并传递到读取电路。

读取电路将电流转换为数字信号,并传送给CPU或其他电路。

写入阶段:写入数据时,列地址信号被打开,通过传输门将输入的数据传输到指定的电容器中。

此后,行地址信号被关闭,使得其他存储单元不受干扰。

刷新阶段:DRAM中的电容器会逐渐失去电荷,如果不进行刷新,则会导致数据的丢失。

因此,DRAM需要周期性地进行刷新操作来更新存储单元中的数据。

刷新操作通过激活每个存储单元的行,然后立即关闭来实现。

这个过程通常由内存控制器自动完成。

然而,DRAM也存在一些问题。

首先,由于电容器的性质,DRAM存储电荷容易泄漏,需要定期刷新来保持数据的稳定性。

其次,DRAM的访问速度较慢,因为读取和写入数据需要时间来充电和放电电容器。

此外,DRAM的密集集成度和存储容量相对较低。

为了解决这些问题,人们还开发了其他类型的存储器,例如静态随机存取存储器(SRAM)和闪存存储器。

SRAM由触发器组成,不需要定期刷新,但成本更高,存储密度较低。

闪存存储器比DRAM的密度更高,用于存储非易失性数据,但访问速度相对较慢。

总之,DRAM的基本工作原理是利用电容器存储和读取数据。

通过选择、读取、写入和刷新等阶段,DRAM能够实现数据的存储和访问。

DRAM的发展

DRAM的发展概述:动态随机存取存储器(DRAM)是一种常用的计算机内存技术,它在计算机系统中起着至关重要的作用。

本文将详细介绍DRAM的发展历程,包括其原理、发展阶段和未来趋势。

一、DRAM的原理DRAM是一种基于电容的存储器技术,它通过电容的充放电来存储和读取数据。

每一个DRAM存储单元由一个电容和一个开关构成。

当电容被充电时,表示存储的是1;当电容被放电时,表示存储的是0。

为了保持数据的稳定性,DRAM需要定期进行刷新操作。

二、DRAM的发展阶段1. 早期DRAM早期的DRAM采用的是单个晶体管和电容的结构,存储密度较低,容量有限。

这种DRAM在20世纪60年代末至70年代初得到了广泛应用,但由于创造工艺的限制,无法进一步提高存储密度。

2. 高密度DRAM随着创造工艺的进步,高密度DRAM应运而生。

这种DRAM采用了多层结构,通过堆叠多个存储层来提高存储密度。

高密度DRAM在80年代初得到了商业化推广,并逐渐取代了早期的DRAM。

3. SDRAM同步动态随机存取存储器(SDRAM)是DRAM的一种改进型。

它在存储和读取数据时采用了同步时钟信号,提高了数据传输速度和带宽。

SDRAM在90年代初得到了广泛应用,成为主流的计算机内存技术。

4. DDR SDRAM双倍数据率同步动态随机存取存储器(DDR SDRAM)是SDRAM的进一步改进。

它在每一个时钟周期内能够传输两次数据,提高了数据传输速度和性能。

DDR SDRAM在2000年代初得到了广泛应用,成为主流的计算机内存技术。

5. DDR2、DDR3和DDR4随着技术的进步,DDR2、DDR3和DDR4相继问世。

这些新一代的DDR SDRAM在数据传输速度、能耗和稳定性方面都有所提升。

DDR4是目前最新的DDR SDRAM标准,已经广泛应用于高性能计算机和服务器领域。

三、DRAM的未来趋势1. 高带宽存储器随着数据中心、人工智能和大数据应用的快速发展,对存储器的带宽需求越来越高。

DDR基本原理范文

DDR基本原理范文DDR全称为Double Data Rate,即双倍数据率。

它是一种采用双边沿触发技术的动态随机存取存储器(DRAM)。

DDR在运行时,能够在每个时钟周期中发送两次数据,这样就使得数据传输速度提高了一倍。

下面将通过详细地介绍DDR的基本原理。

首先,我们需要了解基本的DRAM原理。

DRAM是一种动态存储器,它的存储单元是由一个电容器和一个访问晶体管组成的。

每个存储单元被构成为一个矩阵,其中每个行和每个列都有一个独立的字线和位线。

通过对字线和位线进行相应的操作,可以实现对存储单元的读取和写入操作。

然而,DRAM的传输速度有限,原因之一是数据在字线和位线上的传输速度较慢。

DDR通过使用双边沿触发技术,将字线和位线上的数据传输速度提高一倍,从而提高了整体的传输速度。

具体来说,DDR采用了两个时钟信号:一个是基本时钟信号(CK),另一个是数据有效信号(DQS)。

DDR的数据传输过程可以分为四个阶段:预充电(Precharge)、读取(Read)、写入(Write)和关闭(Close)。

在预充电阶段,DRAM的字线和位线都被阻断,电容器中的电荷被放电。

在这个阶段,DRAM准备接收下一个操作的指令。

在读取和写入阶段,数据通过字线传入DRAM内存,并被存储到相应的存储单元中。

在读取过程中,DRAM将字线上的数据通过位线传送给外部设备。

在写入过程中,DRAM将外部设备提供的数据通过位线传输给字线,从而存储到相应的存储单元中。

在关闭阶段,DRAM断开字线和位线之间的连接,将存储单元内的数据保持在电容器中。

DDR的双边沿触发技术是如何实现的呢?在DDR中,时钟信号CK和数据有效信号DQS是不同步的。

在数据的上升沿和下降沿处,数据有效信号DQS都会进行翻转,这样就实现了在一个时钟周期内的两次数据传输。

具体的传输过程如下:1.预充电阶段:CK为低电平,DQS保持不变。

2.第一次传输阶段:CK上升沿,DQS发生变化,传输数据的上升沿部分。

DDR的基本原理与工作过程

DDR的基本原理与工作过程DDR(Double Data Rate)是一种计算机内存标准,它采用了特定的电路设计和信号传输方式来提高内存访问速度。

DDR内存是目前应用最广泛的内存类型之一,其基本原理和工作过程如下:1. 内存结构和组织:DDR内存由多个DRAM芯片组成,每个芯片通常有多个内部存储集合体,称为bank。

每个bank由多个行(row)和列(column)组成,行和列的交叉点称为存储单元,用于存储数据。

2.时钟和数据总线:DDR内存的工作依赖于一个时钟信号和一组数据总线。

时钟信号提供了内存访问和数据传输的时序,数据总线用于读写操作。

3.数据传输方式:DDR内存采用并行传输方式,即每个时钟周期传输多个数据。

DDR内存通过在上升边和下降边两种时钟信号下传输数据,使数据传输速度翻倍,即提供了“双倍数据率”的特性。

4.写入过程:当处理器需要将数据写入DDR内存时,首先要发送写入命令给内存控制器。

然后,内存控制器将数据分割成多个数据块,并通过数据总线逐个传输给内存。

在传输过程中,内存控制器使用一个写入时序来控制数据的传输。

5.读取过程:当处理器需要从DDR内存中读取数据时,首先要发送读取命令给内存控制器,指定要读取的数据地址。

然后,内存控制器根据命令和地址信息,按照读取时序从内存中读取数据,并通过数据总线传输给处理器。

6.预取和刷新:DDR内存支持预取功能,即在读取数据时,内存控制器不仅读取所需的数据,还会自动预先读取一定数量的相邻数据,以提高内存访问效率。

此外,DDR内存还需要定期刷新操作,以保持存储的数据不丢失。

7.控制信号和时序:DDR内存的工作还涉及一组控制信号和时序,通过它们来控制内存的读写操作。

这些信号和时序包括命令信号(如写入命令、读取命令等)、地址信号(指定要读写的数据地址)、数据信号(传输数据的总线)、时钟信号(提供时序信息)、写入时序和读取时序等。

总结起来,DDR内存的工作过程包括内存结构和组织、时钟和数据总线、数据传输方式、写入过程、读取过程、预取和刷新、控制信号和时序等。

内存基本知识4DRAM工作原理

in main

Why DRAM for Main Memory ?? ������ Cost effective (small chip area than SRAM) ������ High Speed(than HDD, flash) ������ High Density(~Gbyte) ������ Mass Production ……

•������ DRAM stands for Dynamic Random Access Memory. •������ Random access refers to the ability to access any of

the information within the DRAM in random order. •������ Dynamic refers to temporary or transient data storage.

Confidential

Memory: DRAM position ������ Semiconductor memory device ������ ROM: Non volatile ������ Mask ROM ������ EPROM ������ EEPROM ������ Flash ������ NAND: low speed, high density ������ NOR: high speed, low density ������ RAM: Volatile ������ DRAM: Dynamic Random Access Memory ������ SRAM: Static Random Access Memory ������ Pseudo SRAM

DRAM工作原理

RRaammaxaexl TeelchTnoelocghy nLiomlitoedgy Limited

DRAM的基本工作原理

DRAM的基本工作原理动态随机存取存储器(Dynamic Random Access Memory,DRAM)是计算机中常见的一种内存类型。

它是一种存储数字信息的半导体器件,其基本工作原理是将电荷储存在电容中,通过检测电容电压的变化来读取和写入数据。

DRAM的基本构成单位是存储单元,每个存储单元由一个电容和一个访问晶体管组成。

电容作为储存电荷的容器,可以在两个电压级别之间切换,代表二进制的0和1;而访问晶体管用于控制电荷在电容和位线之间的流动,实现对存储单元的读取和写入操作。

首先,当需要向DRAM中写入数据时,数据输入线会向所需写入的存储单元的位线引入电荷。

由于电容的特性,电荷会在电容板上积累起来,从而改变电压级别。

写入过程通过控制访问晶体管的开关来实现。

接下来,当需要从DRAM中读取数据时,读取时序信号会通过位线驱动存储单元。

由于电容会保持电荷状态,根据所需读取的存储单元是否带电,会改变位线电压。

这些电压变化被放大,然后通过读取电路解码,最终得到所需的数据。

需要注意的是,DRAM在读取数据之前,需要刷新操作来保持存储单元中的电荷,因为电容会随时间流逝而逐渐泄漏。

刷新操作通过逐行或逐列地访问所有存储单元来刷新电容中的电荷水平。

这种刷新操作需要花费一定的时间,会影响DRAM的响应速度。

除了基本的读写操作,DRAM还具有许多其他的特性和技术,以提高性能和可靠性。

例如,多通道DRAM(Multi-channel DRAM,MCDRAM)可以通过并行访问多个通道来提高数据传输速度;错位控制线(Bit LineSwapping)技术可以减少访问过程中的干扰,提高存储单元之间的隔离效果;自动预充电技术(Auto Precharge)可以在读取或写入操作之后自动将位线电压恢复到初始状态,以准备下一次操作。

综上所述,DRAM的基本工作原理是通过在电容中存储电荷来存储数据,并通过控制电荷的流动来实现读写操作。

DRAM作为一种较廉价和高性能的内存类型,在计算机中广泛应用,并在不断发展中不断提高存储密度和速度。

单管dram工作原理

DRAM(Dynamic Random Access Memory)是一种常见的半导体存储器,广泛应用于计算机系统中。

它具有高速读写性能、较低的功耗和相对较低的成本,因此在现代计算机中被广泛使用。

本文将详细介绍DRAM的工作原理。

1. 引言DRAM是一种易失性存储器,用于存储电荷的状态。

与静态RAM(SRAM)相比,DRAM的存储密度更高,但也更加复杂。

DRAM的工作原理基于电荷的积累和释放。

2. 存储单元DRAM的最小存储单元是一个电容器和一个访问晶体管组成的存储单元。

电容器由两个电极隔着一个薄的氧化层构成。

电容器的一个电极连接到供电电源,而另一个电极连接到晶体管。

晶体管控制对电容器的访问,允许读取和写入操作。

3. 电荷的积累和释放当DRAM被写入时,晶体管被打开,将电荷存储在电容器中。

电荷的大小表示存储的数据值,可以是0或1。

为了保持电荷的稳定,DRAM需要经常刷新。

在刷新过程中,电荷被重新写入电容器以防止电荷的逸失。

4. 读取操作当需要读取存储在DRAM中的数据时,首先要选择所需的行和列。

选择行后,晶体管被打开,允许电荷流动。

电荷从电容器流到一个放大器电路,然后转换为电压信号。

电压信号经过放大和解码后,被传输到计算机系统的其他部分。

5. 写入操作写入数据到DRAM的过程与读取操作类似。

首先选择要写入的行和列,然后将数据转换为电荷。

通过打开晶体管,将电荷存储在电容器中。

写入操作不会影响其他存储单元的数据。

6. 刷新操作刷新是DRAM的一个重要过程。

由于电容器逐渐失去电荷,刷新操作用于定期重新写入电容器中的电荷,以保持数据的稳定性。

刷新操作会暂停正常的读写操作,因此需要在设计系统时考虑刷新时间。

7. DRAM的性能特点DRAM具有较低的访问延迟和较高的带宽,这使其成为计算机系统中重要的存储器之一。

然而,DRAM也存在一些缺点,如电荷逸失和刷新操作的开销。

此外,DRAM的存储单元需要经常刷新,这会引入一定的复杂性。

动态ram的工作原理

动态ram的工作原理动态RAM(DRAM)是一种常见的计算机内存类型,它在电子设备中起着重要的作用。

那么,动态RAM的工作原理是什么呢?本文将以简单明了的方式解释动态RAM的工作原理,并详细介绍DRAM的构造、读写操作和使用注意事项。

首先,我们来了解动态RAM的构造。

动态RAM由一系列存储单元组成,每个存储单元都包含一个电容和一个开关。

电容负责存储数据,而开关则控制数据的读写。

这些存储单元通常被组织成一个矩阵,每一行被称为一个“字”,每一列被称为一个“位”。

整个存储器由多个字和位组成。

接下来,让我们一起了解动态RAM的工作过程。

当计算机需要读取某个内存单元的数据时,DRAM控制器首先需要将所需的行选中。

为了选中某一行,DRAM控制器会给控制线发送一个特定的信号。

一旦选中了行,存储单元中的电容会被放电,并将其储存的数据转换为电压信号。

这个电压信号经过放大和转换之后会传递给计算机的其他部件进行处理。

当需要写入数据时,DRAM的工作原理类似。

DRAM控制器会选择需要写入的行,并将数据转换为电压信号。

然后,这个电压信号会被传输到存储单元中的电容中进行充电。

充电过程会改变电容中的电压信号,从而实现数据的写入。

尽管动态RAM具有高速读取和写入的优点,但也存在一些需要注意的问题。

首先,因为电容会逐渐丧失电荷,所以DRAM需要定期进行刷新操作,以防止数据丢失。

其次,由于存储单元之间存在互相干扰的问题,所以需要在读写操作之间进行额外的时间间隔,以确保数据的准确性。

最后,由于DRAM的构造复杂并需要许多晶体管来实现,它相对于静态RAM(SRAM)来说更加昂贵。

总结一下,动态RAM是一种常见的计算机内存类型,其工作原理简单明了。

通过选中行和写入/读取数据的方式,DRAM实现了数据的存储和传输。

然而,由于其特殊性,我们需要定期刷新和注意数据的正确性。

了解动态RAM的工作原理有助于我们更好地了解计算机系统中的内存管理,并能够有效地使用和维护内存资源。

(内存基本知识)_4_DRAM工作原理

Ramaxel Technology Limited Ramaxel Technology Limited

Confidential

Static RAM

• SRAM

– Basic storage element is a 4 or 6 transistor circuit which will hold a 1 or 0 as long as the system continues to receive power – No need for a periodic refreshing signal or a clock – Used in system cache – Fastest memory, but expensive

Confidential

DRAM Architecture

Ramaxel Technology Limited Ramaxel Technology Limited

Confidential

Multi Bank Architecture

– SDRAM has the multi bank architecture. – Conventional DRAM was product that have single bank architecture. – The bank is independent active. memory array have independent internal data bus that have same width as external data bus. – Every bank can be activating with interleaving manner. – Another bank can be activated while 1st bank being accessed. (Burst read or write)

内存的工作原理及时序介绍

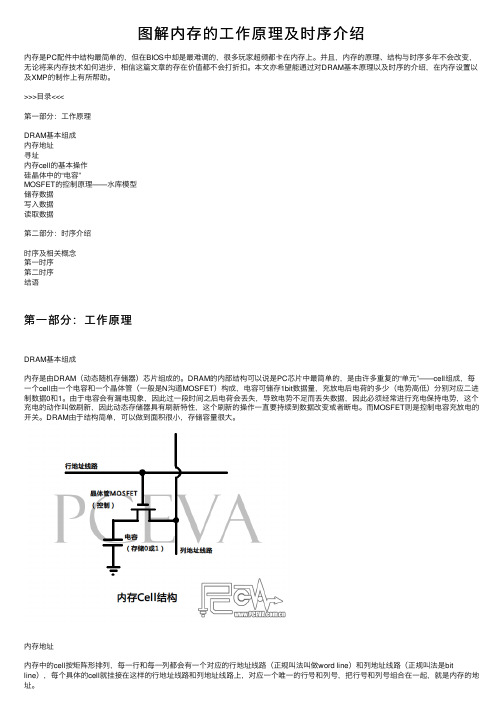

内存的工作原理及时序介绍第一部分:工作原理DRAM基本组成内存是由DRAM(动态随机存储器)芯片组成的。

DRAM的内部结构可以说是PC芯片中最简单的,是由许多重复的“单元”——cell组成,每一个cell由一个电容和一个晶体管(一般是N沟道MOSFET)构成,电容可储存1bit数据量,充放电后电荷的多少(电势高低)分别对应二进制数据0和1。

由于电容会有漏电现象,因此过一段时间之后电荷会丢失,导致电势不足而丢失数据,因此必须经常进行充电保持电势,这个充电的动作叫做刷新,因此动态存储器具有刷新特性,这个刷新的操作一直要持续到数据改变或者断电。

而MOSFET则是控制电容充放电的开关。

DRAM由于结构简单,可以做到面积很小,存储容量很大。

内存地址内存中的cell按矩阵形排列,每一行和每一列都会有一个对应的行地址线路(正规叫法叫做word line)和列地址线路(正规叫法是bit line),每个具体的cell就挂接在这样的行地址线路和列地址线路上,对应一个唯一的行号和列号,把行号和列号组合在一起,就是内存的地址。

上图是Thaiphoon Burner的一个SPD dump,每个地址是一个字节。

不过我们可以把这些数据假设成只有一个bit,当成是一个简单的内存地址表,左边竖着的是行地址,上方横着的是列地址。

例如我们要找第七行、倒数第二列(地址为7E)的数据,它就只有一个对应的值:FD。

当然了,在内存的cell中,它只能是0或者1。

寻址数据要写入内存的一个cell,或者从内存中的一个cell读取数据,首先要完成对这个cell的寻址。

寻址的过程,首先是将需要操作的cell的对应行地址信号和列地址信号输入行/列地址缓冲器,然后先通过行解码器(Row Decoder)选择特定的行地址线路,以激活特定的行地址。

每一条行地址线路会与多条列地址线路和cell相连接,为了侦测列地址线路上微弱的激活信号,还需要一个额外的感应放大器(Sense Amplifier)放大这个信号。

dram 芯片 结构

dram 芯片结构DRAM(Dynamic Random Access Memory)是一种常见的内存芯片,被广泛用于计算机和其他电子设备中。

DRAM的结构与工作原理非常重要,下面将详细介绍。

DRAM的基本结构由一个个存储单元组成,每个存储单元由一个电容器和一个访问晶体管组成。

电容器用于存储数据,在存储数据之前需要通过内部电路对电容器进行充电或放电。

访问晶体管则用于将数据写入或读取出来。

DRAM存储单元之间通过网格连接,形成二维的阵列结构。

该结构被分为若干个行和列,每个行都包含一个或多个存储单元,每个列也包含一个或多个存储单元。

行和列的交叉点称为交叉引线,用于控制对存储单元的访问,读取或写入数据。

在DRAM中,数据的读取和写入是通过访问晶体管来实现的。

访问晶体管可以作为一个开关,用于控制单元之间的数据流动。

当需要读取或写入数据时,所选行的对应访问晶体管会被打开,允许数据的读取或写入。

而其他行的访问晶体管则会被关闭,以防止数据的干扰。

另外,为了确保数据的稳定性,DRAM需要周期性地刷新数据。

刷新是通过将所有存储单元的数据重写来实现的,以避免数据的丢失或破坏。

刷新操作通常由内部计时器触发,并在DRAM芯片上执行。

DRAM的工作原理可以归结为以下几个步骤:1.数据写入:当访问晶体管打开时,数据可以通过行选择引脚和列选择引脚写入到DRAM中。

所选行的存储单元将被充电或放电,以存储新的数据。

2.数据读取:当访问晶体管打开时,所选行的存储单元中的数据可以通过列选择引脚读取出来。

读取的数据将通过输出引脚传递给其他电子设备。

3.数据刷新:定期刷新操作将所有存储单元中的数据重新写入,以保持数据的稳定性。

这个过程通过内部计时器触发,并在整个DRAM 芯片上进行。

DRAM的结构和工作原理使其具有以下优点:1.高容量:DRAM的二维阵列结构使其能够存储大量数据,满足计算机和其他电子设备的内存需求。

2.可扩展性:由于行和列的结构,DRAM可以通过扩展行和列的数量来增加存储容量。

1t1c dram工作原理

1t1c dram工作原理

1T1C DRAM(One Transistor One Capacitor Dynamic Random Access Memory)的工作原理是利用一个晶体管和一个电容器来

存储和读取数据。

在1T1C DRAM中,每个存储单元由一个晶体管和一个电容器组成。

晶体管充当存储单元的开关,可以控制电容器是否允许电荷通过。

电容器用来存储数据,其充电状态表示存储的位值。

工作原理如下:

1. 写入数据:当要写入数据时,晶体管被打开,电容器与电源连接,通过电流流过电容器,使其充电或放电,以表示存储的位值。

充电或放电的时间决定了存储的数据是0还是1。

2. 读取数据:当需要读取数据时,准备读取的存储单元的晶体管被打开,读取电路连接到电容器,通过读取电路可以测量电容器的电压。

根据电容器的充放电状态,读取电路可以确定存储的数据位值。

3. 刷新数据:由于电容器会逐渐失去电荷,所以需要定期刷新数据。

刷新电路会读取和重新写入每个存储单元,以保持数据的正确性。

1T1C DRAM相对于其他DRAM结构的优势在于它只需要一

个晶体管和一个电容器来存储一个位,使得它在密度和成本方面更具优势。

然而,由于电容器的容量相对较小,数据存储会逐渐衰减,所以需要定期刷新数据,增加了功耗和复杂性。

(内存基本知识)_DRAM工作原理

in main

Why DRAM for Main Memory ?? ������ Cost effective (small chip area than SRAM) ������ High Speed(than HDD, flash) ������ High Density(~Gbyte) ������ Mass Production ……

Data stored in dynamic memories naturally decays over time. Therefore, DRAM need periodic refresh operation to prevent data loss.

Memory: DRAM position ������ Semiconductor memory device ������ ROM: Non volatile ������ Mask ROM ������ EPROM ������ EEPROM ������ Flash ������ NAND: low speed, high density ������ NOR: high speed, low density ������ RAM: Volatile ������ DRAM: Dynamic Random Access Memory ������ SRAM: Static Random Access Memory ������ Pseudo SRAM

– Each bank can be independently controlled

Main memory

Main Memory Everything that happens in the computer is resident memory Capacity: around 100 Mbyte to 100 Gbyte Random access Typical access time is 10- 100 nanoseconds

图解内存的工作原理及时序介绍

图解内存的⼯作原理及时序介绍内存是PC配件中结构最简单的,但在BIOS中却是最难调的,很多玩家超频都卡在内存上。

并且,内存的原理、结构与时序多年不会改变,⽆论将来内存技术如何进步,相信这篇⽂章的存在价值都不会打折扣。

本⽂亦希望能通过对DRAM基本原理以及时序的介绍,在内存设置以及XMP的制作上有所帮助。

>>>⽬录<<<第⼀部分:⼯作原理DRAM基本组成内存地址寻址内存cell的基本操作硅晶体中的“电容”MOSFET的控制原理——⽔库模型储存数据写⼊数据读取数据第⼆部分:时序介绍时序及相关概念第⼀时序第⼆时序结语第⼀部分:⼯作原理DRAM基本组成内存是由DRAM(动态随机存储器)芯⽚组成的。

DRAM的内部结构可以说是PC芯⽚中最简单的,是由许多重复的“单元”——cell组成,每⼀个cell由⼀个电容和⼀个晶体管(⼀般是N沟道MOSFET)构成,电容可储存1bit数据量,充放电后电荷的多少(电势⾼低)分别对应⼆进制数据0和1。

由于电容会有漏电现象,因此过⼀段时间之后电荷会丢失,导致电势不⾜⽽丢失数据,因此必须经常进⾏充电保持电势,这个充电的动作叫做刷新,因此动态存储器具有刷新特性,这个刷新的操作⼀直要持续到数据改变或者断电。

⽽MOSFET则是控制电容充放电的开关。

DRAM由于结构简单,可以做到⾯积很⼩,存储容量很⼤。

内存地址内存中的cell按矩阵形排列,每⼀⾏和每⼀列都会有⼀个对应的⾏地址线路(正规叫法叫做word line)和列地址线路(正规叫法是bit line),每个具体的cell就挂接在这样的⾏地址线路和列地址线路上,对应⼀个唯⼀的⾏号和列号,把⾏号和列号组合在⼀起,就是内存的地址。

址。

上图是Thaiphoon Burner的⼀个SPD dump,每个地址是⼀个字节。

不过我们可以把这些数据假设成只有⼀个bit,当成是⼀个简单的内存地址表,左边竖着的是⾏地址,上⽅横着的是列地址。