ISE软件使用说明

ISE开发环境使用指南[FPGA开发教程

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

ISE使用教程(修改稿)

点击project菜单的New Source

设计输入

• 要完成这个计数器模块,可以在ISE自动生成的代 码框架基础上通过自己编写代码完成,也可使用 ISE的语言模板(ISE Language Template)工具 来完成。 • 选择Edit->Language Template或者通过点击工 具栏中最右端的灯泡按钮 来打开语言模板。 在语言模版(Language Template )窗口中,有 很多Xilinx提供的参考代码片断,找到需要的 counter代码片断。

功能仿真

• 首先在 Project Navigator 中创建一个 testbench 波形源 文件该文件将在 HDL Bencher 中进行修改 • 1. 在工程项窗口Project Window的源文件中选中计数器 (counter.vhd) • 2. 选择 Project -> New Source • 3. 在新的对话框中选择新文件类型为 Test Bench Waveform, 键入文件名为counter_tbw • 5. 点击 Next • 6. 点击 Next • 7. 点击 Finish • 此时HDL Bencher 程序自动启动并等候你输入所需的时 序需求

语言模版工具界面截图

设计输入

从 VHDL 综合模板中选择 计数器模板(Counter Template) 并把它拖动或粘 贴到源程序 counter.vhd 的 begin 和 end 之间

粘贴修改后的

Counter.vhd

设计输入

保存counter.vhd即 完成了设计输入

1.将输入好的 VHDL保存

1.选中

2.双击 编写完成后保存

自动布局布线

1.选中

2.双击

ISE使用指导

-3-

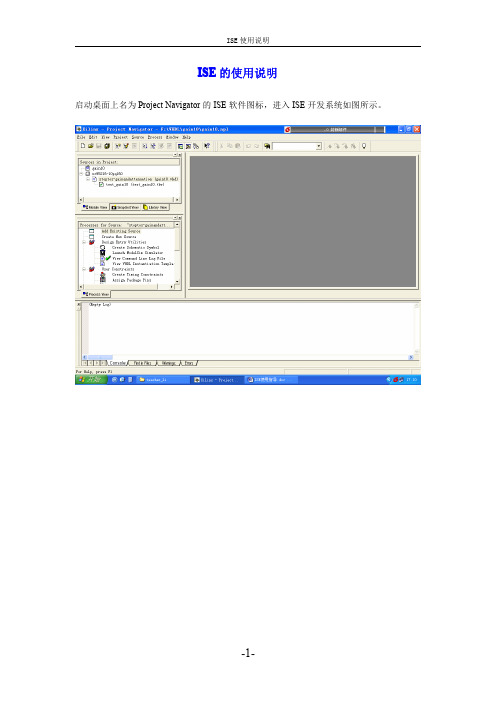

ISE 使用说明

下一步,进行可编程器件型号的选择以及设计流程的设置。在器件型号栏有 Device family , Device (型号) ,封装,speed grade,可以根据实验平台所用的可编程逻辑器件分别设置相 应选项。对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了 New Project Information 的设置。如图所示:

-9-

ISE 使用说明

count<="000000"; end if; elsif flag='1' and flag1='1' then if count<59 then count<=count+1; elsif count>=59 then count<="000000"; end if; end if; end if; end process; end Behavioral; -- flag='1' , 则进行 60 进制计数

然后单击工程 counter 下的子目录 count-Behavioral(count.vhd) , 接着在界面的 Processes for Source 一栏选择 Implement Design,进行布局布线的综合:

-15-

ISE 使用说明

然后工程名 counter 上单击右键,弹出对话框,选择新建 Test Bench Waveform,在 file 命名 为 test_counter。

在界面的 Processes for Source 一栏,是一系列综合工具。 Synthesize XST 工具一般可以分析 代码的语法错误,查看错误报告和 RTL 级的电路设计图。 单击 View Synthesis,出现如图所示对话框:

ISE软件说明

1.安装XILINX的ISE和EDK工具以及最新的Service Pack 安装如下图所示3个必须的工具。

iMPACT最低版本必须如下图所示:ISE最低版本必须如下图所示:XPS最低版本必须如下图所示:2.TS201板中CPLD和FPGA设计的目录结构将CPLD和FPGA设计的整个目录edk_ise_615拷入到微机的D:盘根目录下,使得整个目录结构看上去如下面所描述。

这一点很重要,否者打开工程时可能会出现缺各种文件的情况。

只要严格按本说明去操作,可以避免手工去修改工程的各项配置,可以顺利地熟悉整个T201板上CPLD和FPGA的设计工作。

目录结构和相应的ISE主工程文件:D:\edk_ise_615\cpld\pandr\cpld.iseD:\edk_ise_615\edk81\615htmii_ise\projnav\system.ise 不推荐使用D:\edk_ise_615\edk91\615htmii_ise\projnav\system.iseD:\edk_ise_615\edk91\615htgmii_ise\projnav\system.ise注意目录中还存在下列JTAG烧写文件:D:\edk_ise_615\edk81\615htmii_ise\ipf\prom_htmii.cdf 不推荐使用D:\edk_ise_615\edk81\615htmii_ise\ipf\all_htmii.cdf 不推荐使用D:\edk_ise_615\edk91\615htmii_ise\ipf\prom_htmii.cdfD:\edk_ise_615\edk91\615htmii_ise\ipf\all_htmii.cdfD:\edk_ise_615\edk91\615htgmii_ise\ipf\prom_htgmii.cdfD:\edk_ise_615\edk91\615htgmii_ise\ipf\all_htgmii.cdf说明:cpld目录是给TS201板上的CPLD工程用的;edk81目录代表TS201板上的FPGA工程是用8.1版本的EDK&ISE工具设计的;edk91目录代表TS201板上的FPGA工程是用9.1版本的EDK&ISE工具设计的,推荐使用最新版本的EDK&ISE工具,最好不要使用老版本;htmii表示的是hard temac mii的意思,即V4百兆硬核,该工程FPGA实现的是百兆网;htgmii表示的是hard temac gmii的意思,即V4千兆硬核,该工程FPGA实现的是千兆网;615htmii_ise和615htgmii_ise中的_ise表示工程最终的编译工具用的是ISE,也就是说先通过EDK设计好,然后输出到ISE,最后通过ISE编译完生成FPGA的BIT位流文件。

ISE教程

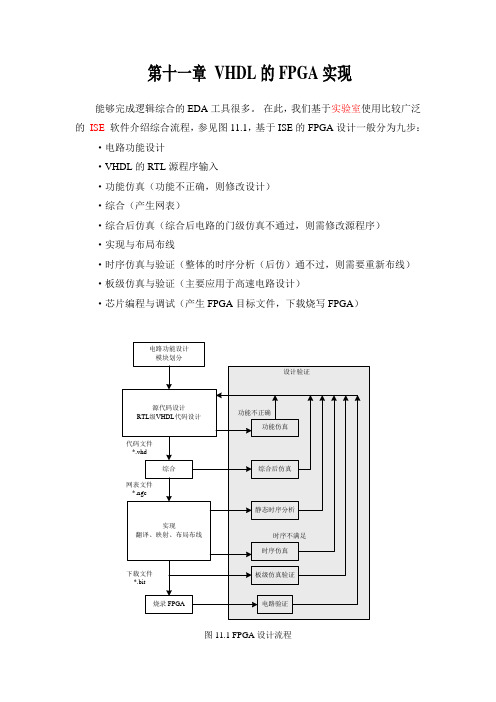

第十一章VHDL的FPGA实现能够完成逻辑综合的EDA工具很多。

在此,我们基于实验室使用比较广泛的ISE 软件介绍综合流程,参见图11.1,基于ISE的FPGA设计一般分为九步:·电路功能设计·VHDL的RTL源程序输入·功能仿真(功能不正确,则修改设计)·综合(产生网表)·综合后仿真(综合后电路的门级仿真不通过,则需修改源程序)·实现与布局布线·时序仿真与验证(整体的时序分析(后仿)通不过,则需要重新布线)·板级仿真与验证(主要应用于高速电路设计)·芯片编程与调试(产生FPGA目标文件,下载烧写FPGA)图11.1 FPGA设计流程在仿真模型中完全可以用VHDL来描述一项设计的时序特性,但在综合中,这些时序行为(如惯性或传输延迟)的描述都会被VHDL综合器忽略,而此设计的实际时序行为仅依赖于目标器件的物理结构和映射方式。

因此,若将设计模型从一个目标器件移植到另一个目标器件时,那些依赖于正确的延迟特性才能正常工作的VHDL模型,将不可能得到期望的综合结果和时序仿真效果。

仿真模型可以描述一些无限制的条件(如无穷循环或无范围限制的整型数),硬件却不能提供这些条件。

在某些情况下,如无穷循环或循环次数不确定的情况下,综合工具会产生错误并退出。

在其他的情况下,如无范围的整数,VHDL综合器会假设一个默认的表示方式,如以32bit二进制数表示无范围的整数。

尽管这是可综合的,但却无法生成所期望的电路。

11.2 VHDL的FPGA逻辑综合以下将以第七章例7.15交通信号灯监测电路的程序为例来说明如何对VHDL程序进行综合。

具体步骤如下:1.启动ISE如图11.2所示,在windows操作系统的开始菜单中启动Xilinx ISE Design Suite 10.1中的ISE主窗口,之后如图11.3。

图11.2 启动ISE 10.1图11.3 ISE 10.1 主窗口2.创建一个新的项目ISE 10.1主窗口打开后,选择创建一个新的项目,一般分为以下七步:(1) 单击【File】 【New Project …】命令,如图11.4.1,出现图11.4.2所示的【Create New Project】对话框。

ISE使用指南中

ISE使用指南中ISE(Integrated Software Environment)是一种软件开发工具,帮助开发人员编写和调试程序。

它提供了许多功能,使开发过程更加高效和容易。

本文将介绍ISE的基本使用指南,帮助初学者了解如何使用这个强大的工具。

安装ISE开始一个新项目在安装完成后,您可以打开ISE并开始一个新项目。

在“文件”菜单中选择“新建项目”,然后按照向导的指示操作。

在新项目设置过程中,您需要输入项目名称、目标设备、工作目录等信息。

确保所有信息都输入正确,然后点击“完成”按钮。

编写代码进行综合完成代码编写后,您需要进行综合。

综合是将高级代码转换为门级网表或其他低级描述的过程。

在ISE中,您可以通过选择“综合”选项来进行综合。

确保设置正确,然后点击“运行综合”按钮。

实现与映像调试一旦设计映像到目标设备,您可以进行调试。

在ISE中,您可以使用仿真器来模拟设计行为,并找出错误。

您还可以使用调试工具来分析信号波形、查看寄存器状态等。

确保所有功能都按照预期工作。

优化性能最后,您可以优化设计的性能。

在ISE中,您可以使用不同的优化技术来减少延迟、面积等。

通过调整参数和设置,您可以使设计更加高效和稳定。

确保优化后的设计满足性能要求。

总结在本文中,我们介绍了ISE的基本使用指南。

通过正确安装软件、开始一个新项目、编写代码、进行综合实现、调试和优化性能,您可以利用ISE开发高质量的程序。

希望这些信息对您有所帮助,祝您在使用ISE中取得成功!。

思科ISE部署手册说明书

部署•思科ISE部署术语,第2页•分布式思科ISE部署中的角色,第2页•配置思科ISE节点,第2页•支持多种部署方案,第4页•思科ISE分布式部署,第5页•部署和节点设置,第8页•日志记录设置,第17页•管理员访问设置,第20页•管理节点,第23页•支持管理节点的自动故障切换,第30页•策略服务节点,第31页•监控节点,第33页•监控数据库,第37页•配置用于自动故障切换的监控节点,第39页•思科pxGrid节点,第40页•查看部署中的节点,第47页•从MnT节点下载终端统计数据,第47页•数据库崩溃或文件损坏问题,第48页•设备的监控配置,第48页•同步主要和辅助思科ISE节点,第48页•更改节点角色和服务,第48页•在思科ISE中修改节点的影响,第49页•创建策略服务节点组,第49页•从部署中删除节点,第50页•关闭思科ISE节点,第51页•需要重新注册节点的场景示例示例,第52页•更改独立思科ISE节点的主机名或IP地址,第53页部署思科ISE部署术语思科ISE部署术语以下是讨论思科ISE部署方案时常用的术语:•服务:服务是角色提供的特定功能,例如网络访问、分析器、终端安全评估、安全组访问、监控和故障排除等。

•节点:节点是运行思科ISE软件的单个实例。

思科ISE可用作设备,也可用作能在VMware上运行的软件。

运行思科ISE软件的每个实例(设备或VMware)叫节点。

•角色:节点的角色决定节点提供的服务。

思科ISE节点可以承担以下任意角色:管理、策略服务、监控和pxGrid。

通过管理员门户可用的菜单选项取决于思科ISE节点承担的职责和角色。

•部署模式:决定您的部署是分布式、独立式还是作为基本双节点部署的独立式高可用性部署。

分布式思科ISE部署中的角色思科ISE节点可以承担管理、策略服务或监控角色。

思科ISE节点可以根据它承担的角色提供各种服务。

部署中的每个节点均可承担管理、策略服务和监控角色。

ISE软件使用说明

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

ISE软件的基本操作

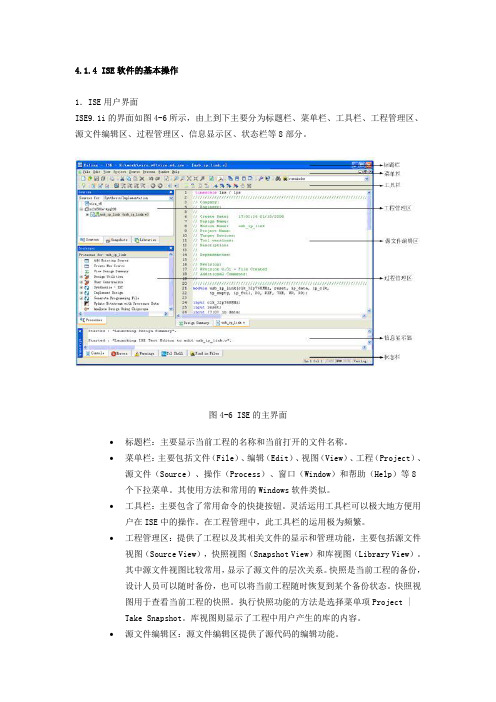

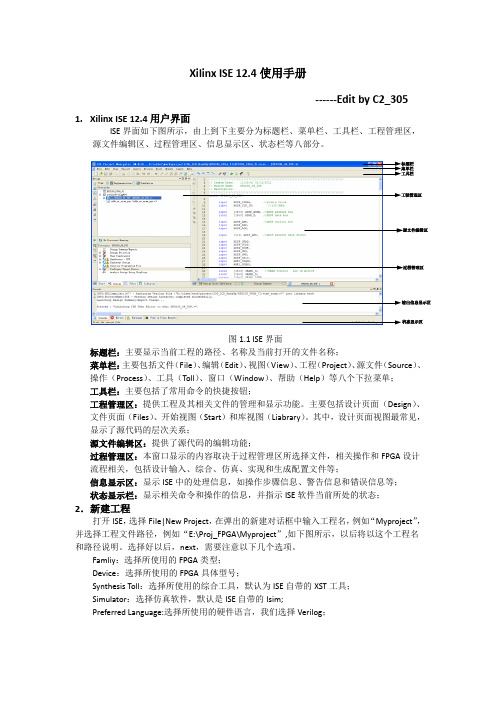

4.1.4 ISE软件的基本操作1.ISE用户界面ISE9.1i的界面如图4-6所示,由上到下主要分为标题栏、菜单栏、工具栏、工程管理区、源文件编辑区、过程管理区、信息显示区、状态栏等8部分。

图4-6 ISE的主界面∙标题栏:主要显示当前工程的名称和当前打开的文件名称。

∙菜单栏:主要包括文件(File)、编辑(Edit)、视图(View)、工程(Project)、源文件(Source)、操作(Process)、窗口(Window)和帮助(Help)等8个下拉菜单。

其使用方法和常用的Windows软件类似。

∙工具栏:主要包含了常用命令的快捷按钮。

灵活运用工具栏可以极大地方便用户在ISE中的操作。

在工程管理中,此工具栏的运用极为频繁。

∙工程管理区:提供了工程以及其相关文件的显示和管理功能,主要包括源文件视图(Source View),快照视图(Snapshot View)和库视图(Library View)。

其中源文件视图比较常用,显示了源文件的层次关系。

快照是当前工程的备份,设计人员可以随时备份,也可以将当前工程随时恢复到某个备份状态。

快照视图用于查看当前工程的快照。

执行快照功能的方法是选择菜单项Project |Take Snapshot。

库视图则显示了工程中用户产生的库的内容。

∙源文件编辑区:源文件编辑区提供了源代码的编辑功能。

∙过程管理区:本窗口显示的内容取决于工程管理区中所选定的文件。

相关操作和FPGA设计流程紧密相关,包括设计输入、综合、仿真、实现和生成配置文件等。

对某个文件进行了相应的处理后,在处理步骤的前面会出现一个图标来表示该步骤的状态。

∙信息显示区:显示ISE中的处理信息,如操作步骤信息、警告信息和错误信息等。

信息显示区的下脚有两个标签,分别对应控制台信息区(Console)和文件查找区(Find in Files)。

如果设计出现了警告和错误,双击信息显示区的警告和错误标志,就能自动切换到源代码出错的地方。

ISE的使用说明

ISE的使用说明ISE(Integrated Software Environment)是一种集成软件环境,用于设计和验证硬件开发项目。

它由Xilinx公司开发,旨在为FPGA(Field-Programmable Gate Array)和SoC(System-on-a-Chip)设计提供完整的解决方案。

ISE具有多种功能和工具,可以帮助工程师在整个开发过程中完成各种任务。

ISE的安装:ISE的主要功能:ISE为硬件设计和验证提供了全面的解决方案。

以下是ISE的主要功能:2.综合和优化:ISE包含了综合和优化工具,将HDL代码转换为布尔函数表示。

综合工具会分析代码并生成等效的硬件电路电路。

优化工具会尝试将电路改进为更有效的形式,以提高性能和减少资源消耗。

3.约束和分析:在设计过程中,您通常需要对硬件进行约束,以满足特定的要求。

ISE提供了工具来定义时序约束、电气约束和物理约束,并分析设计是否满足这些约束。

4.实现和布局:一旦设计和优化完成,ISE将使用实现和布局工具将电路映射到目标FPGA或SoC中。

这些工具将选择适当的逻辑资源,并将其布局在特定的芯片区域,以最大程度地提高性能和效率。

5.仿真和调试:在设计过程中,您需要对硬件进行仿真和调试,以验证其正确性和性能。

ISE提供了仿真工具,可以对设计进行功能仿真、时序仿真和混合信号仿真。

它还提供了调试功能,可帮助您定位和解决问题。

以下是使用ISE的一般步骤:1.创建新工程:在ISE中,您需要先创建一个新的工程,用于存储和组织设计文件。

可以在ISE中创建一个新的工程,并选择适当的目标设备。

2. 添加设计文件:一旦工程创建完成,您可以添加设计文件到工程中。

通过右键单击工程文件夹,并选择“Add Source”来添加设计文件。

选择适当的文件类型,并在文件对话框中选择要添加的文件。

3. 设置约束:在设计过程中,您需要为硬件设计设置约束,以满足特定的要求。

通过右键单击工程文件夹,并选择“Add Constraints”来添加约束文件。

关于Xilinx ISE简单使用方法介绍

output [7:0] y_out,

);

assign y_out = flag ? x_in : 8'b00000000;

endmodule

3.程序语法检查

如下图所示:

或者:

4.创建测试文件(功能仿真数据的建立)

ProjectNew Source。如输入文件名:Two2One_tf(*.v)。

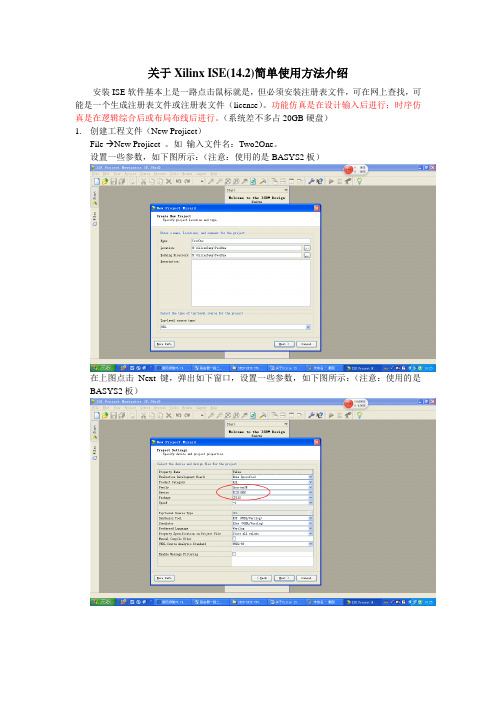

关于Xilinx ISE(14.2)简单使用方法介绍

安装ISE软件基本上是一路点击鼠标就是,但必须安装注册表文件,可在网上查找,可能是一个生成注册表文件或注册表文件(license)。功能仿真是在设计输入后进行;时序仿真是在逻辑综合后或布局布线后进行。(系统差不多占20GB硬盘)

1.创建工程文件(New Projiect)

将运行另外一个程序产生仿真波形图,如下图所示:

详细波形图:

6.管脚适配(为下载做准备)

先创建*.UCF文件

弹出窗口,点击Yes,创建.UCF文件

之后,系统会启动管脚配置程序,然后设计人员根据情况配置管脚,下图为BASYS2板管脚情况,所示:

适配后:

配置好管脚后保存好文件。

7.综合与实现

管脚分配完成之后,必须进行布局布线,如下图所示:

FileNew Projiect。如输入文件名:Two2One。

设置一些参数,如下图所示:(注意:使用的是BASYS2板)

在上图点击Next键,弹出如下窗口,设置一些参数,如下图所示:(注意:使用的是BASYS2板)

2.创建资源文件(New Source)

ProjectNew Source。如输入文件名:One2Two。

选择,如Verilog Test Fxiture,建立用于测试以上资源文件(电路)用的数据文件。建立不同时间段的输入数据,用于产生相应时段的输出波形。

ISE使用指南完整版

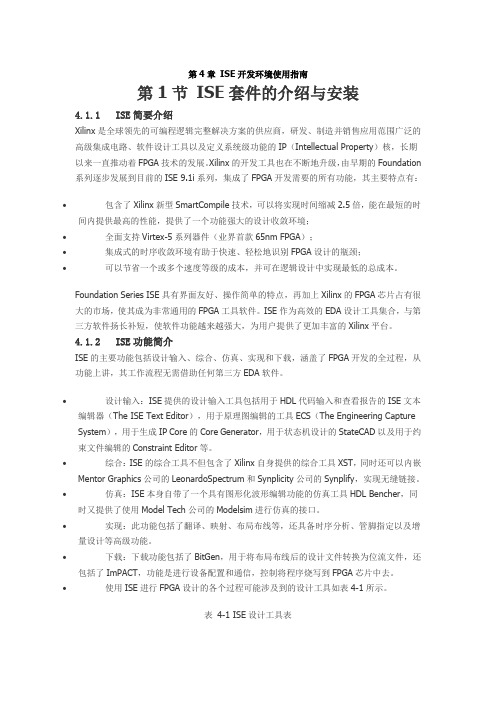

第4章ISE开发环境使用指南第1节ISE套件的介绍与安装4.1.1 ISE简要介绍Xilinx是全球领先的可编程逻辑完整解决方案的供应商,研发、制造并销售应用范围广泛的高级集成电路、软件设计工具以及定义系统级功能的IP(Intellectual Property)核,长期以来一直推动着FPGA技术的发展。

Xilinx的开发工具也在不断地升级,由早期的Foundation 系列逐步发展到目前的ISE 9.1i系列,集成了FPGA开发需要的所有功能,其主要特点有:•包含了Xilinx新型SmartCompile技术,可以将实现时间缩减2.5倍,能在最短的时间内提供最高的性能,提供了一个功能强大的设计收敛环境;•全面支持Virtex-5系列器件(业界首款65nm FPGA);•集成式的时序收敛环境有助于快速、轻松地识别FPGA设计的瓶颈;•可以节省一个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

Foundation Series ISE具有界面友好、操作简单的特点,再加上Xilinx的FPGA芯片占有很大的市场,使其成为非常通用的FPGA工具软件。

ISE作为高效的EDA设计工具集合,与第三方软件扬长补短,使软件功能越来越强大,为用户提供了更加丰富的Xilinx平台。

4.1.2 ISE功能简介ISE的主要功能包括设计输入、综合、仿真、实现和下载,涵盖了FPGA开发的全过程,从功能上讲,其工作流程无需借助任何第三方EDA软件。

•设计输入:ISE提供的设计输入工具包括用于HDL代码输入和查看报告的ISE文本编辑器(The ISE Text Editor),用于原理图编辑的工具ECS(The Engineering Capture System),用于生成IP Core的Core Generator,用于状态机设计的StateCAD以及用于约束文件编辑的Constraint Editor等。

•综合:ISE的综合工具不但包含了Xilinx自身提供的综合工具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum和Synplicity公司的Synplify,实现无缝链接。

思科身份服务引擎(ISE)安装指南:使用 CIMC 安装说明书

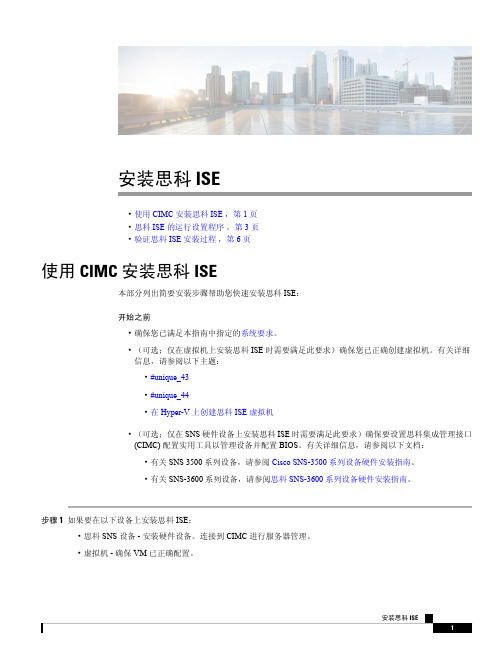

安装思科ISE•使用CIMC安装思科ISE,第1页•思科ISE的运行设置程序,第3页•验证思科ISE安装过程,第6页使用CIMC安装思科ISE本部分列出简要安装步骤帮助您快速安装思科ISE:开始之前•确保您已满足本指南中指定的系统要求。

•(可选;仅在虚拟机上安装思科ISE时需要满足此要求)确保您已正确创建虚拟机。

有关详细信息,请参阅以下主题:•#unique_43•#unique_44•在Hyper-V上创建思科ISE虚拟机•(可选;仅在SNS硬件设备上安装思科ISE时需要满足此要求)确保要设置思科集成管理接口(CIMC)配置实用工具以管理设备并配置BIOS。

有关详细信息,请参阅以下文档:•有关SNS3500系列设备,请参阅Cisco SNS-3500系列设备硬件安装指南。

•有关SNS-3600系列设备,请参阅思科SNS-3600系列设备硬件安装指南。

步骤1如果要在以下设备上安装思科ISE:•思科SNS设备-安装硬件设备。

连接到CIMC进行服务器管理。

•虚拟机-确保VM已正确配置。

1步骤2下载思科ISE ISO 映像。

a)转至/go/ise 。

您必须已经具有有效的 登录凭证才能访问此链接。

b)点击为此产品下载软件(Download Software for this Product)。

思科ISE 映像上已经安装90天的评估许可证,因此在完成安装和初始配置后,可以对所有思科ISE 服务进行测试。

步骤3启动设备或虚拟机。

•思科SNS 设备:1.连接到CIMC 并使用CIMC 凭证登录。

2.启动KVM 控制台。

3.选择“虚拟媒体”(Virtual Media)>“激活虚拟设备”(Activate Virtual Devices)。

4.选择“虚拟媒体”(Virtual Media)>“映射CD/DVD ”(Map CD/DVD),并选择ISE ISO 映像,然后点击“映射设备”(Map Device)。

ISE使用指南下

ISE使用指南下ISE(Integrated Software Environment,综合软件环境)是一种基于计算机软件的工具,用于辅助设计、开发和部署各种应用程序。

它提供了一个集成的开发环境,可以帮助开发者提高开发效率、降低开发成本,并提供高质量的应用程序。

2.创建新项目:在开始使用ISE之前,您需要创建一个新项目来组织您的开发工作。

在ISE中,您可以选择创建一个全新的项目,或者导入一个已有的项目。

创建新项目时,您需要选择项目的类型(如Web应用程序、桌面应用程序或移动应用程序)以及项目的目录结构。

4.调试代码:在开发应用程序时,您经常需要调试代码以查找并修复错误。

ISE提供了一个强大的调试器,可以帮助您进行代码调试。

您可以设置断点、单步调试代码,并查看变量的值和堆栈跟踪信息。

5.构建和部署应用程序:当您完成了代码的编写和调试,您可以使用ISE将应用程序构建成可执行文件或部署包。

ISE提供了多种构建工具和选项,您可以选择适合您项目的选项。

一旦构建完成,您可以将应用程序部署到目标设备上进行测试和使用。

6.管理代码库:在开发过程中,您可能需要使用代码版本控制系统来管理您的代码库。

ISE集成了一些常用的代码版本控制系统,如Git和SVN,可以帮助您轻松地管理和协作开发代码。

7.性能优化:在开发和部署应用程序时,您可能会遇到性能问题。

ISE提供了一些性能优化工具和分析器,可以帮助您分析和改进应用程序的性能。

您可以使用这些工具来查找性能瓶颈和优化热点,并采取相应的措施来提高应用程序的性能。

8.文档和帮助:ISE提供了丰富的文档和帮助资源,可以帮助您更好地了解和使用ISE。

您可以访问ISE的官方网站或查看ISE内置的帮助文档,以获得详细的使用说明和示例代码。

总之,ISE是一个非常强大和灵活的开发工具,可以帮助开发者更高效地开发各种类型的应用程序。

通过使用ISE,您可以提高开发效率、降低开发成本,并提供高质量的应用程序。

ISE12.4使用手册

Xilinx ISE 12.4使用手册------Edit by C2_305 1.Xilinx ISE 12.4用户界面ISE界面如下图所示,由上到下主要分为标题栏、菜单栏、工具栏、工程管理区,源文件编辑区、过程管理区、信息显示区、状态栏等八部分。

过程管理区图1.1 ISE界面标题栏:主要显示当前工程的路径、名称及当前打开的文件名称;菜单栏:主要包括文件(File)、编辑(Edit)、视图(View)、工程(Project)、源文件(Source)、操作(Process)、工具(Toll)、窗口(Window)、帮助(Help)等八个下拉菜单;工具栏:主要包括了常用命令的快捷按钮;工程管理区:提供工程及其相关文件的管理和显示功能。

主要包括设计页面(Design)、文件页面(Files)、开始视图(Start)和库视图(Liabrary)。

其中,设计页面视图最常见,显示了源代码的层次关系;源文件编辑区:提供了源代码的编辑功能;过程管理区:本窗口显示的内容取决于过程管理区所选择文件,相关操作和FPGA设计流程相关,包括设计输入、综合、仿真、实现和生成配置文件等;信息显示区:显示ISE中的处理信息,如操作步骤信息、警告信息和错误信息等;状态显示栏:显示相关命令和操作的信息,并指示ISE软件当前所处的状态;2.新建工程打开ISE,选择File|New Project,在弹出的新建对话框中输入工程名,例如“Myproject”,并选择工程文件路径,例如“E:\Proj_FPGA\Myproject”,如下图所示,以后将以这个工程名和路径说明。

选择好以后,next,需要注意以下几个选项。

Famliy:选择所使用的FPGA类型;Device:选择所使用的FPGA具体型号;Synthesis Toll:选择所使用的综合工具,默认为ISE自带的XST工具;Simulator:选择仿真软件,默认是ISE自带的Isim;Preferred Language:选择所使用的硬件语言,我们选择Verilog;图2.1 新建工程step1 图2.2 新建工程step2后面直接点next即可,直到完成新工程的建立。

xilinx ise 软件使用方法

双击【 Finish】

选择后缀为bit的文件,单击【 Open】

单击

单击【 Bypass 】

完成下载

1、光标移至该图 标,单击右键

2、单击 Program

单击【 Ok】

下载成功。在开发板上观察结果。

ISE软件使用

• 设计流程 • 新建项目 • 综合 • 仿真

• 设计实现

设计流程

文本编辑器、图形编辑器

VHDL仿真器 (行为仿真、 功能仿真、 时序仿真)

VHDL综合器

网表文件 (EDIF、XNL、 VHDL…) 门级仿真器

(逻辑综合、优化)

FPGA/CPLD布线/适配器 (自动优化、布局、布线、适配)

在测试文件的 tb 进程中对输入信号进行赋值

如下图,在Source for 中选择【Behavioral

Simulation】

如下图,在Processes 窗口中双击【Simulate Behavioral Model】

按下图选择【Add】【Wave】【Signal in Design】,添加 需要观察的信号。如不需观察中间信号,此步骤可省略。

在文本编辑器中输入源文件

综合

在Source窗口中选中需要处理的源文件,在Process窗口 中双击Synthesize-XST。

仿真

如下图,单击【 Create New Source】, 选择源文件类型【 VHDL Test Bench 】,填写源文件名称、路径 然后单击【Next】

如下图,选择与仿真测试文件所对应的源文件,然后单击 【Next】

按下图选择【Run All】, 【Zoom out】 【Zoom mode】、

并删除多余信号。如不需观察中间信号,此步骤可省略

ISE的使用说明

ISE的使用说明ISE是集成电路设计中常用的一种工具,是一种综合软件环境,它用于设计目的,例如创建和测试电路设计的逻辑模型。

本文将详细介绍ISE 的使用说明,包括安装步骤、主要功能、常用操作和调试技巧。

一、安装步骤2.运行安装程序:双击安装程序启动安装流程,按照提示完成安装向导。

3.设置安装选项:在安装向导中,您可以选择安装目录、添加快捷方式和其他个性化设置。

4.完成安装:等待安装程序完成所有必要文件的复制和配置,安装完成后重启计算机。

二、主要功能1.逻辑设计:ISE提供了丰富的逻辑设计工具,包括原理图设计、硬件描述语言编写和逻辑优化等功能。

用户可以通过拖放元件、连接线和逻辑门,创建电路的逻辑模型。

2.约束设置:ISE允许用户定义各种约束条件,如时钟频率、延迟限制和电气规范等。

这些约束条件对于确保设计的正确性和性能至关重要。

3.仿真和验证:ISE提供了强大的仿真和验证工具,以验证设计的功能和时序正确性。

用户可以模拟不同输入情况下的电路行为,并通过波形查看器等工具进行调试和分析。

4.综合和布局布线:ISE可以将逻辑设计综合为电路网表,并根据指定的目标器件和约束条件进行布局布线。

综合和布局布线的结果直接影响电路的性能和可靠性。

6.文档生成:ISE可以根据设计规范和用户的需求,自动生成各种设计文档,如用户手册、接口定义和设计报告等。

这些文档对于设计团队的交流和项目管理非常重要。

三、常用操作2.添加文件:在工程中,用户可以添加设计文件、约束文件和仿真文件等。

这些文件描述了电路的结构、约束条件和仿真模型,是设计的基础。

3.进行综合和优化:在添加文件后,用户需要对设计进行综合和优化,以便生成电路网表。

综合和优化的操作可以通过综合工具和约束文件完成。

4.进行布局布线:综合完成后,用户需要对设计进行布局布线,以生成具体的物理布局。

布局布线的操作可以通过布局布线工具和约束文件完成。

5.进行仿真和验证:在布局布线完成后,用户可以使用ISE提供的仿真和验证工具,对设计进行功能和时序验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

给出了整个工 程大致属性

Finish

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

完成后在Sources窗口中显 示工程文件夹以及工程所用 芯片。

在该窗口中右键

可以新建文件,添加已经写 好的文件,添加文件并复制 该文件到工程文件夹中。

Xilinx公司ISE10.1软件设计流程介绍

Xilinx公司ISE10.1软件设计流程介绍

--打开ISE软件时的面板

当以前使用 过该软件时会默 认打开上一个工 程。

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

选择芯片

选择综合工具 选择仿真工具 选择代码语言

--添加波形仿真文件

给出该波形 文件的相关 属性

Finish

Xilinx公司ISE10.1软件设计流程介绍

--添加波形仿真文件

注意选择

波形测试文件内容,具体 参考Blackboard中举例

波形测试文件,

Xilinx公司ISE10.1软件设计流程介绍

--添加波形仿真文件

注意选择

仿真时一定要点在 测试文件上

Next

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

这里可以新建一 个文件,也可以 在工程属性建立 完成后在工程内 新建,我们选择 Next

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

这里可以添加工 程文件,也可以 在工程建立后添 加,我们选择 Next

Xilinx公司ISE10.1软件设计流程介绍

双击进行仿真 仿真结果

--添加实体端口

Xቤተ መጻሕፍቲ ባይዱlinx公司ISE10.1软件设计流程介绍

--自动生成文件结构框架

双击gate文件 自动生成实体结构

生成了结构体框架 只需加入逻辑语句即可

Xilinx公司ISE10.1软件设计流程介绍

--添加代码及注释

添加的 逻辑代 码

--之后为 注释语句

Xilinx公司ISE10.1软件设计流程介绍

这个图标指示顶层文件 选中顶层文件,Processes窗口中 给出能操作的项目

双击XST进行综合操作

Xilinx公司ISE10.1软件设计流程介绍

--添加波形仿真文件

Next

Xilinx公司ISE10.1软件设计流程介绍

--添加波形仿真文件

选择所要仿真的 VHDL文件

Next

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

新建文件 的类型, 不同的类 型有着不 同的功能 和意义。

该文 件的 实体 名

Xilinx公司ISE10.1软件设计流程介绍

--添加实体端口

Next

端口名

端口的类型及位数

Xilinx公司ISE10.1软件设计流程介绍

--添加实体端口

给出了该文件 的概要

Finish

Xilinx公司ISE10.1软件设计流程介绍