定点DSP中高精度除法的实现方法

第三章 DSP定点运算

数的定标 高级语言 DSP定点算术运算 非线性运算的定点快速实现 小 结

3.1.1 数的定标

在定点DSP芯片中,采用定点数进行数 值运算,其操作数一般采用整型数来表 示。 一个整型数的最大表示范围取决于DSP 芯片所给定的字长,一般为16位或24位。 显然,字长越长,所能表示的数的范围 越大,精度也越高。

虽然有时需要使用混合表示法,但是,更通常 的是全部以Q15格式表示的小数或以Q0格式表 示的整数来工作。 这一点对于主要是乘法和累加的信号处理算法 特别现实,小数乘以小数得小数,整数乘以整 数得整数。 乘积累加时可能会出现溢出现象,在这种情况 下,程序员应当了解数学里面的物理过程以注 意可能的溢出情况。 返回

3.4.2 查表法

在实时DSP应用中实现非线性运算,一般都采取适当 降低运算精度来提高程序的运算速度。查表法是快速 实现非线性运算最常用的方法。 查表法:根据自变量的范围和精度要求事先制作一张 表格,根据输入值确定表的地址,根据地址就可得到 相应的值。 显然输入的范围越大,精度要求越高,则所需的表格 就越大,即存储量也越大。 查表法求值所需的计算就是根据输入值确定表的地址, 因而运算量较小。 查表法比较适合于非线性函数是周期函数或已知非线 性函数输入值范围这两种情况 。

3.3 DSP定点算术运算

定点DSP芯片的数值表示是基于2的补码表示形 式。 每个16位数用1个符号位、i个整数位和15-i个小 数位来表示。 例如数00000010.10100000表示的值为 21 + 2 −1 + 2 −3 =2.625, 这个数可用Q8格式(8个小数位)来表示,它表 示的数值范围为-128~+127.996,一个Q8定点 数的小数精度为1/256=0.004。

DSP基本算数运算

基本算术运算一﹑实验目的加、减、乘、除是数字信号处理中最基本的算术运算。

DSP 中提供了大量的指令来实现这些功能。

本实验学习使用定点DSP 实现16位定点加、减、乘、除运算的基本方法和编程技巧。

二﹑实验原理1﹑定点DSP 中数据表示方法C54X 是16位的定点DSP 。

一个16位的二进制数既可以表示一个整数,也可以表示一个小数。

当它表示一个整数时,其最低位(D0)表示02,D1位表示12,次高位(D14)表示142。

如果表示一个有符号数时,最高位(D15)为符号位,0表示正数,1表示负数。

例如,07FFFH 表示最大的正数32767(十进制),而0FFFFH 表示最大的负数-1(负数用2的补码方式显示)。

当需要表示小数时,小数点的位置始终在最高位后,而最高位(D15)表示符号位。

这样次高位(D14)表示12-,然后是22-,最低位(D0)表示152-。

所以04000H 表示小数0.5,01000H 表示小数125.023=-,而0001H 表示16位定点DSP 能表示的最小的小数(有符号)152-=0.000030517578125。

在后面的实验中,除非有特别说明,我们指的都是有符号数。

在C54X 中,将一个小数用16位定点格式来表示的方法是用152乘以该小数,然后取整。

从上面的分析可以看出,在DSP 中一个16进制的数可以表示不同的十进制数,或者是整数,或者是小数(如果表示小数,必定小于1),但仅仅是在做整数乘除或小数乘除时,系统对它们的处理才是有所区别的,而在加减运算时,系统都当成整数来处理。

2﹑实现16定点加法C54X 中提供了多条用于加法的指令,如ADD ,ADDC ,ADDM 和ADDS 。

其中ADDS 用于无符号数的加法运算,ADDC 用于带进位的加法运算(如32位扩展精度加法),而ADDM 专用于立即数的加法。

ADD 指令的寻址方式很多,其详细使用说明请参考《TMS320C54X 实用教程》。

DSP芯片的定点运算

第3章DSP芯片的定点运算3.1 数的定标在定点DSP芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。

一个整型数的最大表示范围取决于DSP芯片所给定的字长,一般为16位或24位。

显然,字长越长,所能表示的数的范围越大,精度也越高。

如无特别说明,本书均以16位字长为例。

DSP芯片的数以2的补码形式表示。

每个16位数用一个符号位来表示数的正负,0表示数值为正,1则表示数值为负。

其余15位表示数值的大小。

因此二进制数0010000000000011b=8195二进制数1111111111111100b=-4对DSP芯片而言,参与数值运算的数就是16位的整型数。

但在许多情况下,数学运算过程中的数不一定都是整数。

那么,DSP芯片是如何处理小数的呢?应该说,DSP芯片本身无能为力。

那么是不是说DSP芯片就不能处理各种小数呢?当然不是。

这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。

这就是数的定标。

通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。

数的定标有Q表示法和S表示法两种。

表3.1列出了一个16位数的16种Q表示、S表示及它们所能表示的十进制数值范围。

从表3.1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示但对于DSP芯片来说,处理方法是完全相同的。

从表3.1还可以看出,不同的Q所表示的数不仅范围不同,而且精度也不相同。

Q越大,数值范围越小,但精度越高;相反,Q越小,数值范围越大,但精度就越低。

例如,Q0的数值范围是-32768到+32767,其精度为1,而Q15的数值范围为-1到0.9999695,精度为1/32768 =0.00003051。

因此,对定点数而言,数值范围与精度是一对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想提高精度,则数的表示范围就相应地减小。

DSP的定点运算

DSP的定点运算DSP的定点运算技术2007-06-29 09:45:14阅读82评论0字号:大中小许DSP芯片只支持整数运算,如果现在这些芯片上进行小数运算的话,定点小数运算应该是最佳选择了,此外即使芯片支持浮点数,定点小数运算也是最佳的速度选择。

在DSP世界中,由于DSP芯片的限制,经常使用定点小数运算。

所谓定点小数,实际上就是用整数来进行小数运算。

下面先介绍定点小数的一些理论知识,然后以C语言为例,介绍一下定点小数运算的方法。

在TI C5000 DSP系列中使用16比特为最小的储存单位,所以我们就用16比特的整数来进行定点小数运算。

先从整数开始,16比特的储存单位最多可以表示0x0000到0xffff,65536种状态,如果它表示C语言中的无符号整数的话,就是从0到65535。

如果需要表示负数的话,那么最高位就是符号位,而剩下的15位可以表示32768种状态。

这里可以看出,对于计算机或者DSP芯片来说,符号并没有什么特殊的储存方式,其实是和数字一起储存的。

为了使得无论是无符号数还是符号数,都可以使用同样的加法减法规则,符号数中的负数用正数的补码表示。

我们都知道-1+1=0,而0x0001表示1,那么-1用什么来表示才能使得-1+1=0呢?答案很简单:0xffff。

现在就可以打开Windows的计算器,用16进制计算一下0xffff+0x0001,结果是0x10000。

那么0x10000和0x0000等价么,我们刚才说过用16比特来表达整数,最高位的1是第17位,这一位是溢出位,在运算寄存器中没有储存这一位,所以结果是低16位,也就是0x0000。

现在我们知道负数的表达方式了。

举个例子:-100。

首先我们需要知道100的16进制,用计算器转换一下,可以知道是0x0064,那么-100就是0x10000-0x0064,用计算器算一下得0xff9c。

还有一种简单的转换符号的方法,就是取反加一:把数x写成二进制格式,每位0变1,1变0,最后把结果加1就是-x了。

DSP定点运算

一DSP定点算数运算1 数的定标在定点DSP芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。

一个整型数的最大表示范围取决于DSP芯片所给定的字长,一般为16位或24位。

显然,字长越长,所能表示的数的范围越大,精度也越高。

如无特别说明,本书均以16位字长为例。

DSP芯片的数以2的补码形式表示。

每个16位数用一个符号位来表示数的正负,0表示数值为正,l则表示数值为负。

其余15位表示数值的大小。

因此,二进制数0010000000000011b=8195二进制数1111111111111100b= -4对DSP芯片而言,参与数值运算的数就是16位的整型数。

但在许多情况下,数学运算过程中的数不一定都是整数。

那么,DSP芯片是如何处理小数的呢?应该说,DSP芯片本身无能为力。

那么是不是说DSP芯片就不能处理各种小数呢?当然不是。

这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。

这就是数的定标。

通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。

数的定标有Q表示法和S表示法两种。

表1.1列出了一个16位数的16种Q表示、S表示及它们所能表示的十进制数值范围。

从表1.1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同。

例如,16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示但对于DSP芯片来说,处理方法是完全相同的。

从表1.1还可以看出,不同的Q所表示的数不仅范围不同,而且精度也不相同。

Q越大,数值范围越小,但精度越高;相反,Q越小,数值范围越大,但精度就越低。

例如,Q0 的数值范围是一32768到+32767,其精度为1,而Q15的数值范围为-1到0.9999695,精度为1/32768=0.00003051。

因此,对定点数而言,数值范围与精度是一对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想精度提高,则数的表示范围就相应地减小。

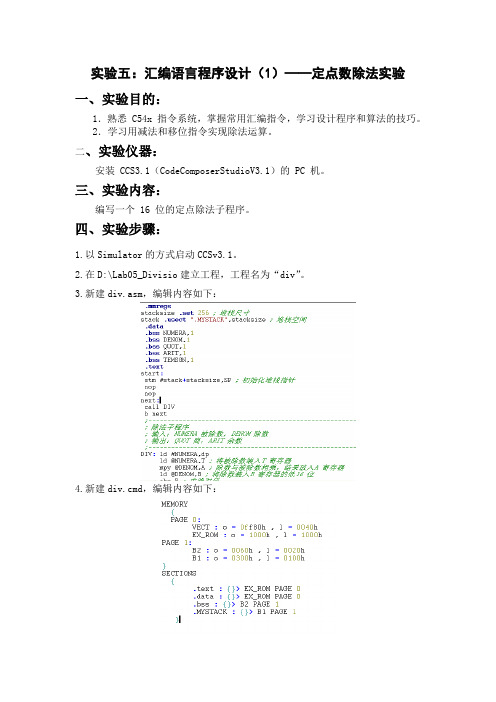

DSP实验报告五:汇编语言程序设计(1)——定点数除法实验

实验五:汇编语言程序设计(1)——定点数除法实验一、实验目的:1.熟悉 C54x 指令系统,掌握常用汇编指令,学习设计程序和算法的技巧。

2.学习用减法和移位指令实现除法运算。

二、实验仪器:安装 CCS3.1(CodeComposerStudioV3.1)的 PC 机。

三、实验内容:编写一个 16 位的定点除法子程序。

四、实验步骤:1.以Simulator的方式启动CCSv3.1。

2.在D:\Lab05_Divisio建立工程,工程名为“div”。

3.新建div.asm,编辑内容如下:4.新建div.cmd,编辑内容如下:5.汇编/编译与连接执行Project→Rebuild All 编译链接.如果未对汇编语言修改编译连接环境(参见实验 2),编译时将出现如下错误:warning:entry point symbol _c_int0 undefined出错原因:缺省时CCS设置项目程序为 C 语言编译,因此当我们编译汇编程序时,要对项目作适当配置。

发现错误要及时修改,修改方法与实验 2 相似:执行Project→Build Options…打开编译选项;在linker 属性页上单击,把Autoinit Model栏选择为 No Autoinitialization;按“确定”保存对配置的修改。

6. 装载程序准备运行调试(1)执行 File→Load Program 装载程序,装载完程序后,CCS把指针指向程序区 0000 处。

为了执行我们的程序代码,需要修改 DSP 的 PC 值;执行ViewÆCPU RegistersÆCPU Registers 打开寄存器窗口;双击窗口中的 PC 标号,CC 弹出修改对话框供修改寄存器;在对话框中输入”start“,程序将处于我们的程序入口点上。

(2)在div.asm窗口中NUMERA变量名上双击鼠标左键,再单击鼠标右键,选择“Add to Watch Window”,在观察窗口中出现 NUMERA 变量,请将窗口中变量名(Name)由“NUMERA”改成“(int*)NUMERA”;“Radix”由“hex”改成“dec”,结果如下:(3)重复(1)的操作,加入 DENOM、QUOT 和 ARIT 四个变量。

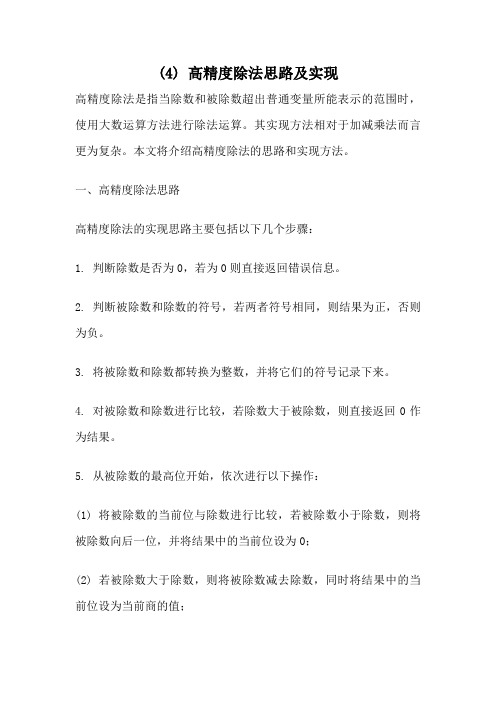

(4) 高精度除法思路及实现

(4) 高精度除法思路及实现高精度除法是指当除数和被除数超出普通变量所能表示的范围时,使用大数运算方法进行除法运算。

其实现方法相对于加减乘法而言更为复杂。

本文将介绍高精度除法的思路和实现方法。

一、高精度除法思路高精度除法的实现思路主要包括以下几个步骤:1. 判断除数是否为0,若为0则直接返回错误信息。

2. 判断被除数和除数的符号,若两者符号相同,则结果为正,否则为负。

3. 将被除数和除数都转换为整数,并将它们的符号记录下来。

4. 对被除数和除数进行比较,若除数大于被除数,则直接返回0作为结果。

5. 从被除数的最高位开始,依次进行以下操作:(1) 将被除数的当前位与除数进行比较,若被除数小于除数,则将被除数向后一位,并将结果中的当前位设为0;(2) 若被除数大于除数,则将被除数减去除数,同时将结果中的当前位设为当前商的值;(3) 若被除数等于除数,则直接将结果中的当前位设为1,并返回结果。

6. 若被除数的所有位数都被处理完毕,则返回结果。

二、高精度除法实现高精度除法的实现可以使用字符串来存储被除数、除数和结果。

具体实现步骤如下:1. 首先定义两个字符串来存储被除数和除数,并读入它们的值。

2. 判断除数是否为0,若为0则直接返回错误信息。

3. 判断被除数和除数的符号,并将它们的符号记录下来。

4. 去除被除数和除数的符号,并将它们转换为整数。

这里可以使用字符串转数字的方法来实现。

5. 对被除数和除数进行比较,若除数大于被除数,则直接返回0作为结果。

6. 定义一个字符串来存储结果,并初始化为0。

7. 从被除数的最高位开始,依次进行以下操作:(1) 将被除数的当前位与除数进行比较,若被除数小于除数,则将被除数向后一位,并将结果中的当前位设为0;(2) 若被除数大于除数,则将被除数减去除数,同时将结果中的当前位设为当前商的值;(3) 若被除数等于除数,则直接将结果中的当前位设为1,并返回结果。

8. 若被除数的所有位数都被处理完毕,则返回结果。

DSP芯片的定点运算之四非线性运算的定点快速实现

DSP芯片的定点运算之四非线性运算的定点快速实现在数值运算中,除基本的加减乘除运算外,还有其他许多非线性运算,如对数运算、开方运算、指数运算、三角函数运算等,实现这些非线性运算的方法一般有:(1)调用DSP编译系统的库函数;(2)查表法;(3)混合法。

下面分别介绍这三种方法。

1.调用DSP编译系统的库函数TMS320C2X/C5X的C编译器提供了比较丰富的运行支持库函数。

在这些库函数中,包含了诸如对数、开方、三角函数、指数等常用的非线性函数。

在C 程序中(也可在汇编程序中)只要采用与库函数相同的变量定义,就可以直接调用。

例如,在库函数中,定义了以10为底的常用对数log10():#include math.h double log10(double x);在C程序中按如下方式调用:float x,y;x=10.0;y=log10(x);从上例可以看出,库函数中的常用对数log10()要求的输入值为浮点数,返回值也为浮点数,运算的精度完全可以保证。

直接调用库函数非常方便,但由于运算量大,很难在实时DSP中得到应用。

2.查表法在实时DSP应用中实现非线性运算,一般都采取适当降低运算精度来提高程序的运算速度。

查表法是快速实现非线性运算最常用的方法。

采用这种方法必须根据自变量的范围和精度要求制作一张表格。

显然输入的范围越大,精度要求越高,则所需的表格就越大,即存储量也越大。

查表法求值所需的计算就是根据输入值确定表的地址,根据地址就可得到相应的值,因而运算量较小。

查表法比较适合于非线性函数是周期函数或已知非线性函数输入值范围这两种情况,例3.12和例3.13分别说明这两种情况。

例3.12已知正弦函数y=cos(x),制作一个512点表格,并说明查表方法。

由于正弦函数是周期函数,函数值在-1至+1之间,用查表法比较合适。

由于Q15的表示范围为-1至32767/32768之间,原则上讲-1至+1的范围必须用Q14表示。

【转】dsp定点运算基本方法

【转】dsp定点运算基本⽅法⽬录参考:⼀DSP定点算数运算1 数的定标在定点DSP芯⽚中,采⽤定点数进⾏数值运算,其操作数⼀般采⽤整型数来表⽰。

⼀个整型数的最⼤表⽰范围取决于DSP芯⽚所给定的字长,⼀般为16位或24位。

显然,字长越长,所能表⽰的数的范围越⼤,精度也越⾼。

如⽆特别说明,本书均以16位字长为例。

DSP芯⽚的数以2的补码形式表⽰。

每个16位数⽤⼀个符号位来表⽰数的正负,0表⽰数值为正,l则表⽰数值为负。

其余15位表⽰数值的⼤⼩。

因此,⼆进制数0010000000000011b=8195⼆进制数1111111111111100b= -4对DSP芯⽚⽽⾔,参与数值运算的数就是16位的整型数。

但在许多情况下,数学运算过程中的数不⼀定都是整数。

那么,DSP芯⽚是如何处理⼩数的呢?应该说,DSP芯⽚本⾝⽆能为⼒。

那么是不是说DSP芯⽚就不能处理各种⼩数呢?当然不是。

这其中的关键就是由程序员来确定⼀个数的⼩数点处于16位中的哪⼀位。

这就是数的定标。

通过设定⼩数点在16位数中的不同位置,就可以表⽰不同⼤⼩和不同精度的⼩数了。

数的定标有Q表⽰法和S表⽰法两种。

表1.1列出了⼀个16位数的16种Q表⽰、S表⽰及它们所能表⽰的⼗进制数值范围。

从表1.1可以看出,同样⼀个16位数,若⼩数点设定的位置不同,它所表⽰的数也就不同。

例如,16进制数2000H=8192,⽤Q0表⽰16进制数2000H=0.25,⽤Q15表⽰但对于DSP芯⽚来说,处理⽅法是完全相同的。

从表1.1还可以看出,不同的Q所表⽰的数不仅范围不同,⽽且精度也不相同。

Q越⼤,数值范围越⼩,但精度越⾼;相反,Q越⼩,数值范围越⼤,但精度就越低。

例如,Q0 的数值范围是⼀32768到+32767,其精度为1,⽽Q15的数值范围为-1到0.9999695,精度为1/32768=0.00003051。

因此,对定点数⽽⾔,数值范围与精度是⼀对⽭盾,⼀个变量要想能够表⽰⽐较⼤的数值范围,必须以牺牲精度为代价;⽽想精度提⾼,则数的表⽰范围就相应地减⼩。

DSP数据运算基础

DSP数据运算基础在应⽤DSP时,其实硬件⼀般都问题不⼤,主要的是软件,是算法!下⾯的关于DSP运算的精华但愿有些价值!⼀ DSP定点算数运算1 数的定标在定点DSP芯⽚中,采⽤定点数进⾏数值运算,其操作数⼀般采⽤整型数来表⽰。

⼀个整型数的最⼤表⽰范围取决于DSP芯⽚所给定的字长,⼀般为16位或24位。

显然,字长越长,所能表⽰的数的范围越⼤,精度也越⾼。

如⽆特别说明,本书均以16位字长为例。

DSP芯⽚的数以2的补码形式表⽰。

每个16位数⽤⼀个符号位来表⽰数的正负,0表⽰数值为正,l则表⽰数值为负。

其余15位表⽰数值的⼤⼩。

因此,⼆进制数0010000000000011b=8195⼆进制数1111111111111100b= -4对DSP芯⽚⽽⾔,参与数值运算的数就是16位的整型数。

但在许多情况下,数**算过程中的数不⼀定都是整数。

那么,DSP芯⽚是如何处理⼩数的呢?应该说,DSP芯⽚本⾝⽆能为⼒。

那么是不是说DSP芯⽚就不能处理各种⼩数呢?当然不是。

这其中的关键就是由程序员来确定⼀个数的⼩数点处于16位中的哪⼀位。

这就是数的定标。

通过设定⼩数点在16位数中的不同位置,就可以表⽰不同⼤⼩和不同精度的⼩数了。

数的定标有Q表⽰法和S表⽰法两种。

表1.1列出了⼀个16位数的16种Q表⽰、S表⽰及它们所能表⽰的⼗进制数值范围。

从表1.1可以看出,同样⼀个16位数,若⼩数点设定的位置不同,它所表⽰的数也就不同。

例如,16进制数2000H=8192,⽤Q0表⽰16进制数2000H=0.25,⽤Q15表⽰但对于DSP芯⽚来说,处理⽅法是完全相同的。

从表1.1还可以看出,不同的Q所表⽰的数不仅范围不同,⽽且精度也不相同。

Q越⼤,数值范围越⼩,但精度越⾼;相反,Q越⼩,数值范围越⼤,但精度就越低。

例如,Q0 的数值范围是⼀32768到+32767,其精度为1,⽽Q15的数值范围为-1到0.9999695,精度为1/32768=0.00003051。

(4) 高精度除法思路及实现

(4) 高精度除法思路及实现高精度除法是指在计算机中对于非常大的数进行除法运算时,可以保持高精度的计算结果。

在传统的计算机中,对于超过计算机位数的数进行除法运算会导致精度丢失,因此需要使用高精度除法来解决这个问题。

下面将介绍高精度除法的思路及实现。

一、思路高精度除法的主要思路是模拟手工除法的过程,将被除数从高位到低位依次除以除数,得到商和余数,并将余数作为下一位的被除数,直到除数的所有位都被除完为止。

具体的步骤如下:1. 将被除数和除数都转换成字符串形式,并将小数点移动到最后一位。

2. 初始化商和余数为0。

3. 从被除数的最高位开始,依次取出一位数字进行除法运算。

4. 将商的当前位设置为被除数的当前位除以除数的当前位的商,余数设置为被除数的当前位除以除数的当前位的余数。

5. 将商的当前位添加到结果字符串中。

6. 将余数移到下一位,继续进行下一轮的除法运算。

7. 重复步骤3到步骤6,直到被除数的所有位都被除完为止。

8. 最后得到的结果即为高精度除法的结果。

二、实现下面是一个使用Python语言实现高精度除法的示例代码:```pythondef high_precision_division(dividend, divisor):dividend_str = str(dividend)divisor_str = str(divisor)dividend_str = dividend_str.replace(".", "")divisor_str = divisor_str.replace(".", "")dividend_len = len(dividend_str)divisor_len = len(divisor_str)quotient = ""remainder = 0index = 0while index < dividend_len:current_digit = int(dividend_str[index])current_dividend = remainder * 10 + current_digitquotient += str(current_dividend // int(divisor_str[0]))remainder = current_dividend % int(divisor_str[0])index += 1return quotientdividend = 12345678901234567890divisor = 1234result = high_precision_division(dividend, divisor)print(result)```在这个示例代码中,我们首先将被除数和除数转换成字符串形式,并将小数点移动到最后一位。

DSP原理及应用实验三:除法运算程序

• 1、实验要求: 编程实现下面的除法运算: (1)16384÷(-512)

(2) 0.66 ÷(-0.33)

(3)0.4÷(-0.8)

• 2、操作步骤要点: (1)新建项目/新建文件/添加文件到项目/编 辑文件; (2)点“rebuild all”工具进行编译、汇编和 链接; (3)装载上一步生成的out文件; (4)运行后点“view/memory”观察运行结果。

stack

பைடு நூலகம்

table: start:

end:

• 4、思考题: (1)三个算式,其除法运算结果分别是多少? (2)仔细阅读主程序,分析.text段各条重要指 令的含义,阐述带符号数减法程序的基本编程 思路。 (2)阐述C54xDSP的小数是如何表示的?

• 3、整数除法程序参考例程:(小数除法程序参考教材P154)

.title "Ex_543.asm" .mmregs .usect "STACK", 10H .bssnum,1 .bssden,1 .bssquot,1 .def start .data .word 16384 .word -512 .text STM #0, SWWSR STM #stack+10H, SP STM #num, AR1 RPT #1 MVPD table, *AR1+ LD @den, 16, A MPYA @num ABS A STH A, @den LD ABS RPT SUBC XC NEG STL B .end @num, A A #15 @den, A 1, BLT A A, @quot end

DSP除法原理范文

DSP除法原理范文首先,我们需要明确的是,在数字信号处理器中,除法运算是通过位操作实现的,与通常的除法算法有所不同。

DSP除法利用了数值的二进制表示,通过移位和减法的操作来实现除法运算。

1.恒定除法:恒定除法是通过将除数乘以一个逆除数(reciprocal)来实现的,逆除数是将除数的倒数进行二进制表示的一个数。

将逆除数与被除数相乘,然后通过右移和减法操作来得到商和余数。

具体步骤如下:(1) 计算逆除数:逆除数可以通过使用牛顿拉夫逊(Newton-Raphson)迭代法来计算,或者通过查表的方式。

逆除数的精度决定了除法运算的精度。

(2) 将逆除数与被除数相乘:利用乘法器(multiplier)将逆除数与被除数进行乘法运算,得到一个中间结果。

(3)右移操作:将中间结果进行右移操作,使得其逐渐接近被除数。

(4)减法操作:将右移后的中间结果与被除数进行减法操作,得到商和余数。

恒定除法的优点是计算速度较快,并且可以通过查表的方式实现逆除数的计算。

缺点是对于高精度的除法运算,逆除数的计算会较为耗时。

2.非恒定除法:非恒定除法是通过将除数和被除数同时调整为一定的范围内进行除法运算。

具体步骤如下:(1)将除数和被除数进行位扩展:将除数和被除数进行左移或右移操作,使得二者的范围都在一定的范围内。

(2)通过左移或右移操作保持商的范围:根据除数和被除数的位扩展结果,相应地对商进行左移或右移操作。

这样可以保持商的大小范围。

(3)通过减法操作计算商:将被除数减去除数,并根据减法结果调整商的位。

(4)通过减法操作计算余数:将商和除数相乘,并将乘法结果减去被除数,得到余数。

非恒定除法的优点是可以适应不同的除数和被除数范围,并且精度较高。

缺点是计算速度较慢,需要多次移位和减法操作。

需要注意的是,DSP除法在实际应用中通常结合其他运算进行,如乘法、加法等,以实现更复杂的信号处理任务。

总而言之,DSP除法原理涉及到恒定和非恒定除法两种方法。

高精度除法运算的实现

本文所附程序用高级BASIC语言写成,在Super PC/24;A/B=?"

100 rst$ = rst$ + STR$(s)

110 NEXT i

120 PRINT STR$(a); "/"; STR$(b); "="; first$; "."; rst$

130 END

50 aa = a

55 s = INT(aa / b)

60 first$ = STR$(s)

70 FOR i = 1 TO n

80 aa = (aa - b * s) * 10

90 s = INT(aa / b)

20 INPUT "input A="; a

30 INPUT "input B="; b

35 INPUT "stop at :"; n

40 IF b = 0 THEN PRINT "error: divided by zero!": BEEP: GOTO 10

高精度除法运算的实现

蒲小勤

1994-03-18

笔者设计了一种算法,可以实现除法的高精度运算,理论上可精确到小数点后无限位。该算法突破了计算机中除法运算的一般概念,不是向计算机直接输入运算式,由计算机运算后得到结果,而是利用了计算机运算速度快的特点,用计算机模仿除法运算的实际步骤,先用被除数除以除数,得到一个整数商和一个余数,将整数商记录下来作为结果,将余数乘以10后作为下一步运算的被除数,继续运算,并往复循环。

DSP定点运算-Q格式

DSP芯片的定点运算---Q格式(转)2008-09-03 15:47DSP芯片的定点运算1.数据的溢出:1>溢出分类:上溢(overflow):下溢(underflow)2>溢出的结果:MaxMin上溢在圆圈上按数据逆时针移动;下溢在圆圈上顺时钟移动。

例:signed int :32767+1=-32768;-32768-1=32767unsigned char:255+1=0;0-1=2553>为了避免溢出的发生,一般在DSP中可以设置溢出保护功能。

当发生溢出时,自动将结果设置为最大值或最小值。

2.定点处理器对浮点数的处理:1>定义变量为浮点型(float,double),用C语言抹平定点处理器和浮点处理器的区别,但是程序的代码庞大,运算速度也慢。

2>放大若干倍表示小数。

比如要表示精度为0.01的变量,放大100倍去运算,运算完成后再转化。

但是这个做法比较僵硬,如要将上面的变量重新定义成0.001精度,又需要放大1000倍,且要重新编写整个程序,考虑溢出等问题。

3>定标法:Q格式:通过假定小数点位于哪一位的右侧,从而确定小数的精度。

Q0:小数点在第0位的后面,即我们一般采用的方法Q15 小数点在第15位的后面,0~14位都是小数位。

转化公式:Q=(int)(F×pow(2,q))F=(float)(Q×pow(2,-q))3.Q格式的运算1>定点加减法:须转换成相同的Q格式才能加减2>定点乘法:不同Q格式的数据相乘,相当于Q值相加3>定点除法:不同Q格式的数据相除,相当于Q值相减4>定点左移:左移相当于Q值增加5>定点右移:右移相当于Q减少4.Q格式的应用格式实际应用中,浮点运算大都时候都是既有整数部分,也有小数部分的。

所以要选择一个适当的定标格式才能更好的处理运算。

一般用如下两种方法:1>使用时使用适中的定标,既可以表示一定的整数复位也可以表示小数复位,如对于2812的32位系统,使用Q15格式,可表示-65536.0~65535.999969482区间内的数据。

一DSP定点算数运算 1 数的定标 在定点DSP芯片中,采用...

一DSP定点算数运算1 数的定标在定点DSP芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。

一个整型数的最大表示范围取决于DSP芯片所给定的字长,一般为16位或24位。

显然,字长越长,所能表示的数的范围越大,精度也越高。

如无特别说明,本书均以16位字长为例。

DSP芯片的数以2的补码形式表示。

每个16位数用一个符号位来表示数的正负,0表示数值为正,l则表示数值为负。

其余15位表示数值的大小。

因此,二进制数0010000000000011b=8195 二进制数1111111111111100b= -4 对DSP芯片而言,参与数值运算的数就是16位的整型数。

但在许多情况下,数学运算过程中的数不一定都是整数。

那么,DSP芯片是如何处理小数的呢?应该说,DSP芯片本身无能为力。

那么是不是说DSP芯片就不能处理各种小数呢?当然不是。

这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。

这就是数的定标。

通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。

数的定标有Q表示法和S表示法两种。

表1.1列出了一个16位数的16种Q表示、S表示及它们所能表示的十进制数值范围。

从表1.1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同。

例如,16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示但对于DSP芯片来说,处理方法是完全相同的。

从表1.1还可以看出,不同的Q所表示的数不仅范围不同,而且精度也不相同。

Q越大,数值范围越小,但精度越高;相反,Q越小,数值范围越大,但精度就越低。

例如,Q0 的数值范围是一32768到+32767,其精度为1,而Q15的数值范围为-1到0.9999695,精度为1/32768=0.00003051。

因此,对定点数而言,数值范围与精度是一对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想精度提高,则数的表示范围就相应地减小。

DSP 除法运算

实验六除法运算一、实验目的掌握除法运算的实现方法。

二、实验设备计算机、DSP 实验箱。

三、实验内容分别编写程序,实现计算0.4÷(-0.8)和16384÷512 的值。

四、实验步骤1、用仿真器将计算机与DSP 实验箱连接好,并依次打开实验箱电源、仿真器电源,然后运行CCS 软件。

2、新建一个项目:点击Project-New,将项目命名为zhao9f,并将项目保存在自己定义的文件夹下,注意文件夹一定要用英文名,不要将文件夹取名为中文名,因为CCS 软件不能识别以中文命名的文件夹。

3、新建一个源文件:点击File-New-Source File 可以打开一个文本编辑窗口,点击保存按键,保存在和项目相同的一个文件夹下面(zhao9f),保存类型选择*.ASM(如果源文件是C 语言编写的,保存类型选择*.C,本实验中的例程是使用汇编语言编写的,所以选择*.ASM为保存类型),我们在这里将保存名字命名为zhao9f.asm 。

4、在项目中添加源文件:在新建立了一个源文件以后,要想使用CCS 编译器对该源文件进行编译还需要将源文件添加到项目中去。

添加方法是在工程管理器中右键单击zhao9f.pjt,在弹出的菜单中选择Add Files,然后将刚才建立的zhao9f.asm 文件添加到该项目中去。

5、编写源程序:在工程管理器中双击zhao9f.asm ,将出现文本编辑窗口,在该文本编辑窗口中输入如下内容:********************************** |被除数|<|除数|,商为小数** 计算0.4÷(-0.8)的值**********************************.title "zhao9f.asm".mmregsSTACK .usect "STACK",10H.bss num,1 ;分子.bss den,1 ;分母.bss quot,1 ;商.datatable: .word 4*32768/10 ;-128.word -8*32768/10 ;1024.def _c_int00.text_c_int00: LD #1H,DP ;设置数据页指针,使DP 指向第1 页(80H 处)STM #num,AR1RPT #1MVPD table,*AR1+ ;传送2 个数据至分子、分母LD @den,16,A ;将分母移到累加器A(31~16)MPYA @num ;(num)*(A(31~16))->B,获取商的符号;(在累加器B 中)ABS A ;分母取绝对值STH A,@den ;分母取绝对值存回原处LD @num,16,A ;将分子移到累加器A(32~16)ABS A ;分子取绝对值RPT #14 ;15次减法循环,完成除法SUBC @den,AXC 1,BLT ;如果B<0(商为负数),则需要变号NEG ASTL A,@quot ;保存商end: B end.end6、编写链接配置文件:参照实验一,需要更改的地方如下:7、编写中断向量表文件参照实验一,可不作修改。

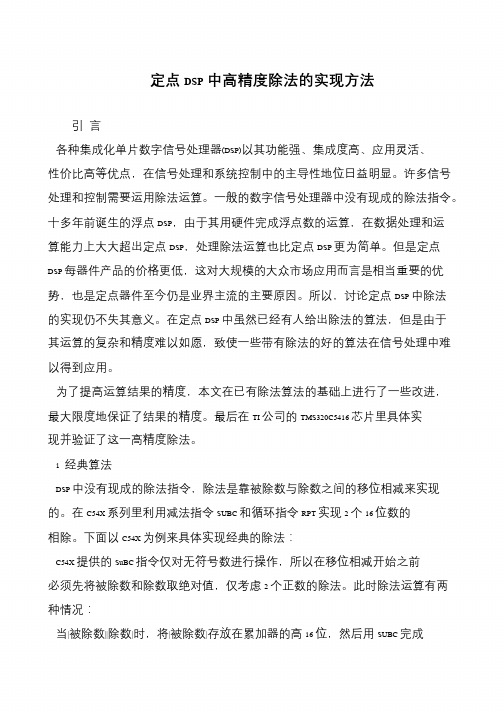

定点DSP中高精度除法的实现方法

定点DSP中高精度除法的实现方法

引言

各种集成化单片数字信号处理器(DSP)以其功能强、集成度高、应用灵活、

性价比高等优点,在信号处理和系统控制中的主导性地位日益明显。

许多信号处理和控制需要运用除法运算。

一般的数字信号处理器中没有现成的除法指令。

十多年前诞生的浮点DSP,由于其用硬件完成浮点数的运算,在数据处理和运算能力上大大超出定点DSP,处理除法运算也比定点DSP 更为简单。

但是定点DSP 每器件产品的价格更低,这对大规模的大众市场应用而言是相当重要的优势,也是定点器件至今仍是业界主流的主要原因。

所以,讨论定点DSP 中除法的实现仍不失其意义。

在定点DSP 中虽然已经有人给出除法的算法,但是由于其运算的复杂和精度难以如愿,致使一些带有除法的好的算法在信号处理中难以得到应用。

为了提高运算结果的精度,本文在已有除法算法的基础上进行了一些改进,最大限度地保证了结果的精度。

最后在TI 公司的TMS320C5416 芯片里具体实现并验证了这一高精度除法。

1 经典算法

DSP 中没有现成的除法指令,除法是靠被除数与除数之间的移位相减来实现的。

在C54X 系列里利用减法指令SUBC 和循环指令RPT 实现2 个16 位数的相除。

下面以C54X 为例来具体实现经典的除法:

C54X 提供的SuBC 指令仅对无符号数进行操作,所以在移位相减开始之前必须先将被除数和除数取绝对值,仅考虑2 个正数的除法。

此时除法运算有两种情况:

当|被除数||除数|时,将|被除数|存放在累加器的高16 位,然后用SUBC 完成。

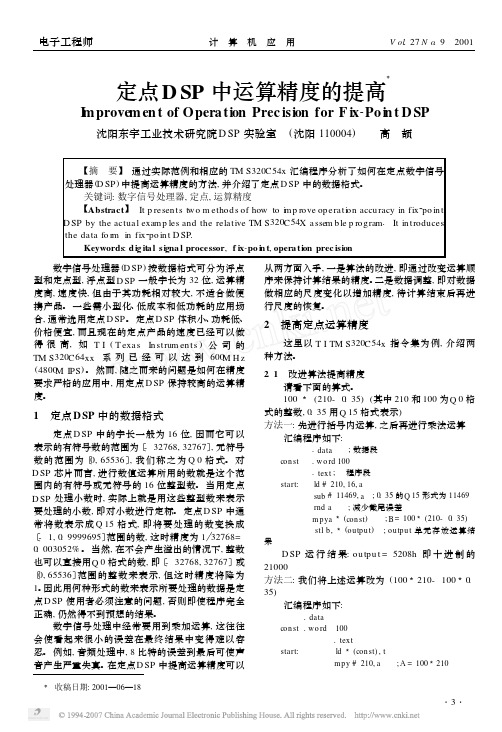

定点DSP中运算精度的提高

定点D SP中运算精度的提高ΞI m provem en t of Operation Prec ision for F ix-Po i n t D SP沈阳东宇工业技术研究院D SP实验室 (沈阳110004) 高 颉 【摘 要】 通过实际范例和相应的TM S320C54x汇编程序分析了如何在定点数字信号处理器(D SP)中提高运算精度的方法,并介绍了定点D SP中的数据格式。

关键词:数字信号处理器,定点,运算精度【Abstract】 It p resen ts tw o m ethods of how to i m p rove op erati on accu racy in fix2po in t D SP by the actual exam p les and the relative TM S320C54X assem b le p rogram.It in troduces the data fo rm in fix2po in t D SP.Keywords:d ig ita l signa l processor,f ix-po i n t,opera tion prec ision 数字信号处理器(D SP)按数据格式可分为浮点型和定点型,浮点型D SP一般字长为32位,运算精度高,速度快,但由于其功耗相对较大,不适合做便携产品。

一些需小型化、低成本和低功耗的应用场合,通常选用定点D SP。

定点D SP体积小、功耗低、价格便宜,而且现在的定点产品的速度已经可以做得很高,如T I(T exas In strum en ts)公司的TM S320C64xx系列已经可以达到600M H z (4800M IPS)。

然而,随之而来的问题是如何在精度要求严格的应用中,用定点D SP保持较高的运算精度。

1 定点D SP中的数据格式定点D SP中的字长一般为16位,因而它可以表示的有符号数的范围为〔-32768,32767〕,无符号数的范围为〔0,65536〕,我们称之为Q0格式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

万方数据

万方数据

万方数据

定点DSP中高精度除法的实现方法

作者:刘洪鸣, 邱建辉, 邱奕文, Liu Hongming, Qui Jianhui, Qiu Yiwen

作者单位:刘洪鸣,Liu Hongming(武警杭州指挥学院), 邱建辉,Qui Jianhui(杭州电子科技大学),邱奕文,Qiu Yiwen(杭州萧山国际机场)

刊名:

单片机与嵌入式系统应用

英文刊名:MICROCONTROLLERS & EMBEDDED SYSTEMS

年,卷(期):2009(1)

被引用次数:2次

1.戴明桢;周建江TMS320C54X DSP结构、原理及应用 2001

2.石元君定点DSP除法原理及其TMS320C6000实现[期刊论文]-单片机与嵌入式系统应用 2002(10)

3.Texas Instruments TMS320C54x DSP Reference Set Volume 2:Mnemonic Instruction Set (SPRU172B)

4.张雄伟DSP芯片的原理与开发应用 2003

5.酆勇;李阳;李方伟基于DSP的视频编码的优化和实现[期刊论文]-电子工程师 2002(10)

1.丁电宽.万毅.DING Dian-kuan.WAN Yi除法运算在定点DSP中的实现[期刊论文]-安阳师范学院学报2006(2)

2.王华.汶德胜.Wang,Hua.Wen,Desheng浮点除法运算在TMS320C3X DSP中的实现[期刊论文]-微计算机信息2005,21(23)

3.田华快速浮点除法运算及其在单片机上的实现[期刊论文]-陕西师范大学学报(自然科学版)2004,32(2)

1.黄李国基于TMS320LF2407A的32位除法算法研究[期刊论文]-科技信息 2010(15)

2.陈晟.杨津骁.张洪华基于DSP的水下目标模拟器[期刊论文]-舰船科学技术 2011(11)

引用本文格式:刘洪鸣.邱建辉.邱奕文.Liu Hongming.Qui Jianhui.Qiu Yiwen定点DSP中高精度除法的实现方法[期刊论文]-单片机与嵌入式系统应用 2009(1)。