杭电计组实验一二三

计算机组成原理实验(接线、实验步骤)

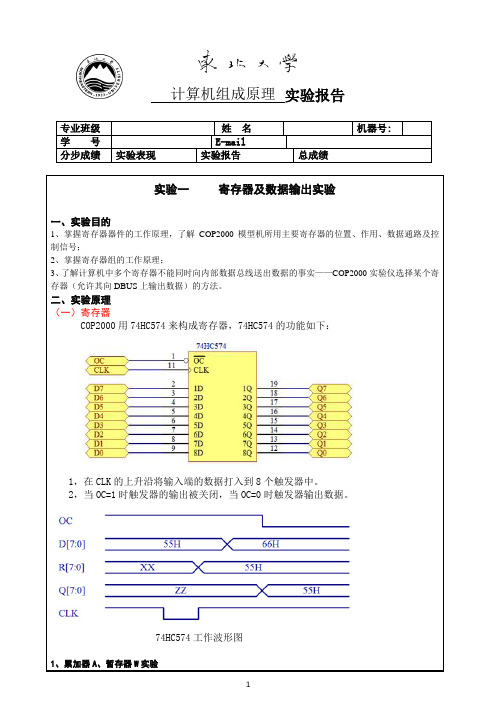

计算机组成原理实验(接线、实验步骤)实验⼀运算器[实验⽬的]1.掌握算术逻辑运算加、减、乘、与的⼯作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]⼀、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输⼊10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输⼊10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显⽰灯的显⽰与进位结果C的显⽰)6.改变S2S1S0的值,对同⼀组数做不同的运算,观察显⽰灯的结果。

⼆、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执⾏不同的运算[思考]M1、M2控制信号的作⽤是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输⼊时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验⼆双端⼝存储器[实验⽬的]1.了解双端⼝存储器的读写;2.了解双端⼝存储器的读写并⾏读写及产⽣冲突的情况。

杭电计组实验报告10

计组实验十老师:包健一、源代码测试模块代码:module Top(inputinclk,inputmem_clk,inputrst,outputreg[7:0] LED,input [3:0] SW);wireclk;MyButtonmb(.clk_100MHz(mem_clk),.BTN(inclk),.BTN_Out(clk));wire [31:0] ALU_F;wire [31:0] M_R_Data;wire ZF;wire OF;wire [31:0]PC;My_I_CPUmy_i_cpu(.clk(clk),.mem_clk(mem_clk),.rst(rst),.ALU_F(ALU_F),.M_R_Data(M_R_Data),.ZFF(ZF),.OF(OF),.PC_out(PC));always@(*)begincase(SW)4'd0:LED=ALU_F[7:0];4'd1:LED=ALU_F[15:8];4'd2:LED=ALU_F[23:16];4'd3:LED=ALU_F[31:24];4'd4:LED=M_R_Data[7:0];4'd5:LED=M_R_Data[15:8];4'd6:LED=M_R_Data[23:16];4'd7:LED=M_R_Data[31:24];4'd8:LED={ZF,6'd0,OF};4'd12:LED=PC[7:0];4'd13:LED=PC[15:8];4'd14:LED=PC[23:16];4'd15:LED=PC[31:24];default:LED=8'b0000_0000;endcaseendendmodule顶层模块代码:moduleMy_I_CPU(inputclk,inputmem_clk,inputrst,output [31:0] ALU_F,output [31:0] M_R_Data,output ZFF,output OF,output [31:0]PC_out);//wire clk_n = ~clk;wire[31:0] codes;wire [31:0]PC_new;reg [31:0]PC;Inst_Fetch1 inst_fetch(.PC(PC),.rst(rst),.clk(clk),.Inst_codes(codes),.PC_new(PC_new));wire[5:0] OP;wire[5:0] func;wire ZF;assign ZFF=ZF;assignPC_out=PC;wire [1:0]w_r_s;wireimm_s;wirert_imm_s;wire [1:0]wr_data_s;wire[2:0] ALU_OP; wireWrite_Reg;wireMem_Write;wire [1:0]PC_s;wire [15:0] imm;wire [31:0] imm_data ; wire [25:0] address;assign OP = codes[31:26]; assignfunc = codes[5:0]; assignimm = codes[15:0]; assign address=codes[25:0];OP_Decoderop_decoder( .OP(OP),//input.func(func),.ZF(ZF),//input.w_r_s(w_r_s),.imm_s(imm_s),.rt_imm_s(rt_imm_s),.wr_data_s(wr_data_s),.ALU_OP(ALU_OP),.Write_Reg(Write_Reg),.Mem_Write(Mem_Write), .PC_s(PC_s));wire[4:0] rs;wire[4:0] rt;wire[4:0] rd;assignrs = codes[25:21]; assignrt = codes[20:16]; assignrd = codes[15:11];wire[4:0] W_Addr;wire [31:0]W_Data;wire [31:0]ALU_B;assign W_Addr=(w_r_s[1])?5'b11111:((w_r_s[0])?rt:rd);assign W_Data=(wr_data_s[1])?PC_new:((wr_data_s[0])?M_R_Data:ALU_F); assign imm_data = (imm_s)?{{16{imm[15]}},imm}:{{16{1'b0}},imm}; assign ALU_B =(rt_imm_s)?imm_data:R_Data_B;always@(*)begincase(PC_s)2'b00:PC=PC_new;2'b01:PC=R_Data_A;2'b10:PC=PC_new+(imm_data<<2);2'b11:PC={PC_new[31:28],address,2'b00};default:PC=PC_new;endcaseendwire [31:0]R_Data_A;wire [31:0]R_Data_B;RegisterHeapregister(.R_Addr_A(rs),.R_Addr_B(rt),.W_Addr(W_Addr),.Write_Reg(Write_Reg),.Reset(rst),.Clk(clk),.W_Data(W_Data),.R_Data_A(R_Data_A),.R_Data_B(R_Data_B));wire [31:0]ALU_A;assign ALU_A = R_Data_A;ALU alu(.ALU_OP(ALU_OP),.A(ALU_A),.B(ALU_B),.F(ALU_F),.ZF(ZF),.OF(OF));Data_Memdata_mem (.clka(mem_clk), // input clka.wea(Mem_Write), // input [0 : 0] wea.addra(ALU_F[5:0]), // input [5 : 0] addra.dina(R_Data_B), // input [31 : 0] dina.douta(M_R_Data) // output [31 : 0] douta);Endmodule二、仿真波形三、电路图四、引脚配置:NET "LED[7]" LOC = "T11";NET "LED[6]" LOC = "R11";NET "LED[5]" LOC = "N11";NET "LED[4]" LOC = "M11";NET "LED[3]" LOC = "V15";NET "LED[2]" LOC = "U15";NET "LED[1]" LOC = "V16";NET "LED[0]" LOC = "U16";//LEDNET "inclk" LOC = "C9";NET "mem_clk" LOC = "V10";//100mHZNET "SW[3]" LOC = "M8";// 右边4个开关NET "SW[2]" LOC = "V9";NET "SW[1]" LOC = "T9";NET "SW[0]" LOC = "T10";NET "rst" LOC = "D9";五、思考与探索1,经过汇编器汇编即可产生程序的机器码。

杭电计组实验3-多功能ALU设计实验

杭电计组实验3-多功能ALU设计实验杭州电子科技大学计算机学院实验报告实验项目:课程名称:计算机组成原理与系统结构课程设计姓名: 学号: 同组姓名: 学号: 实验位置(机号):实验日期: 指导教师:一、实验目的(1)学习多功能ALU的工作原理,掌握运算器的设计方法。

(2)掌握运用Verilog HDL进行数据流描述与建模的技巧和方法,掌握运算器的设计方法。

二、实验仪器实验 ISE工具软件内容三、步骤、方法(算(1)启动Xilinx ISE软件,选择File->New Project,输入工程名shiyan2,默认选择后,点法、击Next按钮,确认工程信息后点击Finish按钮,创建一个完整的工程。

程(2)在工程管理区的任意位置右击,选择New Source命令。

弹出New Source Wizard对序、话框,选择Verilog Module,并输入Verilog 文件名shiyan3,点击Next按钮进入下一步,点步骤击Finish完成创建。

和方(3)编辑程序源代码,然后编译,综合;选择Synthesize--XST项中的Check Syntax右击法) 选择Run命令,并查看RTL视图;如果编译出错,则需要修改程序代码,直至正确。

(4)在工程管理区将View类型设置成Simulation,在任意位置右击,选择New Source命令,选择Verilog Test Fixture选项,输入实验名shiyan3_test。

点击Next,点击Finish,完成。

编写激励代码,观察仿真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。

(5)由于实验三并未链接实验板,所以后面的链接实验板的步骤此处没有。

一,操作过程实验过程和描述:module shiyan3(ALU_OP,AB_SW,OF,ZF,F);reg [31:0]A,B;input [2:0]ALU_OP;input [2:0]AB_SW;操作 wire OF;过程 reg ZF;及结reg [31:0]F;果 output OF;output ZF;output F;reg C32;always@(*)begincase(AB_SW)3'b000: begin A=32'h0000_0000; B=32'h0000_0000; end3'b001: begin A=32'h0000_0003; B=32'h0000_0607; end3'b010: begin A=32'h8000_0000; B=32'h8000_0000; end3'b011: begin A=32'h7FFF_FFFF; B=32'h7FFF_FFFF; end3'b100: begin A=32'hFFFF_FFFF; B=32'hFFFF_FFFF; end3'b101: begin A=32'h8000_0000; B=32'hFFFF_FFFF; end3'b110: begin A=32'hFFFF_FFFF; B=32'h8000_0000; end3'b111: begin A=32'h1234_5678; B=32'h3333_2222; enddefault: begin A=32'h9ABC_DEF0; B=32'h1111_2222; endendcaseendalways@(*)begincase(ALU_OP)3'b000: F<=A&B;3'b001: F<=A|B;3'b010: F<=A^B;3'b011: F<=A~^B;3'b100: {C32,F}<=A+B;3'b101: {C32,F}<=A-B;3'b110: begin if(A<B) F<=32'h0000_0001; else F<=32'h0000_0000; end 3'b111: begin F<=B<<A; enddefault: F<=32'h0000_0000;endcaseendalways@(*)beginif(F===32'h0000_0000)ZF<=1;elseZF<=0;endassign OF=C32^F[31]^A[31]^B[31]; endmodule仿真代码module shiyan3_test;// Inputsreg [2:0] ALU_OP;reg [2:0] AB_SW;// Outputswire OF;wire ZF;wire [31:0] F;// Instantiate the Unit Under Test (UUT) shiyan3 uut (.ALU_OP(ALU_OP),.AB_SW(AB_SW),.OF(OF),.ZF(ZF),.F(F));initial begin// Initialize InputsALU_OP = 0;AB_SW = 0;// Wait 100 ns for global reset to finish #100;// Add stimulus here #100;ALU_OP = 001;AB_SW = 001; #100;ALU_OP = 010;AB_SW = 010; #100;ALU_OP = 011;AB_SW = 011; #100;ALU_OP = 100;AB_SW = 100; #100;ALU_OP = 101;AB_SW = 101; #100;ALU_OP = 110;AB_SW = 110; #100;ALU_OP = 111;AB_SW = 111;end endmodule RTL图二、结果思考题:(2)经过分析,该ALU不能实现MIPS核心指令集的所有指令。

杭电计组实验四

0000_0003

$00011

7FFF_FFFF

7FFF_FFFF

$00111

7FFF_FFFF

7FFF_FFFF

$01111

0000_0000

0000_0000

$11111

000ቤተ መጻሕፍቲ ባይዱ_0003

0000_0003

$10000

7FFF_FFFF

7FFF_FFFF

$11000

7FFF_FFFF

input [4:0] W_Addr;

input [31:0] W_Data;

input Write_Reg;

input Clk;

input Reset;

output [31:0] R_Data_A;

output [31:0] R_Data_B;

integer i;

reg[31:0] REG_Files[31:0];//定义寄存器

实验报告

2016年4月22日成绩:

姓名

学号

班级

专业

信息安全

课程名称

《计算机组成原理课程设计》

任课老师

曾虹

指导老师

曾虹

机位号

实验序号

实验名称

寄存器堆

实验时间

2016、4、22

实验地点

1教南

实验设备号

一、实验程序源代码

module Reg(LED,RW_SW,AB,Reg_Addr_A,Reg_Addr_B,Write_Reg,clk,rst);

NET "Add[3]" LOC = "V8";

NET "Add[2]" LOC = "U8";

杭电计组实验-存储器设计实验

杭电计组实验-存储器设计实验————————————————————————————————作者:————————————————————————————————日期:实验报告2018 年 5 月 5 日成绩:姓名阳光男学号16041321 班级16052317专业计算机科学与技术课程名称《计算机组成原理与系统结构试验》任课老师张翔老师指导老师张翔老师机位号默认实验序号5实验名称《实验五存储器设计实验》实验时间2018/5/12实验地点1教211实验设备号个人电脑、Nexys3开发板一、实验程序源代码存储器顶层电路代码:module top_RAM_B(Mem_Addr,C,Mem_Write,Clk,LED);input [7:2]Mem_Addr;//开关的3、4、5、6、7、8位input Mem_Write,Clk;//clk为按键C9,读写使能信号为按键C4,0为读,1为写input [1:0]C;//选择写入数据+读操作时选择显示字节,为开关1、2位output reg [7:0]LED;wire [31:0]M_R_Data;//存在存储器里的32位读出数据reg [31:0]M_W_Data;//寄存在暂存器的32位写入数据RAM_B test_ram (.clka(Clk), //输入时钟信号.wea(Mem_Write), //输入读写信号.addra(Mem_Addr[7:2]), //输入5位地址信号.dina(M_W_Data), //写入32位数据.douta(M_R_Data) //读出32位数据);always@(*)beginLED=0;//初始化M_W_Data=0;//初始化if(!Mem_Write)//读操作begincase(C)2'b00:LED=M_R_Data[7:0];//读出数据的0-7位2'b01:LED=M_R_Data[15:8];//读出数据的8-15位2'b10:LED=M_R_Data[23:16];//读出数据的16-23位2'b11:LED=M_R_Data[31:24];//读出数据的24-31位endcaseendelsebegincase(C)2'b00:M_W_Data=32'h0055_7523;//写入第一个数据2'b01:M_W_Data=32'h1234_5678;//写入第二个数据2'b10:M_W_Data=32'h8765_4321;//写入第三个数据2'b11:M_W_Data=32'hffff_ffff;//写入第四个数据endcaseendendendmodule测试代码:module test;// Inputsreg clka;reg [0:0] wea;reg [5:0] addra;reg [31:0] dina;// Outputswire [31:0] douta;// Instantiate the Unit Under Test (UUT)RAM_B uut (.clka(clka),.wea(wea),.addra(addra),.dina(dina),.douta(douta));initial begin// Initialize Inputsclka = 0;wea = 0;addra = 0;dina = 0;// Wait 100 ns for global reset to finish #100;// Add stimulus hereclka = 1;wea = 0;addra = 6'b000001;dina = 32'h0000_0003;#100;clka = 0;wea = 0;addra = 6'b000001;dina = 32'h0000_0607;#100;clka = 1;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;#100;clka = 0;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;endendmodule二、仿真波形三、电路图顶层电路模块顶层电路内部结构:四、引脚配置(约束文件)NET "Clk" LOC = C9;NET "LED[4]" LOC = M11;NET "LED[3]" LOC = V15;NET "LED[2]" LOC = U15;NET "LED[1]" LOC = V16;NET "LED[0]" LOC = U16;NET "Mem_Addr[7]" LOC = U8;NET "Mem_Addr[6]" LOC = N8;NET "Mem_Addr[5]" LOC = M8;NET "Mem_Addr[4]" LOC = V9;NET "Mem_Addr[2]" LOC = T10;NET "Mem_Write" LOC = C4;NET "Mem_Addr[3]" LOC = T9;NET "C[1]" LOC = T5;NET "C[0]" LOC = V8;NET "LED[7]" LOC = T11;NET "LED[5]" LOC = N11;NET "LED[6]" LOC = R11;五、思考与探索(1)读操作实验结果记录表存储器地址初始化数据读出数据写入新数据读出数据5’b000000 32’b0000000032’b0000000032'h0055_752332'h0055_7523 5’b000001 32’b0000000132’b0000000132'h0055_752332'h0055_7523 5’b000002 32’b0000000232’b0000000232'h0055_752332'h0055_7523 5’b000003 32’b0000000332’b0000000332'h0055_752332'h0055_7523 5’b000004 32’b0000000432’b0000000432'h0055_752332'h0055_7523 5’b000005 32’b0000000532’b0000000532'h0055_752332'h0055_7523 5’b000006 32’b0000000632’b0000000632'h0055_752332'h0055_7523 5’b000007 32’b0000000732’b0000000732'h0055_752332'h0055_7523 (2)答:这些单元的数据已经被改写了。

杭电过程控制实验报告

过程控制实验报告班级:组号:组员:年月日实验一、水箱液位定值控制实验一、实验目的1、通过实验熟悉单回路反馈控制系统的组成和工作原理。

2、分析分别用P、PI和PID调节时的过程图形曲线。

3、定性地研究P、PI和PID调节器的参数对系统性能的影响。

二、面板位图与实验电气连接图1、实验面板位图实验面板位图如图1-1,图1-2,图1-3所示图1-1、传感器执行器位图图1-2、电源面板位图2、实验电气接线图3、实验信号实物连接图图1-5、实验信号实物连接图三、实验原理图1-6、实验控制框图1-6为单回路水箱液位控制系统,单回路调节系统一般指在一个调节对象上用一个调节器来保持一个参数的恒定,而调节器只接受一个测量信号,其输出也只控制一个执行机构。

本系统所要保持的恒定参数是液位的给定高度,即控制的任务是控制上水箱液位等于给定值所要求的高度。

根据控制框图,这是一个闭环反馈单回路液位控制,采用工业智能仪表控制。

当调节方案确定之后,接下来就是整定调节器的参数,一个单回路系统设计安装就绪之后,控制质量的好坏与控制器参数选择有着很大的关系。

合适的控制参数,可以带来满意的控制效果。

反之,控制器参数选择得不合适,则会使控制质量变坏,达不到预期效果。

因此当一个单回路控制系统组成好以后,如何整定好控制器的参数是一个很重要的实际问题。

一个控制系统设计好以后,系统的投运和参数整定是十分重要的工作。

四、实验内容和步骤1、系统连线(1)将系统的所有电源开关打在关的位置。

(2)按照实验电气图将系统接好2、仪表操作按照实验手册设置相应参数:主要包括Inp 33;SCL 0 ; SCH 650.03、启动实验装置4、实验内容(一)比例调节(P)控制(1)启动计算机MCGS软件,进入实验系统选择水箱液位定值控制实验(2)按下水泵1启动按钮,启动水泵1,进行实验。

(3)设定给定值30,设置P(20)参数,将I(9999)参数设置为最大值,D参数设置为0,观察屏幕上的曲线,待被调参数基本稳定于给定值后,可以开始加干扰实验。

杭电计算机组成原理MIPS汇编器模拟器实验6

sltu $2,$0,$1;#$2=0000_0001

add $3,$2,$2;#$3=0000_0002

add $4,$3,$2;#$4=0000_0003

add $5,$4,$3;#$5=0000_0005

add $6,$5,$3;#$6=0000_0007

(3ቤተ መጻሕፍቲ ባይዱ了解使用MIPS教学系统模拟器运行程序的方法

实验环境

PCSpim模拟器

实验内容(算法、程序、步骤和方法)

1.使用记事本编辑.asm文件,输入内容

2.运行PCSpim程序,在七分钟打开asm文件,先连续执行,输入地址0X0040000,在单步执行,按照需要在控制条输入2个数据,观察结果。

3.按照之前的步骤执行,输入指令,单步执行,记录。

add $29,$22,$2;#$29=8000_0000

sub $30,$20,$2;#$30=7FFF_FFFF

add $31,$11,$26;#$30=9000_6FF1

(接上)

实验内容(算法、程序、步骤和方法)

结论(结果)

利用断点的思想,对于学习编程的人断点可能是最熟悉不过的东西,断点下个各个变量值的变化,汇编语言不是太熟悉,大概的看的懂一点

试验心得与小结

跟着单步执行,看看结果。断点设计跟踪,熟悉各种变化之间的关系,这才我此次实验的最大的收获。

指导教师

评议

成绩评定:指导教师签名:

sub $24,$20,$22;#$24=0000_0001

sub $25,$22,$20;#$25=FFFF_FFFF

xor $26,$18,$1;#$26=8FFF_FFFF

杭电数电实验课内题设计答案

数字逻辑电路课内仿真实验第六章Quartusll 原理图设计初步二、实验仪器: Quartusll 软件。

三、实验内容:6-1用Quartusll 库中的宏功能模块 74138和与非门实现指定逻辑函数按照6.3节和6.4节的流程,使用 Quartusll 完整图6-2电路的设计,包括:创建工程, 在原理图编辑窗中绘制此电路, 全程编译,对设计进行时序仿真, 根据仿真波形说明此电路一、实验目的: 初步了解学习使用 Quartusll 软件进行电路自动化设计。

的功能,引脚锁定编译,编程下载于FPGA 中进行硬件测试。

最后完成实验报告。

1、原理图 両诬YDN A V1M ftv?NlCY 酬 G1 T4IM <?£AhY 州G 比hve'i^N0~、r冋幅亍 —j — ................ _y p -' :n :tl; ......................■■ .!・■ ■・[・・—・・・・UI •■■I■!■■且■ b 0 b J …J k ■ L J …―年1 一… ■ - ■ -p - pJ ip k ■ L JFN W ・・I HN 91… I PPJ 49I....… gk 八却拽:f=>E|| II- !■ i|E qi 1|1 ^1 1|1, JI 1|1 :JI 1|1 i_.i !■■_ i IIB -II iih.-i |ih»M^ii Liiqii i;=iqii l^iRn ■^■Rn审厂 恥1"=il2 T|H_3 刊毗J 刊口=1 匸10 吨112、 波形设置M^AIrimEdAT 皿rjs& 科B n* 1 [■遶 * L-r p. > ■-i h' M7 :to5 F B V 4Z3Si 出EwJ I弓舞"5 平“ 15 単“;[> 弩":*“30 号"呼"4竽 E «^竽"mq- 36 字“也4 366 呼 6鬥5 ra3、仿真波形rlKi.It WirMl¥iuFF4位二进制数值比较器 7485串联扩展为8位比较器,使用Quartusll 完成全部设 计和测试,包括创建工程、编辑电路图、全程编译、时序仿真及说明此电路的功能、弓I 脚锁 定、编程下载,进行硬件测试。

杭电数电试验课内题设计答案

数字逻辑电路课内仿真实验第六章Quartusll原理图设计初步一、实验目的:初步了解学习使用Quartus||软件进行电路自动化设计。

二、实验仪器:Quartus||软件。

三、实验内容:6-1用Quartus||库中的宏功能模块74138和与非门实现指定逻辑函数按照6.3节和6.4节的流程,使用Quartus||完整图6-2电路的设计,包括:创建工程,在原理图编辑窗中绘制此电路,全程编译,对设计进行时序仿真,根据仿真波形说明此电路的功能,引脚锁定编译,编程下载于FPGA中进行硬件测试。

最后完成实验报告。

riruEUiioisn -t Z3E£m Zi64 丄21:EPtD.Zfc IT15 3E STS E-5 & 口a.IDFT5 ra3、仿真波形6-2用两片7485设计一个8位比较器用两片4位二进制数值比较器7485串联扩展为8位比较器,使用Quartus||完成全部设计和测试,包括创建工程、编辑电路图、全程编译、时序仿真及说明此电路的功能、弓I脚锁定、编程下载,进行硬件测试。

最后完成实验报告。

1、原理图2、波形设置3、波形仿真6-3设计8位串行进位加法器首先根据图4-33,用半加器设计一个全加器元件,然后根据图4-34,在顶层设计中用8个1位全加器构成8位串行进位加法器。

给出时序仿真波形并说明之,引脚锁定编译,编程下载于FPGA中进行硬件测试,最后完成实验报告,讨论这个加法器的工作速度。

1、原理图:半加器1位全加器8位串行进位全加器集成后的8位串行进位全加器2、波形设置3、波形仿真6-5设计一个十六进制7段显示译码器用Verilog的case语句设计一个可以控制显示共阴7段数码管的十六进制码7段显示译码器。

首先给出此译码器的真值表,此译码器有4个输入端:D、C B、A。

D是最高位,A是最低位;输出有8位:p、g、f、e、d、c、b、a,其中p和a分别是最高和最低位,p控制小数点。

杭电 计算机网络实验报告

目录实验一、使用数据拷贝线组网 (2)实验二、制作直通双绞线组网 (5)实验三、制作交叉双绞线组网 (8)实验四、Cisco IOS基本使用 (10)实验五、交换机基本使用 (14)实验六、VLAN的使用 (18)实验七、路由器的基本使用 (25)实验八、动态路由配置 (30)实验一、使用数据拷贝线组网实验一使用数据拷贝线组网实验台号:实验时间:实验小组号:成员及本次实验分工:实验目的:学会使用并行电缆(数据拷贝线)实现双机通信和资源共享。

使用直接电缆实现两台PC机之间的通信。

实验环境说明:硬件:2台计算机、2-3根并行电缆软件:Windows XP操作系统实验过程及步骤(可另附页、使用网络拓扑图等辅助说明):(1)、使用并行电缆将两台PC机,进行物理互连;(2)、分别在两台PC机上的网上邻居中创建一个新连接。

按照新建连接向导的指示来做。

首先网络连接类型选为“设置高级连接”;然后其中作为服务器的那台PC机创建为“接受传入的连接”,作为客户机的则创建为“直接连接到其他计算机的连接”,并让此计算机担任“来宾”的角色。

接下去根据向导直至完成创建新连接。

(3)、测试两机的可通用性。

创建好连接之后可以用ping命令测试一下两台机器之间是否已经连通。

(4)、连接创建成功之后,客户机可以找到并登入到服务器,就可以实现对服务器上的资源的共享了。

当然在此之前作为服务器的主机还需要将文件夹属性设置成为可共享的。

测试数据线连接以后Ping对方说明能够Ping通在一台PC上设置共享,然后在另外一台PC上查看共享截图如下:说明通过数据拷贝线成功地连接了两台PC,实现了他们之间的通信。

实验总结(遇到的问题及解决办法、体会):刚开始配置客户机的时候出了点问题。

需要输入对方计算机的名字,我们却输入了服务器上的计算机用户的帐号,所以一直没有连接成功。

后来终于发现了这个问题。

配置也就顺利了。

实验器材、工具领用及归还负责人:验收人:实验执笔人:实验记录人:报告协助人:实验报告完成时间:2010-4-28小组成员签名:指导教师评议成绩评定:指导教师签名:实验二、制作直通双绞线组网实验二制作直通双绞线组网实验台号:实验时间:实验小组号:成员及本次实验分工:实验目的:1.了解双绞线的相关知识;2.学会制作直通双绞线;3.掌握用双绞线实现集线器和计算机之间的互连。

杭电实验报告模版

一、实验模块实验名称:____________________实验课程:____________________实验时间:____________________实验地点:____________________实验人员:____________________二、实验标题____________________三、实验目的1. 了解____________________2. 掌握____________________3. 培养____________________四、实验原理____________________五、实验仪器与设备1. 仪器名称:____________________2. 仪器型号:____________________3. 仪器规格:____________________4. 其他设备:____________________六、实验步骤1. 实验步骤一:(1)____________________(2)____________________(3)____________________2. 实验步骤二:(1)____________________(2)____________________(3)____________________3. 实验步骤三:(1)____________________(2)____________________(3)____________________(注:根据实际实验内容,添加相应步骤)七、实验过程1. 实验过程一:(1)____________________(2)____________________(3)____________________2. 实验过程二:(1)____________________(2)____________________(3)____________________3. 实验过程三:(1)____________________(2)____________________(3)____________________(注:根据实际实验内容,添加相应过程)八、实验数据记录与分析1. 实验数据记录:(注:根据实际实验内容,添加数据记录表格)2. 实验数据分析:(注:根据实际实验内容,对实验数据进行分析)九、实验结论1. 实验结果:(1)____________________(2)____________________(3)____________________2. 实验结论:(1)____________________(2)____________________(3)____________________十、实验讨论1. 实验中遇到的问题及解决方法:(1)____________________(2)____________________(3)____________________2. 实验改进建议:(1)____________________(2)____________________(3)____________________十一、实验总结通过本次实验,我了解了____________________,掌握了____________________,培养了____________________。

HDU杭电单片机技术与应用实验指导书

单片机技术与应用实验指导书王俊宏周洪波暨仲明编杭州电子科技大学自动化学院二零零五年十月目录第一章系统安装和启动 (1)第二章调试软件LCA51界面介绍 (2)1.主界面 (2)2.菜单介绍................................................................................................................ 错误!未定义书签。

3.热键表. (11)第三章LCA51软件调试 (12)1.调试界面 (12)2.调试主要方法和技巧 (13)实验一扩展存储器读写实验 (15)实验二P1口、P3口输入、输出实验 (17)实验三定时器实验 (20)实验四外部中断实验(急救车与交通灯) (22)实验五8279显示实验................................................................................................. 错误!未定义书签。

实验六8255扫描键盘、显示实验 (24)实验七D/A和A/D转换实验 (27)实验八步进电机控制实验 (31)实验九压力测量显示实验.......................................................................................... 错误!未定义书签。

实验十单片机串行口与PC机通讯实验 (34)第一章系统安装和启动1.实验系统工作在51串口实验/仿真方式(1)实验台上开关选择51(2)打开电源,在PC机上打开LCA51软件,运行实验程序。

2.实验系统工作在MCS51方式下开关初始状态●XB、XB1 : 短路套全插上。

●XB2,XB5 : 短路套向上插(SPEAK端),第10模块处于放音功能。

●第○4模块中:多位开关K3拨向最左(温度控制)端,做温度控制实验用。

计组第一次实验报告总结

(1) R?的写入

写入R0:

置数据:

K23

K22

K21

K20

K19

K18

K17

K16

0

1

0

1

0

1

0

1

置控制信号:

K11(RRD)

K10(RWR)

K1(SB)

K0(SA)

1

0

0

0

给出CLOCK脉冲上升沿。

写入R1:

置数据:

K23

K22

K21

K20

K19

K18

K17

K16

0

1

0

1

0

1

0

1

置控制信号:

2、µPC预置数据实验

用二进制开关K23~K16将数据送到数据总线(DBUS),置数据??H

K23

K22

K21

K20

K19

K18

K17

K16

0

1

0

1

0

1

0

1

设置控制信号为:

K3(EMRD)

K2(EMWR)

K1(EMEN)

K0(IREN)

0

1

0

0

按住CLOCK键,CLOCK由高变低,这时µPC的黄色预置指示灯亮,表明µPC被预置数。放开CLOCK键,CLOCK产生下降沿,数据??H被写入µPC寄存器。

2、寄存器组的数据读出与CLOCK脉冲是否有关系?由此说明寄存器的数据打入与读出在控制上的差别。

答:寄存器组的数据读出与CLOCK脉冲无关。寄存器输入需要CLOCK提供上升沿信号,而读出不需要,因为OC始终接地为低电平有效。

3、总结寄存器部分实验有多少个控制信号,并写出其作用。

杭电计组实验9-实现R-I型指令地CPU设计实验

clk=1;

// Add stimulus here

forever

begin

#50;

clk=~clk;

end

end

endmodule

顶层LED验证模块:

module TOP_LED(clk_100MHz,oclk,rst,SW,LED);

input clk_100MHz;

input oclk,rst;

begin

if(rst)

PC=32'h00000000;

else

PC={24'h000000,PC_new[7:0]};

end

endmodule

OP指令功能译码模块

module OP_YIMA(inst,ALU_OP,rs,rt,rd,Write_Reg,

imm,rd_rt_s,imm_s,rt_imm_s,Mem_Write,alu_mem_s);

wire [31:0]ALU_B;

wire [2:0]ALU_OP;

pc pc_connect(clk,rst,Inst_code);

OP_YIMA op(Inst_code,ALU_OP,rs,rt,rd,Write_Reg,imm,rd_rt_s,imm_s,rt_imm_s,Mem_Write,alu_mem_s);

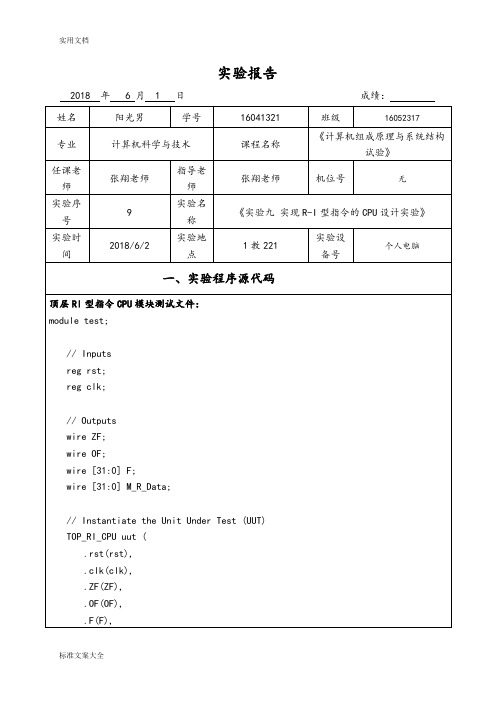

实验报告

2018年

班级

16052317

专业

计算机科学与技术

课程名称

《计算机组成原理与系统结构试验》

任课老师

张翔老师

指导老师

张翔老师

机位号

无

实验序号

9

实验名称

《实验九实现R-I型指令的CPU设计实验》

杭电计组实验5-6-7(章老师不插板实验报告)

sllv $19,$3,$17;#$19=0002_0000

sllv $20,$19,$7;#$20=8000_0000

sub $21,$1,$20; #$21=7FFF_FFFF

or $22,$18,$21;#$22=7FFF_FFFF

add $23,$20,$22; #$23=FFFF_FFFF

sub $24,$18,$19; #$24=6FFE_0000

sub $25,$19,$18; #$25=9002_0000

xor $26,$1,$18;#$26=8FFF_FFFF

sltu $27,$22,$20;#$27=0000_0001

sltu $28,$26,$20;#$28=0000_0000

#10;

Clk=1;

B

#100;

clka=0;

wea=0;

addra=6'b000001;

dina=32'b11111111110001111111111101101111;

#100;

clka=1;

wea=0;

addra=6'b000001;

dina=32'b11111111110001111111$1=FFFF_FFFF

sltu $2,$0,$1;#$2=0,000_0001

add $3,$2,$2; #$3=0000_0002

add $4,$3,$2; #$4=0000_0003

add $5,$4,$3; #$5=0000_0005

add $6,$5,$3; #$6=0000_0007

实验报告

2016年5月10日 成绩:

杭电数电课内实验

数字逻辑电路课内仿真实验第六章 QuartusII原理图设计初步一、实验目的:初步了解学习使用Quartus||软件进行电路自动化设计。

二、实验仪器:Quartus||软件。

三、实验内容:6-1 用Quartus||库中的宏功能模块74138和与非门实现指定逻辑函数按照6.3节和6.4节的流程,使用Quartus||完整图6-2电路的设计,包括:创建工程,在原理图编辑窗中绘制此电路,全程编译,对设计进行时序仿真,根据仿真波形说明此电路的功能,引脚锁定编译,编程下载于FPGA中进行硬件测试。

最后完成实验报告。

1、原理图2、波形设置3、仿真波形6-2 用两片7485设计一个8位比较器用两片4位二进制数值比较器7485串联扩展为8位比较器,使用Quartus||完成全部设计和测试,包括创建工程、编辑电路图、全程编译、时序仿真及说明此电路的功能、引脚锁定、编程下载,进行硬件测试。

最后完成实验报告。

1、原理图2、波形设置3、波形仿真6-3 设计8位串行进位加法器首先根据图4-33,用半加器设计一个全加器元件,然后根据图4-34,在顶层设计中用8个1位全加器构成8位串行进位加法器。

给出时序仿真波形并说明之,引脚锁定编译,编程下载于FPGA中进行硬件测试,最后完成实验报告,讨论这个加法器的工作速度。

1、原理图:半加器1位全加器8位串行进位全加器集成后的8位串行进位全加器2、波形设置3、波形仿真6-5 设计一个十六进制7段显示译码器用Verilog的case语句设计一个可以控制显示共阴7段数码管的十六进制码7段显示译码器。

首先给出此译码器的真值表,此译码器有4个输入端:D、C、B、A。

D是最高位,A 是最低位;输出有8位:p、g、f、e、d、c、b、a,其中p和a分别是最高和最低位,p控制小数点。

对于共阴控制,如果要显示A,输入DCBA=1010;若小数点不亮,则输出pgfedcba=01110111=77H,给出时序仿真波形并说明之,引脚锁定,下载于FPGA中对共阴数码管进行硬件测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2016年3月11

班级

计科5班

专业

计算机科学与技术

课程名称

《数字电路课程设计》

任课老师

章复嘉老师

指导老师

章复嘉老师

机位号

实验序号

1,2,3

实验名称

实验一,二,三

实验时间

3月11日

实验地点

1教225

实验设备号

一、实验程序源代码

实验1:

module ex1(Ai,Bi,Ci,Fi,Ci_1);

reg ZF,OF;

wire C32,C31;

reg [7:0]i;

reg[31:0] F;

always(*)

begin

case(ALU_OP)

3'b000:F=A&B;

3'b001:F=A|B;

3'b010:F=A^B;

3'b011:F=!(A|B);

3'b100:begin{C32,F}=A+B;OF=C32^A[31]^B[31]^F[31];end

3'b101:begin{C32,F}=A-B;OF=C32^A[31]^B[31]^F[31];end

3'b110:begin if(A<B)

F=1;

else

F=0;

end

3'b111:F=B<<A;

default: begin end

endcase

for(i=0;i<=31;i=i+1)

ZF=ZF|F[i];

input Ai,Bi,Ci;

output Fi,Ci_1;

assign Fi=Ai^Bi^Ci;

wire Ai,Bi,Ci,Fi,Ci_1;

assign Ci_1=Ai&Bi|(Ai^Bi)&Ci;

endmodule

实验2:

module ex2_1(F,A,B,C0,C4);

input[3:0] A,B;

ZF=!ZF;

end

endmodule

二、仿真波形

实验2

实验3

三、电路图

四、引脚配置(约束文件)

五、思考与探索

1.复习了FPGA,Verilog HDL的用法

六、意见和建议

1.无

input C0;

output[3:0] F;

output C4;

assign {C4,F}=A+B+C0;

endmodule

实验3:

module ex3(ALU_OP,A,B,F,ZF,OF

);

input[2:0] ALU_OP;

input[31:0] A,B;

output[31:0] F;

output ZF,OF;