杭电计组实验十

杭州电子科技大学自动控制原理实验报告(DOC)

自动控制原理实验报告班级: __________学号: ______________姓名: ______________指导老师:3.1.1典型环节的模拟研究典型比例环节模拟电路如图3-1-1所示。

图3-1-1 典型比例环节模拟电路传递函数:G(S)_U o(S)_K K -尺:单位阶跃响应:U(t)=KU i(S)R o按下表改变图3-1-1所示的被测系统比例系数,观测结果,填入实验报告。

R0R1输入Ui比例系数K计算值测量值200K100K4V0.50.5050K200K1V4 3.92计算號式,UlrE 十|u.O £tU I「Ulrf —[J D Ufcr3 ED EL B2E3 P1H P340375图1 比例:R0=200, R1= 100,Ui=4V巫一□4V2 Q3¥L 13Q0 B6Hz 2 Q3¥T L 99^ 4.005V Z QJ1V 2.031V■ Fl 亘二 1. l:30 i D BBKt 4.023¥0047 3. 9B7 4.0637 Z.M1V 2.03212 燈-Y1册泌l/02-xl)绘大值屋<1、晅握帼Y1「劇崖电压「季点轻制CH1亠采擇周朝T=OV-SV「时词呈程 -------------- 显示方式图3-1-2典型惯性环节模拟电路按下表改变图3-1-2所示的被测系统时间常数及比例系数,观测结果,填入实验报告。

R0 R1 C 输入Ui比例系数K 惯性常数T 计算值测量值 计算值 测量值 200K 200K1u 4V 1 1.0 0.2 0.2 50K1u1V43.90.20.22).观察惯性环节的阶跃响应曲线 典型惯性环节模拟电路如图周朋性拒那波信号B5 OUT 口200 K3-1-2所示。

K1 200KIK A5A10KA5BU 。

10KI I —1OUTBU O (S) _ KR i 传递函数:G (S) 0K- T =R 1C U i (S) i +rsR ot单位阶跃响应:U o (t) =K(1 -e 下)图 2 比例:R0=50, R1=200, Ui=1V典型积分环节模拟电路如图3-1-3所示。

杭州电子科技大学计算机网络实验报告

IP地址学习Top Previous Next 一、目标学习IP地址、子网划分和子网掩码。

二、实验内容利用IP Calculator工具,完成下面实验练习,熟悉IP地址分类、特殊IP地址、子网划分和子网掩码。

三、实验练习:下面的问题将帮助你评价你在本章中学习到的内容。

仔细阅读所有的选项,因为正确答案可能多于1个。

选择每个问题中所有的正确答案。

1) What is the network address for the address 96.2.3.16 (地址9 6.2.3.16的网络地址是什么)?A. 96.2.0.0B. 96.2.3.0C. 96.0.0.0D. Can 't tell2) What class of address is 190.233.27.13 (190.233.27.13是何类地址)?A. Class AB. Class BC. Class CD. Class D3) How many bits are in the default subnet mask for the address 219.25.23.56 (在地址219.25.23.56的默认子网掩码中有多少位)?A. 8B. 16C. 24D. 324) How many hosts are supported by a Class C network address, without subnetting (C类网络地址在没有子网的情况下支持多少个主机)?A. 254B. 65,000C. 255D. 16,0005) What is the default mask for a Class B network (B类网络的默认掩码是什么)?A. 255.0.0.0B. 255.255.255.0C. 255.255.0.0.D. 255.225.0.06) Approximately how many unique networks are possible with a Class B address (使用B类地址大约可以有多少个不相同的网络)?A. 254B. 16KC. 65KD. 2M7) What is the decimal value of the binary number 11 0 0 1 0 11 (二进制数11 0 0 1 0 11的十进制值是多少)?A. 203B. 171C. 207D. 1938) What is the binary value of the decimal number 219 (十进制数219的二进制值是多少)?A. 111 0 1 0 11B. 01011101C. 111 0 1 0 11D. 11 0 11 0 119) Subnet bits are added to_ _ _ _ _ _ _ _ _ _ to segment the network into subnets (子网位加入到____________以将网络划分为子网)?A. The network addressB. The default subnet maskC. The host addressD. The subnet ID10) If eight bits were allocated to subnetting with a Class B address, how many subnets would be possible (如果在B类地址中,将8位分配给子网,则有多少可能的子网)?A. 62B. 256C. 254D. 16K11) Given the subnet mask 255.255.240 on a Class A address, how many bits are allocated tosubnetting (在A类地址上给定了子网掩码255.255.240,则有多少位分配给子网)?A. 4B. 5C. 9D. 1212) If the subnet mask for the network 150.25.0.0 is 255.255.224.0, which of these is a valid host address (如果网络150.25.0.0的子网掩码是255.255.224.0,下面的哪一个是合法的主机地址)?A. 150.25.0.27B. 150.25.30.23C. 150.25.40.24D. 150.25.224.3013) What is the first subnet ID for the network 25.0.0.0 with a subnet mask of 255.192.0.0(带有子网掩码255.192.0.0的网络25.0.0.0的第一个子网I D是什么)?A. 25.192.0.0B. 25.64.0.0C. 25.128.0.0D. 25.192.64.014) What is the maximum number of subnet bits possible with a Class C address? (在C类地址下,子网位可能的最多数目是多少? )A. 6B. 8C. 14D. 1215) Given a subnet mask of 255.255.240, which of these addresses is not a valid host address(在给定子网掩码255.255.240的情况下,这些地址中的哪一个不是合法的主机地址)?A. 150.150.37.2B. 150.150.16.2C. 150.150.8.12D. 150.150.49.1516) How many hosts per subnet are possible with a Class B address, if five bits are added to the default mask for subnetting (在B类地址中,每个子网有多少可用的主机,如果在默认掩码后加入了5位,以进行子网划分)?A. 510B. 512C. 1022D. 204617) If you were issued a Class C address, and needed to divide the network into seven subnets, with up to 15 hosts in each subnet, what subnet mask would you use (如果你遇到了一个C类地址,并且需要将网络划分为7个子网,每个子网有1 5个主机,则将使用哪个子网掩码)?A. 255.255.255.224B. 255.255.224C. 255.255.255.240D. None of the AboveIP设置Top Previous Next 一、目标学习IP地址、子网划分和子网掩码。

杭电计组实验-存储器设计实验

杭电计组实验-存储器设计实验————————————————————————————————作者:————————————————————————————————日期:实验报告2018 年 5 月 5 日成绩:姓名阳光男学号16041321 班级16052317专业计算机科学与技术课程名称《计算机组成原理与系统结构试验》任课老师张翔老师指导老师张翔老师机位号默认实验序号5实验名称《实验五存储器设计实验》实验时间2018/5/12实验地点1教211实验设备号个人电脑、Nexys3开发板一、实验程序源代码存储器顶层电路代码:module top_RAM_B(Mem_Addr,C,Mem_Write,Clk,LED);input [7:2]Mem_Addr;//开关的3、4、5、6、7、8位input Mem_Write,Clk;//clk为按键C9,读写使能信号为按键C4,0为读,1为写input [1:0]C;//选择写入数据+读操作时选择显示字节,为开关1、2位output reg [7:0]LED;wire [31:0]M_R_Data;//存在存储器里的32位读出数据reg [31:0]M_W_Data;//寄存在暂存器的32位写入数据RAM_B test_ram (.clka(Clk), //输入时钟信号.wea(Mem_Write), //输入读写信号.addra(Mem_Addr[7:2]), //输入5位地址信号.dina(M_W_Data), //写入32位数据.douta(M_R_Data) //读出32位数据);always@(*)beginLED=0;//初始化M_W_Data=0;//初始化if(!Mem_Write)//读操作begincase(C)2'b00:LED=M_R_Data[7:0];//读出数据的0-7位2'b01:LED=M_R_Data[15:8];//读出数据的8-15位2'b10:LED=M_R_Data[23:16];//读出数据的16-23位2'b11:LED=M_R_Data[31:24];//读出数据的24-31位endcaseendelsebegincase(C)2'b00:M_W_Data=32'h0055_7523;//写入第一个数据2'b01:M_W_Data=32'h1234_5678;//写入第二个数据2'b10:M_W_Data=32'h8765_4321;//写入第三个数据2'b11:M_W_Data=32'hffff_ffff;//写入第四个数据endcaseendendendmodule测试代码:module test;// Inputsreg clka;reg [0:0] wea;reg [5:0] addra;reg [31:0] dina;// Outputswire [31:0] douta;// Instantiate the Unit Under Test (UUT)RAM_B uut (.clka(clka),.wea(wea),.addra(addra),.dina(dina),.douta(douta));initial begin// Initialize Inputsclka = 0;wea = 0;addra = 0;dina = 0;// Wait 100 ns for global reset to finish #100;// Add stimulus hereclka = 1;wea = 0;addra = 6'b000001;dina = 32'h0000_0003;#100;clka = 0;wea = 0;addra = 6'b000001;dina = 32'h0000_0607;#100;clka = 1;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;#100;clka = 0;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;endendmodule二、仿真波形三、电路图顶层电路模块顶层电路内部结构:四、引脚配置(约束文件)NET "Clk" LOC = C9;NET "LED[4]" LOC = M11;NET "LED[3]" LOC = V15;NET "LED[2]" LOC = U15;NET "LED[1]" LOC = V16;NET "LED[0]" LOC = U16;NET "Mem_Addr[7]" LOC = U8;NET "Mem_Addr[6]" LOC = N8;NET "Mem_Addr[5]" LOC = M8;NET "Mem_Addr[4]" LOC = V9;NET "Mem_Addr[2]" LOC = T10;NET "Mem_Write" LOC = C4;NET "Mem_Addr[3]" LOC = T9;NET "C[1]" LOC = T5;NET "C[0]" LOC = V8;NET "LED[7]" LOC = T11;NET "LED[5]" LOC = N11;NET "LED[6]" LOC = R11;五、思考与探索(1)读操作实验结果记录表存储器地址初始化数据读出数据写入新数据读出数据5’b000000 32’b0000000032’b0000000032'h0055_752332'h0055_7523 5’b000001 32’b0000000132’b0000000132'h0055_752332'h0055_7523 5’b000002 32’b0000000232’b0000000232'h0055_752332'h0055_7523 5’b000003 32’b0000000332’b0000000332'h0055_752332'h0055_7523 5’b000004 32’b0000000432’b0000000432'h0055_752332'h0055_7523 5’b000005 32’b0000000532’b0000000532'h0055_752332'h0055_7523 5’b000006 32’b0000000632’b0000000632'h0055_752332'h0055_7523 5’b000007 32’b0000000732’b0000000732'h0055_752332'h0055_7523 (2)答:这些单元的数据已经被改写了。

杭电过程控制实验报告

一、实验目的1. 理解过程控制的基本原理和方法;2. 掌握过程控制系统的设计、调试与优化;3. 熟悉过程控制实验设备的使用方法;4. 提高实际操作能力,培养团队合作精神。

二、实验原理过程控制是利用自动化仪表和计算机对工业生产过程中的各种参数进行检测、控制和调节的一种技术。

本实验主要涉及以下原理:1. PID控制算法:PID控制器是一种模拟控制器,它通过比例、积分、微分三个环节对被控对象的输出进行调节,以达到预期的控制效果。

2. 过程控制系统:过程控制系统由被控对象、控制器、执行机构和反馈环节组成。

控制器根据反馈环节的信号对执行机构进行调节,使被控对象达到预期的控制目标。

三、实验设备1. 过程控制实验台;2. 计算机及上位机软件;3. 数据采集卡;4. 控制器、执行机构和传感器等。

四、实验内容1. PID控制器参数整定:通过改变PID控制器的比例、积分、微分参数,观察被控对象的响应,寻找最佳参数组合。

2. 过程控制系统仿真:利用上位机软件,对过程控制系统进行仿真,分析系统性能。

3. 实验数据分析:对实验数据进行处理和分析,得出结论。

五、实验步骤1. 熟悉实验台设备和上位机软件的操作;2. 搭建实验系统,包括被控对象、控制器、执行机构和传感器等;3. 设置实验参数,包括PID控制器参数、采样时间等;4. 进行PID控制器参数整定,观察被控对象的响应;5. 利用上位机软件对过程控制系统进行仿真,分析系统性能;6. 对实验数据进行处理和分析,得出结论。

六、实验结果与分析1. PID控制器参数整定结果通过实验,得到PID控制器参数如下:比例系数Kp:120积分时间Ti:150微分时间Td:10整定后的系统在2秒内达到稳态,稳态误差为0,动态性能较满意。

2. 过程控制系统仿真结果通过仿真,得到以下结果:系统在0.5秒内达到稳态,稳态误差为0,动态性能较满意。

3. 实验数据分析根据实验数据,分析如下:(1)PID控制器参数对系统性能的影响比例系数Kp:增大Kp,系统动作灵敏,响应速度加快,但过大会使振荡次数增加,系统趋向不稳定。

杭电自动化单片机实验报告

杭电自动化单片机实验报告单片机原理与应用及 C51程序设计实验报告实验名称:单片机技术实验实验一继电器控制输出实验一、实验目的1.掌握STC12C5A16S2单片机的最基本电路的设计;2.了解单片机I/O端口的使用方法;3.了解继电器和蜂鸣器控制电路以及小电压控制大电压的方法。

二、实验要求1.利用STC12C5A16S2单片机的P1.2、P1.3口作按钮S9和S10输入,P1.0和P1.1口作开关量输出,并分别控制一个5V的继电器和蜂鸣器。

2.当S9闭合时,P1.0控制继电器闭合并控制灯泡闪亮;当S9断开时,继电器触电断开,灯泡不亮;3.当S10闭合时,P1.1控制蜂鸣器闭合并发出声音;当S10断开时,蜂鸣器不响。

三、电路四、原理说明Q1、Q2为9012三极管即PNP型,低电平导通,当S9或S10按下时,相应的IO口拉低,当P1.0或P1.1赋0时即可控制继电器的吸合活着蜂鸣器的发声。

五、程序代码#includesbit L1=P1^1;sbit L2=P1^2;sbit L3=P1^3;sbit L0=P1^0;//定义位变量void delay(){int i,j;for(i=0;i<250;i++)for(j=0;j<250;j++);//利用系统时钟,定义延时函数}void main (){int n=20;while(1) //不断循环检测{if(L2==0) //判断S9输入{while(n--){L0=0;delay();L0=1;delay(); //灯泡以2*delay为周期闪亮}n=20;}if(L3==0) //判断S10闭合{while(n--){L1=0;delay();delay(); //蜂鸣器以2*delay为周期发声}n=20;}}}实验二 LED轮换点亮实验一、实验目的1.掌握STC12C5A16S2单片机的I/O电路设计;2.学习SN74HC573数据锁存输出方法。

杭电自动化专业计算机控制系统实验报告

实验一、常规PID控制算法仿真仿真框图如下实验参数:shiyanpid Ts=0.1s,b为班号1~5,x为学号后2位,1~45实验要求:(1)画Simulinnk框图(2)设计或凑试PID三个参数,进行仿真(3)使稳态误差为0,且动态性能较满意仿真框图:实验分析:b=1,x=15。

比例系数Kp增大时系统动作灵敏,响应速度加快,过大会使振荡次数增加,系统趋向不稳定,这里取120。

积分环节可以消除稳态误差,Ti减小,系统振荡次数增加,这里取Ki为150。

微分环节可以改善系统动态性能,减小超调和调节时间,这里取Kd为10。

系统在2秒内达到稳态。

实验二、积分分离PID控制算法仿真实验参数:shiyanpidjffl Ts=0.1s,b为班号1~5,x为学号后2位,1~45实验要求:(1)画Simulinnk框图(2)使稳态误差为0,且动态性能较满意(3)尝试不同的积分分离的阈值(比如ε=0,0.1,0.2,……,0.9,1),观察阶跃响应,并确定最佳的阈值实验框图:翻译后Switch模块的说明:如果2输入满足规则,则1通道通过,否则3输入通过。

输入被标号。

1输入通过规则是输入2(偏差e)大于或等于阀值。

第一三输入为数据输入,第二输入为控制输入。

原理:|e(k)|<=ε,ki起作用|e(k)|>ε,ki不起作用,由于阶跃输入,(treshhold )ε=0.1,0.2,……,0.9,1。

由于参数原因去kp=50,ki=kd=0时,曲线最好为了体现ε的作用,积分值不取0,改为Ki=10取不同ε后的曲线ε=0.1ε=0.5ε=1分析:ε=0.1时曲线最好,ε过大起不到积分分离的作用,比如ε=1,总会存在积分作用,ε过小可能是控制不能跳出积分分离的区域,从而只存在PD作用,长时间存在静差。

实验三、不完全微分PID控制算法仿真1、不完全微分PID控制器的阶跃响应实验参数:Shiyanpidbwqwfstep Ts=0.1s,仿真时间设为10s,5s,3s P=1 I=1 D=1滤波器参数a=0.1,0.2,……,0.8,1.2,实验框图:框图1:积分输出:微分输出:可见微分只在第一个单位时间有相应,而且较大框图2:a=0.1时a=0.5时:a=1时:分析:引入惯性环节后,对微分环节对阶跃响应有明显的改善作用。

杭电计算机组成原理多功能ALU设计实验

评议

成绩评定: 指导教师签名:

(7)记录测试结果。

(接上)

实验内容(算法、程序、步骤和方法)

(1)ALU模块代码,利用三八译码器,将我们将要操作的对象,进行分别的处理。

module ALU_TOP(A,B,F,ZF,OF,ALU_OP);

input [31:0] A,B;

input [2:0] ALU_OP;

output ZF,OF;

3'b010:begin CF=A^B; end

3'b011:begin CF=A~^B; end

3'b100:begin CF=A+B; end

3'b101:begin CF=A-B; end

3'b110:begin CF=(A<B); end

3'b111:begin CF=B<<A; end

endcase

end

endmodule

(3)输出数据选择模块代码,根据实验指导书上的对于32位数据的处理方式。

module CLED(F_LED_SW,LED,F,ZF,OF);

input [31:0] F;

input ZF,OF;

input [2:0] F_LED_SW;

output [7:0] LED;

reg [7:0] LED;

output [31:0] F;

reg [31:0] F;

reg ZF,OF;

reg [5:0] i;

reg C;

reg [32:0] CF;

always @ (ALU_OP or A or B)

begin

case(ALU_OP)

杭电计算机组成原理全加器设计实验

cndmodulc

仿真文件:

module test;

w若A;

re若B;

rcg Ci;

// Outputs

wire F;

wire Co;

// Instantiate the Univ Under Test (UUT)

Add uut (

•A(A),

•Ci(Ci),

•F(F),

A = 0;B = l;Ci = 0;

#100;

A二0;B = l;Ci= 1;

#100;

A = 1;E二0;Ci = 0;

#100;

A = 1;B = 0;Ci = 1;

#100;

A = 1;B = 1 ;Ci = 0;

#100;

A= 1;B二l;Ci=1;

#100;

end

cndmodulc

(接上) 实验內容(算 法、程序、步 骤和方法)

<4)生成BIT文件,下载入FPGA,进行硬件测试。

代码:

Module文件:

module Add(A,B,Ci,F,Co);

input A,E,Ci;

output F,Co;

wire A,B,Ci,F,Co;

xorXl(F,A,B,Ci),

X2(S2,A,B);

and Al (SI,A,B),

A2(S3,S2,Ci);

如有侵权请联系告知删除,感谢你们的配合!

杭州电子科技大学计算机学院

实验报告

计算机组成原理

姓

名:

全加器设计实验

班

级

学

号

0

期:2015年4月15日

课程名称: 实验项目: 指导教师: 实脸位置:

计组报告(算术逻辑运算实验)

2.验证运算器74LS181算数逻辑运算功能。

实验环境

Yy-z02计算机组成原理教学实骤和方法)

步骤:

(1)根据实验原理和相关单元电路,画出实验接线图,连接线路,仔细检查接线无误后,接通电源。

(2)通过输入设备INPUT DEVICE向暂存器DA1和DA2置数。

接上实验内容算法程序步骤和方法本实验中输入设备的ai接地表示选中该设备其数据开关inputdevice在输入数据时必须连接至总线使输入设备的数据输入总线

杭州电子科技大学计算机学院

实验报告

课程名称:计算机组成原理实验

实验项目:算术逻辑运算实验

指导教师:__

实验位置:

姓名:__

班级:

学号:

日期:

实验目的

F=(11111101)

0FD

05CH

1111

F=(11111100)

F=(11111101)

F=(11111101)

结论(结果)

运算器74LS181算术逻辑运算功能正常,可以进行正确的算数与逻辑运算。

试验心得与小结

指导教师

评议

成绩评定:指导教师签名:

0FD

05CH

0101

F=(10011110)

F=(10011111)

F=(10100011)

0FD

05CH

0110

F=(10100000)

F=(10100001)

F=(10100001)

0FD

05CH

0111

F=(10100000)

F=(10100001)

F=(10100001)

0FD

05CH

1000

杭电电子线路实习实验报告

杭电电子线路实习实验报告一、实验目的1. 加深对电子线路理论知识的理解,提高实际操作能力。

2. 掌握基本电子仪器的使用方法,如示波器、信号发生器、万用表等。

3. 学习电子线路的安装与调试方法,培养动手能力和团队协作精神。

二、实验内容本次实验为电子线路安装与调试实验,主要包括以下内容:1. 根据电路图搭建电路;2. 正确使用仪器进行测试;3. 分析测试数据,判断电路是否存在问题;4. 调整电路参数,使电路达到预期性能;5. 撰写实验报告。

三、实验过程1. 根据实验指导书给出的电路图,搭建电路。

在搭建过程中,要注意元器件的极性、引脚顺序等,确保电路的正确性。

2. 使用万用表测量电路中的电压、电流等参数,初步判断电路是否正常。

3. 使用示波器观察电路中的信号波形,分析电路的性能。

如有问题,需调整电路参数,如电阻值、电容值等。

4. 针对电路中可能存在的问题,进行多次调试,直至电路性能达到预期。

5. 撰写实验报告,总结实验过程中遇到的问题及解决方法,反思实验过程中的不足。

四、实验结果与分析1. 实验结果:通过多次调试,最终使电路达到了预期性能,信号波形稳定,电路工作正常。

2. 结果分析:在实验过程中,我们掌握了电子仪器的使用方法,提高了动手能力。

同时,通过分析测试数据,我们学会了判断电路是否存在问题,并能够针对问题进行调整。

此外,实验过程中的团队协作也使我们更好地完成了任务。

五、实验收获1. 掌握了电子线路安装与调试的基本方法;2. 学会了使用电子仪器,如示波器、信号发生器、万用表等;3. 提高了动手能力和团队协作精神;4. 加深了对电子线路理论知识的理解。

六、实验反思1. 在实验过程中,我们要严谨认真,确保电路搭建的正确性;2. 学会分析测试数据,判断电路是否存在问题;3. 调整电路参数时,要耐心细致,切勿急躁;4. 加强团队协作,共同完成实验任务。

总之,本次电子线路实习实验使我们受益匪浅,不仅提高了实际操作能力,还加深了对电子线路理论知识的理解。

杭电 计算机网络实验报告

目录实验一、使用数据拷贝线组网 (1)实验二、制作直通双绞线组网 (4)实验三、制作交叉双绞线组网 (7)实验四、Cisco IOS基本使用 (10)实验五、交换机基本使用 (14)实验六、VLAN的使用 (18)实验七、路由器的基本使用 (25)实验八、动态路由配置 (30)实验一、使用数据拷贝线组网实验一使用数据拷贝线组网实验台号:实验时间:实验小组号:成员及本次实验分工:实验目的:学会使用并行电缆(数据拷贝线)实现双机通信和资源共享。

使用直接电缆实现两台PC机之间的通信。

实验环境说明:硬件:2台计算机、2-3根并行电缆软件:Windows XP操作系统实验过程及步骤(可另附页、使用网络拓扑图等辅助说明):(1)、使用并行电缆将两台PC机,进行物理互连;(2)、分别在两台PC机上的网上邻居中创建一个新连接。

按照新建连接向导的指示来做。

首先网络连接类型选为“设置高级连接”;然后其中作为服务器的那台PC机创建为“接受传入的连接”,作为客户机的则创建为“直接连接到其他计算机的连接”,并让此计算机担任“来宾”的角色。

接下去根据向导直至完成创建新连接。

(3)、测试两机的可通用性。

创建好连接之后可以用ping命令测试一下两台机器之间是否已经连通。

(4)、连接创建成功之后,客户机可以找到并登入到服务器,就可以实现对服务器上的资源的共享了。

当然在此之前作为服务器的主机还需要将文件夹属性设置成为可共享的。

测试数据线连接以后Ping对方说明能够Ping通在一台PC上设置共享,然后在另外一台PC上查看共享截图如下:说明通过数据拷贝线成功地连接了两台PC,实现了他们之间的通信。

实验总结(遇到的问题及解决办法、体会):刚开始配置客户机的时候出了点问题。

需要输入对方计算机的名字,我们却输入了服务器上的计算机用户的帐号,所以一直没有连接成功。

后来终于发现了这个问题。

配置也就顺利了。

实验器材、工具领用及归还负责人:验收人:实验执笔人:实验记录人:报告协助人:实验报告完成时间:小组成员签名:指导教师评议成绩评定:指导教师签名:实验二、制作直通双绞线组网实验二制作直通双绞线组网实验台号: 实验时间: 实验小组号:成员及本次 实验分工: 实验目的:1. 了解双绞线的相关知识;2. 学会制作直通双绞线;3. 掌握用双绞线实现集线器和计算机之间的互连。

杭电实验报告模版

一、实验模块实验名称:____________________实验课程:____________________实验时间:____________________实验地点:____________________实验人员:____________________二、实验标题____________________三、实验目的1. 了解____________________2. 掌握____________________3. 培养____________________四、实验原理____________________五、实验仪器与设备1. 仪器名称:____________________2. 仪器型号:____________________3. 仪器规格:____________________4. 其他设备:____________________六、实验步骤1. 实验步骤一:(1)____________________(2)____________________(3)____________________2. 实验步骤二:(1)____________________(2)____________________(3)____________________3. 实验步骤三:(1)____________________(2)____________________(3)____________________(注:根据实际实验内容,添加相应步骤)七、实验过程1. 实验过程一:(1)____________________(2)____________________(3)____________________2. 实验过程二:(1)____________________(2)____________________(3)____________________3. 实验过程三:(1)____________________(2)____________________(3)____________________(注:根据实际实验内容,添加相应过程)八、实验数据记录与分析1. 实验数据记录:(注:根据实际实验内容,添加数据记录表格)2. 实验数据分析:(注:根据实际实验内容,对实验数据进行分析)九、实验结论1. 实验结果:(1)____________________(2)____________________(3)____________________2. 实验结论:(1)____________________(2)____________________(3)____________________十、实验讨论1. 实验中遇到的问题及解决方法:(1)____________________(2)____________________(3)____________________2. 实验改进建议:(1)____________________(2)____________________(3)____________________十一、实验总结通过本次实验,我了解了____________________,掌握了____________________,培养了____________________。

杭电电子电路实习报告

一、实习背景随着科技的飞速发展,电子电路技术已成为现代社会不可或缺的一部分。

为了提高学生的实践能力,培养具备实际操作经验的电子电路技术人才,我校组织了电子电路实习活动。

本次实习在杭州电子科技大学电子电路实验室进行,旨在使学生了解电子电路的基本原理,掌握电子电路的设计与制作方法,提高学生的动手操作能力。

二、实习目的1. 熟悉电子电路的基本原理和设计方法;2. 掌握常用电子元器件的性能和选用技巧;3. 提高电子电路的调试和维修能力;4. 培养团队合作精神和创新意识。

三、实习内容1. 电子电路基础知识学习在实习初期,我们学习了电子电路的基本概念、电路元件、电路分析方法等基础知识。

通过学习,我们对电子电路有了初步的认识,为后续的实习工作奠定了基础。

2. 电子电路设计与制作在实习过程中,我们分组进行电子电路设计与制作。

具体内容包括:(1)电路设计:根据任务要求,我们查阅相关资料,确定电路拓扑结构,绘制电路原理图。

(2)元器件选用:根据电路原理图,选择合适的元器件,并计算其参数。

(3)电路制作:按照电路原理图,焊接元器件,组装成完整的电路。

(4)电路调试:对制作好的电路进行调试,确保电路性能达到预期要求。

3. 电路分析与应用在实习过程中,我们还学习了电路分析的基本方法,如基尔霍夫定律、欧姆定律等。

通过分析电路,我们了解了电路的性能和特点,为后续的电路设计与制作提供了理论依据。

4. 电路故障诊断与维修在实习后期,我们学习了电路故障诊断与维修的基本方法。

通过分析电路故障现象,找出故障原因,并采取相应的维修措施,使电路恢复正常工作。

四、实习收获1. 理论与实践相结合:通过本次实习,我们将所学理论知识与实际操作相结合,提高了自己的动手能力。

2. 团队合作:在实习过程中,我们分组进行电子电路设计与制作,培养了团队合作精神。

3. 创新意识:在电路设计与制作过程中,我们不断尝试新的方法,提高了创新意识。

4. 电路故障诊断与维修能力:通过实习,我们掌握了电路故障诊断与维修的基本方法,为今后的学习和工作打下了基础。

HDU杭电单片机技术与应用实验指导书

单片机技术与应用实验指导书王俊宏周洪波暨仲明编杭州电子科技大学自动化学院二零零五年十月目录第一章系统安装和启动 (1)第二章调试软件LCA51界面介绍 (2)1.主界面 (2)2.菜单介绍................................................................................................................ 错误!未定义书签。

3.热键表. (11)第三章LCA51软件调试 (12)1.调试界面 (12)2.调试主要方法和技巧 (13)实验一扩展存储器读写实验 (15)实验二P1口、P3口输入、输出实验 (17)实验三定时器实验 (20)实验四外部中断实验(急救车与交通灯) (22)实验五8279显示实验................................................................................................. 错误!未定义书签。

实验六8255扫描键盘、显示实验 (24)实验七D/A和A/D转换实验 (27)实验八步进电机控制实验 (31)实验九压力测量显示实验.......................................................................................... 错误!未定义书签。

实验十单片机串行口与PC机通讯实验 (34)第一章系统安装和启动1.实验系统工作在51串口实验/仿真方式(1)实验台上开关选择51(2)打开电源,在PC机上打开LCA51软件,运行实验程序。

2.实验系统工作在MCS51方式下开关初始状态●XB、XB1 : 短路套全插上。

●XB2,XB5 : 短路套向上插(SPEAK端),第10模块处于放音功能。

●第○4模块中:多位开关K3拨向最左(温度控制)端,做温度控制实验用。

杭电计组实验10-实现R-I-J型指令的CPU设计实验

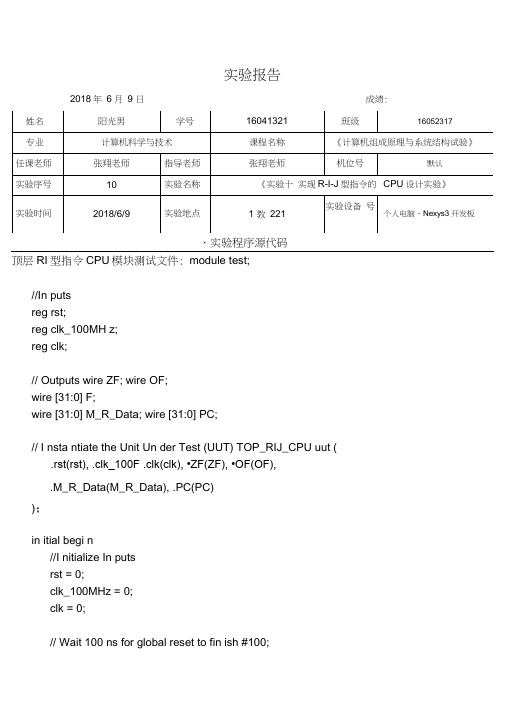

实验报告2018年6月9 日成绩:、实验程序源代码顶层RI型指令CPU模块测试文件: module test;//In putsreg rst;reg clk_100MH z;reg clk;// Outputs wire ZF; wire OF;wire [31:0] F;wire [31:0] M_R_Data; wire [31:0] PC;// I nsta ntiate the Unit Un der Test (UUT) TOP_RIJ_CPU uut ( .rst(rst), .clk_100F .clk(clk), •ZF(ZF), •OF(OF),.M_R_Data(M_R_Data), .PC(PC));in itial begi n//I nitialize In putsrst = 0;clk_100MHz = 0;clk = 0;// Wait 100 ns for global reset to fin ish #100;// Add stimulus hereforeverbegi n#2;clk=~clk;#10;clk_100MHz=~clk_100MH z;endenden dmodule顶层LED验证模块module TOP_LED(clk_100M Hz, oclk,rst,SW 丄ED); in put clk_100MH z; in put oclk,rst;in put [3:0]SW;output reg[7:0]LED;4'b0001:LED二F[15:8];4'b0010:LED=F[23:16];4'b0011:LED=F[31:24];4'b0100:LED=M_R_Data[7:0];4'b0101:LED=M_R_Data[15:8];4'b0110:LED二M_R_Data[23:16];4'b0111:LED=M_R_Data[31:24];4'b1000:begin LED[7:2]=0;LED[1]=OF;LED[0]=ZF;e nd4'b1100:LED=PC[7:0];4'b1101:LED=PC[15:8];4'b1110:LED=PC[23:16];4'b1111:LED=PC[31:24];default:LED=0;endcaseenden dmodule顶层RIJ型指令CPU验证模块:module TOP RIJ CPU(i nput rst, in put elk 100MHz,i nput clk,output ZF, output OF,output [31:0]F,output [31:0]M_R_Data,output [31:0]PC);wire Write_Reg;wire [31:0]lnst_code;wire [4:0]rs;wire [4:0]rt;wire [4:0]rd;wire [31:0]rs_data;wire [31:0]rt_data;wire [31:0]rd_data;wire [31:0]imm_data;〃被扩展的立即数wire [15:0]imm;//wire rd_rt_s;wire [1:0]w_r_s;wire imm_s;〃判断是否需要扩展wire rt_imm_s;//B 端选择rt或者是扩展后的immwire Mem_Write;//wire alu_mem_s;wire [1:0]wr_data_s;wire [31:0]W_Addr;wire [31:0]W_Data;wire [31:0]R_Data_A;wire [31:0]R_Data_B;wire [31:0]F;wire [31:0]ALU_B;//B 端口数据wire [2:0]ALU_OP;wire [1:0]PC_s;wire [31:0]PC_ new;wire [31:0]PC;wire [25:0]address;pc pc_c onn ect(clk,rst,PC_s,R_Data_A,imm_data,address,l nst_code,PC);OP_YIMA op(I nst_code,ALU_QP;,rt,rd,Write_Reg,imm,imm_s,rt_imm_s,Mem_Write,address,w_r_s,wr_data_s,PC_s,ZF);elsebeg in case(PC_s)2'b00:PC<二PC_ new;2'bO1:PC<二R_Data_A;2'b10:PC<=PC_ new+(imm_data<<2);2'b11:PC<={PC_ new[31:28],address,2'b00};endcaseendenden dmoduleOP指令功能译码模块:module OP_YIMA(i nst,ALU_OPfe,rt,rd,Write_Reg,imm,imm_s,rt_imm_s,Mem_Write,address,w_r_s,wr_data_s,PC_s,ZF) in put [31:0]i nst; output reg[2:0]ALU_OP;output reg[4:0]rs;output reg[4:0]rt;output reg[4:0]rd;output reg Write_Reg;output reg[15:0]imm;//output reg rd_rt_s;output reg imm_s;output reg rt_imm_s;output reg Mem_Write;output reg [25:0]address;output reg[1:0] w_r_s;output reg[1:0] wr_data_s;output reg[1:0] PC_s;in put ZF;always@(*)begi nw_r_s=2'b01;Write_Reg=1; wr_data_s=2'b00;case(i nst[31:26])6'b001000:begin imm_s=1;ALU_OP=3'b100;e nd 6'b001100:begin imm_s=0;ALU_OP=3'b000;e nd 6'b001110:begin imm_s=0;ALU_OP=3'b010;e nd 6'b001011:begin imm_s=0;ALU_OP=3'b110;e nd endcaseend// ------- 处理I型取数/存数指令------if((i nst[31:30]==2'b10)&&(in st[28:26]==3'b011))imm=i nst[15:0];rt=i nst[20:16];//rt 寄存器rs=inst[25:21];//rs 寄存器//rd_rt_s=1;//rt作为目的存储器rt_imm_s=1;//imm 作为源操作数imm_s=1;w_r_s=2'b01;wr_data_s=2'b01;PC_s=2'b00;case(i nst[31:26])6'b100011:begin Mem_Write=O; Write_Reg=1;ALU_OP=3'b100;e nd 6'b101011:begin Mem_Write=1; Write_Reg=0;ALU_OP=3'b100;e nd endcaseend// ---------- 处理I型跳转指令-------if(i nst[31:27]==5'b00010)begi nimm=i nst[15:0];rt=i nst[20:16];//rtrs=i nst[25:21];//rscase(i nst[31:26])for(i=0;iv=31;i二i+1)REG_Files[i]=O;endassign R_Data_A=REG_Files[R_Addr_A]; assign R_Data_B=REG_Files[R_Addr_B]; always@(posedge Clk or posedge Reset) begi nif(Reset)for(i=0;i<=31;i=i+1)REG_Files[i]v=O;elseif(Write_Reg&&W_Addr!=0)REG_Files[W_Addr]<=W_Data; enden dmoduleALU运算模块:module ALU(A,B,F,ALU_QZF,OF); in put [31:0]A,B;in put [2:0]ALU_OP;output reg ZF,OF;output reg[31:0]F;reg C32;always@(*)begi nOF=1'b0;C32=1'b0;case(ALU_OP)3'b000:F=A&B;3'b001:F=A|B;3'b010:F=A A B;3'bO11:F=~(A^B);3'b100:begin {C32,F}=A+B;OF=A[31]A B[31]A F[31]A C32;e nd3'b101:begin {C32,F}二A-B;OF二A[31]AB[31]AF[31FC32;e nd 3'b110: if(A<B)F=1;elseF=0;3'b111:F=B<< A;endcaseif(F==0)ZF=1;elseZF=0;enden dmodule三、电路图J!仿真波形NjmeVtki*曲饶k ■ FIJI*]•电M_R_Dala[11fl]0 1吃网IIIhO Q10000(X1 悴259^353顶层电路内部结构:四、引脚配置(约束文件)NET "LED[7]" LOC = T11; NET "LED[6]" LOC = R11; NET "LED[5]" LOC = N11; NET "LED[4]" LOC = M11; NET "LED[3]" LOC = V15; NET "LED[2]" LOC = U15; NET "LED[1]" LOC = V16; NET "LED[0]" LOC = U16; NET "SW[3]" LOC = M8; NET "SW[1]" LOC = T9; NET "SW[01" LOC = T10;顶层电路模块SW(3:D)TOP LEDLED(7:0)elk 100MH2odknsl■ /TOP_LEDTOP LED.1NET "clk_100MHz" LOC = V10;NET "oclk" LOC = C9;NET "rst" LOC = C4;NET "SW[2]" LOC = V9;五、思考与探索(1) R-l-J型指令CPU实验结果记录表序号指令执行结果标志结论1 00004020 $8=0000_0000 0 0 正确2 00004820 $9=0000_0000 0 0 正确3 200a0014 $10=0000_0014 0 0 正确4 8d2b0010 $11=0000_0010 0 0 正确5 010b4020 $8=0000_2222 0 0 正确6 21290004 $9=0000_0004 0 0 正确7 214affff $10=000_0013 0 0 正确8 11400001 判断:$10不为0 0 0 正确0 0 正确9 08000003 返回去执行地址为0000_0010 的指令,即序号4:8d2b001010 ac0b0030 存储器地址:0000 0030 0 0 正确。

杭电数电课内实验

数字逻辑电路课内仿真实验第六章 QuartusII原理图设计初步一、实验目的:初步了解学习使用Quartus||软件进行电路自动化设计。

二、实验仪器:Quartus||软件。

三、实验内容:6-1 用Quartus||库中的宏功能模块74138和与非门实现指定逻辑函数按照6.3节和6.4节的流程,使用Quartus||完整图6-2电路的设计,包括:创建工程,在原理图编辑窗中绘制此电路,全程编译,对设计进行时序仿真,根据仿真波形说明此电路的功能,引脚锁定编译,编程下载于FPGA中进行硬件测试。

最后完成实验报告。

1、原理图2、波形设置3、仿真波形6-2 用两片7485设计一个8位比较器用两片4位二进制数值比较器7485串联扩展为8位比较器,使用Quartus||完成全部设计和测试,包括创建工程、编辑电路图、全程编译、时序仿真及说明此电路的功能、引脚锁定、编程下载,进行硬件测试。

最后完成实验报告。

1、原理图2、波形设置3、波形仿真6-3 设计8位串行进位加法器首先根据图4-33,用半加器设计一个全加器元件,然后根据图4-34,在顶层设计中用8个1位全加器构成8位串行进位加法器。

给出时序仿真波形并说明之,引脚锁定编译,编程下载于FPGA中进行硬件测试,最后完成实验报告,讨论这个加法器的工作速度。

1、原理图:半加器1位全加器8位串行进位全加器集成后的8位串行进位全加器2、波形设置3、波形仿真6-5 设计一个十六进制7段显示译码器用Verilog的case语句设计一个可以控制显示共阴7段数码管的十六进制码7段显示译码器。

首先给出此译码器的真值表,此译码器有4个输入端:D、C、B、A。

D是最高位,A 是最低位;输出有8位:p、g、f、e、d、c、b、a,其中p和a分别是最高和最低位,p控制小数点。

对于共阴控制,如果要显示A,输入DCBA=1010;若小数点不亮,则输出pgfedcba=01110111=77H,给出时序仿真波形并说明之,引脚锁定,下载于FPGA中对共阴数码管进行硬件测试。

杭电仪表实验指导书修改版共119页

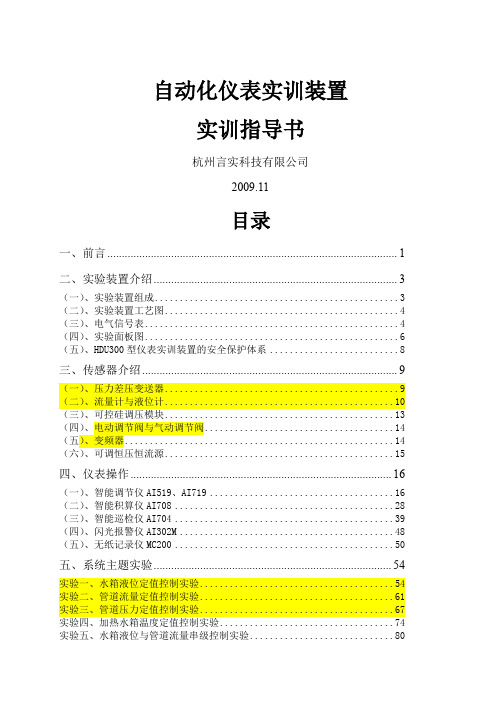

自动化仪表实训装置实训指导书杭州言实科技有限公司2009.11目录一、前言 (1)二、实验装置介绍 (3)(一)、实验装置组成 (3)(二)、实验装置工艺图 (4)(三)、电气信号表 (4)(四)、实验面板图 (6)(五)、HDU300型仪表实训装置的安全保护体系 (8)三、传感器介绍 (9)(一)、压力差压变送器 (9)(二)、流量计与液位计 (10)(三)、可控硅调压模块 (13)(四)、电动调节阀与气动调节阀 (14)(五)、变频器 (14)(六)、可调恒压恒流源 (15)四、仪表操作 (16)(一)、智能调节仪AI519、AI719 (16)(二)、智能积算仪AI708 (28)(三)、智能巡检仪AI704 (39)(四)、闪光报警仪AI302M (48)(五)、无纸记录仪MC200 (50)五、系统主题实验 (54)实验一、水箱液位定值控制实验 (54)实验二、管道流量定值控制实验 (61)实验三、管道压力定值控制实验 (67)实验四、加热水箱温度定值控制实验 (74)实验五、水箱液位与管道流量串级控制实验 (80)实验六、管式电阻炉温度定值控制实验 (84)实验七、孔板流量定值控制实验 (90)实验八、加热水温与流量串级控制实验 (96)实验九、无纸记录仪实验 (101)实验十、闪光报警仪实验 (104)实验十一、热电阻热电偶温度变送实验 (108)实验十二、霍尔转速测量实验 (112)实验十三、超声波液位计实验 (115)第一部分产品使用说明一、前言职业教育的根本是培养有较强实际动手能力和职业精神的技能型人才,而实训设备是培养这种能力的关键环节。

传统的实验设备更多是验证实验原理,缺乏对学生实际动手能力的培养,更无法实现生产现场的模拟,故障的发现,分析,处理能力等综合素质的培养。

为了实现职业技术人才的培养,必须建立现代化的实训基地,具有现代工厂情景的实训设备。

本仪表自动化实训装置把热工参数检测、变送处理、信号隔离、现场防爆、传感器仪表校验、自动化控制,数据通讯采集处理有机的糅合在一起,把理论知识与实际应用紧密的对接起来,使学生学到的知识通过本实训装置的实际应用得到检验、深化,同时加强了学生的实际动手能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

);

input [31:0] inst;

output reg [2:0] ALU_OP;

);

assign ALU_B=(rt_imm_s)?imm_data:rt_data;

//对源操作数运算,存于目的操作数

ex3 ALU(

.ALU_OP(ALU_OP),

.A(rs_data),

.B(ALU_B),

.F(ALU_Data),

.ZF(ZF),

.OF(OF)

);

//----

wire clk_temp;

output [1:0] PC_s;//PC选择器

output [25:0] address;//地址解析数据

//读指令

ex7 pc (

.clka(clk),

.douta(inst),

.rst(reset),

.PC(PC),

.PC_new(PC_new),

.PC_s(PC_s),

.R_Data_A(rs_data),

.douta(M_R_Data) // output [31 : 0] douta

);

assign W_Data = (wr_data_s[1])?PC_new:(wr_data_s[0]?M_R_Data:ALU_Data);

endmodule

pc模块:

module ex7(clka,douta,rst,PC,PC_new,PC_s,R_Data_A,imm_data,address

,ALU_B,rt_imm_s,Mem_Write,M_R_Data,ALU_Data,alu_mem_s,w_r_s,wr_data_s,PC_s,address);

input wire clk;

input reset;

output [2:0] ALU_OP;//操作符

output [31:0] inst;//指令存放

input [25:0] address;

wire [31:0]dina;

reg [0:0] wea=0;

assign PC_new=PC+4;

ex77 regrom (

.clka(clka), // input clka

.wea(wea), // input [0 : 0] wea

.addra(PC[7:2]), // input [5 : 0] addra

begin

//--------------------处理R型指令----------------------

if(inst[31:26]==6'b000000)//判断是否为R型

begin

rd=inst[15:11];//rd

rt=inst[20:16];//rt

rs=inst[25:21];//rs

实验报告

2016年5月11日 成绩:

姓名

周勇

学号

14071225

班级

计科5班

专业

计算机科学与技术

课程名称

《数字电路课程设计》

任课老师

章复嘉老师

指导老师

章复嘉老师

机位号

实验序号

10

实验名称

R-I-J指令CPU

实验时间

5月11日

实验地点

1教225

实验设备号

一、实验程序源代码

顶层架构CPU模块:

module cpu(clk,reset,ALU_OP,inst,rs,rt,rd,rs_data,rt_data,rd_data,ZF,OF,Write_Reg,PC,PC_new,rd_rt_s,W_Addr,imm,W_Data,imm_s,imm_data

.clka(clk_temp), // input clka

.wea(Mem_Write), // input [0 : 0] wea

.addra(ALU_Data[5:0]), // input [5 : 0] addra

.dina(rt_data), // input [31 : 0] dina

output [31:0]M_R_Data;//从数据rom读出来的数据

output [31:0]ALU_Data;//ALU运算出来的结果,根据alu_mem_s选择由M_W_Data或者W_Data来赋值

output alu_mem_s;//看上面

output [1:0] w_r_s;

output [1:0] wr_data_s;

output [15:0] imm; //立即数

output [31:0] imm_data;//被扩展的立即数

output imm_s;//是否需要扩展

output rt_imm_s;//B端选择rt或者是imm

output [31:0] ALU_B;//ALU_B端口数据

output Mem_Write;//是否写入数据rom

output [31:0] PC;

output [31:0] PC_new;

output ZF;

output OF;

output Write_Reg;//是否写入

output [31:0] W_Data;

output rd_rt_s; //控制那个作为目的寄存器

output [4:0]W_Addr;//目的操作数地址

wire d_outn;

reg d_out=0;

assign clk_temp = clk ^ d_out ;

assign d_outn = ~d_out ;

//----

always@(posedge clk_temp)

begin

d_out <= d_outn ;

end

//数据存储器

Data_Rom Datarom (

output reg Mem_Write;

output reg alu_mem_s;

output reg [25:0] address;

output reg [1:0] w_r_s;

output reg [1:0] wr_data_s;

output reg [1:0] PC_s;

input ZF;

always@(*)

6'b101011:begin ALU_OP=3'B110; Write_Reg=1;PC_s=2'b00;end

6'b000100:begin ALU_OP=3'B111; Write_Reg=1;PC_s=2'b00;end

6'b001000:begin ALU_OP=3'B100; Write_Reg=0;PC_s=2'b01;end

2'b00: PC<=PC_new;

2'b01: PC<=R_Data_A;

2'b10: PC<=PC_new+(imm_data<<2);

2'b11: PC<={PC_new[31:28],address,2'b00};

endcase

end

end

endmodule

analysis_inst模块:

module analysis_inst(

rd_rt_s=1;//rt作为目的存储器

rt_imm_s=1;//imm作为源操作数

// alu_mem_s=0;//以alu结果输出

w_r_s=2'b01;

Write_Reg=1;

wr_data_s=2'b00;

PC_s=2'b00;

//判断属于那条指令

case(inst[31:26])

6'b001000: begin imm_s=1; ALU_OP=3'B100;end

reg1 Reg(

.R_Addr_A(rs),

.R_Addr_B(rt),

.Clk(clk),

.W_Addr(W_Addr),

.W_Data(W_Data),

.R_Data_A(rs_data),

.R_Data_B(rt_data),

.Reset(reset),

.Write_Reg(Write_Reg) //不写入

.PC_s(PC_s),

.ZF(ZF)

);

//读取源操作数的值:

assign W_Addr = (w_r_s[1])?5'b11111:((w_r_s[0])?rt:rd);

assign imm_data = (imm_s)?{{16{imm[15]}},imm}:{{16{1'b0}},imm};

.imm_data(imm_data),

.address(address)

//解析指令

);

analysis_inst analysis_inst(

.inst(inst),

.ALU_OP(ALU_OP),

.rs(rs),

.rt(rt),

.rd(rd),

.Write_Reg(Write_Reg),

.imm(imm),

output reg [4:0] rs;

output reg [4:0] rt;

output reg [4:0] rd;

output reg Write_Reg;

output reg [15:0] imm;

output reg rd_rt_s;

output reg imm_s;