第5章 存储器(讲义)

S3C2410中文手册第5章_存储器控制器

S3C2410A 中文数据手册(第五章)

杭州立宇泰电子有限公司编著(Version 1.0)

SDRAM的BANK地址引脚连接

表 5-2. SDRAM Bank 地址结构

Bank大小 2MB 4MB 8MB 16MB

32MB 64MB 128MBห้องสมุดไป่ตู้

总线宽度 x8 x16 x8 x16 x32 x16 x32 x8 x8 x16 x16 x32 x32 x8 x8 x16 x16 x32 x32 x8 x16 x16 x16 x32 x32 x16 x32 x8 x16 x32 x16 x32 x8 x32

0x307f_ffff

0x30ff_ffff

0x3000_0000 0x31ff_ffff

0x3000_0000 0x3000_0000

0x33ff_ffff

0x37ff_ffff

Bank 7

起始 0x3020_0000 0x3040_0000 0x3080_0000

地址

0x3100_0000

终址 地址

OM0 (操作模式0) 0 1 0 1

导入ROM 数据宽度 Nand Flash Mode

16-bit 32-bit Test Mode

存储器(SROM/SDRAM)地址引脚的连接

MEMORY ADDR. PIN

A0 A1

S3C2410A ADDR. @ 8-bit DATA BUS A0 A1

•••

x32

(8M x 16 x 4banks) x 2 ea

5.2.1nWAIT 引脚的作用

如果对每个bank使能WAIT功能,当对某个bank区进行访问时,nOE的低电平有效时间 就会在nWAIT引脚的控制下延长。从tacc-1时刻开始检测nWAIT的状态。在采样到nWAIT为 高电平后的下一个时钟,nOE将恢复高电平。nWAIT对nWE信号的作用与对nOE信号相同。

微机原理 第5章5.2.4串操作类指令

第5章

2、REPZ重复前缀指令

REPZ

;每执行一次串指令,CX减1 每执行一次串指令,CX减 并判断ZF是否为0 ZF是否为 ;并判断ZF是否为0, 只要CX CX= ZF= 重复执行结束 ;只要CX=0或ZF=0,重复执行结束

【例5.42】比较S1、S2两个数据串是否相同,不同则 】 比较 、 两个数据串是否相同, 两个数据串是否相同 例5.42:比较字符串 : 跳到NOMATCH执行。 执行。 跳到 执行 S1 DB 0,1,1,0,0 S2 DB 0,1,1,1,0 …… CLD LEA SI,S1 ;源串偏移地址赋值给 源串偏移地址赋值给SI 源串偏移地址赋值给 LEA DI,ES:S2 ;目的串偏移地址赋值给 目的串偏移地址赋值给SI 目的串偏移地址赋值给 MOV CX,5 ;源串和目的串的数据个数 源串和目的串的数据个数 AGAIN: CMPSB ;源串与目的串相减,标志位 源串与目的串相减, 源串与目的串相减 JNE NOMATCH ;有任一不同,跳到NOMATCH 有任一不同,跳到 有任一不同 DEC CX ;数据串没比较完,继续比较 数据串没比较完, JNZ AGAIN 数据串没比较完 NOMATCH:

第5章

四、串比较CMPS

将主存中的源操作数减去目的操作数, 将主存中的源操作数减去目的操作数,以便设 置标志(影响AF,ZF,PF,SF,OF,CF) , 进而比 置标志 ( 影响 ) 较两操作数之间的关系 CMPSB ;字节串比较:DS:[SI]-ES:[DI] 字节串比较:DS:[SI]- SI←SI± DI←DI± ;SI←SI±1,DI←DI±1 CMPSW ;字串比较:DS:[SI]-ES:[DI] 字串比较:DS:[SI]- SI←SI± DI←DI± ;SI←SI±2,DI←DI±2

第5章 存储系统

控制 输入 电路

读 /写 选 片

地址反相器

A5 A6 A7 A8 A9

第14页 2012年6月11日星期一

第5章 存储系统 1.存储体 一个基本存储电路表示一位二进制位 存储电路有规则的组合,就是存储体,即存储阵列 2.外围电路 包括地址译码器、I/O电路、片选控制、输出驱 动电路 3.地址译码方式 (1)单译码方式 只有行方向的译码器 (2)双译码方式 行译码(X译码)和列译码(Y译码)

可擦除可编程ROM—EPROM :用特殊手段擦除, 然后可重新多次写入

电可擦除可编程ROM—E2PROM :用电方式进行 在线擦除

第24页 2012年6月11日星期一

第5章 存储系统

5.4.1 掩膜型ROM(Read Only Memory)

其基本存储电路可由二极管、晶体管、MOS管构成

X选线 X选线 X选线

基本存储电路如图示(6管) X 选 择 线 T1、T2:双稳态触发器 T3、T4:负载管 T T5、T6:控制门 T7、T8:控制管 T1截止 →A为1 →T2导通 → ↑ B为0 ← ← T2截止为另一种稳态

第11页

Vc c

1T

5

3

T4 B T2

0

T6

─ ─

T1

A

→

D0 T7

D0 T8 I /O

I /O

第15页 2012年6月11日星期一

第5章 存储系统 (1)单译码方式

A0 A1 · · An 地 址 译 码 · · · · · · · ··· · · ·

···

写 读选通 写选通

I/O 控 制

读 写

I/O 控 制

读

第16页

2012年6月11日星期一

【微机原理】5.1-存储器分类

§ 5.1 存储器分类 § 5.2 随机存取存储器RAM § 5.3 只读存储器ROM § 5.4 存储器与CPU的连接 § 5.5 高速缓冲存储器*

*供选用

第5章 存储器 §5.1 存储器分类

按地位 和

作用分

存储器的分类

其它分类方法:

按存储介质分类 半导体存储器、磁表面存储器、光表面存储器等

▪各类小型存储介质,如

CF卡(紧凑式闪存) SM卡(固态软盘卡)

SD卡(安全数码卡) MMC卡(多媒体卡)

MS卡(记忆棒)

XD卡(尖端数字图像卡) 等

性能好、功耗低、体积小、重量轻。

U盘 SD卡

CF卡

XD卡 256GB固态盘

记忆棒 MMC卡

6)新的非易失性存储器技术

正在涌现的非易失性存储器技术,包括: ▪ 铁电介质存储器(FeRAM) ▪ 磁介质存储器(MRAM) ▪ 奥弗辛斯基效应一致性存储器(OUM) ▪ 聚合物存储器(PFRAM) ▪ 导电桥RAM(CBRAM) ▪ 纳米RAM(NRAM)等

位于主机内部,简称内存或主存,存放系统软件和正执行的 程序和使用的数据,CPU可直接访问内存。

为与CPU速度匹配,内存采用速度较快的半导体存储器。 按照数据保存方法和读写过程,半导体存储器可分成RAM和

ROM两大类。

1. RAM 随机存取存储器

Random Access Memory

可随机写入和读出,访问速度快,但断电后内容会全部丢失,即 具有易失性。

2)DRAM(Dynamic RAM,动态RAM)

➢用MOS开关管控制电容的充放电来存储信息,电路简单,但 存取速度慢,电容上存储的信息会丢失,需要刷新。

➢容量大,价格便宜,PC机上的内存都采用DRAM,而且做成 内存条,便于扩充内存容量。

《计算机专业英语》谢希仁第二版-第5章讲义PPT课件

Computer English

Chapter 5 Operating System

.

1

Key points: Function and structure of

entrust v.委托

criteria n.标准

constraint n.约束, 强制, 局促 partition vt.分区

apriori 预先,事前

perceive v.感知, 感到, 认识到

suboptimal adj.未达最佳标准的

preemption n.抢占

sequential adj. 顺序的,串行的 concurrent adj.并发的, 并行的

在资源分区方式中,操作系统预先决定把哪些资源分配给某个 用户计算使用,这种方法也称为静态分配,因为分配是在程序 执行前进行的。静态资源分配易于实现,但由于它不是从程序 的实际需要出发,而是根据程序预先提出的需求来做决定,所 以容易导致系统利用率下降。

.

10

5.1.1 Resource allocation and related functions

.

12

5.1.1 Resource allocation and related functions

In the partitioned resource allocation approach, the OS decides on the resources to be allocated to a program based on the number of resources and the number of programs in the system. For example, an OS may decide that a program can be allocated 1 MB of memory, 2000 disk blocks and a monitor. Such a collection of resources is referred to as a partition. In effect, a set of partitions can be predefined in the system. The resource table can have an entry for each resource partition. When a new program is to be started, an available partition is allocated to it.

计算机操作系统教程(张尧学(第三版)第五章

精品课程系列-计算机学院版权所有

关于动态地址重定位可以如下图所示的过程说明:

制 作 者 : 郭 平 、 王 在 模 、 何 静 媛

用户程序的虚地址空间 0 100 1KB 0 内存 基地址寄存器 操作系统 22628 22KB 22528

XXXXX

20KB 22KB 22KB+100 XXXXXX

制 作 者 : 郭 平 、 王 在 模 、 何 静 媛

精品课程系列-计算机学院版权所有

动态地址重定位

制 作 者 : 郭 平 、 王 在 模 、 何 静 媛

动态地址重定位是在程序执行过程中,在CPU访问 内存之前,将要访问的程序或数据地址转换成内存地 址。动态地址重定位依靠硬件地址变换机构完成。

硬件地址转换机构一般由一个“基地址寄存器” 和一个“虚地址寄存器”组成,用户程序不做任何修 改地装入分配给它的存储区域。当调度到用户程序运 行时,则转换成实际的物理地址。

精品课程系列-计算机学院版权所有

分区的分配与释放

制 作 者 : 郭 平 、 王 在 模 、 何 静 媛

分区的分配: 若采用的是一个队列的管理方案,则当一个分区被释放时, 需要在队列中选出一个作业运行,可以有以下几种方案: (1)选出第一个可容纳的作业。该方案虽然实现简单,选择 率高,但是可能会因为一个小作业进入而浪费掉该分区的大部分 存储空间,存储利用率不高。 (2)在队列中找出该分区能容纳的最大的作业。由于每个分 配出的分区产生出的内部碎片小,因此,此方案存储空间的利用 率高;缺点是对小作业不公平。

22kb10022kb300023kbd图51地址变换示意图郭平王在模何静媛其中程序a中的一条入口地址为3000的一条指令为call100其中程序a中的一条入口地址为3000的一条指令为call100在装入内存之后由于程序的起始地址不再为0故程序中的指令需要做相应的转换

电气控制与plc应用技术课件教学配套课件黄永红第五章

S7-200 CPU输入、输出的操作

I/O映像区实际上就是外部输入输出设备状态的映像区,PLC 通过I/O映像区的各个位与外部物理设备建立联系。I/O映像区 每个位都可以映像输入、输出模块上的对应端子状态。

3. 辅助继电器(M)

• 辅助继电器(M)的地址格式为: • 位地址:M[字节地址].[位地址],如M0.2、

],如LB33、LW44、LD55。 • CPU226模块局部存储器的有效地址范围为:L(

0.0~63.7);LB(0~63);LW(0~62);LD (0~60)。

6. 顺序控制继电器(S)

• 顺序控制继电器(S)用于顺序控制或步进控制。 • 顺序控制继电器(S)使用时可以按位、字节、字

、双字访问,其地址格式为: • 位地址:S[字节地址].[位地址],如S3.1、

5.1 S7-200 PLC的编程语言

1.梯形图(LAD) 2. 功能块图(FBD) 3. 语句表(STL)

1.梯形图(LAD)

▲ 梯形图(LAD)与电 气控制电路图相呼应。 ▲沿用了继电器、触点、 串并联等术语 ▲简化了图形符号 ▲增加了特殊功能的指令 ▲信号流向清楚、简单、 直观、易懂。

I0.0 Q0.1

=I

Q3.1

LD

I3.1

AN

I3.2

=I

Q3.1

语句表可以编写梯形图和功能块图无法 编写的程序。

5.2 S7-200 PLC的数据类型与存储区域

5.2.1 位、字节、字、双字和常数

常数的几种表示形式:

进制 二进制 十进制 十六进制 ASCII 浮点数

书写格式

举例

2#二进制数值

2#0101011100010

5119.7);VB(0~5119);VW(0~5118);VD(0~ 5116)。

计算机系统结构多媒体教程课件_第五章 多处理机系统2

2013-8-31 4

一、问题由来

• 当每个处理机都有自己专用的cache时, 系统效率提高,但产生cache不一致问题。

2013-8-31

5

1、共享可写数据引起的不一致

2013-8-31

6

2、进程迁移引起数据不一致

2013-8-31

7

2、进程迁移引起数据不一致

• P1、p2都有共享数据X拷贝,p2修改了X,并 采用写通过策略,同时修改内存中的X。当该 进程迁移到P1上,这时P1中仍然是X。

目录表法: (非总线结构)

主存设置目录表〈数据块地址,指示器、标志 位〉,某PE写Cache时,通知指示器中的PE处理。

2013-8-31 13

5.3.4 多处理机系统的特点

1.结构灵活性 • 相比并行处理机的专用性,多处理机系 统是要把能并行处理的任务、数组,以 及标量都进行并行处理,有较强的通用 性。因此多处理机系统要能适应更多样 化的算法,具有更灵活的结构,以实现 各种复杂的机间互联模式。

2013-8-31 14

ห้องสมุดไป่ตู้

多处理机系统的特点(cont.)

2.程序并行性 • 在多处理机中,并行性存在于指令外部, 即表现在多任务之间。为充分发挥系统 通用性的优点,便要利用多种途径:算 法、程序语言、编译、操作系统以至指 令、硬件等,尽量挖掘各种潜在的并行 性。

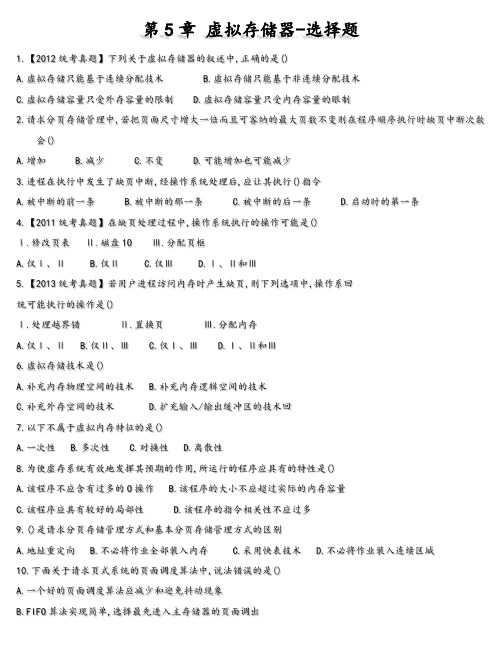

第5章虚拟存储器-选择题

第5章虚拟存储器-选择题1.【2012统考真题】下列关于虚拟存储器的叙述中,正确的是()A.虚拟存储只能基于连续分配技术B.虚拟存储只能基于非连续分配技术C.虚拟存储容量只受外存容量的限制D.虚拟存储容量只受内存容量的眼制2.请求分页存储管理中,若把页面尺寸增大一倍而且可客纳的最大页数不变则在程序顺序执行时缺页中断次数会()A.增加B.减少C.不变D.可能增加也可能减少3.进程在执行中发生了缺页中断,经操作系统处理后,应让其执行()指令A.被中断的前一条B.被中断的那一条C.被中断的后一条D.启动时的第一条4.【2011统考真题】在缺页处理过程中,操作系统执行的操作可能是()Ⅰ.修改页表Ⅱ.磁盘1O Ⅲ.分配页框A.仅Ⅰ、ⅡB.仅ⅡC.仅ⅢD.Ⅰ、Ⅱ和Ⅲ5.【2013统考真题】若用户进程访问内存时产生缺页,则下列选项中,操作系回统可能执行的操作是()Ⅰ.处理越界错Ⅱ.置换页Ⅲ.分配内存A.仅Ⅰ、ⅡB.仅Ⅱ、ⅢC.仅Ⅰ、ⅢD.Ⅰ、Ⅱ和Ⅲ6.虚拟存储技术是()A.补充内存物理空间的技术B.补充内存逻辑空间的技术C.补充外存空间的技术D.扩充输入/输出缓冲区的技术回7.以下不属于虚拟内存特征的是()A.一次性B.多次性C.对换性D.离散性8.为使虚存系统有效地发挥其预期的作用,所运行的程序应具有的特性是()A.该程序不应含有过多的O操作B.该程序的大小不应超过实际的内存容量C.该程序应具有较好的局部性D.该程序的指令相关性不应过多9.()是请求分页存储管理方式和基本分页存储管理方式的区别A.地址重定向B.不必将作业全部装入内存C.采用快表技术D.不必将作业装入连续区城10.下面关于请求页式系统的页面调度算法中,说法错误的是()A.一个好的页面调度算法应减少和迎免抖动现象C.LRU算法基于局部性原理,首先调出最近一段时间内最长时间未被访问过的页面D. CLOCK算法首先调出一段时间内被访问次数多的页面11考虑页面置换算法,系统有m个物理块供调度,初始时全空,页面引用串长度为P,包含了n个不同的页号,无论用什么算法,缺页次数不会少于()A.mB.pC.nD. min(n, n)12.在请求分页存储管理中,若采用FFO页面淘汰算法,则当可供分配的页数增加时,缺页中断的次数()A.减少B.增加C.无影响D.可能増加也可能减少13.设主存容量为IMB,外存容量为400MB,计算机系统的地址寄存器有32位,那么虚拟存储器的最大容量是()A. IMBB. 401MBC. IMB+232MBD.232B14.虚拟存储器的最大容量()A.为内外存容量之和B.由计算机的地址结构决定C.是任意的D.由作业的地址空间决定15.某虚拟存储器系统采用页式内存管理,使用LRU页面替換算法,考虑页面回访问地址序列18178272183821317137.假定内存容量为4个页面,开给时是空的,则页面失效次数是()A.4B.5C.6D.716.导致LRU算法实现起来耗费高的原因是()A.需要硬件的特殊支持B.需要特珠的中断处理程序C.需要在页表中标明特殊的页类型D.需要对所有的页进行排序17.在虚拟存储器系统的页表项中,决定是否会发生页故障的是()A.合法位B.修改C.页类型D.保护码18.在页面置换策略中,()策略可能引起抖动A. FIFOB. LRUC.没有一种D.所有19.虚拟存储管理系统的基础是程序的()理论A.动态性B.虚拟性C.局部性D.全局性20.用()方法可以实现虚拟存储A.分区合并B.覆盖、交换C.快表D.段合并21.请求分页存储管理的主要特点是()A.消除了页内零头B.扩充了内存C.便于动态链接D.便于信息共享22.在请求分页存储管理的页表中增加了若千项信息,其中修改位和访问位供()参考A.内存空间太小B.CPU运行速度太慢C.CPU调度算法不合理D.页面置换算法不合理24.在页面置換算法中,存在 Belady现象的算法是()A.最佳页面置换算法(OPT)B.先进先出置换算法(FIFO)C.最近最久未使用算法(LRU)D.最近未使用算法(NRU)25.页式虚拟存储管理的主要特点是()A.不要求将作业装入主存的连续区域B.不要求将作业同时全部装入主存的连续区域C.不要求进行缺页中断处理D.不要求进行页面置换26.提供虚拟存储技术的存储管理方法有()A.动态分区存储管理B.页式存储管理C.请求段式存储管理D.存储覆盖技术27.在计算机系统中,快表用于()A.存储文件信息B.与主存交换信息C.地址变换D.存储通道程序28.在虚拟分页存储管理系统中,若进程访问的页面不在主存中,且主存中没有可用的空闲帧时,系统正确的处理顺序为()A.决定淘汰页→页面调出一缺页中断一页面调入B.决定淘汰页→页面调入一缺页中断一页面调出C.缺页中断→决定淘汰页一页面调出一页面调入D.缺页中断→决定淘汰页→页面调入→页面调出29.已知系统为32位实地址,采用48位虚拟地址,页面大小为4KB,页表项大小为8B,假设系统使用纯页式存储,则要采用()级页表,页内偏移()位A.3,12B.3,14C.4,12D.4,1430.下列说法中,正确的是()Ⅰ.先进先出(FIFO)页面置換算法会产生 Belady现象Ⅱ.最近最少使用(LRU)页面置換算法会产生 Belady现象Ⅲ.在进程运行时,若其工作集页面都在虚拟存储器内,则能够使该进程有效地运行否则会出现频繁的页面调入/调出现象IV.在进程运行时,若其工作集页面都在主存储器内,则能够使该进程有效地运行则会出现频繁的页面调入/调出现象A.Ⅰ、ⅢB.Ⅰ、ⅣC.Ⅱ、ⅢD.Ⅱ、Ⅳ31.测得某个采用接需调页策略的计算机系统的部分状态数据为:CPU利用率为20%,用于交换空间的磁盘利用率为97.7%,其他设备的利用率为5%由此判断系统出现异常,这种情况下()能提高系统性能A.安装一个更快的硬盘 C.增加运行进程数用率为99.7%,其他1O设备的利用率为5%,下面()措施将可能改进CPU的利用率Ⅰ.增大内存的容量Ⅱ.增大磁盘交换区的容量Ⅲ.减少多道程序的度数IV.增加多道程序的度数 V.使用更快速的磁盘交换区 VI.使用更快速的CPUA.Ⅰ、Ⅱ、Ⅲ、IVB.Ⅰ、ⅢC.Ⅱ、Ⅲ、VD.Ⅱ、Ⅵ33.【2011统考真题】当系统发生抖动时,可以采取的有效措施是()Ⅰ.撤销部分进程Ⅱ.增加磁盘交换区的容量Ⅲ.提高用户进程的优先级A.仅ⅠB.仅ⅡC.仅ⅢD.仅Ⅰ、Ⅱ34.【2014统考真题】下列措施中,能加快虚实地址转换的是()Ⅰ.增大快表(TLB)容量Ⅱ.让页表常驻内存Ⅲ.增大交换区(swap)A.仅ⅠB.仅ⅡC.仅Ⅰ、ⅡD.仅Ⅱ、Ⅲ35.[2014统考真题】在页式虚拟存管理系统中,采用某些页面置換算法会出回现 Belady异常现象,即进程的缺页次数会随着分配给该进程的页柜个数的增加而增加。

计算机组成原理讲义

计算机组成原理讲义计算机组成原理是一门研究计算机硬件和软件协同工作的学科。

它研究计算机系统的组成、结构、工作原理和设计方法,涉及到计算机的各个层次、各个组成部分和各种操作。

计算机组成原理作为计算机科学和计算机工程的基础课程,对于理解计算机的工作原理和提高计算机系统设计和性能优化具有重要意义。

首先,计算机组成原理涵盖了计算机的硬件组成。

计算机的硬件部分主要包括中央处理器(CPU)、存储器、输入输出设备和总线等。

中央处理器是计算机的核心部件,又被称为计算机的大脑。

它包括算术逻辑单元(ALU)和控制单元(CU),负责执行指令、算术运算和逻辑运算等。

存储器用于存储数据和指令,分为主存储器(RAM)和辅助存储器(硬盘、固态硬盘等)。

输入输出设备用于与计算机交互,包括键盘、鼠标、显示器、打印机等。

总线用于连接计算机的各个组成部分,包括数据总线、地址总线和控制总线等。

了解计算机硬件组成,对于设计和优化计算机系统具有重要意义。

其次,计算机组成原理涉及计算机的工作原理。

计算机的工作原理主要包括数据的表示和存储、指令的执行和流水线技术等。

数据的表示和存储是计算机进行数据处理的基础。

计算机使用二进制表示数据,将数据存储在内存中。

指令的执行是计算机进行计算和逻辑操作的基本单元。

计算机通过解码和执行指令,对数据进行处理。

流水线技术是提高计算机执行效率的一种重要方法。

通过将指令执行分解成多个阶段,可以提高指令的吞吐量。

计算机组成原理对于理解计算机工作原理和提高计算机系统性能具有重要意义。

最后,计算机组成原理涉及计算机的设计方法。

计算机的设计方法包括指令系统的设计、组合逻辑电路的设计和微程序设计等。

指令系统的设计是计算机体系结构的基础,决定了计算机的功能和性能。

组合逻辑电路设计是实现计算机各个功能模块的基础,包括加法器、乘法器、寄存器和控制电路等。

微程序设计是实现指令的执行和控制的基础,将指令分解成微指令并存储在控制存储器中。

计算机原理存储器

计算机原理存储器

计算机原理中,存储器是指计算机用来存储数据和程序的部件。

存储器一般分为内存和外存两种类型。

内存是计算机中用于存储当前运行程序和数据的存储器。

它分为主存和辅存两部分。

主存是计算机中最主要的存储器,由半导体存储芯片构成,通常包括随机访问存储器(RAM)和只

读存储器(ROM)。

RAM具有读写功能,用于临时存储运行

程序和数据,数据可以快速读取和写入。

而ROM是只读存储器,其中的数据是固化的,无法进行修改。

主存的容量通常较小,但速度快。

外存主要是指硬盘、光盘等可以作为辅助存储器使用的设备。

相比主存,外存容量大,但速度较慢。

外存被用于长期存储程序和数据,能够持久保存。

计算机在运行过程中,通常需要将外存中的数据加载到主存中进行操作。

存储器在计算机中起到了至关重要的作用,它直接影响到计算机的性能和数据的处理速度。

不同类型的存储器在容量、速度和价格等方面有所差异,计算机系统需要根据不同的需求来选择合适的存储器组合。

存储器工作原理

存储器工作原理

存储器是计算机中用于存储和读取数据的设备。

它是计算机内部的一个重要组成部分,其工作原理可以分为存储和检索两个过程。

在存储数据的过程中,存储器将数据按照一定的格式和顺序存放在不同的存储单元中,如字节、字等。

每个存储单元都有一个唯一的地址,通过地址可以找到对应的存储单元。

数据在存储器中的位置由计算机的操作系统进行管理。

当计算机需要从存储器中读取数据时,它会根据指定的地址来找到对应的存储单元,并将存储单元中的数据读取出来。

读取的过程类似于找到书架上特定位置的一本书并将其取下。

存储器的工作原理可以分为随机访问存储器(RAM)和只读存储器(ROM)两种类型。

RAM是一种易失性存储器,也就是说,当计算机断电时,其中存储的数据会丢失。

RAM可以随机访问,即可以根据指定的地址直接读取或写入数据。

RAM通常被用作临时存储器,用于存放正在运行的程序、临时数据和用户输入等。

ROM是一种非易失性存储器,其中的数据不会因为计算机断电而丢失。

ROM中的数据通常是由厂商预先写入的,用户无法进行修改。

ROM常用于存储计算机的固件和操作系统等关键信息。

总的来说,存储器通过存储和检索数据的过程来实现数据的长期保存和快速读取。

它在计算机系统中扮演着重要的角色,对于计算机的运行和数据处理起着至关重要的作用。

2015_射频识别技术-第5章

5000m/s。

(2)实现电子器件的优越性能。 (3)易于工业化生产。

(4)性能稳定。

(5)以能在金属和液体中正常工作而著称。

3.声表面波标签

SAW标签是由叉指换能器和若干反射器组成。如果将

反射器组按某种特定的规律设计,使其反射信号表示规

定的编码信息,那么读写器接收到的反射高频电脉冲串

就带有该物品的特定编码。

5.1一位电子标签

1位的电子标签不需要芯片,可以采用射频法、微波法、分 频法、智能型、电磁法和声磁法等多种方法进行工作。下面 以射频法为例,介绍1位电子标签的工作原理。

射频法工作原理

射频法工作系统由读写器(检测器)、电子标签和去激活器三部分组成。电子标

签采用L-C振荡电路进行工作,振荡电路将频率调谐到某一振荡频率上。射频法

和MIFARE(r)PLUS的兼容性,与现有的MIFARE(r)读写设备完全兼容。

MIFARE(r)PRO的物理尺寸使该产品可以用来生产ISO标准的智能卡片。 MIFARE(r)PRO片内的微处理器是80C51,80C51可以工作在接触和非接触

微处理器不仅是微型计算机的核心部件,也是各种数字化智

能设备的关键部件。如今微处理器已经无处不在,无论是智 能洗衣机、移动电话等家电产品,还是汽车引擎控制、数控 机床等工业产品,都要嵌入各类不同的微处理器。

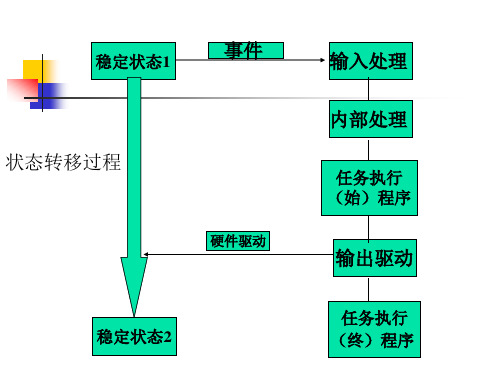

5.5.2操作系统命令的处理过程

读写器向电子标签发送的命令,经电子标签的天线进入射频 模块,信号在射频模块中处理后,被传送到操作系统中。操

快。接触式IC卡的读写操作速度较慢,操作也不方便,每次读写时必须

把卡正确地插入到读写器的口槽才能完成数据交换,这样,在公交、考 勤等需要频繁读写卡的场合就很不方便,而且读写器的触点和卡片上IC

现代交换原理 第5章 内部分析处理.ppt

I=32*p+q

以TST三级交换网络为例。任何一对入、出线之间都存 在32条内部链路,为了实现交换,这32条链路中至少应有一条空 闲,即组成该链路的1-2级间链路和2-3级间链路必须同时空闲。 控制系统在通路选择时,首先调出对应入线的第一级链路的忙闲

状态,再调出对应出线的第二级链路的忙闲状态,通过运算找出 可以使用的空闲内部链路。运算过程如下,其中“0”表示链路忙, “1”表示链路闲。

第一级链路的忙闲状态: 11010011101001001101101111000010

第二级链路的忙闲状态: 01010101000111100000011111001000

与运算结果:

01010001000001000000001111000000

运算结果表明有8条内部链路空闲,可以从中选择任意一条空闲 的使用。

去话分析

主叫摘机

主叫用户 数据

收号前的 准备工作

去话接续

硬件变化

输入信息

分析程序

输出

用户数据:呼叫类别,端子类别, 线路类别,运用类别, 话机类别,计费类别, 出局类别,优先级别, 服务类别等。

去话分析的数据及程序运行的流程

2. 数字分析: 是对主叫用户所拨被叫 (号码分析) 号码进行分析,以决定

来话 硬件变化

被叫用户 数据

输入信息

来话分析

被叫用户 分析

分析程序

叫出被叫 输出

被叫用户数据

被叫类别 计费类别 来话检查 忙闲状态 服务类别

被叫用户设备号

来话分析的数据及程序运行的流程

4.状态分析:对引起的状态变化的

因素进行分析,以确

定任务及下一状态号码等。

第5章(第5版)李朝青-单片机原理及接口技术(第5版)课件

二、查询方式程序流程图

03:42

输入状态信息

N

准备好?

Y

传送数据

三、查询方式的过程

启动外设设备 延迟

传送数据

查询方式的过程: 查询——等待——数据传送,待到 下一次数据传送时则重复上述过程。

03:42

四、查询方式的特点

优点:通用性好,可以用于各类外设和CPU 间的数据传送。

• 缺点:CPU在完成一次数据传送后要等待很 长时间才能进行下一次的传送。在等待过程 中,CPU不能进行其他操作,所以效率比较 低。

03:42

中断技术实现的功能 • 1、分时操作

• 2、实时处理 • 3、故障处理

03:42

1、分时操作

• 计算机的中断系统可以使CPU与外设同时 工作。

• CPU在启动外设后,便继续执行主程序; 而外设被启动后,开始进行准备工作。当 外设准备就绪时,就向CPU发出中断请求, CPU响应该中断请求并为其服务完毕后, 返回原来的断点处继续运行主程序。外设 在得到服务后,也继续进行自己的工作。

为0,则相应的中断源规定为低级中断。

03:42

3、中断优先级排列顺序

• 当同时接收到几个同一优先级的中断请求时,响应哪个中断源则取决于 内部硬件查询顺序。

• 其优先级顺序排列如 图所示。

中断源

同级内的中断优先级

外部中断0中断 定时器/计数器T0溢出中断 外部中断1 定时器/计数器T1溢出中断 串行口中断

(b)用位操作指令

SETB ET0;定时器/计数器0允许中断 SETB ET1;定时器/计数器1允许中断 SETB EA ;CPU开中断

03:42

三、中断优先级控制

1、89C51/S51的中断优先级 2、中断优先级寄存器IP 3、中断优先级排列顺序 4、中断优先级控制实现的功能 5、例5-2

第5章 硬盘

硬盘的内部结构

将硬 盘面 板揭 开后, 内部 结构 即可 一目 了然。

硬盘的内部结构

细 看 硬 盘 内 部 结 构 。

硬盘的内部结构

细 看 硬 盘 内 部 结 构 。

浮动磁头组件

是硬盘中最精密的部位之一,它由读写磁头、 传动手臂、传动轴三部份组成。 磁头是硬盘技术中最重要和关键的一环,实际 上是集成工艺制成的多个磁头的组合,它采用 了非接触式头、盘结构,加后电在高速旋转的 磁盘表面移动,与盘片之间的间隙只有0.1~ 0.3 μm ,这样可以获得很好的数据传输率。现 在转速为7200RPM的硬盘飞高一般都低于0.3 μm,以利于读取较大的高信噪比信号,提供数 据传输率的可靠性。

硬盘的工作模式

硬盘的工作模式主要有三种,分别是:

NORMAL LBA LARGE。

NORMAL模式

NORMAL(普通模式)是最早的 IDE 方 式,在硬盘访问时,BIOS 和 IDE 控制器 对参数不做任何转换。该模式支持的最 大硬盘的容量为528MB。也就是说,在 此模式下,硬盘的实际物理容量再大, 也只能用到其中的 528M。

主轴组件

前置控制电路

前置电路控制磁头感应的信号、主轴电 机调速、磁头驱动和伺服定位等,由于 磁头读取的信号微弱,将放大电路密封 在腔体内可减少外来信号的干扰,提高 操作指令的准确性。

硬盘的性能指标

硬盘也是计算机的重要部件,同样对计 算机的整体性能起着决定性的作用。我 们就介绍一下硬盘主要的性能指标。

主轴转速

随着硬盘转速的提升, 会使硬盘的发热量不 断升高,若硬盘散发 的热量不能及时地传 导出去,硬盘就会升 温。为此,可以在硬 盘上安装一个硬盘散 热风扇,增强散热效 果。

数据结构讲义第5章-数组和广义表

5.4 广义表

5)若广义表不空,则可分成表头和表尾,反之,一对表头和表尾 可唯一确定广义表 对非空广义表:称第一个元素为L的表头,其余元素组成的表称 为LS的表尾; B = (a,(b,c,d)) 表头:a 表尾 ((b,c,d)) 即 HEAD(B)=a, C = (e) D = (A,B,C,f ) 表头:e 表尾 ( ) TAIL(B)=((b,c,d)),

5.4 广义表

4)下面是一些广义表的例子; A = ( ) 空表,表长为0; B = (a,(b,c,d)) B的表长为2,两个元素分别为 a 和子表(b,c,d); C = (e) C中只有一个元素e,表长为1; D = (A,B,C,f ) D 的表长为4,它的前三个元素 A B C 广义表, 4 A,B,C , 第四个是单元素; E=( a ,E ) 递归表.

以二维数组为例:二维数组中的每个元素都受两个线性关 系的约束即行关系和列关系,在每个关系中,每个元素aij 都有且仅有一个直接前趋,都有且仅有一个直接后继. 在行关系中 aij直接前趋是 aij直接后继是 在列关系中 aij直接前趋是 aij直接后继是

a00 a01 a10 a11

a0 n-1 a1 n-1

a11 a21 ┇ a12 a22 ┇ ai2 ┇ … amj … amn … aij … ain … … a1j a2j … … a1n a2n β1 β2 ┇ βi ┇ βm

第5章存-储-器-系-统

则存储器地址范围为:FE000H ~FFFFFH

A19 1

A18

A17

A16

&

A15

A14

A13 1

/CS1

高位地址A19 ~ A13须为0111 110方能选 中该芯片,则地址范围为: 7C000H ~7DFFFH

A19

A18 1

A17

A16

≥1

A15

A14

A13

/CS1

高位地址A19 ~ A13须为0100 000方能选 中该芯片,则地址范围为: 40000H ~41FFFH

CS1 CS2 WE OE 数据引脚

H × × × 高阻 × L × × 高阻

L H H L 输出

L H L H 输入

L H H H 高阻

Intel 6264引脚排列及功能

6264的外部特性( 8K×8 )

28个引脚:13根地址线,8根数据线,4根控制信号 线,电源线,地线

(1)A0~A12:213=8K,决定存储单元的个数 (M),与系统地址总线的低13位相连。

将一个存储器芯片接到总线上,除部分控 制信号线及数据线的连接外,主要是如何保 证该芯片在整个内存中占据的地址范围满 足用户的要求。 高位地址信号决定了芯片在整个内存中占 据的地址范围。

低位地址线:与芯片地址线相连 高位地址线:片选信号 例如:居住小区、学号、身份证号等 370102 XXXX XX XX XXX X

A12 ~ ~A0 0 ~~0

…… 1 ~ ~1

全0、全1的地址线组合在一起使用,作译码器的使 能端、输入端。

A15 A14 A13:作译码器的输入端,则输 出端为/Y7

A19 A18:全0,经或门与/G2A 相连 A17 A16:全1,经与非门与/G2B 相连 /MEMR、/MEMW:经与非门与G1相连

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

第5章 存储器

存储器概述

5.1半导体存储芯片与CPU 的连接

5.28088系统的存储器接口5.48086系统的存储器接口

5.58086/8088的存储器组织

5.3

4

5.1 存储器概述

半导体存储器的分类5.1.1典型的半导体存储器芯片

5.1.3半导体存储器芯片的结构 5.1.255.1.1 半导体存储器的分类

随机存取存储器1只读存储器

2

71.随机存取存储器RAM

存储器中的信息既可以读又可以写。

RAM 中的信息在掉电后立即消失,是一种易失性存储器(volatile memory )。

分为:

⏹静态RAM(SRAM)⏹动态RAM(DRAM)

12

5.1.2 半导体存储器芯片的结构

175.1.3 典型的半导体存储器芯片

SRAM 芯片HM61161DRAM 芯片Intel 21642EPROM 芯片Intel 2732A

3

18

1.静态RAM(SRAM)芯片HM6116

高速静态CMOS 随机存取存储器。

有11条地址线A 0~A 11、8条数据线I/O 1~I/O 8,可构成2KB 的内存。

有3条控制线:

⏹片选信号CE :用来选择芯片;⏹写允许信号WE :控制读/写操作;⏹输出允许信号OE :用来把数据输出到数据线。

个单元,20

3.只读存储器(EPROM)芯片Intel 2732A

存储容量为4K ×8b ,有12条地址线A 11~ A 0,8条数据线O 7~O 0。

CE 为芯片允许信号,用来选择芯片;OE/V PP 为输出允许信号及编程电源输入线。

当CE 为低电平时,若OE/V PP 也为低电平,对存储器进行读操作;若OE/V PP 加上21V 编程电压时,对存储器重新编程。

21

5.2 半导体存储芯片与CPU 的连接

这是本章的重点内容

SRAM 、EPROM 与CPU 的连接

译码方法同样适合I/O 端口

数据线的连接★地址线的连接★片选端的连接

★读写控制线的连接

★存储芯片与CPU 连接时应考虑的问题

★23位扩展

等效为

64K ×8位

A 15~A 0

D 7~D 0

R/W

CS 图5.10 由64K×1位芯片位扩展组成64K×8位存储器(P.127)

芯片的片选信号并联,可接CPU 控制总线中的存储器选择信号(IO/M ),也可接地址线高位或地址译码器输出端(后述)。

25片内译码

000H 001H 002H …3FDH 3FEH 3FFH

全0

全1

00...0000...0100...10...11...0111...1011 (11)

范围(16进制)

A 9~A

36

地址范围

12

××××××××××

A 19~ A 1504000H ~05FFFH 02000H ~03FFFH

全0~全1全0~全1

1 00 1

一个可用地址A 12~A 0A 14 A 13

切记: A 14 A 13=00的情况不能出现00000H ~01FFFH 的地址不可使用

切记: A 14 A 13=00的情况不能出现00000H ~01FFFH 的地址不可使用

38

5.存储芯片与CPU 连接时应考虑的问题

存储芯片与CPU 总线的连接,还有两个很重要的问题:

CPU 的总线负载能力

⏹CPU 能否带动总线上包括存储器在内的连接器件

存储芯片与CPU 总线时序的配合

⏹CPU 能否与存储器的存取速度相配合

39

5.3 8086/8088的存储器组织

8086存储器组织18088存储器组织

2

40

1.8086存储器组织

图2.22 8086的存储器组织(P.44)

41

偶区和奇区的解释42

表2.7 奇偶区的选择

8086系统的存储器为什么要分为奇区和偶区两部分?

43信息的存放

偶字节

奇字节

偶字

奇字

MOV AL, [2000H]

MOV AL, [2001H]MOV AX, [2000H]

MOV AX, [2001H]

图5.6 由8088CPU 组成的8位存储器系统

47图5.14 8088系统字位扩展的接线图48

表5.5 图5.14存储器芯片的地址范围

495.5 8086系统的存储器接口

54

图5.13 16位系统全译码法字扩展接线图

55表5.4 图5.13存储器芯片的地址范围

59思考题

某PC 机内存的地址译码器如图所示,试回答以下问题:(1)每片RAM 的最大容量为多少单元?为什么?(2)写出RAM 0、RAM 1的地址范围(假设每片RAM 的容量为8KB )。