FPGA CPLD设计学习笔记(特权同学完整版)

第2章FPGACPLD器件

2020/11/25

第2章FPGACPLD器件

第2章 FPGA/CPLD器件

•2.1 PLD器件概述 •2.2 PLD的基本原理与结构 •2.3 低密度PLD的原理与结构

•内容 •2.4 CPLD的原理与结构 •2.5 FPGA的原理与结构 •2.6 FPGA/CPLD的编程元件 •2.7 边界扫描测试技术 •2.8 FPGA/CPLD的编程与配置 •2.9 FPGA/CPLD器件概述 •2.10 FPGA/CPLD的发展趋势

•CPLD器件 •的结构

第2章FPGACPLD器件

•CPLD器件 宏单元内部 结构示意图

第2章FPGACPLD器件

典型CPLD器件的结构

•MAX 7000S器件的内部结构

第2章FPGACPLD器件

•MAX 7000S器件的宏单元结构

第2章FPGACPLD器件

•MispLSI 1032器件的GLB的结构

•Lattice公司CPLD器件系列

•ispMACH4000系列 • ispMACH4000系列CPLD器件有3.3V、2.5V 和 1.8V 三种供电电压,分别属于 ispMACH 4000V、 ispMACH 4000B 和 ispMACH 4000C 器件系列。 •Lattice EC & ECP系列

•易失性器件

第2章FPGACPLD器件

•2.2 PLD的基本原理与结构

•PLD器件的原理结构图

第2章FPGACPLD器件

•数字电路符号表示

•数字逻辑电路的两种国标符号对照

第2章FPGACPLD器件

•PLD电路符号表示

•PLD与阵列表示 •PLD的输入缓冲电路

•PLD或阵列表示

FPGACPLD中常见模块设计精华集锦资料

FPGA/CPLD中常见模块设计精华集锦一、智能全数字锁相环的设计1 引言数字锁相环路已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。

随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去。

在基于FPGA的通信电路中,可以把全数字锁相环路作为一个功能模块嵌入FPGA中,构成片内锁相环。

锁相环是一个相位误差控制系统。

它比较输入信号和振荡器输出信号之间的相位差,从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。

所谓全数字锁相环路(DPLL)就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成的锁相环路,其组成框图见图1示。

当锁相环中的鉴相器与数控振荡器选定后,锁相环的性能很大程度依赖于数字环路滤波器的参数设置。

2 K计数器的参数设置74297中的环路滤波器采用了K计数器。

其功能就是对相位误差序列计数即滤波,并输出相应的进位脉冲或是借位脉冲,来调整I/D数控振荡器输出信号的相位(或频率),从而实现相位控制和锁定。

K计数器中K值的选取需要由四根控制线来进行控制,模值是2的N次幂。

在锁相环路同步的状态下,鉴相器既没有超前脉冲也没有滞后脉冲输出,所以K计数器通常是没有输出的;这就大大减少了由噪声引起的对锁相环路的误控作用。

也就是说,K计数器作为滤波器,有效地滤除了噪声对环路的干扰作用。

显然,设计中适当选取K值是很重要的。

K值取得大,对抑止噪声有利(因为K值大,计数器对少量的噪声干扰不可能计满,所以不会有进位或借位脉冲输出),但这样捕捉带变小,而且加大了环路进入锁定状态的时间。

反之,K值取得小,可以加速环路的入锁,但K计数器会频繁地产生进位或借位脉冲,从而导致了相位抖动,相应地对噪声的抑制能力也随之降低。

为了平衡锁定时间与相位抖动之间的矛盾,理想的情况是当数字锁相环处于失步状态时,降低K计数器的设置,反之加大其设置。

特权同学倾情奉献9G海量FPGA学习资料

特权同学倾情奉献9G海量FPGA学习资料

本人最恨恶淘宝上那些卖资料的JS了,本来就是网络上免费搜集来的资料,居然还冠冕堂皇的拿来生财。

为此,本人特别将手上所有的资料共享给广大的FPGA爱好者们。

百度网盘下载地址:

/s/1o62lMYY

《深入浅出玩转FPGA》视频教程:35课时

特权同学精心录制的35课时深入浅出FPGA入门、进阶课程。

可配套北航出版社2010年6月上市的《深入浅出玩转FPGA》一书学习。

整部视频先是阐述FPGA的基本概念和学习方法,接着通过相应的开发套件BJ-EPM和SF-EP1C进行实践学习。

是初学者迈入

《特权和你一起学NIOS2》视频教程:20课时

特权同学的又一力作,SOPC的设计与底层逻辑设计不同,这部教程完全以另一种方式带领初学者领悟基于FPGA的嵌入式系统设计,同时也希望借助本教程能使大家熟悉在EDS 软件平台上实现NIOS2的编程和开发。

与本视频完全配套同步的图书《爱上FPGA开发——

Altera官方专题视频教程:38课时

特权fpga技术公开课

Altera官方资料(各类手册和应用笔记)(略)

百度网盘下载地址:

/s/1o62lMYY。

《CPLD FPGA设计与应用高级教程》随书光盘 第1章 概述

目前Altera、Lattice和Xilinx公司的CPLD/FPGA产品已经占到了市 场份额的80%以上。 Altera公司在20世纪90年代发展迅猛,是最大的可编程器件 供应商之一。在CPLD产品方面,连续推出了MAX3000/7000、 FLEX10、MAXII、MAXIIZ系列,而在FPGA产品方面,也不断推 陈出新,推出了Cyclone、Stratix、Arria等系列产品。 Xilinx公司是FPGA的发明者,老牌的FPGA公司,也是最大的可编 程逻辑器件供应商之一,产品丰富,种类齐全,主要有XC9500、 Coolrunner、 CoolrunnerII等系列的CPLD产品以及Spartan、 Virtex系列的FPGA产品,目前最新款的FPGA是Spartan6,Virtex 6系列的产品。

复杂的集成度也要求人们思考两个问题,该把芯片设计成固定功 能呢,还是设计成可以灵活地选择功能呢?于是集成电路芯片便 朝着两个方向并行发展,一个是专用集成芯片(Application Specific Integrated Circuit,ASIC),另外为可编程逻辑器件。 ASIC一般应用于固定场合。人们设计线路时,需要按照它的要求 进行设计,这就要求电子工程师需要有一定的技术和经验的积累。 有些ASIC功能复杂繁多,而实际上具体应用时只需要其中的一部 分,这样就造成了逻辑资源的浪费。 可编程逻辑器件功能强大,人们可以通过编程来实现自己想要的 功能,去除自己不需要的冗余功能。 另一方面,这样复杂的集成度意味着传统的设计方法和设计理念 已经不能适应芯片的产业发展,这就要求人们去变革和更新现有 的设计理念以及设计方法。

1.5 设计与验证流程

传统上采用的“自下向上(Bottom Up)”的设计方法已经不再 适应CPLD/FPGA的设计需求。 CPLD/FPGA的设计需要从系统整体要求出发,自上向下逐步将设 计内容细化,最后完成系统硬件的整体设计,这就是所谓的自顶 向下(Top Down)的设计方法,也就从抽象到具体的一种设计方 法。 与传统的设计方法相比较,自顶向下的方法不仅节约了大量的设 计时间,也大大减少了调试时间,整体上缩短了系统的设计时间, 节省了大量的人力与物力,加速了产品上市。

《CPLD FPGA设计与应用高级教程》随书光盘第2章 CPLDFPGA硬件结构

图4-2为采用乘积项结构来表示的逻辑示意图。

图5-2为真实的CPLD乘积项结构状态。当逻辑表达式在乘积项中 完成以后,还需要通过可编程触发器以及输出电路把信号输出到 芯片管脚,这样才完成了编程。这一系列的过程都是由软件自动 完成的。

EPROM型:它全称为可擦可编程存取器(Erasable PROM),采 用紫外线擦除,电可编程,但编程电压较高,可多次编程。如果 要重复编程则需要先用紫外线擦除。有时为降低生产成本,在制 造时不加用于紫外线擦除的石英窗口,就只能编程一次,也被称 为OTP器件。 EEPROM型:它是电可擦可编程只读存取器的英文缩写,是采用 浮栅技术生产的可编程存取器。图2-2为浮栅技术的示意图,浮栅 延长区与漏区之间的交叠处有一个厚度约为80埃的绝缘层。当漏 极接地,控制栅极加上足够大的电压的时候,交叠区将产生一个 很强的电场,从而使电子通过这个薄绝缘层到达栅极,这样就使 浮栅带上负电荷,也就是所谓的隧道效应;相反,如果在漏极加 上正电压时,则使浮栅放电。这样通过利用浮栅是否积累有负电 荷来存取二进制数据。因为采用电可擦除,所以速度较EPROM快 。

5.3查找表结构的基本原理 查找表结构的基本原理

查找表(LUT)结构本质上是一个RAM,它类似于一块有4个输入 、16个输出的16bit的存取器(当然也有5输入的结构), 这个存 取器里面储存了所有可能的结果,然后由输入来选择哪个结果应 该输出。当用户通过原理图或者HDL语言来描述一个逻辑电路时 ,PLD/FPGA的综合软件和布局布线软件会自动计算逻辑电路中所 有可能的结果,并且把结果事先写入RAM。这样对输入信号进行 逻辑运算就相当于输入一个地址进行查表,找出并输出地址对应 的内容。如果把输出的D触发器旁路而直接输出,则便实现了组 合逻辑,反之,如果有D触发器则实现了时序逻辑。

11.CPLDFPGA的常用设计

13

BEGIN

ytemp<=CONV_STD_LOGIC_vector(y,8);

WAIT UNTIL clk='1';

CASE state IS

12

例 设计一个8位乘8位的乘法器。

LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY multi8 IS

PORT(clk:IN STD_LOGIC; x,y:IN INTEGER RANGE 0 TO 127; f:OUT INTEGER RANGE 0 TO 65535);

count:=count+1;

state<=st1;

END IF; WHEN st2=> f<=preg;

--输出乘法结果

state<=st0;

END CASE;

END PROCESS;

END multi;

14

乘法器的仿真波形如图所示。

15

查询表法是把乘积放在存储器中,使用 被乘数和乘数组成的操作数作为地址访问 存储器,得到的输出数据就是乘法运算的 结果。

19

一、偶数分频器设计 所谓偶数分频器就是指分频系数

为偶数的分频器,即分频系数 N=2n(n=1,2,…)。若输入的信号 频率为f,那么分频器的输出信号的 频率为f/2n(n=1,2,…)。偶数分频 器完全可以通过计数器计数来实现。

2.FPGA和CPLD结构原理

逻辑阵列

LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE LE

LE LE LE LE LE LE LE LE

EAB 的字长是可配置的

1、逻辑阵列块LAB

一个LAB由16个宏单元组成

对于每个LAB有下列输入信号:

来自作为通用逻辑输入的PIA的36个信号

全局控制信号

从I/O引脚到寄存器的直接输入通道

2、MAX3000A系列的单个宏单元结构

来自 PIA的 36个信号

全局 清零

全局 时钟 来自 I/O引脚

并

行

2 快速输入选择

扩展项

寄存器 旁 路

• EAB的大小灵活可变 256x8 512x4 2048x1

1024x2

• 通过组合EAB 可以构成更大的模块 • 不需要额外的逻辑单元,不引入延迟, EAB 可配置为深度达2048的存储器 512x4 256x8 512x8 256x16 256x8 512x4

EAB 可以用来实现乘法器

实例: 4x4 乘法器

• 2、JTAG边界扫描

• 针对器件密度及I/O 接口数量的增加,信号注入和测取难度越来越 大而提出的一种新的测试技术 • 它不需要使用外部物理测试探针来获得功能数据 • JTAG技术在器件正常工作时,器件的边界扫描单元能够追踪引脚 信号或是从器件逻辑信号中捕捉数据,提供串行扫描路径 • 通过JTAG测试端口很容易完成电路测试 • 它只需4根线(TDI、TDO、TMS、TCK)

按编程工艺分:

(1)熔丝(Fuse)器件

FPGACPLD数字电路设计经验分享

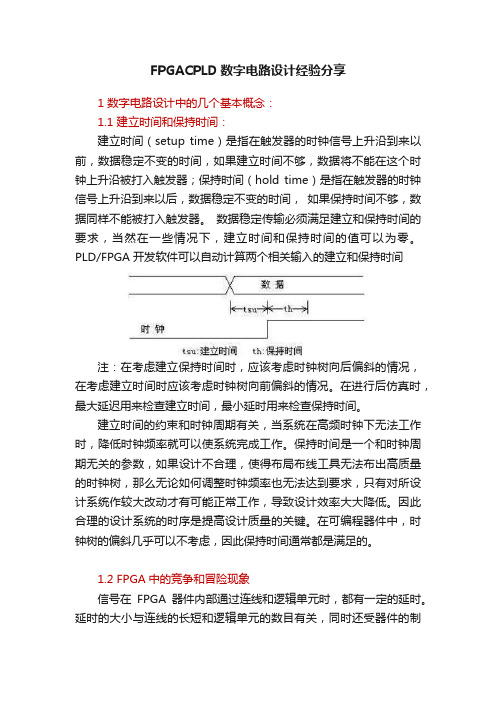

FPGACPLD数字电路设计经验分享1 数字电路设计中的几个基本概念:1.1 建立时间和保持时间:建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间注:在考虑建立保持时间时,应该考虑时钟树向后偏斜的情况,在考虑建立时间时应该考虑时钟树向前偏斜的情况。

在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间。

建立时间的约束和时钟周期有关,当系统在高频时钟下无法工作时,降低时钟频率就可以使系统完成工作。

保持时间是一个和时钟周期无关的参数,如果设计不合理,使得布局布线工具无法布出高质量的时钟树,那么无论如何调整时钟频率也无法达到要求,只有对所设计系统作较大改动才有可能正常工作,导致设计效率大大降低。

因此合理的设计系统的时序是提高设计质量的关键。

在可编程器件中,时钟树的偏斜几乎可以不考虑,因此保持时间通常都是满足的。

1.2 FPGA中的竞争和冒险现象信号在FPGA器件内部通过连线和逻辑单元时,都有一定的延时。

延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。

信号的高低电平转换也需要一定的过渡时间。

由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为'毛刺'。

如果一个组合逻辑电路中有'毛刺'出现,就说明该电路存在'冒险'。

FPGA CPLD设计学习笔记(特权同学)

1、FPGA\CPLD设计学习笔记(特权同学)题记:这个笔记不是特权同学自己整理的,特权同学只是对这个笔记做了一下完善,也忘了是从那DOWNLOAD 来的,首先对整理者表示感谢。

这些知识点确实都很实用,这些设计思想或者也可以说是经验吧,是很值得每一个有志于FP GA/CP LD方面发展的工程师学习的。

1、硬件设计基本原则(1)、速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用“乒乓操作”和“串并转换”的思想进行处理,在芯片输出模块处再对数据进行“并串转换”。

从而实现了用面积复制换取速度的提高。

(2)、硬件原则:理解HDL本质(3)、系统原则:整体把握(4)、同步设计原则:设计时序稳定的基本原则2、Verilog作为一种HDL语言,对系统行为的建模方式是分层次的。

比较重要的层次有系统级(system)、算法级(Algorithm)、寄存器传输级(RTL)、逻辑级(Logic)、门级(Gate)、电路开关级(S witch)。

3、实际工作中,除了描述仿真测试激励(Testbench)时使用for循环语句外,极少在RTL级编码中使用for循环,这是因为for循环会被综合器展开为所有变量情况的执行语句,每个变量独立占用寄存器资源,不能有效的复用硬件逻辑资源,造成巨大的浪费。

一般常用case语句代替。

4、if…else…和case在嵌套描述时是有很大区别的,i f…el s e…是有优先级的,一般来说,第一个i f的优先级最高,最后一个else的优先级最低。

而case语句是平行语句,它是没有优先级的,而建立优先级结构需要耗费大量的逻辑资源,所以能用case的地方就不要用i f…el s e…语句。

CPLD FPGA设计菜鸟必看

所谓综合,就是把描述语言转化成能硬件实现的电路,学verilog的时候,没有人给我说要不要考虑能否综合的问题~~~看了5本书,居然没有一本书讲到能否综合,所以设计出来的程序完全不能用~~~而且,书中都是讲语句的具体使用办法,例如always @(),但是什么时候用always,几个always之间、时序电路、逻辑电路、任务与函数什么时候用,却没有一本书能讲清楚。

这个笔记详细写了这些思路的问题,分享给新手看看,学习一种思路~~先记下来:1、不使用初始化语句;2、不使用延时语句;3、不使用循环次数不确定的语句,如:forever,while等;4、尽量采用同步方式设计电路;5、尽量采用行为语句完成设计;6、always过程块描述组合逻辑,应在敏感信号表中列出所有的输入信号;7、所有的内部寄存器都应该可以被复位;8、用户自定义原件(UDP元件)是不能被综合的。

一:基本Verilog中的变量有线网类型和寄存器类型。

线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器,还有可能被优化掉。

二:verilog语句结构到门级的映射1、连续性赋值:assign连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。

因此连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。

Assign语句中的延时综合时都将忽视。

2、过程性赋值:过程性赋值只出现在always语句中。

阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。

建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。

过程性赋值的赋值对象有可能综合成wire, latch,和flip-flop,取决于具体状况。

如,时钟控制下的非阻塞赋值综合成flip-flop。

过程性赋值语句中的任何延时在综合时都将忽略。

建议同一个变量单一地使用阻塞或者非阻塞赋值。

3、逻辑操作符:逻辑操作符对应于硬件中已有的逻辑门,一些操作符不能被综合:===、!==。

读特权同学《深入浅出玩转FPGA》有感

读特权同学《深入浅出玩转FPGA》有感看了特权同学的这本书,感悟颇多,最终使我重新确立了目标。

只是思路有些杂乱,我得慢慢道来: 初识特权同学实在END网站上,因为他的FPGA助学活动,在得到他的35集FPGA教学视频后,得知他已经和北京航空航天大学出版社合作出板了《深入浅出玩转FPGA》一书。

对于国内格式呆板、内容互抄的教科书,我是一直没有任何兴趣的,但是对于这样一个搞过FPGA项目的工程师写出的经验之谈,而且是以随笔的形式写出的书,我是没有任何理由放过的。

也许我最需要的不是一份说教的知识,而是一个可以在我最困难的时候让陪我聊天、给我动力的‘人’,而这个‘人’就隐藏在这本书点点滴滴、洋洋洒洒的文字之间,等着我去感悟。

由于我个人是习惯在当当网买书的,于是当下就去当当网搜索了一下,果然有这本书,售价是31.9元,但由于最近经济的原因我始终没有点下购买的按钮,于是自己买到这本书的计划便搁浅了。

也就是昨天我和一帮兄弟们去吉大的时候,偶然在兄弟那边看到了这本书,于是很爱不释手,当时便决定从兄弟手中‘横刀夺爱’了。

呵呵,于是,这本书便随我来到了理工,被我带到了实验室。

对于这样一本不同于现代呆板教材的书,我是很欣赏的,于是我开始用心去读这本书,去尽量感悟这本书的精髓,破开表面的知识去追求作者要给我们表达的深层次的意义。

很有幸的,我最后的结论是我没有选错书,在这本书中我感悟了很多,虽然我只读了第一个晚上,但这本书给我带来的感悟要比其他书籍在几周甚至几个月给我带来的感悟远远多得多...我感悟了很多,依靠串行触发是解决不了的,于是,我得用并行触发的方式来表达我的思路,首先得解释一下什么是并行触发:并行是指可以在同一时间进行响应,而没有顺序的问题。

于是,在这部分,我拿并行的概念套用一下,下面的这些感悟没有刻意的进行先后排序,既没有重要程度的高低和内容高低的划分,因为我认为:每一点思考都可以带来进步。

下面我就开始慢慢道来:1:它纠正了我对FPGA的认识 说实话,我的兄弟在去年寒假就给我买好了FPGA开发板,我们分配的任务是我在理工主要攻FPGA方向,很惭愧的是当我用原来单片机的方式去学习FPGA时遇到了很大的障碍,这段学习的路进展很缓慢,于是不知不觉已经推迟到了今年暑假。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、FPGA\CPLD设计学习笔记(特权同学完整版)题记:这个笔记不是特权同学自己整理的,特权同学只是对这个笔记做了一下完善,也忘了是从那DOWNLOAD 来的,首先对整理者表示感谢。

这些知识点确实都很实用,这些设计思想或者也可以说是经验吧,是很值得每一个有志于FPGA/CPLD方面发展的工程师学习的。

1、硬件设计基本原则(1)、速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用“乒乓操作”和“串并转换”的思想进行处理,在芯片输出模块处再对数据进行“并串转换”。

从而实现了用面积复制换取速度的提高。

(2)、硬件原则:理解HDL本质(3)、系统原则:整体把握(4)、同步设计原则:设计时序稳定的基本原则2、Verilog作为一种HDL语言,对系统行为的建模方式是分层次的。

比较重要的层次有系统级(system)、算法级(Algorithm)、寄存器传输级(RTL)、逻辑级(Logic)、门级(Gate)、电路开关级(Switch)。

3、实际工作中,除了描述仿真测试激励(Testbench)时使用for循环语句外,极少在RTL级编码中使用for循环,这是因为for循环会被综合器展开为所有变量情况的执行语句,每个变量独立占用寄存器资源,不能有效的复用硬件逻辑资源,造成巨大的浪费。

一般常用case语句代替。

4、if…else…和case在嵌套描述时是有很大区别的,if…else…是有优先级的,一般来说,第一个if的优先级最高,最后一个else的优先级最低。

而case语句是平行语句,它是没有优先级的,而建立优先级结构需要耗费大量的逻辑资源,所以能用case的地方就不要用if…else…语句。

补充:1.也可以用if…; if…; if…;描述不带优先级的“平行”语句。

(但是这样容易引入锁存器)5、FPGA一般触发器资源比较丰富,而CPLD组合逻辑资源更丰富。

6、FPGA和CPLD的组成:FPGA基本有可编程I/O单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等6部分组成。

CPLD的结构相对比较简单,主要由可编程I/O单元、基本逻辑单元、布线池和其他辅助功能模块组成。

7、Block RAM:3种块RAM结构,M512 RAM(512bit)、M4K RAM(4Kbit)、M-RAM(64Kbit).M512 RAM:适合做一些小的Buffer、FIFO、DPRAM、SPRAM、ROM等;M4K RAM: 适用于一般的需求M-RAM: 适合做大块数据的缓冲区。

Xlinx 和Lattice FPGA的LUT可以灵活配置成小的RAM、ROM、FIFO等存储结构,这种技术被称为分布式RAM。

补充:但是在一般的设计中,不提倡用FPGA/CPLD的片内资源配置成大量的存储器,这是处于成本的考虑。

所以尽量采用外接存储器。

8、善用芯片内部的PLL(Phase Locked Loop 模拟锁相环)或DLL(Delay Locked Loop 数字锁相环)资源完成时钟的分频、倍频率、移相等操作,不仅简化了设计,并且能有效地提高系统的精度和工作稳定性。

DLL是基于数字抽样方式,在输入时钟和反馈时钟之间插入延迟,使输入时钟和反馈时钟的上升沿一致来实现的。

又称数字锁相环。

PLL使用了电压控制延迟,用VCO来实现和DLL中类试的延迟功能。

又称模拟锁相环。

功能上都可以实现倍频、分频、占空比调整,但是PLL调节范围更大,比如说:XILINX使用DLL,只能够2、4倍频;ALTERA 的PLL可以实现的倍频范围就更大毕竟一个是模拟的、一个是数字的。

两者之间的对比:对于PLL,用的晶振存在不稳定性,而且会累加相位错误,而DLL在这点上做的好一些,抗噪声的能力强些;但PLL在时钟的综合方面做得更好些。

总的来说PLL的应用多,DLL则在jitter power precision等方面优于PLL。

目前大多数FPGA厂商都在FPGA内部集成了硬的DLL(Delay-Locked Loop)或者PLL(Phase-Locked Loop),用以完成时钟的高精度、低抖动的倍频、分频、占空比调整移相等。

目前高端FPGA产品集成的DLL和PLL资源越来越丰富,功能越来越复杂,精度越来越高(一般在ps的数量级)。

Xilinx芯片主要集成的是DLL,而Altera芯片集成的是PLL。

Xilinx芯片DLL的模块名称为CLKDLL,在高端FPGA中,CLKDLL的增强型模块为DCM(Digital Clock Manager)。

Altera芯片的PLL模块也分为增强型PLL(Enhanced PLL)和高速(Fast PLL)等。

这些时钟模块的生成和配置方法一般分为两种,一种是在HDL代码和原理图中直接实例化,另一种方法是在IP 核生成器中配置相关参数,自动生成IP。

Xilinx的IP核生成器叫Core Generator,另外在Xilinx ISE 5.x版本中通过Archetecture Wizard生成DCM模块。

Altera的IP核生成器叫做MegaWizard。

另外可以通过在综合、实现步骤的约束文件中编写约束属性完成时钟模块的约束。

9、异步电路和同步时序电路的区别异步电路:电路核心逻辑有用组合电路实现;异步时序电路的最大缺点是容易产生毛刺;不利于器件移植;不利于静态时序分析(STA)、验证设计时序性能。

同步时序电路:电路核心逻辑是用各种触发器实现;电路主要信号、输出信号等都是在某个时钟沿驱动触发器产生的;同步时序电路可以很好的避免毛刺;利于器件移植;利于静态时序分析(STA)、验证设计时序性能。

10、同步设计中,稳定可靠的数据采样必须遵从以下两个基本原则:(寄存器的建立和保持时间)(1)、在有效时钟沿到达前,数据输入至少已经稳定了采样寄存器的Setup时间之久,这条原则简称满足Setup时间原则;(2)、在有效时钟沿到达后,数据输入至少还将稳定保持采样寄存器的Hold时钟之久,这条原则简称满足Hold时间原则。

11、同步时序设计注意事项:异步时钟域的数据转换。

组合逻辑电路的设计方法。

同步时序电路的时钟设计。

同步时序电路的延迟。

同步时序电路的延迟最常用的设计方法是用分频或者倍频的时钟或者同步计数器完成所需的延迟,对比较大的和特殊定时要求的延时,一般用高速时钟产生一个计数器,根据计数产生延迟;对于比较小的延迟,可以用D触发器打一下,这样不仅可以使信号延时了一个时钟周期,而且完成了信号与时钟的初次同步。

在输入信号采样和增加时序约束余量中使用。

另外,还有用行为级方法描述延迟,如“#5 a<=4’0101;”这种常用于仿真测试激励,但是在电路综合时会被忽略,并不能起到延迟作用。

Verilog 定义的reg型,不一定综合成寄存器。

在Verilog代码中最常用的两种数据类型是wire和reg型,一般来说,wire型指定的数据和网线通过组合逻辑实现,而reg型指定的数据不一定就是用寄存器实现。

12、常用设计思想与技巧(1)、乒乓操作;(2)、串并转换;(3)、流水线操作;(4)、异步时钟域数据同步。

是指如何在两个时钟不同步的数据域之间可靠地进行数据交换的问题。

数据时钟域不同步主要有两种情况:两个域的时钟频率相同,但是相差不固定,或者相差固定但是不可测,简称为同频异相问题。

两个时钟频率根本不同,简称异频问题。

两种不推荐的异步时钟域操作方法:一种是通过增加Buffer或者其他门延时来调整采样;另一种是盲目使用时钟正负沿调整数据采样。

13、模块划分基本原则:(1)、对每个同步时序设计的子模块的输出使用寄存器(用寄存器分割同步时序模块原则)。

(2)、将相关逻辑和可以复用的逻辑划分在同一模块内(呼应系统原则)。

(3)、将不同优化目标的逻辑分开。

(4)、将送约束的逻辑归到同一模块。

(5)、将存储逻辑独立划分成模块。

(6)、合适的模块规模。

(7)、顶层模块最好不进行逻辑设计。

14、组合逻辑的注意事项(1)、避免组合逻辑反馈环路(容易毛刺、振荡、时序违规等)。

解决:A、牢记任何反馈回路必须包含寄存器;B、检查综合、实现报告的warning信息,发现反馈回路(combinational loops)后进行相应修改。

(2)、替换延迟链。

解决:用倍频、分频或者同步计数器完成。

(3)、替换异步脉冲产生单元(毛刺生成器)。

解决:用同步时序设计脉冲电路。

(4)、慎用锁存器。

解决:A、使用完备的if…else语句;B、检查设计中是否含有组合逻辑反馈环路;C、对每个输入条件,设计输出操作,对case语句设置default操作。

特别是在状态机设计中,最好有一个default 的状态转移,而且每个状态最好也有一个default的操作。

D、如果使用case语句时,特别是在设计状态机时,尽量附加综合约束属性,综合为完全条件case语句。

小技巧:仔细检查综合器的综合报告,目前大多数的综合器对所综合出的latch都会报“warning”,通过综合报告可以较为方便地找出无意中生成的latch。

15、时钟设计的注意事项(1)、同步时序电路推荐的时钟设计方法:时钟经全局时钟输入引脚输入,通过FPGA内部专用的PLL或DLL进行分频/倍频、移相等调整与运算,然后经FPGA内部全局时钟布线资源驱动到达芯片内所有寄存器和其他模块的时钟输入端。

FPGA设计者的5项基本功《佟林传》里,佟林练的基本功是“绕大树、解皮绳”,然后才练成了什么“鬼影随行、柳叶绵丝掌”。

在我看来,成为一名说得过去的FPGA设计者,需要练好5项基本功:仿真、综合、时序分析、调试、验证。

对于FPGA设计者来说,练好这5项基本功,与用好相应的EDA工具是同一过程,对应关系如下:1. 仿真:Modelsim, Quartus II(Simulator Tool)2. 综合:Quartus II (Compiler Tool, RTL Viewer, Technology Map Viewer, Chip Planner)3. 时序:Quartus II (TimeQuest Timing Analyzer, Technology Map Viewer, Chip Planner)4. 调试:Quartus II (SignalTap II Logic Analyzer, Virtual JTAG, Assignment Editor)5. 验证:Modelsim, Quartus II(Test Bench Template Writer)掌握HDL语言虽然不是FPGA设计的全部,但是HDL语言对FPGA设计的影响贯穿于整个FPGA设计流程中,与FPGA设计的5项基本功是相辅相成的。