基于标准单元库扩展的快速乘法器设计

VHDL的乘法器设计——数字电路课程设计

cout=>c4,s=>s4(1));

------------------------------last u12:full_adder port map (a=>d4(1),b=>d4(2),cin=>d4(3),

【第二章】:设计思路及方案 算法结构(无符号)

由上图可见,乘法的运算最终是加法的运算,两个 4BIT 输入,输出为 7BIT。 模块一、半加器:单比特输入相加,

模块二、全加器:由两个半加器组成,有一个进位输入,

模块三、进位保留加法器:

3

最终程序结构图

流水设计的原理:在前向割集上加入四级流水

图一 图二

elsif clk'event and clk='1' then

--------------------------------------first d1(1)<= x(1); d1(2)<= x(2); d1(3)<= x(3);

7

d1(4)<= x(4); d1(5)<= x(5); d1(6)<= x(6); d1(7)<=c1(1) ; d1(8)<=s1(1); d1(9)<= x(9); d1(10)<=x(10); d1(11)<=c1(2); d1(12)<=s1(2); d1(13)<=x(13); d1(14)<=c1(3) ; d1(15)<=s1(3) ; d1(16)<=x(16);

乘法器设计

EDA设计基础实验课程论文题目乘法器学院通信专业班级学生姓名指导教师2013年6月25 日摘要随着工艺水平的发展,集成电路设计向着速度更快,面积更小的方向稳步发展着。

处理器作为集成电路设计产品的代表,更是需要体现出这种发展趋势。

为了使整体性能有较好的表现,各方面的优化在处理器的各组成部件的设计中都应有所体现。

乘法器是处理器中的一个重要组成部分。

在多媒体应用、图像处理等领域中,大量的循环乘法运算使得乘法器的作用尤为突出,其对处理器的整体性能也起到了至关重要的影响。

本文就是要针对速度和面积方面的性能提高提出查找表乘法器:4bit*4bit查找表乘法器的设计及具体实施方案。

采用了4 - 2 和5 - 2 混合压缩器对部分积进行压缩, 减少了乘法器的延时和资源占率;经Quartus II 集成开发环境下的综合仿真测试, 与用Verilog HDL 语言实现的两位阵列乘法器和传统的Booth编码乘法器进行了性能比较, 得出用这种混合压缩的器乘法器要比传统的 4 - 2 压缩器构成的乘法器速度提高了10 % , 硬件资源占用减少了1 % 。

关键词:乘法器;改进Booth算法;Verilog HDL语言AbstractAs technical level develops, IC design progresses in both the ways of higher speed and smaller area steadily. CPU is more likely to represent this trend for it is a typical product of IC design. To get a better performance of the whole target,we should optimize all the components of the CPU in all possible ways.Multiplier is an important component of the CPU. In the domains of multimedia application, image process and so on, plenty of multiplications in cycles make multiplier a significant part, which plays an important role in deciding the performance of the whole CPU.This paper is about to focus on improvement on speed as well as area and present lookup table multipliers varied by data width:4bit*4bit lookup table multipliers and actualization.Using 4 - 2 compressor and 5 - 2 compressor to compress partial products , while designing multiplier to reduce the delay of time and ratio of resource . Comparing performance of multiplier described in Verilog HDL on speed 、area and the utilization ratio of resource in the integrated exploitation environment of Quartus II . the speed of this multiplier is increased by 10 % and its hardware resource is reduced by 1 % .Keywords multiplier; modified Booth algorithm;Verilog HDL language目录中文摘要 (I)ABSTRACT (II)第一章绪论 (1)1.1课题背景 (1)1.2国内外发展现状 (1)1.2.1国外研究情况 (1)1.2.2国内研究情况 (2)1.3乘法器设计原理 (2)第二章乘法器简介 (4)2.1乘法器工作原理 (4)2.2乘法器实现方法 (4)2.2.1线性结构 (4)2.2.2Wallace 树结构 (5)第三章查找表乘法器的功能仿真 (7)3.1查找表原理 (7)3.1.1部分积压缩器功能简介 (7)3.2设计端口信号描述 (7)3.3查找表乘法器的功能仿真图 (8)第四章相关类型乘法器算法的简介 (9)4.1改进Boosh算法 (9)4.2 关键路径上Booth 编码模块电路设计 (11)第五章Verilog HDL语言 (13)5.1什么是Verilog HDL语言 (13)5.1.1Verilog HDL 简介 (13)5.2Verilog HDL语言与VHDL语言的比较 (13)5.3用Verilog HDL语言编写的程序仿真图 (14)结论 (15)参考文献 (16)致谢 (18)附录 (20)第一章绪论1.1课题背景Ve rilog HDL 是当今最为流行的一种硬件描述语言, 完整的Ve rilog HDL 足以对最复杂的芯片和完整的电子系统进行描述。

32位快速乘法器的设计

第27 卷第9 期合肥工业大学学报(自然科学版)V o l. 27 N o. 9 2004 年9 月JOU RNA L O F H EF E I UN IV ER S IT Y O F T ECHNOLO GY Sep. 200432 位快速乘法器的设计詹文法, 汪国林, 杨羽, 张珍(合肥工业大学电气与自动化工程学院, 安徽合肥230009)摘要: 高性能乘法器是现代微处理器中的重要部件, 乘法器完成一次乘法操作的周期基本上决定了微处理器的主频。

传统的乘法器的设计, 在最终的乘积项求和时, 常采用阵列相加或叠代相加的方法, 不适用中小规模的微处理器的设计。

该文提出的32 位乘法器, 采用了Boo th 编码、422 压缩器、W allace 树算法以及超前进位加法器等多种算法和技术, 在节约面积的同时, 获得了高速度的性能。

关键词: 乘法器; Boo th 编码; 超前进位加法器; W allace 树算法中图分类号: T P 342. 21 文献标识码: A文章编号: 100325060 (2004) 0921 099204D es ign of 32-b it m ul t ipl ier w ith good speed performan ceZHAN W en2fa, W A N G Guo 2lin, YA N G Yu, ZHAN G Zhen(Schoo l of E lectri c Engineeri ng and A utom at ion, H efei U niversity of T echno logy, H ef ei 230009, Ch ina)Abstract: A m u lt i p lier w ith good speed perfo rm ance is a very im po rtan t un it in the m odern m icrop ro2 cesso rs becau s e the cycle that a m u lt i p lier com p letes one m u lt i p lica t i o n operat i o n dete r m ines the m ain frequency of the m icrop rocesso r. In summ ing of the last p roduct in the t radit i o nal m u lt i p lier des ign, the array o r iterat i o n summ ing m ethod is u sed, w h ich is no t su itab le to the des ign of sm all o r m iddle scale in t egrat i o n circu i t. A 322b i t m u lt i p lier is p resen t ed in w h ich m any m ethods, such as Boo th algo2 rithm , 422 com p resso rs, W allace t ree algo rithm , and carry2loo kahead adder, are app lied, w h ich re2 su lt s in h igh speed perfo rm ance.Key words: m u lt i p lier; Boo th algo rithm ; carry2loo kahead adder; W allace t ree algo rithm高性能乘法器是现代微处理器中的重要部件, 乘法器完成一次乘法操作的周期基本上决定了微处理器的主频。

基于FPGA的阵列乘法器的设计与实现

基于FPGA的阵列乘法器的设计与实现*

朱世宇,夏汝华,甘 科,刘春雷,陈小川 (重庆工业自动化仪表研究所 重庆,4 0 1 1 2 1 )

摘 要:先对乘法器进行了分析,然后用现场可编程门阵列( F P G A ) 实现了阵列乘法器,并分析了设计原理。 关 键 词:乘 法 器;现 场 可 编 程 逻 辑 门 阵 列;标 准 硬 件 描 述 语 言;电 子 设 计 自 动 化 Abstract: This paper analyzed the operation of multiplier unit first, then realized array multiplier with FPGA, and described the design principle. Key words: multiplier unit FPGA VHDL EDA 中图分类号:T P 3 4 2 +. 2 2 文献标识码:B 文章编号:1 0 0 1 - 9 2 2 7 ( 2 0 1 1 ) 0 4 - 0 0 6 0 - 0 3

(下转第6 7 页)

61

《自动化与仪器仪表》2011 年第 4 期(总第 156 期) 图5 系统工作流程图

4 结束语 基于 Z i g b e e 组网技术城市窨井实时监测系统中将

多个窨井监测单元组成一个无线网络窨井监测矩阵,再由 一个 G P R S 路由转发器将数据发送到窨井动态监测软件系 统数据库中,实现了窨井事故隐患的主动预警和报警。本 系 统 整 体 技 术 可 改 变 监 测 对 象 ,在 城 市 管 网 、市 政 设 施 、 公路运输等领域广泛应用。

2 F P G A 技术 FPGA 是一类称为现场可编程逻辑(field-program-

《乘法器设计报告》word版

有符号乘法器设计报告——VLSI课程设计2010年12月复旦大学专用集成电路与国家重点实验室第一章 设计要求完成16*16有符号乘法器的设计。

具体设计方案选择要求如下:1、 编码方式:non-booth 编码,Booth 编码,Booth2编码(任选一种)2、 拓扑结构:简单阵列,双阵列,二进制树,Wallace 树(任选一种)3、 加法器:Ripple Carry Adder ,Carry bypass ,Carry select ,Carrylook ahead (任选一种或采用混合方法)设计报告必须包含设计方案说明及选择该方案的理由、仿真和设计结构等。

第二章 设计分析在微控制器(MCU )、微处理器(MPU )、数字信号处理器(DSP )、滤波器(FIR/IIR )等各种电路中都会用到乘法器,乘法器是最基本、最重要的运算模块之一。

并且乘法器往往还是处在关键路径上,所以乘法器的性能就显得更加重要。

伴随着现在工艺水平的提高,模块的面积也随着减小,在一定程度下以面积为代价来追求性能的提升,这也是允许的。

本设计是以追求性能为设计目标的,采用全并行的乘法器电路,设计指标设为传播延时为5ns 。

第三章 乘法器原理分析乘法器通常有三种结构形式,全串行乘法器、串并行乘法器以及全并行乘法器。

全串行乘法器都可以是串行的,需要多个时钟周期,速度很慢;串并行乘法器的一个输入是并行的,另一输入是串行的,乘积串行输出;全并行乘法器,输入和输出都是并行的,电路较为复杂,但是速度极快。

本设计追求的就是速度,所以采用全并行乘法器机构。

16位有符号乘法器可以分为三个部分:根据输入的被乘数和乘数产生部分积、部分积压缩产生和和进位、将产生的和和进位相加。

这三个部分分别对应着编码方式、拓扑结构以及加法器。

3.1 编码方式本设计采用booth2编码。

Booth 算法的提出主要是为了解决有符号数乘法运算中的复杂的符号修正的问题,所以采用booth2编码对于补码表示的两数就不需要考虑符号的问题。

Booth乘法器

Booth乘法器设计1. 实验目的要求掌握Booth算法原理,并根据算法设计Booth乘法器模块以及设计test_bench,最后在Robei可视化仿真软件经行功能实现和仿真验证。

2.实验原理1951年,A.D Booth在其论文“A Signed binary multiplication technique”中提出一种快速乘法算法,即Booth算法,是为了解决有符号乘法运算中复杂的符号修正问题而提出一种乘法算法。

乘法器中若乘数为有符号数,扩展其最高位;若是无符号数,则做一位0扩展。

Booth算法的基础基于二进制数加法的特性,其基本思想为当x乘以一个二进制数时可以将乘数中连续的1序列变换为(2i-2j),其中i>j,然后利用二进制数乘法的特性等于将2i 乘以x向左移i位,只需一个加法器和一个移位寄存器便可实现该段数据的(2i-2j)乘以x 乘法运算,i>j,从而有效减少总体需要的加法运算次数。

假设乘数和被乘数均为n位,那么Booth算法的具体执行过程以下六个步骤:(1)设置一个2n+1位的p空间,并将初始化为0;(2)将乘数填入p[n:1]中;(3)从p空间的最低位依次开始向左扫描,每次扫描两位,并判断所扫描的两位二进制数为表1中的何种情况;表1. Booth算法的加码操作B[i] B[i-1] 加码操作0 0 0(无操作)0 1 1(加被乘数)1 0 1(减被乘数,即加被乘数的补码)1 1 0(无操作)(4) 判断p[2n]位,如果是逻辑0右移一位补0,如果是逻辑1就右移一位补1; (5) 重复步骤(3)(4),循环n 次;(6) 最终p 空间的p[2n:1]就是乘数和被乘数的乘积。

下图1显示Booth 乘法器模块的设计:start_sig done_sig a[7:0] SI b[7:0] product[15:0]图1. Booth 乘法器模块的设计3.实验内容3.1 Booth_multiplier 模型设计1) 新建一个模型命名为 Booth_multiplier ,类型为 module ,同时具备 5 输入 2 输出,每个引脚的属性和名称参照下图2经行对应的修改。

乘法器vhdl课程设计

乘法器vhdl课程设计一、课程目标知识目标:1. 理解乘法器的原理及其在数字信号处理中的应用。

2. 掌握VHDL语言的基本语法和结构,能够使用VHDL进行简单的程序编写。

3. 学习并掌握利用VHDL设计乘法器的方法,理解其位运算和结构设计。

技能目标:1. 能够运用所学知识,独立设计并实现一个简单的乘法器VHDL程序。

2. 培养学生利用电子设计自动化(EDA)工具进行代码编写、仿真和测试的能力。

3. 提高学生的问题分析能力,学会使用VHDL解决实际的数字电路设计问题。

情感态度价值观目标:1. 培养学生对于电子信息和数字电路设计的兴趣,激发学生创新精神和探索欲望。

2. 增强团队合作意识,通过小组讨论和协作,提高学生之间的沟通能力和协作解决问题的能力。

3. 强化学生的工程伦理观念,了解所学技术在国家经济发展和国防建设中的重要性,树立正确的价值观。

本课程针对高年级电子信息工程及相关专业学生设计,结合学生已具备的基础知识和课程性质,以实践性和应用性为导向,旨在通过具体的乘法器VHDL课程设计,将理论知识与实践技能相结合,提升学生解决实际工程问题的能力。

通过本课程的学习,学生应能够展示出上述具体的学习成果。

二、教学内容1. 乘法器原理回顾:包括乘法器的基本工作原理,不同类型的乘法器结构对比,以及乘法器在数字信号处理中的应用。

- 相关教材章节:第三章“数字电路基础”,第5节“算术逻辑单元”。

2. VHDL语言基础:VHDL的基本语法,数据类型,信号与变量,运算符,顺序与并行语句,进程,实体和架构等。

- 相关教材章节:第五章“硬件描述语言VHDL”,第1-3节。

3. 乘法器的VHDL设计方法:- 位运算乘法器设计原理与实现。

- 流水线乘法器设计原理与实现。

- 相关教材章节:第五章“硬件描述语言VHDL”,第4节“VHDL设计实例”;第六章“数字信号处理器的硬件实现”,第2节“乘法器的硬件实现”。

4. EDA工具的应用:利用EDA工具进行VHDL代码的编写、编译、仿真和测试。

32位RISC处理器中可配置乘法器的设计

2007年第24卷第8期微电子学与计算机1引言在某公司32位RISC嵌入式处理器ENOD的设计中,由于位于流水线执行段的上执行部件的乘法器操作复杂,耗时较长,处于整个设计的关键时序路径,因此,乘法器设计的好坏将在很大程度上影响到处理器的整体性能[1]。

而且,由于ENOD处理器被设计成能应用于不同场合的可配置处理器核,因此,同样要求其乘法器单元具有一定的可配置性。

因此,文中采用Radix4-Booth算法完成了该处理器中乘法器IP核的设计。

该乘法器可以通过设置参数,根据需要生成3种不同结构的乘法器:(1)单周期乘法器;(2)流水线乘法器;(3)多周期乘法器。

而且可以通过参数设置乘法器的操作位宽、流水线乘法器的流水级数和多周期乘法器的周期数[2]。

2可配置乘法器的原理乘法器的电路实现算法有很多,Booth算法是比较常用的算法之一,文中采用改进的Radix4-Booth算法。

以32位乘法操作为例,描述Radix4-Booth算法如下:32位Booth乘法器的运算过程中,将乘数和被乘数分别存于M1和M2中,A用于存放部分积,再用Q-1作为辅助位。

(1)将A初始化为零,将Q-1初始化为零;(2)根据表1的Booth编码计算出部分积,然后再将A,M1和Q-1一起整体算术右移两位;(3)重复第二步操作16次。

乘积存放于寄存器A和M1中[3]。

3可配置乘法器的设计根据上述的算法,设计出使用Radix4-Booth算法的3种不同结构的乘法器分别如图1 ̄3所示。

其中的参数WIDTH是乘法器的操作数位宽,PIPEN32位RISC处理器中可配置乘法器的设计李云,张盛兵(西北工业大学,陕西西安710065)摘要:“ENOD”是某公司2006年设计的一款32位嵌入式RISC微处理器。

其中的硬件乘法器位于设计的关键时序路径上,为优化乘法器的时序和提高其灵活性,采用Radix4-Booth算法,设计了单周期、流水线和多周期3种乘法器结构,在Modelsim中进行了功能仿真和时序仿真。

基于EDA的4位乘法器的设计

4位乘法器的设计一、设计目的设计一个四位乘法器。

编写VHDL 源代码,得出正确的仿真波形,并在实验开发系统上进行硬件演示。

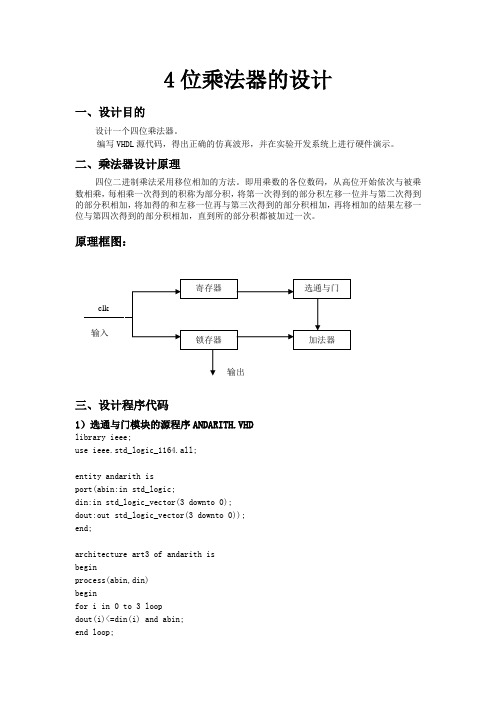

二、乘法器设计原理四位二进制乘法采用移位相加的方法。

即用乘数的各位数码,从高位开始依次与被乘数相乘,每相乘一次得到的积称为部分积,将第一次得到的部分积左移一位并与第二次得到的部分积相加,将加得的和左移一位再与第三次得到的部分积相加,再将相加的结果左移一位与第四次得到的部分积相加,直到所的部分积都被加过一次。

原理框图:三、设计程序代码1)选通与门模块的源程序ANDARITH.VHDlibrary ieee;use ieee.std_logic_1164.all;entity andarith isport(abin:in std_logic;din:in std_logic_vector(3 downto 0);dout:out std_logic_vector(3 downto 0));end;architecture art3 of andarith isbeginprocess(abin,din)beginfor i in 0 to 3 loopdout(i)<=din(i) and abin;end loop; 锁存器 寄存器加法器选通与门 clk输入 输出end process;end art3;2)4位右移寄存器的源程序SREG4B.VHD library ieee;use ieee.std_logic_1164.all;entity sreg4b isport(clk,en:in std_logic;load:in std_logic;din:in std_logic_vector(3 downto 0);qb:out std_logic);end;architecture art1 of sreg4b issignal reg4:std_logic_vector(3 downto 0); beginprocess(clk,load,en)beginif clk'event and clk ='1' and en='1' then if load='0' then reg4<=din;elsereg4(2 downto 0)<=reg4(3 downto 1);end if;end if;end process;qb<=reg4(0);end art1;3)8位锁存器的源程序REG8.VHDlibrary ieee;use ieee.std_logic_1164.all;entity reg8 isport(clk,clr,en:in std_logic;d:in std_logic_vector(4 downto 0);q: out std_logic_vector(7 downto 0)); end;architecture art4 of reg8 issignal r8s:std_logic_vector(7 downto 0); beginprocess(clk,clr)beginif clr='0' then r8s<=(others=>'0');elsif clk'event and clk='1' and en='1' then r8s(2 downto 0)<=r8s(3 downto 1);r8s(7 downto 3)<=d;end if;end process;q<=r8s;end art4;4)乘法运算控制器的源程序ARICTL.VHD library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity arictl isport(clk,start: in std_logic;en,rstall,ariend:out std_logic);end;architecture art5 of arictl issignal cnt2b:std_logic_vector(2 downto 0); beginrstall<=start;process(clk,start) isbeginif start='0' then cnt2b<="000";elsif clk'event and clk='1' thenif cnt2b<4 thencnt2b<=cnt2b+1;end if;end if;end process;process(clk,cnt2b,start) isbeginif start='1' thenif cnt2b<4 thenen<='1';ariend<='0';else en<='0';ariend<='1';end if;else en<='1';ariend<='0';end if;end process;end art5;5)译码器的源程序YIMAQI.VHDlibrary ieee;use ieee.std_logic_1164.all;entity YIMAQI isPORT(code:IN STD_LOGIC_VECTOR(3 DOWNTO 0); LED7S: OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ); end;architecture ART6 of YIMA7 isbeginPROCESS(code)BEGINCASE code ISWHEN "0000" => LED7S <="0000001";WHEN "0001" => LED7S <="1001111";WHEN "0010" => LED7S <="0010010";WHEN "0011" => LED7S <="0000110";WHEN "0100" => LED7S <="1001100";WHEN "0101" => LED7S <="0100100";WHEN "0110" => LED7S <="0100000";WHEN "0111" => LED7S <="0001111";WHEN "1000" => LED7S <="0000000";WHEN "1001" => LED7S <="0000100";WHEN "1010" => LED7S <="0001000";WHEN "1011" => LED7S <="1100000";WHEN "1100" => LED7S <="0110001";WHEN "1101" => LED7S <="1000010";WHEN "1110" => LED7S <="0110000";WHEN "1111" => LED7S <="0111000";WHEN OTHERS => NULL;END CASE;END PROCESS;end ART6;6)4位乘法器的顶层文件四、程序设计步骤1.打开ispEXPERT软件,建立一个新的工程cnt10;1 单击菜单Fil e→New Project2 输入工程路径,工程名2.建立VHDL文件单击File→New菜单项,选择VHDL File选项,单击OK按钮以建立VHDL文件,分别建立4位乘法器的vhd文件ANDARITH.VHD,ARICTL.VHD,REG8.VHD,SREG4B.VHD。

基于改进的 Booth 编码和 Wallace 树的乘法器优化设计

基于改进的 Booth 编码和 Wallace 树的乘法器优化设计石敏;王耿;易清明【摘要】According to the problem that multiplier can’t take into account both the path delay and layout area,we proposed a novel structure of 32 bit signed multiplier.Its characteristics are:the multiplier uses the improved Booth encoding to generate a partial product array ranging regularly,and the circuit it brought forth reduces the delay and area compared with traditional method;it employs the improved novel Wallace tree compressing structure which is the combination of 4 -2 compressor and 3 -2 compressor,and to compress 17 partial products into 2 ones only needs 10 XOR-delays,thus speeds up multiplication computation considerably.The whole design was verified on FPGA,and synthesised with SMIC 0.18 μm-based standard unit process.Synthesis results showed that the chip area was 0.1127 mm2 ,and the key path delay was 3.4ns.Experimental results also showed that the improved multiplier reduced both the key path delay and the layout area.%针对当前乘法器设计难于兼顾路径延时和版图面积的问题,设计一种新型的32位有符号数乘法器结构。

64位高性能嵌入式CPU中乘法器单元的设计与实现

学论作签: 、 位文者名 赵忠 民

Z 7 月1 ‘ 0 年3 日 0

经指导教师同意, 本学位论文属于保密, 在

本授 权书 。 指 导教师签名 : 年 月 日

年解密后适用

学 位论文作者签名:

年 月 日

同济大学学位论文原创性声明

本人郑重声明:所呈交的学位论文,是本人在导师指导下,进 行研究工作所取得的成果。除文中己经注明引用的内 容外,本学位 论文的研究成果不包含任何他人创作的、已公开发表或者没有公开 发表的作品的内容。 对本论文所涉及的研究工作做出贡献的其他个 人和集体,均己 在文中以明 确方式标明。本学位论文原创性声明的 法律责任由本人承担。

进行 了设计与实现 。

关键词 :定点乘法器,树型结构,Boh编码,进位保留加法器,42 ot - 压缩器, 混合电路结构

Ab t 以 sr a

AB T C S RA T

Muii s o h e ui f r rcs . a ei pi p ioe t ky to mc poesr h m ids n ni e lpe t lr n f e ns io o T e n g r c l

9 等, 步减少了Waa 树所需的 : 2 进一 lc le 计数器 个数[ [ 3 1

在乘法器拓 扑结构方面,进 入上世纪九十年代之后,进位保留加法被广泛

乘法器设计

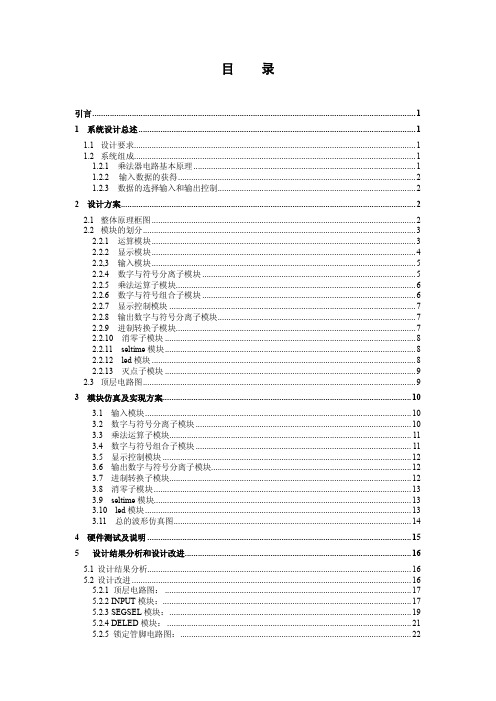

目 录引言 (1)1 系统设计总述 (1)1.1设计要求 (1)1.2系统组成 (1)1.2.1 乘法器电路基本原理 (1)1.2.2输入数据的获得 (2)1.2.3 数据的选择输入和输出控制 (2)2 设计方案 (2)2.1整体原理框图 (2)2.2模块的划分 (3)2.2.1 运算模块 (3)2.2.2 显示模块 (4)2.2,3 输入模块 (5)2.2.4 数字与符号分离子模块 (5)2.2.5 乘法运算子模块 (6)2.2.6 数字与符号组合子模块 (6)2.2.7 显示控制模块 (7)2.2.8 输出数字与符号分离子模块 (7)2.2.9 进制转换子模块 (7)2.2.10 消零子模块 (8)2.2.11 seltime模块 (8)2.2.12 led模块 (8)2.2.13 灭点子模块 (9)2.3顶层电路图 (9)3 模块仿真及实现方案 (10)3.1 输入模块 (10)3.2 数字与符号分离子模块 (10)3.3 乘法运算子模块 (11)3.4 数字与符号组合子模块 (11)3.5 显示控制模块 (12)3.6 输出数字与符号分离子模块 (12)3.7 进制转换子模块 (12)3.8 消零子模块 (13)3.9 seltime模块 (13)3.10 led模块 (13)3.11 总的波形仿真图 (14)4 硬件测试及说明 (15)5设计结果分析和设计改进 (16)5.1设计结果分析 (16)5.2设计改进 (16)5.2.1 顶层电路图: (17)5.2.2 INPUT模块: (17)5.2.3 SEGSEL模块: (19)5.2.4 DELED模块: (21)5.2.5 锁定管脚电路图: (22)5.2.6 电路波形图: (22)5.2.7 调试现象图: (22)6 课程总结 (23)参考文献 (24)附录:程序代码 (25)1 输入模块 (25)2 数字与符号分离子模块 (25)3 乘法运算子模块 (26)4 数字与符号组合子模块 (26)5 显示控制模块 (27)6 输出数字与符号分离子模块 (27)7 进制转换子模块 (28)8 消零子模块 (28)9 seltime模块 (29)10 led模块 (30)引言电子EDA技术发展迅猛,逐渐在教学、科研、产品设计与制造等各方面都发挥着巨大的作用。

64位高性能CPU中乘法器单元的设计与实现毕业论文

64位高性能CPU中乘法器单元的设计与实现摘要随着工艺水平的发展,集成电路设计向着速度更快,面积更小的方向稳步发展着。

处理器作为集成电路设计产品的代表,更是需要体现出这种发展趋势。

乘法器是现代微处理器芯片中的关键部件,其主要设计思想,就是在结构复杂度和电路类型,以及速度和面积之间进行均衡。

本文以此为基本出发点,首先对基4的改进Booth算法给出详细的推导,产生的部分积数目较传统的Booth算法减半,为后续的设计减小了压力。

然后,本文研究乘法器的核心部分——部分积压缩器的树型结构,并对用于压缩部分积的各种加法阵列结构进行分析和比较,提出一种以CSA 和4-2压缩器共同作为基本加法单元的混合电路结构,构建了一种独创的改进Wallace树型结构的乘法器,它在部分积求和过程中的硬件利用率达到了最高,有效地改进了传统Wallace树和其他结构的缺陷。

本论文编码采用硬件编程语言V erilog HDL来描述TOP-DOWN的设计全过程。

使用ModelSim软件对64位定点Wallace树型乘法器进行功能验证,得出此Wallace树型乘法器能正确实现乘法功能,并在一定程度上提高运行速度。

关键词定点乘法器;树型结构;Booth编码;混合电路结构The design and implementation of the multiplier module in CPU with 64-bit high-performanceAbstractAs technical level develops,IC design progresses in both the ways of higher speed and smaller area steadily.CPU is more likely to represent this trend for itis a typical product of IC design.Multiplier is one of the key units of microprocessor. The main design principle for a multiplier is a trade off balance among structure,implementation complexity,speed and area. Multiplication is based on partial product additions.In this thesis,first of all,the modified radix-4 Booth algorithm in conditions of signedmultiplication is figured out.The number of partial product can be reduced to half of the number by original Booth algorithm,which deco mpresses the follow steps.After that,tree structures of the compressors considering are presented,this thesis then proposes a novel architecture for 64-bit fixed-point tree multiplier, employing both carry-save adder and 4-2 compressor as its basic adder units under the frame work of a particular instruction set architecture. It offers the best efficiency in obtaining the sum of the partial products and improves the shortcomings of the original Wallace tree and other prior arts.In this paper, hardware encoding Verilog HDL programming language is described the design of TOP DOWN the entire process.This thesis reports the implementation of a 64-bit fixed-point pipe tree multiplier in V erilog HDL, processing functional verification with the ModelSim software and arithmetic logic unit to increase the operating speed.Keywords fixed-point multiplier; tree structure; Booth encoder;hybrid circuit structure目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 课题背景 (1)1.2国内外研究现状 (1)1.2.1 国外研究情况 (2)1.2.2 国内研究情况 (2)1.3 课题的研究内容及论文安排 (3)1.3.1 主要工作 (3)1.3.2 论文安排 (3)第2章乘法器相关知识简介 (5)2.1 全定制设计方法流程 (5)2.2 乘法运算的基本原理 (7)2.2.1 乘法器的一种硬件实现方法 (7)2.2.2 移位相加乘法器的分析 (10)2.3 本章小结 (10)第3章改进Wallace树型乘法器结构分析与设计 (11)3.1 Booth算法 (11)3.1.1 Booth算法基本原理 (11)3.1.2 基4的Booth算法 (13)3.2 补位逻辑 (15)3.3 阵列乘法器 (17)3.3.1 乘法器中加法阵列结构 (17)3.3.2 乘法器结构的选择 (20)3.4 改进的乘法器结构设计 (25)3.4.1 基于4-2压缩器的乘法器结构设计 (25)3.4.2 采用混和电路结构的Wallace树型乘法器设计 (28)3.5阵列乘法器分析比较 (30)3.6 本章小结 (32)第4章改进Wallace树型乘法器实现与功能验证 (34)4.1 加法器模块生成 (35)4.1.1 一位全加器 (35)4.1.2 CSA模块 (37)4.1.3 4-2压缩器模块 (37)4.2 乘法器模块 (38)4.3 波形仿真和验证 (39)4.3.1 波形仿真 (40)4.3.2 结果分析 (41)4.4 本章小结 (41)结论 (42)致谢 (44)参考文献 (45)附录 (47)第1章绪论1.1课题背景随着微电子技术的不断进步、计算机技术的不断发展,集成电路经历了小规模、中规模、大规模的发展过程,目前已经进入超大规模(VLSI)和甚大规模集成电路(ULSI)阶段。

基于标准单元库扩展的快速乘法器设计

De in o ih s e d mu t l rb s d o tn a d c l l r r xe so sg fh g —p e l p i a e n sa d r el i ay e tn in i e b

适 用 于电路 负载过 大的情 况。

关键 词 :乘法 器 ; 准单元 库扩展 ; 标 改进 的 Bo 编码 算法 ; lc 树 ; ot h Waae l 逻辑功 效

中图分类 号 :T 4 N7 文献标 志码 :A 文章编 号 :10 — 6 5 2 1 )5 17 —3 0 1 3 9 (0 2 0 — 7 8 0

基 金 项 目 :国 家科 技 重 大专 项 基 金 资 助 项 目(09 X 13 .0 .0 ) 2 0 Z 0 00 0 10 2 .

作者简介 : 曾宪恺( 97 ) 男, 1 8 - , 湖北孝感人 , 士, 硕 主要研究方向为超 大规模 集成 电路设计 自动化 (egk l. j eu c ) 郑 丹丹( 9 1 ) znx @vs zu d .n ; i . 18一 , 女, 博士, 主要研究方向为超 深亚微 米集成 电路 S C设计 ; O 严晓浪( 97 ) 男, 授, 14 一 , 教 主要研 究方向为超 大规模 集成 电路 设计、 L I 计 自动化 ; VS设 吕冬 明(9 1 ) 男, 18 一 , 博士, 主要研 究方 向为集成电路 C D研 究; A 葛海通( 92 ) 男, 1 7 . , 博士 , 主要研究方向为嵌入式 系统设计 .

算, 最差情 况下 ( 工作电压 0 9V, . 温度 15℃) 2 工作频率为 3 6 4

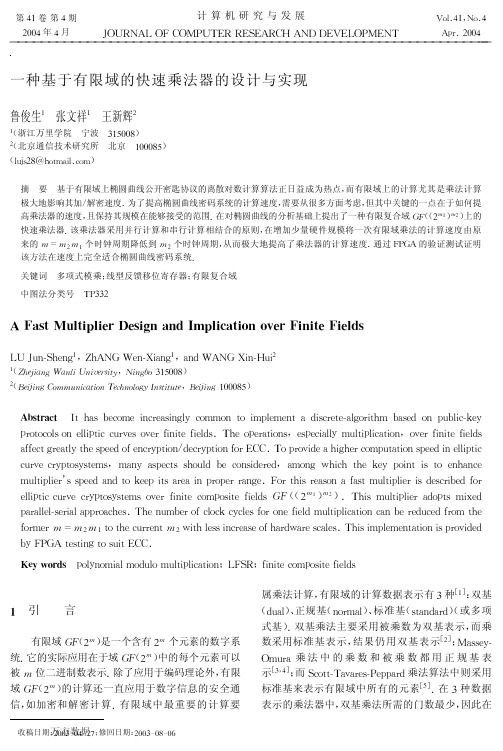

一种基于有限域的快速乘法器的设计与实现

如图2所示,则D(z)=A(z)B(z).

D(z)=Al(z)×Bl(z),

D(z)=Do(z)+z‘72[Dl(z)一Do(z)一

D2(z)]+z7D2(z).

(10)

通过式(9)和式(10)可将系数的乘法次数由原

来的n2减少到3/4”2(见文献[6]).

。固回 田田 圆圈

。匝五习 E互]

困

固

图2 Do(z)=AI(z)×Bl(z)

设.万=(方%数0据,’0),/ =(%8,’8)是 & 上任意两

点,0 是./ 连线%若 . 和/ 0 和曲线相交于 另一点1,02是1 点和无穷远点3 的连线,也就是 说02是过1 点引’ 轴平行线,02和曲线相交于一点 12,用.%/ 表示%若. 和/ 关于% 轴对称或重合 于% 轴,则./ 垂直于% 轴,这时 0 和椭圆曲线相 交于无穷远点3%如图0所示:

L i=1,…,n一2;j=1,’’‘,n

于是式(3)的计算可如下表示

1

(5)

印

fl

C

F曰

:

●

fH l

60

0

^

6l (6)

如;o ∞

o ,:h

:

6。1

其中

【口。,i=O,…,∞一1;J=0,

J

H

几:l““刊嘶一蚤弘一一一…(7)

i=0,l,·一,” 1; l J=1,…,n一1,

,

、

IO, i<J,

图0 椭圆曲线的点加

椭圆曲线的乘法是标量乘以点,即 !.=.0> .8>…>.!%椭圆曲线在有限域 #$(8! )上关于 上述加和乘法构成群%基于椭圆曲线的密码系统主 要的计算表现为标量乘法运算,其中 ! 的值往往很 大,一般情况 下 取 012345% 根 据 下 面 点 加 运 算 规 则 可知,有限域上的乘法运算在整个椭圆曲线密码计 算的计算量%

一种64位Booth乘法器的设计与优化

一种64位Booth乘法器的设计与优化何军;朱英【摘要】In order to solve the issue of large area and power dissipation overhead of the 64-bit integer multiplier of the homebred multr-core processor, the Booth encoding algorithm is optimized and a new Booth encoding is put forward. The correction of the optimized design is verified through multiple methods, and the design is logic synthesized based on standard cell library. As is turned out that the design can work at 1.0 GHz at least, its area is reduced by 9.64% and its dynamic and leakage power dissipation is decreased by 6.34% and 11.98%, which means the optimization can decrease the area and power consumption of multiplier effectively as expected.%针对国产多核处理器的64位整数乘法器面积和功耗开销大的问题,提出一种新的Booth编码方式,对其Booth编码方式进行优化,通过多种方法验证设计优化的正确性,采用标准单元库进行逻辑综合评估.结果表明,工作频率可达1.0 GHz以上,面积减少9.64%,动态功耗和漏电功耗分别减少6.34%和l 1.98%,能有效减少乘法器的面积和功耗,达到预期目标.【期刊名称】《计算机工程》【年(卷),期】2012(038)016【总页数】2页(P253-254)【关键词】Booth编码;并行乘法器;64位乘法器;设计优化;功耗【作者】何军;朱英【作者单位】上海高性能集成电路设计中心,上海201204;上海高性能集成电路设计中心,上海201204【正文语种】中文【中图分类】TP3681 概述乘法器是微处理器和数字信号处理器(DSP)中最基本的运算单元,其速度与处理器的性能密切相关[1]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

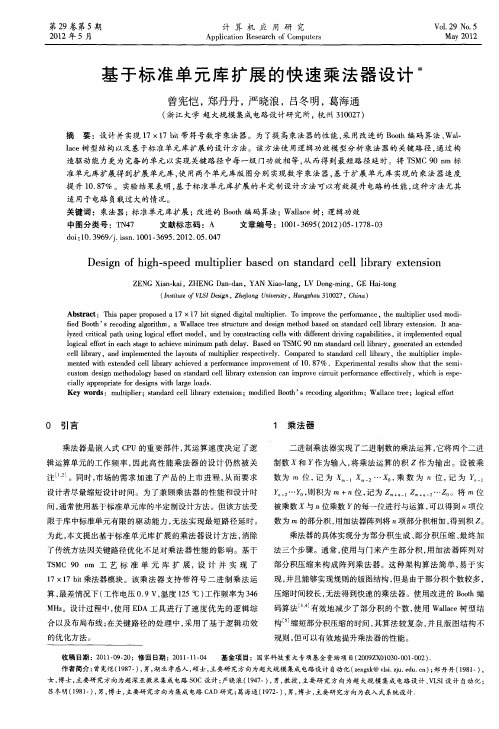

收稿日期:2011-09-20;修回日期:2011-11-04基金项目:国家科技重大专项基金资助项目(2009ZX01030-001-002).作者简介:曾宪恺(1987-),男,湖北孝感人,硕士,主要研究方向为超大规模集成电路设计自动化(zengxk@vlsi.zju.edu.cn );郑丹丹(1981-),女,博士,主要研究方向为超深亚微米集成电路SOC 设计;严晓浪(1947-),男,教授,主要研究方向为超大规模集成电路设计、VLSI 设计自动化;吕冬明(1981-),男,博士,主要研究方向为集成电路CAD 研究;葛海通(1972-),男,博士,主要研究方向为嵌入式系统设计.基于标准单元库扩展的快速乘法器设计*曾宪恺,郑丹丹,严晓浪,吕冬明,葛海通(浙江大学超大规模集成电路设计研究所,杭州310027)摘要:设计并实现17ˑ17bit 带符号数字乘法器。

为了提高乘法器的性能,采用改进的Booth 编码算法、Wal-lace 树型结构以及基于标准单元库扩展的设计方法。

该方法使用逻辑功效模型分析乘法器的关键路径,通过构造驱动能力更为完备的单元以实现关键路径中每一级门功效相等,从而得到最短路径延时。

将TSMC 90nm 标准单元库扩展得到扩展单元库,使用两个单元库版图分别实现数字乘法器,基于扩展单元库实现的乘法器速度提升10.87%。

实验结果表明,基于标准单元库扩展的半定制设计方法可以有效提升电路的性能,这种方法尤其适用于电路负载过大的情况。

关键词:乘法器;标准单元库扩展;改进的Booth 编码算法;Wallace 树;逻辑功效中图分类号:TN47文献标志码:A文章编号:1001-3695(2012)05-1778-03doi :10.3969/j.issn.1001-3695.2012.05.047Design of high-speed multiplier based on standard cell library extensionZENG Xian-kai ,ZHENG Dan-dan ,YAN Xiao-lang ,LV Dong-ming ,GE Hai-tong(Institute of VLSI Design ,Zhejiang University ,Hangzhou 310027,China )Abstract :This paper proposed a 17ˑ17bit signed digital multiplier.To improve the performance ,the multiplier used modi-fied Booth ’s recoding algorithm ,a Wallace tree structure and design method based on standard cell library extension.It ana-lyzed critical path using logical effort model ,and by constructing cells with different driving capabilities ,it implemented equal logical effort in each stage to achieve minimum path delay.Based on TSMC 90nm standard cell library ,generated an extended cell library ,and implemented the layouts of multiplier respectively.Compared to standard cell library ,the multiplier imple-mented with extended cell library achieved a performance improvement of 10.87%.Experimental results show that the semi-custom design methodology based on standard cell library extension can improve circuit performance effectively ,which is espe-cially appropriate for designs with large loads.Key words :multiplier ;standard cell library extension ;modified Booth ’s recoding algorithm ;Wallace tree ;logical effort0引言乘法器是嵌入式CPU 的重要部件,其运算速度决定了逻辑运算单元的工作频率,因此高性能乘法器的设计仍然被关注[1,2]。

同时,市场的需求加速了产品的上市进程,从而要求设计者尽量缩短设计时间。

为了兼顾乘法器的性能和设计时间,通常使用基于标准单元库的半定制设计方法。

但该方法受限于库中标准单元有限的驱动能力,无法实现最短路径延时。

为此,本文提出基于标准单元库扩展的乘法器设计方法,消除了传统方法因关键路径优化不足对乘法器性能的影响。

基于TSMC 90nm 工艺标准单元库扩展,设计并实现了17ˑ17bit 乘法器模块。

该乘法器支持带符号二进制乘法运算,最差情况下(工作电压0.9V ,温度125℃)工作频率为346MHz 。

设计过程中,使用EDA 工具进行了速度优先的逻辑综合以及布局布线;在关键路径的处理中,采用了基于逻辑功效的优化方法。

1乘法器二进制乘法器实现了二进制数的乘法运算,它将两个二进制数X 和Y 作为输入,将乘法运算的积Z 作为输出。

设被乘数为m 位,记为X m -1X m -2…X 0,乘数为n 位,记为Y n -1Y n -2…Y 0,则积为m +n 位,记为Z m +n -1Z m +n -2…Z 0。

将m 位被乘数X 与n 位乘数Y 的每一位进行与运算,可以得到n 项位数为m 的部分积,用加法器阵列将n 项部分积相加,得到积Z 。

乘法器的具体实现分为部分积生成、部分积压缩、最终加法三个步骤。

通常,使用与门来产生部分积,用加法器阵列对部分积压缩来构成阵列乘法器。

这种架构算法简单,易于实现,并且能够实现规则的版图结构,但是由于部分积个数较多,压缩时间较长,无法得到快速的乘法器。

使用改进的Booth 编码算法[3,4]有效地减少了部分积的个数,使用Wallace 树型结构[5]缩短部分积压缩的时间,其算法较复杂,并且版图结构不规则,但可以有效地提升乘法器的性能。

第29卷第5期2012年5月计算机应用研究Application Research of Computers Vol.29No.5May 20122乘法器的结构设计采用改进的Booth 编码算法和Wallace 树型结构实现17ˑ17bit 带符号数字乘法器。

其结构如图1所示。

2.1改进的Booth 编码算法改进的Booth 编码算法对乘数重新编码。

对于17bit 的乘数,在最低位补一个0,记为Y [-1],在最高位补一个符号位,即Y [-16]。

然后从低位Y [1]开始,每三位作为一组,并且每两组之间重叠一位,将乘数分为9组,对每一组按表1方式重新编码,表中X 表示被乘数。

表1改进的Booth 编码Y j +1Y j Y j -1编码NEG X 2ZERO Y j +1Y j Y j -1编码NEG X 2ZERO 0000011100-2X 110001+X 000101-X 100010+X 000110-X 100011+2X1111111为了实现改进的Booth 编码算法,引入三个控制信号X 2、NEG 、ZERO [6]。

其取值如表1所示,即ZERO =Y j +1Y j Y j -1+Y —j +1Y —j Y —j -1NEG =Y j +1X 2=Y j Y j -1+Y —j Y —j -1用X 2、NEG 、ZERO 作为选择器的控制端,实现被乘数移位和取反操作。

改进的Booth 编码实现方案如图2所示。

采用改进的Booth 编码算法,仅产生9个部分积,大大减少了部分积的个数。

当部分积为负时,需要取反加1,如果使用加法器直接执行加1操作,会引入很大延时。

将加1操作移至下一部分积中,在部分积压缩中一起完成,可以省去此延时[7]。

2.2部分积符号位扩展对于17ˑ17bit 带符号位乘法运算,产生34bit 积。

为了保证运算结果正确,需要对每一项部分积进行符号位扩展。

通常的做法是将每一项部分积扩展到34bit ,然后进行部分积压缩,如图3(a )所示,图中黑色部分表示扩展的符号位;PP i _S 分别代表第i 项部分积PP i 产生时可能的加1操作,若该项部分积为正,PP i _S 取0;若该项部分积为负,PP i _S 取1。

该方法会增加一定的硬件开销,因此对部分积符号位进行特殊处理[7]:将第一项部分积PP 1高位扩展3bit (S S S ),将其他部分积高位扩展2bit (1S ),如图3(b )所示,其中S 为当前部分积的符号位,S为部分积符号位取反。

对部分积符号位特殊处理之后,可以使用较少的硬件资源实现带符号乘法运算。

2.3Wallace 树型结构若部分积为负,需要执行取反加1操作。

第9项部分积PP 9的加1操作无法移到后面与下一个部分积求和一起完成。

对此,使用一级半加器对PP 9_S 进行预处理,同时处理其他部分积的PP i _S 位。

将预处理之后的部分积作为Wallace 树型结构的输入,经过四级加法器压缩成为两项部分积,如图4所示,其中CSA 表示进位保留加法器。

对于9项部分积,在压缩阵列的第一级使用三组CSA 将其压缩为6项;在第二级使用两组CSA 将其压缩为4项;第三级和第四级各使用1组CSA 将部分积压缩至两项。

具体压缩过程如图5所示,其中实线表示经过一级CSA 压缩;虚线表示将三项部分积分成一组,并将其作为一组CSA 的输入。

将压缩之后的两项部分积输入到超前进位加法器,得到最终的乘法运算结果。

3标准单元库扩展及乘法器优化算法3.1乘法器关键路径采用改进的Booth 编码算法和Wallace 树型结构实现的17ˑ17bit 乘法器的关键路径如图6所示。

关键路径延时为所有门延时之和。

引入逻辑功效[8],单个门延时采用线性延时模型等效为式(1)。

T p =T p 0(P +GF /r )(1)其中:t p 0为反相器的延时;P 为门电路本征延时与反相器本征延时之比,其值与电路及版图结构有关;G 为逻辑功效,其物理意义为:与反相器相比,复杂门电路因拓扑结构的复杂度导致的驱动能力减弱情况,G 值与电路结构有关,通过HSPICE 仿真计算得到;F 为有效扇出,其值等于外部负载电容与输入电容之比;r 为门本征寄生电容与输入电容之比,其值与工艺相关。