集成电路课程设计74HC138

74HC138_中文资料(工程师必备蓝桥)

74HC138:工程师必备的蓝桥芯片详解一、74HC138芯片概述1. 输入端:具有3个地址输入端(A、B、C)和1个使能端(E1、E2A、E2B);2. 输出端:共有8个输出端(Y0至Y7),分别对应8种不同的输入状态;3. 逻辑功能:当使能端有效时,根据地址输入端的组合,选择一个输出端为低电平,其余输出端为高电平;4. 驱动能力:输出端可驱动8个TTL负载。

二、74HC138芯片引脚功能1. A、B、C:地址输入端,用于选择输出端;2. E1:使能端1,低电平有效;3. E2A、E2B:使能端2,用于扩展译码器,低电平有效;4. Y0至Y7:输出端,对应8种不同的输入状态。

三、74HC138芯片工作原理74HC138芯片的工作原理如下:1. 当使能端E1为低电平,且E2A和E2B中至少有一个为高电平时,芯片处于工作状态;2. 根据地址输入端A、B、C的组合,选择一个输出端为低电平,其余输出端为高电平;3. 当使能端无效时,所有输出端均为高电平。

四、74HC138芯片应用示例假设我们需要设计一个电路,根据输入的三个开关状态(A、B、C),控制8个LED灯的亮灭。

具体步骤如下:1. 将74HC138芯片的A、B、C端分别连接到三个开关;2. 将E1端接地,确保芯片始终处于工作状态;3. 将E2A和E2B端接高电平,扩展译码器功能;4. 将Y0至Y7端分别连接到8个LED灯的正极,负极接地;5. 根据开关状态,对应的LED灯会点亮。

五、74HC138芯片的优势与应用场景74HC138芯片以其独特的优势,在多个领域发挥着重要作用:1. 优势:高集成度:一个小巧的芯片就能实现八路译码功能;低功耗:CMOS工艺制造,功耗较低,适用于电池供电设备;稳定性强:输出端具有高抗干扰能力,确保电路稳定运行;兼容性好:与TTL逻辑电平兼容,便于与其他数字电路芯片配合使用。

2. 应用场景:数字电路设计:用于地址译码、信号分配等;自动化控制:实现多种控制信号的切换;仪器仪表:用于多通道选择和信号处理;计算机及外设:用于接口电路设计,实现数据传输和控制。

74HC138三八译码器的应用 - 单片机

74HC138三八译码器的应用 - 单片机在我们设计单片机电路的时候,单片机的IO口数量是有限的,有时并满足不了我们的设计需求,比如我们的STC89C52RC一共是32个IO口,但是我们为了控制更多的器件,就要使用一些外围的数字芯片,这种数字芯片由简单的输入逻辑来控制输出逻辑,比如74HC138这个三八译码器,图1是74HC138在我们原理图上的一个应用。

图174HC138应用原理图从这个名字来分析,三八译码器,就是把3种输入状态翻译成8种输出状态。

从图1所看出来的,74HC138一共有1~6一共是6个输入引脚,但是其中4、5、6这三个引脚是使能引脚。

使能引脚和我们前边讲74HC245的OE引脚是一样的,这三个引脚如果不符合规定的输入要求,Y0到Y7不管你输入的1、2、3引脚是什么电平状态,总是高电平。

所以我们要想这个74HC138正常工作,ENLED那个输入位置必须输入低电平,ADDR3位置必须输入高电平,这两个位置都是使能控制端口。

不知道大家是否记得我们第二课的程序有这么两句ENLED=0;ADDR3=1;就是控制使这个74HC138使能的。

这类逻辑芯片,大多都是有使能引脚的,使能符合要求了,那下面就要研究逻辑控制了。

对于数字器件的引脚,如果一个引脚输入的时候,有0和1两种状态;对于两个引脚输入的时候,就会有00,01,10,11这四种状态了,那么对于3个输入的时候,就会出现8种状态了,大家可以看下边的这个真值表——图,其中输入是A2,A1,A0的顺序,输出是从Y0,Y1....Y7的顺序。

图274HC148真值表从图2可以看出,任一输入状态下,只有一个输出引脚是低电平,其他的引脚都是高电平。

我们清楚的知道,8个LED小灯的总开关三极管Q16基极的控制端是LEDS6,也就是Y6输出一个低电平的时候,可以开通三极管Q16,从右侧的希望输出的结果,我们可以推导出我们的A2,A1,A0的输入状态应该是110,那我们再来看下原理图3。

74HC138

`LS138 最大 单位 V V

-1.5

0.4 0.5 V 0.1 20 0.1 20 -0.4 mA mA μA mA μA -40 -42 10 mA mA

IOS 输出短路电流 Icc 电源电流

【1】 :测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

动态特性(TA=25℃) ‘S138 最大 7 10.5 Vcc=5V CL=15pF RL=280Ω (‘LS138 为 2KΩ) 12 12 8 11 ‘LS138 最大 20 41 27 39 18 32 26 38 ns

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为 低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低 电平译出。 利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反 相器还可级联扩展成 32 线译码器。 若将选通端中的一个作为数据输入端时,138 还可作数据分配器。 管脚图:

54138/74138

3 线-8 线译码器 简要说明: 138 为 3 线-8 线译码器,共有 54/74S138 和 54/74LS138 两种线路结构型式,其主 要电特性的典型值如下: 型号 CT54S138/CT74S138 CT54LS138/CT74LS138 Tpd (ABC->Y)(3 级) 8ns 22ns PD 245mW 32mW

kings

`S138 测试条件【1】 最小 最大 最小 Vcc 最小 IIK=-12mA 54 -1.2 Vcc=最小, VIH=2V,VIL=最大, IOH=最大 VCC=最 小,VIH=2V,VIL=最 大,IOL=最大 Vcc=5V 2.5 2.5 74 2.7 2.7 54 0.5 74 0.5 1 VI=5.5V VI=7V 50 1 VI=5.5V VI=7V VIH=2.7V VIL=0.4 V VIL=0.5 V 54 74 -40 -40 -2 -100 -100 74 -6 -5 50 Vcc=5V,VIH=2.7V Vcc=最大 Vcc=最大 Vcc=最大 Vcc=最大 Vcc=最大

74HC138概述

74HC138概述1.输入输出电压范围广:74HC138可以接受2V到6V的输入电压,同时其输出也可以在整个电源电压范围内工作。

2.低功耗:相较于传统的TTL器件,CMOS技术使得74HC138具有较低的功耗,能够有效降低电路的发热和功耗。

3.高速操作:74HC138在1.5V至6V的电源电压下,其传输延迟非常小,可以实现高速操作。

4.集成电路设计:74HC138具有集成电路设计的优势,可以将多个逻辑门的功能集成在一颗芯片中,从而减少了电路板上的元器件数量和连线数量。

5.三-八线译码器解码器:74HC138具有三个输入引脚(A0,A1和A2)和八个输出引脚(Y0至Y7)。

根据输入的二进制编码,译码器可以将其转换为相应的输出信号。

6.节省IO口:通过使用74HC138,可以将一个微控制器的输出端口连接到译码器的输入端口,从而实现多个输入/输出设备的控制。

这样就可以节省大量的IO口,提高系统的扩展性。

7.灵活的应用:74HC138可以用于地址译码器的设计,用于选择存储器、IO设备和外围设备。

同时,它也可以用于多路选择器、多维逻辑交叉开关等应用。

8.可靠性:74HC138具有较高的可靠性和稳定性,能够在各种环境条件下稳定工作。

使用74HC138进行地址译码器设计时,用户可以通过将地址总线连接到译码器的输入引脚,将存储器、IO设备和外围设备连接到译码器的输出引脚,从而实现对这些设备的选择和控制。

通过对输入信号和输出信号的编码和解码,地址译码器能够根据用户的需求正确选择所需的设备。

总之,74HC138是一种高性能的三-八线译码器解码器,具有广泛的应用领域和诸多优势。

在数字电路设计中,使用74HC138可以简化电路结构、节省资源、提高系统性能和可靠性,因此在电子工程领域有着重要的地位和作用。

74hc138的工作原理

74hc138的工作原理74HC138是一种集成电路,它是一个3-8线解码器。

它具有8个输出位线(Y0至Y7)和3个输入位线(A0、A1和A2)。

工作原理如下:当74HC138的使能端(E1、E2和E3)为高电平时,解码器开始工作。

使能端的状态可以通过逻辑门或外部信号来控制。

使能端为低电平时,解码器处于无效状态,输出线的状态是未定义的。

输入位线(A0、A1和A2)用于选择要输出的位线。

通过调整输入位线的状态,可以选择8个输出位线中的一个进行激活。

接下来,我们将更详细地描述74HC138的工作原理。

1. 输入编码:输入位线(A0、A1和A2)用于输入编码信息。

通过将这些位线连接到逻辑高电平或逻辑低电平,可以选择需要激活的输出位线。

具体而言,有8种不同的输入编码方式可以选择一个或多个输出位线。

2. 译码和输出:根据输入编码的不同组合,解码器将选择一个或多个输出位线进行激活。

当输入编码为特定模式时,相应的输出位线将被拉低,其他输出位线将保持高电平状态。

这意味着在激活位线上会有一个低电平信号。

例如,当输入编码为000时,输出位线Y0将被选中;当输入编码为001时,输出位线Y1将被选中;以此类推,当输入编码为111时,输出位线Y7将被选中。

请注意,如果使用74HC138的使能端(E1、E2和E3)为低电平,则解码器的输出位线的状态将保持未定义,无论输入编码的状态如何。

3. 逻辑门操作:在74HC138电路中,逻辑门用于控制使能端的状态。

当使能端为高电平时,解码器工作;当使能端为低电平时,解码器处于无效状态。

这意味着无论输入编码如何,输出位线的状态都将是未定义的。

逻辑门操作的目的是选择解码器的工作模式。

通过将多个74HC138连接到逻辑门或其他逻辑电路,可以实现更复杂的逻辑功能。

总结:74HC138是一种3-8线解码器,可以将输入编码转换为相应的输出位线。

通过选择不同的输入编码组合,可以选择一个或多个输出位线进行激活。

译码器74HC138中文资料

译码器74HC138中文资料2010-01-01 08:00集成电路介绍:译码器74HC138中文资料74hc138 3-8线译码器,译码器也称解码器,译码过程实际上是一种翻译过程,即编码的逆过程。

译码器的输入是n位二值代码,输出是m个表征代码原意的状态信号(或另一种代码)。

一般情况下有m小于等于2的n次方,即译码器输入线比输出线要少。

译码器按其功能可分为三大类:(1)变量译码器:将输入的二进制代码还原为原始输入信号。

例如有两位二进制代码(0 ,1),可经译码器还原为四个信号状态(0,0)(0,1)(1,0) (1,1)(2)代码变换译码器:用于将一个数据的不同代码之间的相互转换。

例如二-十进制译码器可将8421码转换为十个状态。

(3)显示译码器:将数字、文字或符号的代码还原成相应的数字、文字、符号并显示出来的电路74hc138 3-8线译码器/CD74HC138 ,CD74HC238和CD74HCT138 , CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

hc138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

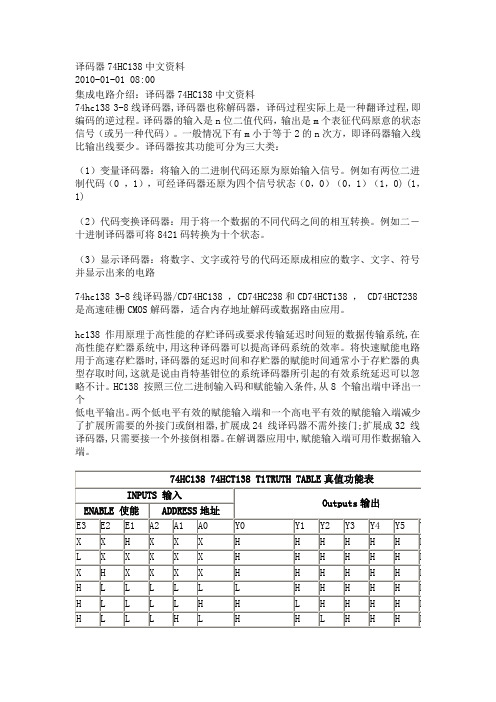

H L L L H H H H H L H H H H L L H L L H H H H L H H H L L H L H H H H H H L H H L L H H L H H H H H H L H L L H H H H H H H H H HCD74HC238, CD74HCT238 T1TRUTH TABLE真值表INPUTS 输入Outputs输出ENABLE 使能ADDRESS地址E3 E2 E1 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 X X H X X X L L L L L L L L X X X X X L L L L L L L X H X X X X L L L L L L L H L L L L L H L L L L L L H L L L L H L H L L L L L H L L L H L L L H L L L L H L L L H H L L L H L L L H L L H L L L L L L H L L H L L H L H L L L L L H L H L L H H L L L L L L L H H L L H H H L L L L L L L图1 引脚图图2 功能图图3 测试电路和波形应用电路:图4 舞台发光二极管灯光图5 可编程时钟定时器电路由上表可见74HC138译码器输出低电平有效。

74hc138的应用原理

74HC138的应用原理介绍74HC138是一种三到八线解码器,通常被用于数字电路设计中。

它具有识别三个输入信号,并将其映射到八个输出之一的功能。

本文将介绍74HC138的工作原理及其应用。

工作原理74HC138由三个二输入正逻辑门和一个三输入与非门组成。

它的三个输入(A0,A1和A2)可以表示八个不同的输入组合,输出由Y0到Y7表示。

通过设置三个输入信号中的不同组合,可以选择要激活的输出。

接下来,我们将详细介绍74HC138的应用原理。

使用示例以下是一个使用74HC138的示例电路图:python +—–+ +—–+ A0 —-| |————–| | | 74HC138 Y0 —- | A1 —-| |————–| | + +—–+ + +—–+ A2 —-| | | | | Decoder | | Register | | | | | E1 —-| | | | E2 —-| | | | E3 —-| | | | +————+ +————+ | | | | | 74LS138 | | 74LS175 | | | | | | | | | +————+ +————+ ```在上述电路中,输入A0,A1和A2信号用于选择要激活的输出。

74HC138芯片将输入信号和输出互相连接,并通过输出信号将电流传递到68LS175寄存器芯片。

功能以下是74HC138的功能:1.选择输出信号:通过设置输入A0,A1和A2的不同组合,可以选择激活的输出。

共有八个输出(Y0到Y7)。

2.输入信号:74HC138接收三个输入信号(A0,A1和A2)。

3.解码功能:74HC138将输入信号解码为对应的输出信号。

4.数字电路集成:74HC138是一个数字电路集成芯片,通过一片芯片就能实现数字信号的输入和输出。

应用领域74HC138广泛应用于以下领域:1.数字系统设计:74HC138用于基于数字信号的系统设计,如计算机、电子设备等。

数字集成电路课程设计74hc138

目录1.目的与任务 (1)2.教学内容基要求 (1)3.设计的方法与计算分析 (1)3.1 74H C138芯片简介 (1)3.2 电路设计 (3)3.3功耗与延时计算 (6)4.电路模拟 (14)4.1直流分析 (15)4.2 瞬态分析 (17)4.3功耗分析 (19)5.版图设计 (19)5.1 输入级的设计 (19)5.2 内部反相器的设计 (19)5.3输入和输出缓冲门的设计 (22)5.4内部逻辑门的设计 (23)5.5输出级的设计 (24)5.6连接成总电路图 (24)5.3版图检查 (24)6.总图的整理 (26)7.经验与体会 (26)8.参考文献 (26)附录 A 电路原理图总图 (28)附录B总电路版图 (29)集成1. 目的与任务本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

2. 教学内容基本要求2.1课程设计题目及要求器件名称:3-8译码器的74HC138芯片 要求电路性能指标:⑴可驱动10个LSTTL 电路(相当于15pF 电容负载); ⑵输出高电平时,OH I ≤20uA,min,OH V =4.4V; ⑶输出低电平时,OLI ≤4mA ,manOL V , =0.4V⑷输出级充放电时间r t =ft ,pdt <25ns ;⑸工作电源5V ,常温工作,工作频率workf =30MHZ ,总功耗maxP =15mW 。

2.2课程设计的内容 1. 功能分析及逻辑设计; 2. 电路设计及器件参数计算;3. 估算功耗与延时;4. 电路模拟与仿真;5. 版图设计;6. 版图检查:DRC 与LVS ;7. 后仿真(选做);8. 版图数据提交。

2.3课程设计的要求与数据1. 独立完成设计74HC138芯片的全过程;2. 设计时使用的工艺及设计规则: MOSIS:mhp_ns5;3. 根据所用的工艺,选取合理的模型库;4. 选用以lambda(λ)为单位的设计规则;3. 设计的方法与计算分析3.1 74HC138芯片简介74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL 系列图3-1 74HC138管脚图表3-1 74HC138真值表由于74HC138芯片是由两个2-4译码器组成,两个译码器是独立的,所以,这里只分析其中一个译码器。

7.1 74HC138测试电路设计与搭建

根据图 7-3 所示搭建 74HC138 测试电 路, 74HC138 测试板卡的正面如图 7-4 所示。根据图 7-3, 使用 LK8820 提供 的万能测试板焊接 74HC138 测试电路 板, 将焊接完成的 74HC138 测试电路 板插到 DUT 板卡的正面, 使用杜邦线将 74HC138 测试电路板与 DUT板卡连接 起来。

图7-1 74HC138引脚图

7.1.2 认识74HC138

2. 74HC138芯片的真值表

74HC138 真值表如表 7-2 所示。

表7-2 74HC138真值表

7.1.2 认识74HC138

3. 74HC138芯片的工作原理

图7-2 74HC138工作原理

7.1.3 74HC138测试电路设计与搭建

《集成电路封装与测试》课程

项目七:74HC138 芯片测试

7.1 74HC138 测试电路设计与搭建

74HC138测试电路设计与搭建

知识目标

7.1.1 任务描述

利用 LK8820 集成电路测试平台和 LK230T 集成电路应用开发资源系统, 根据 74HC138 译码器工作原理, 完成 74HC138 测试电路设计与搭建, 要求如下。 (1)测试电路能实现 74HC138 的开短路、 静态工作电流、 直流参数及功能测试。 (2)74HC138 测试电路的搭建, 采用基于测试区的测试方式, 也就是把 LK8820 与LK230T 的测 试区结合起来, 完成 74HC138 测试电路搭建。 74HC138 是一款高速 CMOS 元器件, 具有传输延迟时间短、 高性能的特点。 例如, 在高性能存 储器系统中, 使用 74HC138 译码器可以提高译码系统的效率。

利用74HC138制作4线—16线译码器

《组合逻辑电路的分析与设计》————利用74HC138制作4线—16线译码器院系:电子与信息工程学院利用74HC138制作4线—16线译码器一、实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

二、实验仪器1、数字电路实验箱2、74HC138 3-8线译码器 2片三、实验原理1、CMOS器件74HC138的逻辑功能及应用74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

其引脚排列如下图(一)所示图(一)74HC138功能表如下表(一)所示:输入输出E1(非)E2(非)E3A2A1AY0(非)Y1(非)Y2(非)Y3(非)Y4(非)Y5(非)Y6(非)Y7(非)H L H L L L L H H H H H H H H L H L L H H L H H H H H H H L H L H L H H L H H H H H H L H L H H H H H L H H H H H L H H L L H H H H L H H H H L H H L H H H H H H L H H H L H H H L H H H H H H L H L L H H H H H H H H H H H LL X X X X X H H H H H H H H X H X X X X H H H H H H H H表(一)3、用两个3线-8线译码器构成4线-16线译码器。

74HC138应用,讲得真的很清楚、很明白。

74HC138资料及应用一、74HC138管脚图E3、E2、E1是使能输入端,E1和E2低电平有效,E3高电平有效。

A0、 A1和A3是控制输入端,由他们的组合决定Y的输出。

Y0——Y7是输出端,输出低电平,同一时刻八个Y之中只有一个输出有效。

74HC138图二、真值表三、引脚接法及应用举例(一)74HC138连接图(1)接法如上图中所示,一般1.E3 接电源、E2、E1接地;2.管脚A、B、C接单片机P口的控制信号;3.Y0——Y7接输出对象。

(2)应用举例上图中,输入管脚A、B、C分别由P1.0、P1.1、P1.2信号控制,Y0——Y7输出做其他芯片的片选信号。

根据真值表,当P1.0=0、P1.1=0 、P1.2=0时,Y0=0,CS1=0,选通62256芯片;同理,当P1.0=1、P1.1=0 、P1.2=0时,Y1=0,CS2=0,选通DS12887芯片。

其他依次类推。

(二)E3 接高、E2、E1接地。

一个简易程序:138译码器实验控制跑马灯#include <reg51.h>sbit HC138A = P2^2; //定义译码器输入端A 在 P2.2 管脚上sbit HC138B = P2^3; //定义译码器输入端B 在 P2.3 管脚上sbit HC138C = P2^4; //定义译码器输入端C 在 P2.4 管脚上void delay(unsigned int i){unsigned char j;for(i; i > 0; i--)for(j = 255; j > 0; j--);}main(){// 点亮第一个LED灯HC138C = 0; HC138B = 0; HC138A = 0; delay(1500); //延时// 点亮第二个LED灯HC138C = 0; HC138B = 0; HC138A = 1; delay(1500); //延时// 点亮第三个LED灯HC138C = 0; HC138B = 1; HC138A = 0; delay(1500);// 点亮第四个LED灯HC138C = 0; HC138B = 1; HC138A = 1; delay(2000);// 点亮第五个LED灯HC138C = 1; HC138B = 0; HC138A = 0;delay(1500);// 点亮第六个LED灯HC138C = 1; HC138B = 0; HC138A = 1; delay(1500);HC138C = 1; HC138B = 1; HC138A = 0; delay(1500);HC138C = 1; HC138B = 1; HC138A = 1; delay(1500);}。

实验二74HC138译码器实验(学生)

实验⼆74HC138译码器实验(学⽣)实验⼆ 74HC138译码器实验⼀、实验⽬的与要求1、掌握74HC138译码器的⼯作原理,熟悉74HC138译码器的具体运⽤连接⽅法,了解74HC138是如何译码的。

2、认真预习本节实验内容,尝试⾃⾏编写程序,填写实验报告⼆、实验设备STAR系列实验仪⼀套、PC机⼀台(1)实验要求要求从8255的C⼝低4位输出数据,控制74LS138的ABC端⼝,74LS138控制LED信号灯,使信号灯从第1个开始点亮,间隔⼀定时间,依次点亮第⼆个,直到第8个,每次只点亮⼀个。

如果要反⽅向点亮,程序应该如何调整。

如果要求正⽅向逐个点亮,最后8个灯全亮。

程序⼜该如果调整。

(2)连线说明C3区:A、B、C ——B4区:PC0、PC1、PC2C3区:G1、G2A、G2B ——C1区:VCC、GND、GNDC3区:JP35 ——G6区:JP65(LED指⽰灯)B4区:CS、A0、A1 ——A3区:CS1、A0、A1(3)程序部分8255地址分配:PA:0F000PB:0F001PC:0F002控制⼝:0F003程序开始部分,汇编部分⾃⼰补全:1.正⽅向点亮的程序:.MODEL TINYCon_8255 EQU 0F003H ;8255控制⼝PC_8255 EQU 0F002H ;8255 PC⼝.STACK 100.CODESTART: MOV DX,Con_8255MOV AL,80HOUT DX,AL ;8255初始化,PC⼝作输出⽤MOV DX,PC_8255MOV AL,0START1: OUT DX,AL ;把0输出到8255的PC⼝CALL Delay ;延时INC AL ;AL加1,改变亮灯的状态JMP START1Delay:PROC NEAR ;延时Delay1: XOR CX,CXLOOP $RETDelay ENDPEND START说明:本实验只⽤到PC0、PC1、PC2三个引脚,分别接到74LS138的A、B、C引脚。

集成电路课程设计--含2个 2-4线译码器的74HC139芯片

集成电路课程设计----含2个2-4线译码器的74HC139芯片一.目的与任务本课程设计是《集成电路分析与设计》的实践课程,其主要目的是为了在了解了集成电路的基本结构的基础上进一步的学习集成电路的设计,本次设计通过对TANNER TOOLS PRO工具的使用让我们能够从简单入手到能设计一个完整的芯片,。

并进行电路仿真对比。

二.课程设计题目、内容及要求2.1 设计题目1.器件名称:一个3-8译码器的74HC138芯片;2.要求的电路性能指标:(1)可驱动10个LSTTL电路(相当于15pF电容负载);(2)输出高电平时,︱IoH︱≤20uA,Voh,min=4.4V;(3)输出低电平时,︱IoL︱≤4mA,Vol,max=0.4V;(4)输出级充放电时间tr = tf,tpd<25ns;(5)工作电源5V,常温工作,工作频率fwork =30MHz,总功耗Pmax=150mW。

2.2 设计内容(1)功能分析及逻辑设计(2)电路设计(3)估算功耗与延时(4)电路模拟与仿真(5)版图设计(全手工、层次化设计)(6)版图检查:DRC与LVS(7)后仿真(选做)(8)版图数据提交2.3 设计要求(1)独立完成设计74HC138 芯片的全过程;(2)设计时使用的工艺及设计规则:MOSIS:mamin08;(3)根据所用的工艺,选取合理的模型库;(4)选用以lambda(λ)为单位的设计规则;(5)全手工、层次化设计版图;(6)达到指导书提出的设计指标要求。

三、74HC139电路简介3.1 通用74HC139芯片的引脚图74HC139芯片包含两个2-4译码器,它的通用引脚图入图1其中,(1A0、1A1)和(2A0、2A1)分别为两个译码器的地址输入端,而1E (以下取名为Csa )和2E (以下取名为Csb )分别为两个译码器的使能端(低电平有效),1Y0~1Y7和2Y0~2Y7为译码器的数据输出端。

3.2通用74HC139的真值表 通用74HC139的真值表如表一3.3通用74HC139的逻辑表达式根据表一,我们可以很容易得到一下的逻辑表达式 Y0=E+A1+A0=01A A E ∙∙ Y1=E+A1+0A =01A A E ∙∙ Y2=E+1A +A0=01A A E ∙∙ Y3=E+1A +0A =01A A E ∙∙3.4通用74HC139的逻辑图,如图2所示图二所示为通用74HC139芯片的其中一个译码器的逻辑图。

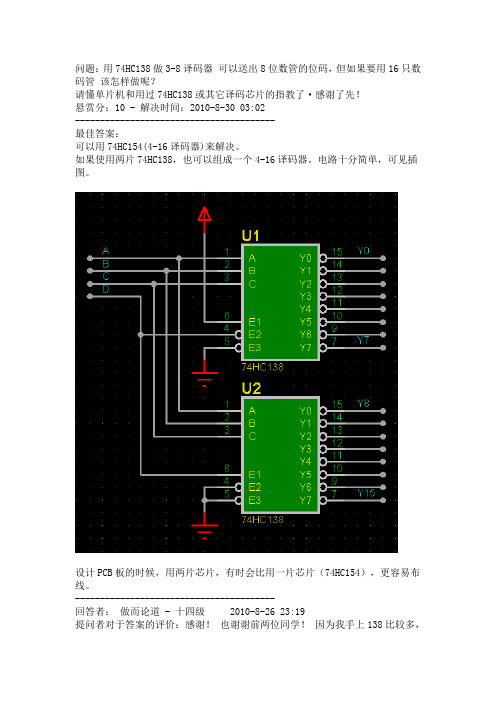

74HC138级联

问题:用74HC138做3-8译码器可以送出8位数管的位码,但如果要用16只数码管该怎样做呢?请懂单片机和用过74HC138或其它译码芯片的指教了·感谢了先!悬赏分:10 - 解决时间:2010-8-30 03:02----------------------------------------最佳答案:可以用74HC154(4-16译码器)来解决。

如果使用两片74HC138,也可以组成一个4-16译码器。

电路十分简单,可见插图。

设计PCB板的时候,用两片芯片,有时会比用一片芯片(74HC154),更容易布线。

----------------------------------------回答者:做而论道 - 十四级 2010-8-26 23:19提问者对于答案的评价:感谢!也谢谢前两位同学!因为我手上138比较多,所以考虑用这个组合下。

原题网址:/question/178416038.html----------------------------------------后记:使用一块74HC154,就是把16条译码输出引线都集中在一块芯片,然后还需要把它们再分散到16个目标地点。

这在PCB上布线的时候,十分的不便。

用两个74HC138芯片,就方便多了。

呵呵,必须是有实践经验的人,才能理解这个观点。

另外,做而论道还用三块74HC138芯片设计过5-24的译码电路,电路也十分简单,可见下图。

当时是用在24×192点阵的LED显示屏幕上,分成24行显示8个24×24点阵的汉字。

/* 点阵显示屏为16*64条屏,可级联,上下屏由两个74HC138分别控制1/8扫 *//* 屏接口为20针,1:A0,3:A1,5:A2,7:下半屏,9:RCK,11:SCK,13:SI,15:下一屏接口17:下半屏,19,2-20:地*//* 李于浙江2011.5.3 */#include<reg52.h>#define uchar unsigned char#define uint unsigned int/*************************************************/sbit hc595_SI = P0^0;//串行移位数据输入sbit hc595_SCK = P0^1;//595移位时钟,上升沿触发sbit hc595_RCK = P0^2;//595数据锁存信号,上升沿触发,输出锁存器控制sbit LS138_A0 = P1^0;//行选择1-8 行sbit LS138_A1 = P1^1;//行选择sbit LS138_A2 = P1^2;//行选择sbit LS138_G_S = P1^3;//上半屏显示允许控制信号端口,138行扫描使能端,高电平有效sbit LS138_G_X = P1^4;//下半屏显示允许控制信号端口,138行扫描使能端,高电平有效// 11110000 上屏第1行,且亮,下屏全不亮0xf0// 11111000void delay(uint dt){uchar bt;for(;dt;dt--)for(bt=0;bt<200;bt++);}/**********************74HC595驱动************************/void hc595_write_data(uchar data_ds){uchar n_bit;//n位for(n_bit=0;n_bit<8;n_bit++) //1个字节{hc595_SCK=0;if(data_ds&0x01) //低位在前{hc595_SI=1;}else{hc595_SI=0;}data_ds = data_ds>>1;//数据在上升沿移位hc595_SCK=1;delay(1);}}/*************74HC595数据锁存输出*********/void hc595_display(){hc595_RCK=0;delay(1);hc595_RCK=1;}uchar sw[16]={0xf0,0xf1,0xf2,0xf3,0xf4,0xf5,0xf6,0xf7,0x88,0x89,0x8a,0x8b,0x8c,0x8d,0x8e,0x8f,};//138的驱动代码,根据138的真值表计算而来。

利用74HC138制作4线—16线译码器

《组合逻辑电路的分析与设计》————利用74HC138制作4线—16线译码器院系:电子与信息工程学院利用74HC138制作4线—16线译码器一、实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

二、实验仪器1、数字电路实验箱2、74HC138 3-8线译码器 2片三、实验原理1、CMOS器件74HC138的逻辑功能及应用74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

其引脚排列如下图(一)所示图(一)74HC138功能表如下表(一)所示:表(一)3、用两个3线-8线译码器构成4线-16线译码器。

利用使能端能方便地将两个 3/8译码器组合成一个4/16译码器,如下图图(二)所示。

图(二)四、实验结果记录:1、74HC138逻辑功能测试结果记录如下表表(二)所示:输入输出E 1E2+E3A2A1AY0(非)Y1(非)Y2(非)Y3(非)Y4(非)Y5(非)Y6(非)Y7(非)1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 12 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 0 X X X X 1 1 1 1 1 1 1 1 X 1 X X X 1 1 1 1 1 1 1 1表(二)2、测试部分图片如下图图(三)、图(四)、图(五)、图(六)图(七)所示:图(三)图(四)图(五)图(六)图(七)五、实验心得:通过这次试验,使我学到了不少实用的知识,更重要的是,做实验的过程,思考问题的方法,这与做其他的实验是通用的,真正使我受益匪浅。

74HC138中文资料_数据手册_参数

74HCT138 3至8行解码器/解复用器;反相 [1] 对于DIP16封装:P TOT 线性降低12 MW / K以上70 C. [2] 对于SO16封装:P TOT 线 性降低至70 MW / K以上 C. [3] 对于SSOP16和TSSOP16封装:P TOT 线性降低 至 5.5 MW / K以上 C. [4] 对于DHVQFN16封装:P TOT 线性降低 至 4.5 MW / K,高于60 C. 8.推荐工作条件 9.静态特性 P TOT总功耗 DIP16封装 [1] - 750 SO16封装 [2] - 500毫瓦 SSOP16包 [3] - 500毫瓦 TSSOP16包 [3] - 500毫瓦 DHVQFN16包 [4] - 500毫瓦表4 限制值 ...继续根据绝对大额定值系统(IEC 60134).电压以GND为参考(地= 0 V).符号参数条件敏马克斯单元表5推荐工作条件电压以GND为参考(地= 0 V)符号参数 条件 74HC138 74HCT138单元敏典型马克斯敏典型马克斯 V CC电源电压 2.0 5 6 4.5 5 5.5 V V 我输入电压 0 - V CC 0- V CC V V O 输出电压 0 - V CC 0- V CC V T AMB环境温度 -40 +25 +125 -40 +25 +125 C ΔT/ΔV输入转换升降率 V CC = 2.0 V - - 625 - - - NS / V V CC = 4.5V - 1.67 139 - 1.67 139 NS / V V CC = 6.0 V - - 83 - - - NS / V表6静态特性在推荐的操作条件下;电压参考GND(地= 0 V).符号参数条件 T AMB = 25 C T AMB = -40°C至 + 85 C T AMB = -40°C至 +125 C单元敏典型马克斯敏马克斯敏马克斯 74HC138 V IH高水平输入电压 产品数据表 2012年6月4日至27日 17之19恩智浦半导体 74HC138; 74HCT138 3至8行解码器/解复用器;反相 15.法律信息 15.1数据表 状态 [1]请在启动或完成设计之前查阅近发布的文档. [2]术语“短数据表”在“定义”一节中进行了解释. [3]本文档中描述的设 备的产品状态可能在本文档发布后发生变化,并且在多个设备的情况下可能会有所不同.新的产品状态有关信息可以在网址 上找到. 15.2定义草案 - 文件仅为草案版本.内容还在内部审查和正式批准,可能会导致修改或添加.恩 智浦半导体不给任何陈述或保证的准确性或完整性包含在这里的信息,并且对后果不承担任何责任使用这些信息.简短的数据 表 - 简短的数据表是来自完整数据表的摘录具有相同的产品型号和标题.一个简短的数据表是打算仅供快速参考,不应依赖于 详细说明完整的信息.有关详细和完整的信息,请参阅相关的完整数据可通过当地恩智浦半导体销售部门索取办公室.如果与短 数据表有任何不一致或冲突,应以完整的数据表为准.产品规格 - 产品中提供的信息和数据数据表应按照约定的方式定义产品 的规格恩智浦半导体及其客户,除非恩智浦半导体和客户已经以书面形式明确表示同意.然而,在任何情况下,恩智浦半导体 产品的协议应是有效的被视为提供了超出上述范围之外的功能和品质产品数据表. 15.3免责声明有限保修和责任 - 本文件中的信 息被认为是准确可靠.但是,恩智浦半导体并没有给予任何陈述或保证,明示或暗示,准确性或这些信息的完整性,对此不承 担任何责任使用这些信息的后果.恩智浦半导体不采纳如果信息提供,则对本文件中的内容负责恩智浦半导体以外的来源.恩智 浦半导体不对任何间接的,附带的,惩罚性的,特殊的或相应的损害赔偿(包括但不限于 - 损失利润,

74HC138

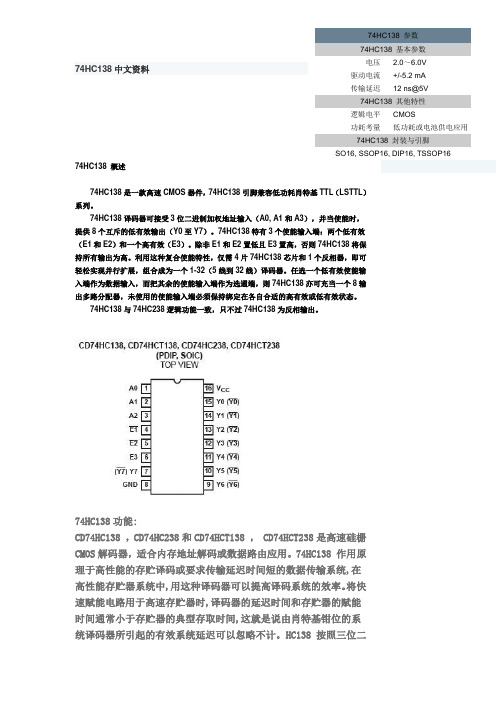

74HC138中文资料74HC138 概述74HC138是一款高速CMOS 器件,74HC138引脚兼容低功耗肖特基TTL (LSTTL )系列。

74HC138译码器可接受3位二进制加权地址输入(A0, A1和A3),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC138与74HC238逻辑功能一致,只不过74HC138为反相输出。

74HC138功能:CD74HC138 ,CD74HC238和CD74HCT138 , CD74HCT238是高速硅栅CMOS 解码器,适合内存地址解码或数据路由应用。

74HC138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在 高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二74HC138 参数 74HC138 基本参数电压 2.0~6.0V 驱动电流 +/-5.2 mA 传输延迟 12 ns@5V 74HC138 其他特性逻辑电平 CMOS功耗考量低功耗或电池供电应用74HC138 封装与引脚 SO16, SSOP16, DIP16, TSSOP16进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

74HC138系列单片机控制LED数码管的原理图解析

74HC138系列单片机控制LED数码管的原理图解析LED小灯是一种简单的LED,只能通过亮和灭来表达简单的信息。

而这节课我们要来学习一种能表达更复杂信息的器件——LED数码管。

先给大家提供一张原理图看一下,如图5-3所示。

这是比较常见的数码管的原理图,我们板子上一共有6个数码管。

前边有了 LED 小灯的学习,数码管学习就会轻松的多了。

从图5-3可以看出来,数码管共有 a、b、c、d、e、f、g、dp 这么8个段,而实际上,这8个段每一段都是一个LED 小灯,所以一个数码管就是由8个LED 小灯组成的。

我们看一下数码管内部结构的示意图,如图5-4。

数码管分为共阳和共阴两种,共阴数码管就是8只 LED 小灯的阴极是连接在一起的,阴极是公共端,由阳极来控制单个小灯的亮灭。

同理,共阳数码管就是阳极接在一起,大家可以认真研究下图5-4。

细心的同学会发现,图5-3的数码管上边有2个com,这就是我们数码管的公共端。

为什么有2个呢,一方面是2个可以起到对称的效果,刚好是10个引脚,另外一个方面,公共端通过的电流较大,我们初中就学过,并联电路电流之和等于总电流,用2个 com 可以把公共电流平均到2个引脚上去,降低单条线路承受的电流。

从我们开发板的电路图上能看出来,我们所用的数码管都是共阳数码管,一共有6个,如图5-5所示。

6个数码管的 com 都是接到了正极上,当然了,和 LED 小灯电路一样,也是由74HC138 控制三极管的导通来控制整个数码管的使能。

先来看最右边的DS1 这个数码管,原理图上可以看出,控制DS1 的三极管是 Q17,控制 Q17 的引脚是 LEDS0,对应到 74HC138 上边就是 U3 的 Y0 输出,如图5-6所示。

我们现在的目的是让 LEDS0 这个引脚输出低电平,相信大家现在可以根据前边学过的知识独立把ADDR0、ADDR1、ADDR2、ADDR3、ENLED 这4个所需输入的值写出来了,现在大家不要偷懒,根据74HC138 的手册去写一下,不需要你记住这些结论,但是遇到就写一次,锻炼过几次后,遇到同类芯片自己就知道如何去解决问题了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录【摘要】.....................................................................................................................................................- 2 -1. 设计目的与任务....................................................................................................................................- 3 -2. 设计要求及内容....................................................................................................................................- 3 -3. 设计方法及分析....................................................................................................................................- 4 -3.1 74HC138芯片简介 ......................................................................................................................- 4 -3.2 工艺和规则及模型文件的选择 .................................................................................................- 5 -3.3 电路设计......................................................................................................................................- 6 -3.3.1 输出级电路设计.............................................................................................................- 6 -3.3.2.内部基本反相器中的各MOS 尺寸的计算................................................................- 9 -3.3.3.四输入与非门MOS尺寸的计算...............................................................................- 10 -3.3.4.三输入与非门MOS尺寸的计算............................................................................... - 11 -3.3.5.输入级设计................................................................................................................. - 11 -3.3.6.缓冲级设计.................................................................................................................- 12 -3.3.7.输入保护电路设计...................................................................................................- 14 -3.4. 功耗与延迟估算.......................................................................................................................- 15 -3.4.1. 模型简化........................................................................................................................- 16 -3.4.2. 功耗估算........................................................................................................................- 16 -3.4.3. 延迟估算........................................................................................................................- 17 -3.5. 电路模拟...................................................................................................................................- 19 -3.5.1 直流分析.........................................................................................................................- 20 -3.5.2 瞬态分析.......................................................................................................................- 22 -3.5.3 功耗分析.......................................................................................................................- 24 -3.6. 版图设计...................................................................................................................................- 26 -3.6.1 输入级的设计...............................................................................................................- 26 -3.6.2 内部反相器的设计.......................................................................................................- 27 -3.6.3 输入和输出缓冲门的设计 ...........................................................................................- 27 -3.6.4 三输入与非门的设计...................................................................................................- 28 -3.6.5 四输入与非门的设计...................................................................................................- 29 -3.6.6 输出级的设计...............................................................................................................- 30 -3.6.7 调用含有保护电路的pad元件 ...................................................................................- 31 -3.6.8 总版图...........................................................................................................................- 31 -3.7. 版图检查...................................................................................................................................- 32 -3.7.1 版图设计规则检查(DRC).......................................................................................- 32 -3.7.2 电路网表匹配(LVS)检查........................................................................................- 33 -3.7.3 版图数据的提交...........................................................................................................- 34 -4. 经验与体会..........................................................................................................................................- 35 -5. 参考文献..............................................................................................................................................- 36 - 附录A:74HC138电路总原理图 ...........................................................................................................- 37 - 附录B:74HC138 芯片版图(未加焊盘) ................................................................................................- 38 -【摘要】现代社会正在飞速的发展,集成电路已经成为现代科技发展的支柱产业,现代技术产业的心脏,可以说,没有集成电路,就没有现代社会。