什么是晶圆级晶片尺寸封装

晶圆级芯片封装技术

重布线技术的作用

• 再分布技术就是在器件表面重新布置I/O 焊盘。 传统芯片的焊盘设计通常为四周分布,以便进行 引线键合,焊盘分布很难满足凸点制备的工艺要 求,因此为了满足倒装工艺,需要进行焊盘再分 布。芯片焊盘设计为阵列分布,如果分布不合理 或者使用的凸点制备工艺不同仍然不能满足倒装 焊工艺时,可以通过焊盘再分布技术实现倒装。

• 在所有的薄膜应用中最好采用聚合物,是由于 其非常低的介电常数和最小的损耗角正切值。

• 与干蚀刻材料相比,采用光敏聚合物, 要求更少的工艺处理步骤(可进行光刻) ,因此节省成本。

焊料凸点制作工艺

• 焊点制作可采用蒸发法、化学镀法、电镀 法、置球法和和焊膏模板印制法等。目前 仍以电镀法用得较多,该法2019年约占所有 焊料凸点制作法的70%(含金焊点制作), 其次是蒸发法(高铅),约占22.5%, 再者为 焊膏模板印制法, 约占5.5%。但因焊膏模板 印制法制作焊料凸点比较简便, 自动化程度 较高, 成本也较低, 故该法将会被较多地采 用。

• WL-CSP是在圆片前道工序完成后, 直接对圆片

利用半导体工艺进行后道工序, 再切割分离成单个 器件。因此, 采用WL-CSP能使产品直接从制造商 转入用户手中作全面测试。该项技术不但适应于 现有的标准表面贴装技术(SMT)设备, 而且也解决 了优质芯片问题。

• 圆片级器件和SMT进行大批量封装WL-CSP的封 装效率可达90%以上.

晶圆级芯片封装技术(WL-CSP)

游凯

• 一、晶圆级芯片封装的定义 • 二、晶圆级芯片封装工艺 • 三、晶圆级芯片封装的可靠性

晶圆级芯片封装的定义

• 根据定义,晶圆级芯片封装就是芯片 尺寸的封装,其尺寸与芯片原尺寸相 同。基本概念是,在制造后,通常在 测试之前,马上取出晶片,再增加一 些步骤(金属和电介质层)产生一种结构, 就可将产品组装到电路板上。

晶圆尺寸的定义与应用

晶圆尺寸的定义与应用晶圆尺寸的定义与应用概念介绍:晶圆尺寸是在半导体制造过程中非常重要的一个参数。

它指的是用于制造芯片的硅片或其他衬底的直径。

晶圆尺寸的定义与应用对于理解半导体制造过程、芯片封装以及整个电子行业的发展都至关重要。

本文将深入探讨晶圆尺寸的定义、不同尺寸的应用领域以及晶圆尺寸对半导体行业的影响。

1. 晶圆尺寸的定义晶圆尺寸指的是硅片或其他衬底的直径,通常以英寸(inch)为单位。

常见的晶圆尺寸有4英寸、6英寸、8英寸和12英寸,其中以12英寸最为常见。

不同尺寸的晶圆在半导体制造中具有不同的应用和优势。

2. 不同尺寸的晶圆应用领域- 4英寸晶圆:4英寸晶圆是较早期使用的尺寸。

它主要应用于一些较老的半导体工艺,例如某些RF(射频)应用、一些具有特定尺寸限制的芯片和一些低成本应用领域。

- 6英寸晶圆:6英寸晶圆是较为常见的尺寸,在过去的一些年份被广泛应用。

它适合于制造一些较小的集成电路和较低功耗的应用。

- 8英寸晶圆:8英寸晶圆是过去十多年来主流的尺寸。

它在很多领域都有广泛的应用,包括计算机芯片、通信芯片、嵌入式系统等。

8英寸晶圆的制造成本相对较低,适合中小规模生产。

- 12英寸晶圆:12英寸晶圆(也称为300mm晶圆)是目前主流的尺寸。

它被广泛应用于高性能计算、云计算、人工智能、物联网等领域。

随着芯片功能的增加和制程工艺的进步,12英寸晶圆能够提供更高的芯片产量和更好的性能。

3. 晶圆尺寸对半导体行业的影响晶圆尺寸对半导体行业有着深远的影响。

以下是其中几个方面的影响:- 成本效益:较大尺寸的晶圆在单个晶圆上可以容纳更多的芯片,从而提高了生产效率和降低了制造成本。

- 投资规模:随着晶圆尺寸的增大,制造厂商需要更大规模的设备和投资,这对于新厂商来说是一个挑战,同时也加大了行业中的竞争。

- 技术进步:随着晶圆尺寸的增加,制程工艺也需要不断提高和创新,以适应更高的要求和更复杂的芯片设计。

- 产能和供应:较大尺寸的晶圆可以提供更高的产能,有助于满足市场对芯片的需求。

晶圆级芯片规模封装——微型表面贴装元器件

晶圆级芯片规模封装——微型表面贴装元器件1 引言芯片规模封装(CSP)已改变了集成电路的设计和制造技术,较早的CSP类型与传统封装形式相同,也就是说,将晶圆片上芯片分离后,应用后端工艺进行封装,此传统工艺方法虽然使用后端设施运作良好,但是不能转变为最节省成本的封装方案。

近来已出现较新的趋势,就是驱使封装向芯片尺寸方向的微缩,封装在切片之前直接在晶圆片上进行。

微型表面贴装元器件(microSMD)是晶圆级芯片规模/尺寸封装(CSP),通常把CSP确定为封装的外部尺寸小于或等于内部芯片尺寸的120%以内,微型SMD主要优点在于,该封装是采用晶圆形式装配的,适合于标准表面贴装的加工工艺,最适合于下一代更快、更小,更轻和更节省成本的产品,主要优点为:(1)采用倒装片凸点形成技术--比引线键合的互连技术更快;(2)无需下填充物材料--客户组装循环时间与成本更低;(3)每个I/O最小的脚印--显著的印刷电路板(PCB)成本节省;(4)能够实现的标准表面贴装技术--无需新设备,用户成本更低;(5)节省成本的晶圆级制造技术--卖方循环时间与成本更低;(6)0.5mm节距下互连设计--适合于别的CSP标准,虽然较严格的节距是可行的,但是这样的设计会转变为更昂贵的细节距板技术,并形成对专用细节距组装和检查设备的需求。

2 封装结构微型SMD 8 I/O封装如图1所示,此结构形式提供了商业方面用于8 I/O封装的最小脚印,形成了优于等体积8-线MSOP(微小型封装,目前最小的传统表面贴装8I/O封装)6倍的不动产成本节省费用。

MSOP与微型SMD封装的比较(见图2)与其他封装的I/O密度比较(见图3)。

在质量方面,微型SMD为4mg,大约是8I/O MSOP(27mg)质量的1/7,8 I/O 微型SMD为1.45mm×1.45mm,厚度近似于0.9mm,硅片背部采用防护密封剂保护层,此涂层起着双重作用,即:在划片阶段防止硅碎片及较清晰的激光打印特征。

什么是晶圆级芯片封装WLCSP

什么是晶圆级芯片封装WLCSP

随着移动电子产品趋向轻巧、多功能、低功耗发展,为了在更小的封装面积下容纳更多的引脚数,因而发展出晶圆级芯片封装WLCSP。

它具备更多的功能集成、在体积、成本和性能方面更具优势,可以应用在移动电话、蓝牙

产品、医疗设备、射频收发器、电源管理单元、音频放大器和GPS模块使用。

什幺是晶圆级芯片封装WLCSP呢?

大家可能比较熟悉BGA,CSP就是小型的BGA,外形和球间距比BGA 小,球间距小于0.8毫米的BGA称为CSP,或者封装面积和里面芯片的面积之比小于1.2。

至于WLCSP,就是晶圆级CSP,即是大型的倒装晶片,中间没有载体,

焊球直接植于硅基材上,一般焊球间距为0.4至0.8毫米间。

由于晶圆级芯片封装的密间距,其敏感度远远超过BGA。

那幺,在组装晶圆级芯片封装这种具有焊球直径小、焊球间距小、外形尺。

什么是晶圆级芯片封装WLCSP

什么是晶圆级芯片封装WLCSP

随着移动电子产品趋向轻巧、多功能、低功耗发展,为了在更小的封装面积下容纳更多的引脚数,因而发展出晶圆级芯片封装WLCSP。

它具备更多的功能集成、在体积、成本和性能方面更具优势,可以应用在移动电话、蓝牙产品、医疗设备、射频收发器、电源管理单元、音频放大器和GPS模块使用。

什么是晶圆级芯片封装WLCSP呢?

大家可能比较熟悉BGA,CSP就是小型的BGA,外形和球间距比BGA小,球间距小于0.8毫米的BGA称为CSP,或者封装面积和里面芯片的面积之比小于1.2。

至于WLCSP,就是晶圆级CSP,即是大型的倒装晶片,中间没有载体,焊球直接植于硅基材上,一般焊球间距为0.4至0.8毫米间。

由于晶圆级芯片封装的密间距,其敏感度远远超过BGA。

那么,在组装晶圆级芯片封装这种具有焊球直径小、焊球间距小、外形尺寸小的元器件特征时,厂家要注意什么呢?环球仪器提出了什么解决方案呢?

晶圆级芯片封装的装配流程

目前有两种工艺,一种是锡膏装配,但为了避免“桥连”或“少锡”缺陷,环球仪器建议采用助焊剂浸蘸的方法进行组装。

工艺流程:

拾取晶圆级芯片封装

浸蘸助焊剂

贴装晶圆级芯片封装

回流焊接

底部填充(如有需要)

在这里先集中讨论浸蘸助焊剂流程,环球仪器建议采用助焊剂薄膜浸蘸方式,即在元器件贴装前浸蘸一定厚度的助焊剂薄膜,使每个焊球上附着一定量的助焊剂。

采用助焊剂薄膜浸蘸的两大优点:。

晶圆级封装(Fan

晶圆级封装(Fan便携式及手持电子设备的小型化,激发了传统BGA和CSP封装往更小尺寸的发展趋势。

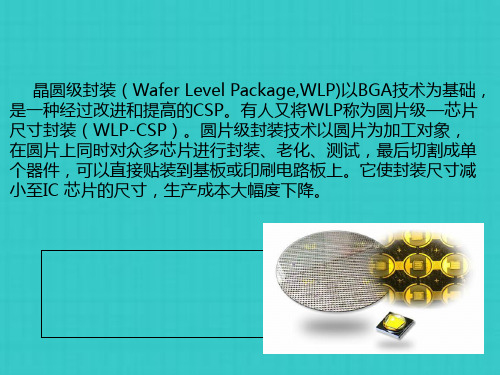

芯片级封装(Chip Scale Package,CSP),是芯片面积与封装面积之比接近1:1的一种封装形式,而晶圆级封装(Wafer Level Package,WLP),可以认为是一种经过改进和提高的CSP,广泛应用于智能手机、可穿戴设备等领域的集成电路,如功率放大器、电源模块、射频滤波器、存储器及逻辑电路等。

晶圆级封装,以晶圆片为加工对象,在晶圆片上同时对多个芯片进行全部的封装及测试,最后再切割成单个器件,使用时直接贴装到基板或印刷电路板上。

由于晶圆级封装的封装尺寸与基板或印制电路板上安装面积相同,所以WLP通常被认为是集成电路封装的最终形式,10mm2的芯片,如采用典型的QFP扁平封装占据约900mm2的安装面积,载带自动焊封装(Tape Automated Bonding,TAB是将芯片组装在金属化柔性高分子聚合物载带上的封装技术)、板上芯片封装(Chip On Board,COB是将晶圆直接安装到印制电路板,然后用键合丝实现互联,再用有机材料涂覆到晶圆上完成后期封装)分别占据550mm2、300mm2,而WLP只需约100mm2的安装面积,这就表明WLP可以使整机模块尺寸更小、重量更轻、集成度更高,同时成本也更低。

WLP主要用于具有以下功能的集成电路:o低引脚数(≤200)o焊球间距范围为0.50mm、0.40mm、0.35mm和0.30mmo小尺寸芯片(≤5mm*5mm)o低成本、低端o大批量使用晶圆级封装后的体积与集成电路的裸芯片基本一致,并且整合了芯片的前端和后端工艺,封装成本也随着晶圆尺寸(圆片级封装的成本与每个圆片上的芯片数量密切相关,晶圆尺寸的增加,每个晶圆就可以生产更多的IC,芯片数越多,晶圆级封装的成本也就越低)的增加或IC封装尺寸的降低而减少晶圆级封装以晶圆形式的批量生产工艺进行制造,加工效率高,与其它封装类型相比,尺寸也较小,很好的满足便携式电子设备尺寸不断减小的需求;在传输性能上,有效增加了数据传输的频宽并减少了信号损耗,提升了数据传输的速度和稳定性;在散热性能上,由于WLP没有像传统封装的塑封料或陶瓷包封,所以散热能力效果更优;另外,晶圆级封装的芯片设计和封装设计可以统一考虑、同时进行,这将大大提高设计效率,从芯片制造、封装再到产品发往用户的整个过程中,周期也会大幅缩减晶圆级封装(Fan-in WLP)工艺技术从封装技术特点上看,晶圆级封装主要分为Fan-in和Fan-out两种形式。

芯片常用封装

芯片常用封装芯片常用封装是指对芯片进行包装和封装的一种技术,它可以保护芯片,提高芯片的可靠性和稳定性,并方便芯片的使用和安装。

芯片常用封装形式主要有晶圆级封装和后封装两种。

1. 晶圆级封装晶圆级封装是指将芯片直接封装在晶圆上。

这种封装方式具有高度集成、高密度、高性价比等优点。

晶圆级封装主要有以下几种形式。

(1) 裸芯封装:将芯片直接封装在晶圆上,没有任何其他材料进行封装。

这种封装方式适用于一些对成本要求较高、不需要对芯片进行保护的应用场景。

(2) 热压封装:将芯片通过热压工艺与晶圆封装。

这种封装方式可以提高芯片的可靠性和热导性能。

(3) 胶粘封装:将芯片封装在晶圆上,并使用胶粘剂进行固定。

这种封装方式可以提高芯片的抗震性和抗振动性能。

(4) 焊接封装:将芯片封装在晶圆上,并通过焊接工艺进行连接。

这种封装方式可以提高芯片的可靠性和连接性能。

2. 后封装后封装是指将已经完成芯片制造的芯片进行封装。

这种封装方式可以根据不同的应用需求选择不同的封装形式。

(1) DIP封装:DIP封装是一种早期的常用封装形式,它可以直接插入到电路板上。

DIP封装具有安装方便、维修性好等优点,但是不适用于集成度高的芯片。

(2) BGA封装:BGA封装是一种较新的封装技术,它将芯片通过球形焊盘进行连接。

BGA封装具有高集成度、高密度、高可靠性等优点,适用于高性能芯片的封装。

(3) QFP封装:QFP封装是一种表面贴装封装技术,它将芯片通过引脚焊接到电路板上。

QFP封装具有体积小、重量轻、适用于高速信号传输等优点,适用于一些对体积要求较小的应用场景。

(4) CSP封装:CSP封装是一种超小型封装技术,它将芯片直接封装在引脚上。

CSP封装具有体积小、能耗低、适用于高光性能等优点,适用于一些对体积和能耗要求较高的应用场景。

综上所述,芯片常用封装形式有晶圆级封装和后封装两种,各有不同的优点和适用场景。

在选择封装形式时,需要根据芯片的性能要求、应用场景和成本等因素进行综合考虑选择。

芯片最小尺寸封装

芯片的最小尺寸封装可以因芯片类型、技术水平和制造工艺而有所不同。

下面列举几种常见的芯片封装类型及其最小尺寸:

1.裸片(Die):裸片是指将芯片从晶圆上切割下来,没有任何封装。

裸片的尺寸通常

以芯片的边长或直径来表示,可以非常小,达到数百微米甚至更小的尺寸。

2.芯片级封装(Chip Scale Package,CSP):CSP是一种紧凑型封装形式,尺寸接近芯

片尺寸,通常只比芯片大出几个焊盘的宽度。

CSP的最小尺寸可以小到几百微米,甚至更小。

3.超薄封装:超薄封装是指封装高度非常薄的封装形式,常用于移动设备等需要紧凑

结构的应用。

超薄封装的最小尺寸可以小于1毫米。

4.面积阵列封装(Wafer-Level Package,WLP):WLP是一种在晶圆级别进行封装的技

术,封装区域与芯片面积相当,常用于集成电路的封装。

WLP的最小尺寸可以小到几百微米。

晶圓級尺寸(WLCSP)IC封測製程介紹

6. Laser Marking Laser making (Wafer form)

蓋印

切割 外觀檢驗 捲帶 目檢

11.Pack

Vacuum sealing dry packing

包裝

5

The Testing Industry Benchmark Benchmark The Testing Industry

封裝方式 優 點 缺 點

傳統封裝(QFP、BGA) 1. 技術成熟 2. 製程穩定

1. 無法達到未來細間距要求 2. 製程較複雜 3. 完成的IC成本高 1. I/O數少(<100)

晶圓級晶片尺寸封裝

1. 尺寸小 2. 成本低 3. 簡化製程 4. 可達Fine Pitch要求

3

圓級晶片尺寸封測製程介紹

圓級晶片尺寸封測製程介紹

Prepared by Andy

1

圓級晶片尺寸封測製程介紹

1.什麼是晶圓級晶片尺寸封裝? (Wafer Level Chip Scale Packaging)

晶圓級晶片尺寸封裝(Wafer Level Chip Scale Packaging) 是先在整片晶圓上進行封裝和測試,然後經切割並將IC直 接用機台以pick up & flip方式將其放置於Carrier tape中, 並以Cover tape保護好後,提供後段SMT (Surface Mounting technology)直接以機台將該IC自Carrier tape取 料後,置放於PCB上。

Process 1. Ball Mount 2. CP 3. Grinding 4. BSM (option) 5. BSC (option) 7. Dicing 8. AOI 9. T&R 10. V/M Description Solder ball mount Chip probing test Wafer back-grind Wafer backside metallization Wafer backside coating Wafer mount and saw Sort inspection Tape and reel (pick and place) Inspection after T&R Remark 植球 CP測試 研磨 硬化處理 覆層

什么是晶圆级晶片尺寸封装

什么是晶圆级晶片尺寸封装(Wafer Level Chip Scale Packaging)1. 晶圆级晶片尺寸封装(Wafer Level Chip Scale Packaging)是先在整片晶圆上进行封装和测试,然后经切割并将IC直接用机台以pick up & flip方式将其放置于Carrier tape中,并以Cover tape保护好后,提供后段SMT (Surface Mounting technology)直接以机台将该IC自Carrier tape取料后,置放于PCB上。

WLCSP选用较大的锡铅球来形成接点藉以进行电性导通,其目的是增加元件与基板底材之间的距离,进而降低并承受来自于基板与元件间因热膨胀差异产生的应力,增加元件的可靠性。

利用重分布层技术则可以让锡球的间距作有效率的安排,设计成矩阵式排列(grid array)。

采用晶圆制造的制程及电镀技术取代现有打金线及机械灌胶封模的制程,不需导线架或基板。

晶圆级封装只有晶粒般尺寸,且有较好的电性效能,因系以每批或每片晶片来生产, 故能享有较低之生产成本。

2.特点:WLCSP 少掉基材、铜箔等,使其以晶圆形态进行研磨、切割后完成的IC 厚度和一般QFP 、BGA……等等比较起来为最薄、最小、最轻,较符合未来产品轻、薄之需求;且因其不需再进行封装,即可进行后段SMT 制程,故其成本价格可以较一般传统封装为低。

● 封装技术比较:3.产品应用面:3.1 Power supply (PMIC/PMU, DC/DC converters, MOSFET' s,...)3.2 Optoelectronic device3.3 Connectivity (Bluetooth, WLAN)3.4 Other features (FM, GPS, Camera)4.生产流程简介Wafer backside metallization。

晶圆级芯片封装

晶圆级芯片封装晶圆级芯片封装是指将芯片直接封装在晶圆上,以实现更高的集成度和更小的体积。

在制造过程中,晶圆级芯片封装是非常重要的一步。

本文将从以下几个方面对晶圆级芯片封装进行详细介绍。

一、晶圆级芯片封装的概念和意义1.1 晶圆级芯片封装的定义晶圆级芯片封装是指将裸露的芯片直接封装在晶圆上,以实现更高的集成度和更小的体积。

它是半导体制造过程中非常重要的一步。

1.2 晶圆级芯片封装的意义晶圆级芯片封装可以提高半导体器件的集成度和性能,并且可以减小器件体积,降低生产成本。

此外,在大规模集成电路领域,晶圆级芯片封装也可以提高生产效率。

二、晶圆级芯片封装工艺流程2.1 芯片选切在制造过程中,先要从整个硅块中选择出符合要求的区域,并对其进行切割。

这个过程称为芯片选切。

2.2 芯片清洗选切好的芯片需要进行清洗,以去除表面的杂质和污垢。

这个过程可以使用化学溶液或超声波等方法。

2.3 芯片涂胶在芯片表面涂上一层粘合剂,以便将其固定在晶圆上。

这个过程称为芯片涂胶。

2.4 晶圆准备在晶圆上涂上一层粘合剂,以便将芯片固定在晶圆上。

此外,还需要对晶圆进行清洗和烘干等处理。

2.5 排列芯片将芯片放置在晶圆上,并按照一定的排列方式进行布局。

此外,还需要进行对齐和精细调整等操作。

2.6 封装焊接将芯片与晶圆焊接起来,并用封装材料将其密封起来。

这个过程可以使用焊接机器或激光焊接等方法。

三、晶圆级芯片封装的优势和不足3.1 优势(1)提高集成度:通过直接将芯片封装在晶圆上,可以实现更高的集成度。

(2)减小体积:晶圆级芯片封装可以减小器件的体积,从而提高产品的便携性和可靠性。

(3)降低成本:晶圆级芯片封装可以降低生产成本,提高生产效率。

3.2 不足(1)技术难度高:晶圆级芯片封装需要高精度的设备和技术,制造难度较大。

(2)适用范围有限:由于其制造难度较大,晶圆级芯片封装只适用于一些特定的领域和应用场景。

四、晶圆级芯片封装的应用4.1 大规模集成电路在大规模集成电路领域,晶圆级芯片封装可以提高生产效率,并且可以实现更高的集成度和更小的体积。

晶圆级封装 cis

晶圆级封装 cis

晶圆级封装 CIS

本文介绍了晶圆级封装 CIS(Chip Scale Package)的优点和关键技术,晶圆级封装技术是一种紧凑、先进和低成本的封装技术,有望实现更快的计算性能和更高的集成密度。

晶圆级封装技术是一种新型的微型封装技术,其特点是封装片尺寸仅有封装片厚度的2~3倍。

它具有体积小,性能高,散热性能好,集成度高,灵活性高等优点,可以在现有集成电路封装技术中实现芯片的更紧凑、更先进、更低成本的封装。

晶圆级封装技术可以将单片机和系统芯片等芯片尺寸缩小至比传统封装尺寸更小的尺寸,从而使芯片的功率和效能比传统封装技术更高。

此外,由于封装片厚度较小,因此可以减少封装过程中的介质层厚度,从而提高封装过程中的连接密度,有效地提高芯片的内部数据传输速率以及芯片的功能实现速度。

晶圆级封装技术的关键技术主要包括以下几个方面:1)封装片的制作:需要用厚度可控的材料做成多层的封装片,然后将晶圆和其他附属物安装在其上;2)焊接技术:主要分为气焊技术、浸焊技术和贴片技术;3)检测技术:采用光学检测和扫描电阻检测等检测技术,以确保封装的合格程度;4)表面处理技术:采用热熔塑包覆等方法,以保证封装片表面的牢固性和外观质量。

晶圆级封装技术在高速、低功耗和高集成度的应用中有着重要的意义和作用,可以使技术节点尺寸更小、技术性能更高,从而更好地

满足客户的需求,实现数据传输的更快速度和芯片的更高工作性能。

晶圆级封装技术说课讲解

重布线层(RDL)的目的是对芯片的铝焊区 位置进行重新布局,使新焊区满足对焊料球 最小间距的要求,并使新焊区按照阵列排布。

第二种结构如图(b)所示,焊球 置于在RDL 层上,并通过2 层 聚合物介质层与Si 芯片相连, 此种结构中没有焊点下金属层。 两层聚合物层作为钝化和再布线 层。这种结构不同于第一种结构, 尽管两种结构均有再布线层。如 图b所示,高分子介电薄膜层置 于焊球和硅衬底。这种高分子层 能够作为缓冲层来降低由于温度 变化所引起的PCB 和硅的热失 配产生的热-机械应力。这种 WLP 结构能拓展到间距为0.5 mm 的12×12焊球阵列。

所示为典型的晶圆凸点制作 的工艺流程。 首先在晶圆上完成UBM 层 的制作。然后沉积厚胶并曝 光,为电镀焊料形成模板。 电镀之后,将光刻胶去除并 刻蚀掉暴露出来的UBM 层。 最后一部工艺是再流,形成 焊料球。

电镀技术可以实现很窄的凸点节 距并维持高产率。并且该项技术 应用范围也很广,可以制作不同 尺寸、节距和几何形状的凸点, 电镀技术已经越来越广泛地在晶 圆凸点制作中被采用,成为最具 实用价值的方案。

不同的WLP 结构

第三种WLP 结构如图(c)所示,是在图(b)结构的基础 上,添加了UBM 层。由于添加了这种UBM 层,相应 增加了制造成本。这种UBM 能稍微提高热力学性能。

图(d)所示的第四种WLP 结构,采用了铜柱结构, 首先电镀铜柱,接着用环氧树脂密封。

晶圆级封装技术

晶圆级封装技术

晶圆级封装技术(Wafer-level packaging technology)是一种将整个晶圆进行封装的集成电路封装技术。

它在晶圆制造的最后阶段,直接在晶圆上进行集成电路的封装和测试,而不需要将每个芯片单独切割封装,可以提高生产效率和集成度。

晶圆级封装技术主要包括以下步骤:

1. 晶圆准备:将完成芯片制造的晶圆经过清洗和去除残渣等工艺准备。

2. 测试:对晶圆上的芯片进行测试,检测芯片的电气性能。

3. 封装:选用适当的封装材料和封装工艺,将芯片连接到封装基板上,并进行线路布线、焊接等操作。

4. 封装测试:对封装完成的芯片进行功能测试,检测封装后芯片的电气性能。

晶圆级封装技术的优点包括:

1. 高集成度:由于封装直接在晶圆上进行,可以实现更高的集成度,减少了芯片之间的连线长度,提高了信号传输速度和性能。

2. 高生产效率:晶圆级封装技术可以同时对整个晶圆上的芯片进行封装和测试,相比传统单芯片封装技术,生产效率更高。

3. 尺寸厚度更小:晶圆级封装技术可以减少封装的体积和厚度,适用于要求轻薄短小的应用场景。

4. 低成本:晶圆级封装技术可以减少封装材料的使用量和加工步骤,降低了封装成本。

晶圆级封装技术在半导体行业得到了广泛应用,尤其在高性能计算、物联网、移动通信等领域有着重要的地位。

晶圆级芯片尺寸封装(WLCSP)技术应用现状及市场前景分析

晶圆级芯片尺寸封装(WLCSP)技术应用现状及市场前景分析先进封装是指处于当时最前沿的封装形式和技术。

目前,带有倒装芯片(FC)结构的封装、晶圆级封装(WLP)、2.5D 封装、3D 封装等被认为属于先进封装的范畴。

先进封装发展线路图资料来源:公开资料从2018 年到2024 年,整个半导体封装市场的营收预计将以5.2%的复合年增长率(CAGR)增长,而先进封装市场将以8%的复合年增长率增长,市场规模到2023 年将增长至400亿美元。

另一方面,传统封装市场的复合年增长率则低于3.3%。

在各种不同的先进封装平台中,3D 硅通孔(TSV)和扇出型(Fan-out)封装,将分别以29%和15%的速度增长。

而占据先进封装市场主要市场份额的倒装芯片(Flip-chip)封装,将以约8%的复合年增长率增长。

与此同时,扇入型晶圆级封装(Fan-in WLP)主要受到移动市场驱动,也将以8%的复合年增长率增长。

2018~2024 年全球先进封装技术市场规模预测情况(十亿美元)资料来源:Yole 此外,前段晶圆制造与后段先进封装结合的趋势日渐增强。

全球晶圆制造大厂(如英特尔、台积电和三星等)更是将先进的晶圆制造技术与先进封装形式紧密结合,以强化集成电路产品制造的技术集成优势。

受技术和规模两方面的影响,全球封测产业集中度稳步提升,2017 年前八大封测企业(含晶圆代工厂后段封装业务部分)占据先进封装市场约87%的份额。

晶圆级芯片尺寸封装(WLCSP)作为一类先进封装技术,符合消费电子发展的需求和趋势(产品的轻小短薄化和低价化)。

WLCSP 封装与传统封装相比,其主要优势体现在:①WLC SP优化了封装产业链。

传统封装方式是先将晶圆划片成颗粒芯片,经测试为合格芯片后,将其放到引线框架或封装衬底(基板)上,而后再进行封装测试,产业链涉及晶圆厂、基板厂、封装厂、测试厂。

而晶圆级芯片尺寸封装是先对晶圆进行封装、测试作业,然后再对封装测试后的晶圆进行切割。

晶圆级芯片规模封装

晶圆级芯片规模封装1.引言1.1 概述晶圆级芯片规模封装技术是现代微电子产业快速发展和集成电路封装技术进步的重要推动力之一。

它是将芯片和尺寸较大的电子元器件集成到一个整体封装中,使其更加紧凑和高效。

在晶圆级芯片规模封装中,同时实现了芯片封装和尺寸较大部件的集成,为芯片提供了更好的保护,提高了产品的可靠性和性能。

随着科技的进步和市场需求的不断变化,人们对晶圆级芯片规模封装技术的要求也越来越高。

在晶圆级芯片规模封装领域,主要有几个核心关键技术。

首先是多芯片系统封装技术,即在一个封装中集成多个芯片。

这种技术可以提高系统的整体性能,并减小产品的尺寸和重量。

其次是高速射频封装技术,用于处理高频信号的传输和射频电路的保护。

这种技术在通信和无线网络等领域具有广泛的应用前景。

另外,晶圆级芯片规模封装还需要考虑封装材料的选择和优化,以及封装工艺的开发和改进。

晶圆级芯片规模封装技术不仅在电子产品中得到广泛应用,而且在汽车电子、工业控制和医疗设备等领域也有重要的地位。

封装技术的不断创新和进步,推动了集成电路的发展和应用范围的扩大。

未来,随着芯片尺寸的不断缩小和多功能芯片的需求增加,晶圆级芯片规模封装技术将迎来更多的挑战和机遇。

在本文中,我们将探讨晶圆级芯片规模封装技术的发展现状和趋势,介绍相关的关键技术和应用领域,并展望未来的发展方向。

通过对晶圆级芯片规模封装技术的深入了解和研究,我们可以更好地把握行业的动态,为我国微电子产业的发展做出贡献。

1.2 文章结构文章结构部分的内容可以包括以下内容:文章结构部分主要介绍了本篇文章的整体结构,以帮助读者更好地理解和阅读文章内容。

具体内容如下:本文主要从以下几个方面展开讨论:引言、正文和结论。

1. 引言部分:引言部分将对晶圆级芯片规模封装进行概述,介绍其背景和基本概念,以便读者能够了解文章的研究对象和背景知识。

同时,还会对文章的整体结构进行简要介绍,以便读者大致了解文章的组织和内容安排。

晶圆片级芯片规模封装工艺

晶圆片级芯片规模封装工艺

晶圆片级芯片规模封装(Wafer Level Chip Scale Packaging,简称WLCSP),即晶圆级芯片封装方式,是一种将整片晶圆进行封装和测试,然后再切割成一个个的IC颗粒的封装技术。

这种技术与传统的芯片封装方式(先切割再封测,而封装后至少增加原芯片20%的体积)不同,因为它在切割晶圆成单个芯片之前就已经完成了封装和测试,因此封装后的体积等同于IC裸晶的原尺寸。

晶圆片级芯片规模封装工艺具有以下优点:

1.封装尺寸小:由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得

WLCSP的封装尺寸几乎等于芯片尺寸。

2.高传输速度:与传统金属引线产品相比,WLCSP一般有较短的连接线路,在

高效能要求如高频下,会有较好的表现。

3.高密度连接:WLCSP可运用数组式连接,芯片和电路板之间连接不限制于芯

片四周,提高单位面积的连接密度。

4.生产周期短:WLCSP从芯片制造到封装到成品的整个过程中,中间环节大大

减少,生产效率高,周期缩短很多。

5.工艺成本低:WLCSP是在硅片层面上完成封装测试的,以批量化的生产方式

达到成本最小化的目标。

WLCSP的成本取决于每个硅片上合格芯片的数量,芯片设计尺寸减小和硅片尺寸增大的发展趋势使得单个器件封装的成本相应地减少。

WLCSP可充分利用晶圆制造设备,生产设施费用低。

综上所述,晶圆片级芯片规模封装工艺是一种先进的封装技术,具有许多优点,能够提高芯片的性能和降低生产成本。

晶圆级封装

植球。顺应无铅化环保的要求,目前应用在WLP 的 焊料球都是锡银铜合金。焊料球的直径一般为 250μm。为了保证焊膏和焊料球都准确定位在对应 的UBM 上,就要使用掩模板。焊料球通过掩模板的 开孔被放置于UBM 上,最后将植球后的硅片推入回 流炉中回流,焊料球经回流融化与UBM 形成良好的 浸润结合。

晶圆级封装(Wafer Level Package,WLP)以BGA技术为基础, 是一种经过改进和提高的CSP。有人又将WLP称为圆片级—芯片 尺寸封装(WLP-CSP)。圆片级封装技术以圆片为加工对象, 在圆片上同时对众多芯片进行封装、老化、测试,最后切割成单 个器件,可以直接贴装到基板或印刷电路板上。它使封装尺寸减 小至IC 芯片的尺寸,生产成本大幅度下降。

不同的WLP 结构

•第一种是ball on I/O 结构,如 图(a)所示。这种工艺和典型的倒 装工艺相类似。焊球通过焊点下 金属层与铝盘直接相连 图(a)或 者通过再布线层( redistribution layer, RDL)与Si 芯片直接相连(图(a)2)。 •通常情况下,这种结构限制在焊 球间距为0.5 mm 的6×6 阵列结 构,以满足热循环可靠性的要求 。

常见的RDL 材料是电镀铜(plated Cu)辅以打底的钛、铜溅射层(Sputtered Ti/Cu)。

焊这为料种了球 W保L的证P直焊结I等径膏P构一和D能器般焊拓(为料集件展球2到5成。都0间μ准m距无圆确。为定源片0.位器级在对件封应的)装、UB技模M 上术拟,已就芯要广片使用泛掩模板。 用于闪速存储器、EEPROM、 为了保证焊膏和焊料球都准确定位在对应的UBM 上,就要使用掩模板。

晶圓級晶片尺寸封裝(waferlevelchipscalepackage,WLCSP)

晶圓級晶片尺寸封裝(waferlevelchipscalepackage,WLCSP)由於可攜式電腦與消費電子產品的外形尺寸日趨縮小,以致內部可供放置電子元件的空間也日

益減小,因此對於近晶片尺寸或晶片尺寸構裝(chip scale package, CSP)的需求快速增加。

如

此一來許多不同的封裝方式如:多晶片模組(multi-chip module, MCM)、球柵陣列(ball grid

array,BGA)、覆晶(flip chip, FC)等先進技術應運而生。

直到近幾年,晶圓級晶片尺寸封裝

(wafer level chip scale package,WLCSP)可說是當前最受到全球封裝業界矚目的後起之秀。

由於其在封裝尺寸上更加輕薄短小,並且在製程及材料成本上具有優勢,因此目前深受業界注

視。

最近因為工作關係接觸了不少WLCSP的廠商及資訊,發覺未來真的是產業界的新型態,因為從

長遠角度來看如果chip size小而選擇WLCSP封裝確實成本是較傳統封裝來的便宜(傳統封裝有

leadframe的基本cost),所以我們才會採用此種封裝,雖然初期需要花費RDL Mask tooling cost較

高外,長久還是值得考慮

而且目前各大廠也都擴產能在WLCSP and Bumping , 因為目前產能需求是很大

所以國內各大封裝也都紛紛投入擴線計劃,原QFN市場也都慢慢轉投WLCSP這個領域,未來是值

得注意~~~WLCSP外觀

Front-end process

WLCSP proces overview

Cost Competitor。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

什么是晶圆级晶片尺寸封装(Wafer Level Chip Scale Packaging)

1. 晶圆级晶片尺寸封装(Wafer Level Chip Scale Packaging)是先在整片晶圆上进行封装和测试,然后经切割并将IC直接用机台以pick up & flip方式将其放置于Carrier tape中,并以Cover tape保护好后,提供后段SMT (Surface Mounting technology)直接以机台将该IC自Carrier tape取料后,置放于PCB上。

WLCSP选用较大的锡铅球来形成接点藉以进行电性导通,其目的是增加元件与基板底材之间的距离,进而降低并承受来自于基板与元件间因热膨胀差异产生的应力,增加元件的可靠性。

利用重分布层技术则可以让锡球的间距作有效率的安排,设计成矩阵式排列(grid array)。

采用晶圆制造的制程及电镀技术取代现有打金线及机械灌胶封模的制程,不需导线架或基板。

晶圆级封装只有晶粒般尺寸,且有较好的电性效能,因系以每批或每片晶片来生产, 故能享有较低之生产成本。

2.特点:

WLCSP 少掉基材、铜箔等,使其以晶圆形态进行研磨、切割后完成的IC 厚度和一般QFP 、BGA……等等比较起来为最薄、最小、最轻,较符合未来产品轻、薄之需求;且因其不需再进行封装,即可进行后段SMT 制程,故其成本价格可以较一般传统封装为低。

● 封装技术比较:

3.产品应用面:

3.1 Power supply (PMIC/PMU, DC/DC converters, MOSFET' s,...)

3.2 Optoelectronic device

3.3 Connectivity (Bluetooth, WLAN)

3.4 Other features (FM, GPS, Camera)

4.生产流程简介

Wafer backside metallization。