查表法计算CRC

[技术栈]CRC校验原理及C#代码实现CRC16、CRC32计算FCS校验码

![[技术栈]CRC校验原理及C#代码实现CRC16、CRC32计算FCS校验码](https://img.taocdn.com/s3/m/0bc92025cec789eb172ded630b1c59eef8c79a88.png)

[技术栈]CRC校验原理及C#代码实现CRC16、CRC32计算FCS校验码1.CRC、FCS是什么CRC,全称Cyclic Redundancy Check,中⽂名称为循环冗余校验,是⼀种根据⽹络数据包或计算机⽂件等数据产⽣简短固定位数校验码的⼀种信道编码技术,主要⽤来检测或校验数据传输或者保存后可能出现的错误。

它是利⽤除法及余数的原理来作错误侦测的。

FCS,全称Frame Check Sequence,中⽂名称为帧校验序列,俗称帧尾,即计算机⽹络数据链路层的协议数据单元(帧)的尾部字段,是⼀段4个字节的循环冗余校验码。

注:CRC循环冗余校验和FCS帧校验序列是单独的概念,CRC是⼀种错误校验⽅法,FCS是帧尾校验码,FCS可以采⽤CRC校验⽅法,也可以采⽤其他校验⽅法。

2.CRC算法原理我们可以把任意的⼀串⼆进制数据表⽰为⼀个与之对应的多项式。

⽐如:⼆进制数据:1100101多项式:x^6 + x^5 + x^2+1多项式:x^6 + x^4+x^3 + x^2+1⼆进制数据:1011101有了这样的对应关系,对⼆进制数据的CRC校验就可以利⽤多项式运算规则进⾏校验计算。

CRC校验算法正是采⽤了模2除法,在数据处理⾥的具体表现为异或运算。

CRC的具体运算规则为:假设要传输的⼆进制数据为:10010110,对应的m阶多项式为:M =x^7+x^4+x^2+x^1,除数为h阶的多项式为:H=x^4+x,对应的⼆进制码为:10010,先将M乘以x^h,即将M对应的⼆进制数据后⾯加h个0,然后除以h阶的多项式H,得到的h-1阶的余数项R对应的⼆进制数据即为数据10010110的CRC校验码。

3.计算CRC校验3.1.⼿⼯计算CRC校验码M和H的多项式除法运算,可以⽤模2除法运算计算。

下⾯为以⽣成多项式为H求10010110的CRC校验码运算过程:对应到异或运算:通过⽰例即其他⾃定义的⼀些数据运算后,根据运算现象总结可以得到⼀些规律:1.每次异或运算,当从左到右⾸位为1的时候,就与⽣成多项式H异或运算,然后再左移1位;当⾸位为0的时候只将数据左移1位。

循环冗余检验(CRC)算法原理

循环冗余检验(CRC)算法原理Cyclic R edundancy C heck循环冗余检验,是基于数据计算⼀组效验码,⽤于核对数据传输过程中是否被更改或传输错误。

算法原理假设数据传输过程中需要发送15位的⼆进制信息g=101001110100001,这串⼆进制码可表⽰为代数多项式g(x) = x^14 + x^12 + x^9 + x^8 + x^7 + x^5 + 1,其中g中第k位的值,对应g(x)中x^k的系数。

将g(x)乘以x^m,既将g后加m个0,然后除以m阶多项式h(x),得到的(m-1)阶余项r(x)对应的⼆进制码r就是CRC编码。

h(x)可以⾃由选择或者使⽤国际通⾏标准,⼀般按照h(x)的阶数m,将CRC算法称为CRC-m,⽐如CRC-32、CRC-64等。

国际通⾏标准可以参看g(x)和h(x)的除运算,可以通过g和h做xor(异或)运算。

⽐如将11001与10101做xor运算:明⽩了xor运算法则后,举⼀个例⼦使⽤CRC-8算法求101001110100001的效验码。

CRC-8标准的h(x) = x^8 + x^7 + x^6 + x^4 + x^2 + 1,既h是9位的⼆进制串111010101。

经过迭代运算后,最终得到的r是10001100,这就是CRC效验码。

通过⽰例,可以发现⼀些规律,依据这些规律调整算法:1. 每次迭代,根据gk的⾸位决定b,b是与gk进⾏运算的⼆进制码。

若gk的⾸位是1,则b=h;若gk的⾸位是0,则b=0,或者跳过此次迭代,上⾯的例⼦中就是碰到0后直接跳到后⾯的⾮零位。

2. 每次迭代,gk的⾸位将会被移出,所以只需考虑第2位后计算即可。

这样就可以舍弃h的⾸位,将b取h的后m位。

⽐如CRC-8的h是111010101,b只需是11010101。

3. 每次迭代,受到影响的是gk的前m位,所以构建⼀个m位的寄存器S,此寄存器储存gk的前m位。

每次迭代计算前先将S的⾸位抛弃,将寄存器左移⼀位,同时将g的后⼀位加⼊寄存器。

crc查表法计算实例

CRC(循环冗余校验)是一种常用的错误检测技术,其中查表法是一种高效计算CRC 值的方法。

下面是一个使用查表法计算CRC 的示例:```pythondef crc_lookup(data, crc_table):crc = 0xFFFF # 初始CRC 值for byte in data:crc = (crc >> 8) ^ crc_table[(crc ^ byte) & 0xFF]return crcdef calculate_crc(data):crc_table = [0x0000, 0x1021, 0x2042, 0x3063, 0x4084, 0x50A5, 0x60C6, 0x70E7,0x8108, 0x9129, 0xA14A, 0xB16B, 0xC18C, 0xD1AD, 0xE1CE, 0xF1EF] # CRC 查表# 将数据转换为字节列表if isinstance(data, str):data = data.encode()# 计算CRCcrc = crc_lookup(data, crc_table)return crc# 示例数据data = "Hello, World!"# 计算CRCcrc_result = calculate_crc(data)print(f"CRC Result: {hex(crc_result)}")```在上面的示例中,我们定义了两个函数:`crc_lookup` 和`calculate_crc`。

`crc_lookup` 函数用于执行CRC 查表操作,接受一个数据字节列表和CRC 查表作为参数,返回计算得到的CRC 值。

`calculate_crc` 函数用于将数据转换为字节列表,并调用`crc_lookup` 函数计算CRC 值。

在示例中,我们使用了一个16 位CRC 查表,以及一个示例数据"Hello, World!"。

modbus crc 查表法与计算法

Modbus是一种用于串行通信的协议,通常用于工业控制系统中的设备之间的通信。

在Modbus协议中,通信的数据经常需要进行CRC (循环冗余校验)校验以确保数据的准确性。

在实际应用中,我们可以通过查表法或计算法来计算Modbus协议中的CRC校验值。

本文将介绍Modbus CRC的查表法和计算法,并对这两种方法进行比较和分析。

一、Modbus CRC的概念及应用Modbus通信协议是一种用于工业控制系统的通信协议,它规定了设备之间的数据通信格式和规则。

在Modbus协议中,通信的数据需要进行CRC校验以确保数据的完整性和准确性。

CRC校验是一种通过对数据进行处理得到固定长度的校验码,用于校验数据传输的正确性的技术。

Modbus协议中的CRC校验值通常是16位的,可以通过CRC计算器进行计算,并将计算得到的校验值附加到数据传输中。

接收端收到数据后,同样可以通过计算CRC校验值来验证数据的正确性。

二、Modbus CRC的查表法1. 查表法是一种通过预先计算出CRC校验值并存储在表中,然后在实际使用时直接查表得到CRC校验值的方法。

对于Modbus协议中的CRC校验,可以使用一个256个元素的查表来进行计算。

2. 查表法的优点是计算速度快,适用于嵌入式系统或资源有限的设备。

由于CRC校验是通过查表得到的,因此不需要进行复杂的计算,可以节省系统资源和计算时间。

3. 但是查表法的缺点是需要额外的存储空间来存储CRC校验值的查表,对于一些资源有限的设备可能会造成存储空间的浪费。

三、Modbus CRC的计算法1. 计算法是一种通过数学计算来得到CRC校验值的方法。

对于Modbus协议中的CRC校验,可以使用多项式除法来进行计算。

2. 计算法的优点是不需要额外的存储空间来存储查表,因此不会造成存储空间的浪费。

而且计算法可以适用于任何系统,不受资源限制的影响。

3. 但是计算法的缺点是计算速度相对较慢,特别是对于资源有限的嵌入式系统或单片机来说,可能会影响系统的性能。

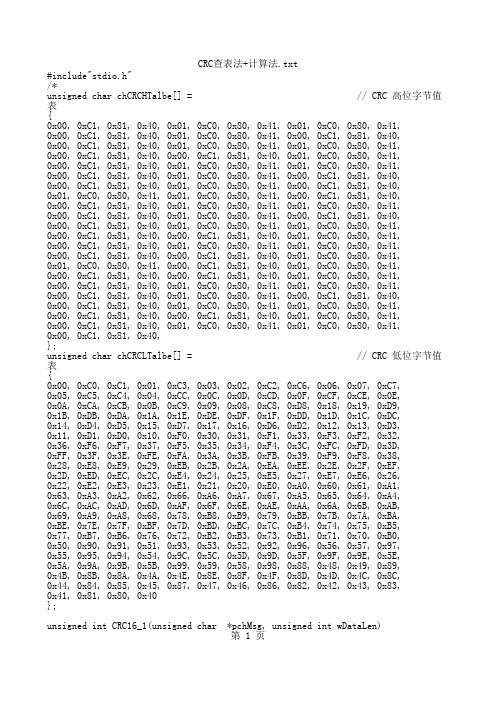

CRC查表法 计算法

}

return ((chCRCHi << 8) | chCRCLo) ;

}

unsigned char data[9]={0x01, 0x10 ,0x00, 0x40 ,0x00, 0x01 ,0x02 ,0x07, 0xD0}; #define length 9 unsigned char *p[length]; void main() {

CRC16=*ptr^CRC16; for (j=0;j< 8;j++) {

tmp=CRC16 & 0x0001; CRC16 =CRC16 >>1; if (tmp) CRC16=CRC16 ^ 0xa001; } *ptr++; } return(CRC16); } void main() { for(j=0;j<10;j++) { p[j]=&data[j]; } CRC=crc16l(*p,length);

0x00, 0xC1, 0x81, 0x40, 0x00, 0xC1, 0x81, 0x40, 0x01, 0xC0, 0x80, 0x41,

0x00, 0xC1, 0x81, 0x40, 0x01, 0xC0, 0x80, 0x41, 0x01, 0xC0, 0x80, 0x41,

0x00, 0xC1, 0x81, 0x40, 0x00, 0xC1, 0x81, 0x40, 0x01, 0xC0, 0x80, 0x41,

int CRC=0; int j=0; for(j=0;j<10;j++) {

p[j]=&data[j]; }

CRC=CRC16_1(*p,length);

c语言crc校验程序查表法

c语言crc校验程序查表法

(原创版)

目录

1.CRC 校验原理

2.C 语言 CRC 校验程序实现

3.查表法在 CRC 校验中的应用

4.实例:使用查表法实现 CRC 校验

正文

一、CRC 校验原理

CRC(Cyclic Redundancy Check,循环冗余校验)是一种基于二进制多项式的数据校验技术。

它通过在数据末尾附加一些校验位,然后接收方在接收到数据后,通过相同的计算方法,对数据进行校验,以判断数据在传输过程中是否发生了改变或损坏。

CRC 校验的主要优点是能够检测出大部分数据传输错误,且计算简单,易于实现。

二、C 语言 CRC 校验程序实现

C 语言中实现 CRC 校验的主要步骤如下:

1.首先,根据需要生成一个二进制多项式。

这个多项式可以是固定的,也可以是随机生成的。

2.将待校验的数据用二进制表示,并在数据末尾添加一些校验位,使得整个数据长度可以被二进制多项式整除。

3.使用二进制多项式去除数据,得到一个余数。

这个余数就是 CRC 校验的结果。

4.在接收端,使用相同的方法计算 CRC 校验结果,然后将其与发送端得到的结果进行比较。

如果二者相同,则认为数据传输正确;如果不同,

则认为数据发生了改变或损坏。

三、查表法在 CRC 校验中的应用

查表法是一种常用的 CRC 校验算法。

它通过预先计算一组 CRC 值,并将其存储在表格中。

在需要进行 CRC 校验时,只需要查找对应的 CRC 值即可。

这种方法的优点是计算速度快,节省存储空间。

crc16查表法中表格数据计算方法及实例

最近在搞CRC校验,用的是CRC16标准,查看了很多资料发现很多讲的都是CRC16-CCITT标准,一直想弄明白CRC-16标准中的采用查表法的方式中那两个表格中的数是如何求出来的。

可惜没有一个文章仔细的讲,更没有文章给出实例来算一算。

一切只能靠自己了,谁让我喜欢寻根摸底呢。

研究了一下本站会员玉丫子的文章,自己琢磨了琢磨,终于知道是怎么算出来的了。

CRC16算法的生成多项式x^16 + x^15 + x^2 + 1,十六进制表示为0x8005。

CRC16常见的表格中的数据是按照先传输LSB,消息右移进寄存器来计算的。

因此需要判断寄存器的最低位LSB,同时要将0x8005按位颠倒后(0xA001)根据LSB的情况决定是否与寄存器异或即可。

CRC16的表格中对应的数依次为0~255计算出来的CRC值,因此,此处只选取其中一两个数作为实例计算CRC值。

具体步骤如下所示:1)从0~255中选取需要计算的数,将其对应的十六进制数放入一个长度为16的寄存器的低八位,高八位填充0;2)如果寄存器的末位LSB为1,将寄存器的数值右移1位,再与0xA001位异或,否则仅将寄存器右移1位;3)重复第2步,直到低八位全部右移出寄存器;4)寄存器中的值则为校验码。

从0~255中挑选2(对应0x02)计算其CRC值:0x02的CRC-16的表格计算(反向)00000000 00000010 <- 最低位LSB = 0,高八位填充000000000 000000010 右移,高位填充0,并舍弃最后一位----------------- 第一次计算00000000 00000001 <- LSB = 100000000 000000001 右移,舍弃最后一位^10100000 00000001 <-与0xA001异或----------------- 第二次10100000 00000001 <- LSB = 101010000 000000001右移,舍弃最后一位^10100000 00000001 <-与0xA001异或----------------- 第三次11110000 00000001 <- LSB = 101111000 000000001右移,舍弃最后一位^10100000 00000001 <-与0xA001异或----------------- 第四次11011000 00000001 <- LSB = 101101100 000000001右移,舍弃最后一位^10100000 00000001 <-与0xA001异或----------------- 第五次11001100 00000001 <- LSB = 101100110 000000001右移,舍弃最后一位^10100000 00000001 <-与0xA001异或----------------- 第六次11000110 00000001 <- LSB = 101100011 000000001右移,舍弃最后一位^10100000 00000001 <-与0xA001异或----------------- 第七次11000011 00000001 <- LSB = 101100001 100000001右移,舍弃最后一位^10100000 00000001 <-与0xA001异或----------------- 一共右移了八次,得到的结果为CRC11000001 10000001 <- CRC: 0xC1 81从本文最后的附表中可以看出auchCRCHi[]的第三个值就是0x 81,auchCRCLo[]的第三个值就是0xC1,可见计算无误。

crc校验查表法原理

crc校验查表法原理CRC(Cyclic Redundancy Check)校验是一种常用的数据传输错误检测方法,广泛应用于计算机网络、通信等领域。

CRC校验的查表法原理是其中一种实现方式,通过查表的方式来进行校验计算,下面将详细介绍这种方法的原理和应用。

1. CRC校验的基本原理CRC校验是一种基于多项式除法的校验方法。

在CRC校验过程中,发送方和接收方约定一个生成多项式(Generator Polynomial),通常记作G(x)。

发送方在发送数据之前,先计算待发送数据的CRC校验值,并将其附加到数据末尾,形成一个完整的帧。

接收方同样计算接收到数据的CRC校验值,并与接收到的CRC校验值进行比较,如果两者相等,则数据传输没有出现错误。

2. 查表法原理查表法是实现CRC校验的一种高效方法。

其基本原理是将CRC校验过程中的除法运算转化为查表操作,从而提高计算效率。

具体步骤如下:(1)生成查表表格:根据生成多项式G(x)的阶数,生成一个2^m 大小的查表表格,其中m为生成多项式的阶数。

(2)数据处理:将待发送的数据按照二进制形式表示,并在数据末尾添加n个0,其中n为生成多项式的阶数。

(3)查表运算:从数据的最高位开始,每次取m位数据,并将其作为查表表格的索引,找到对应的查表值。

然后将查表值与当前数据进行异或运算,并将结果作为下一次计算的数据。

(4)重复上述操作,直到处理完所有数据位。

(5)得到CRC校验值:经过上述计算后,最后剩下的数据即为CRC 校验值,将其附加到原始数据末尾,形成一个完整的帧。

3. 查表法的优势相比于其他计算方法,查表法具有以下几个优势:(1)高效性:通过查表的方式,可以大大提高CRC校验的计算效率,尤其是对于大数据量的情况,查表法比较快速。

(2)易于实现:查表法的实现相对简单,只需要生成查表表格,并根据表格进行查表运算即可。

(3)节省存储空间:通过查表的方式,可以将除法运算转化为查表操作,从而避免了除法运算需要的存储空间。

三种常用的CRC16校验算法的C51程序的优化

}

ptr++;

count--;

}

return crc.x;

}

编译后函数crc2的代码长度为76,函数crc3的代码长度为68,变化不是太大,但是执行效率是很不一样的,具体差别见后面的表一。

优化后的查表+计算法的程序为:

unsigned int crc5(unsigned char *ptr,unsigned char len)

crc.x <<=4;

crc.c[0] ^=crch[t];

crc.c[1] ^=crcl[t];

t = (crc.c[0]>>4) ^ (*ptr & 0x0F);

crc.x <<=4;

crc.c[0] ^=crch[t];

crc ^= crc_ta[da^(*ptr/16)]; /* CRC的高4位和本字节的前半字节相加后查表*/

/*计算CRC,然后加上上一次CRC的余数 */

da = ((crc/256))/16; /* 暂存CRC的高4位 */

crc <<=4; /* CRC右移4位, 相当于CRC的低12位) */

unsigned int crc3(unsigned char *ptr,unsigned char count)

{

data unsigned char i;

union{

unsigned char c[2];

unsigned int x;

}data crc;

pData++;

}

return CRC16;

}

编译后,函数crc0的代码为68字节,加上表格占用的512字节,一共使用了580个字节的代码空间。

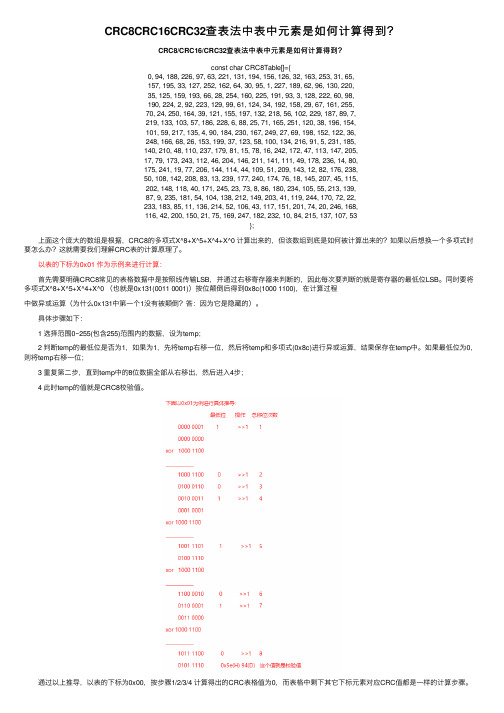

CRC8CRC16CRC32查表法中表中元素是如何计算得到?

CRC8CRC16CRC32查表法中表中元素是如何计算得到?CRC8/CRC16/CRC32查表法中表中元素是如何计算得到?const char CRC8Table[]={0, 94, 188, 226, 97, 63, 221, 131, 194, 156, 126, 32, 163, 253, 31, 65,157, 195, 33, 127, 252, 162, 64, 30, 95, 1, 227, 189, 62, 96, 130, 220,35, 125, 159, 193, 66, 28, 254, 160, 225, 191, 93, 3, 128, 222, 60, 98,190, 224, 2, 92, 223, 129, 99, 61, 124, 34, 192, 158, 29, 67, 161, 255,70, 24, 250, 164, 39, 121, 155, 197, 132, 218, 56, 102, 229, 187, 89, 7,219, 133, 103, 57, 186, 228, 6, 88, 25, 71, 165, 251, 120, 38, 196, 154,101, 59, 217, 135, 4, 90, 184, 230, 167, 249, 27, 69, 198, 152, 122, 36,248, 166, 68, 26, 153, 199, 37, 123, 58, 100, 134, 216, 91, 5, 231, 185,140, 210, 48, 110, 237, 179, 81, 15, 78, 16, 242, 172, 47, 113, 147, 205,17, 79, 173, 243, 112, 46, 204, 146, 211, 141, 111, 49, 178, 236, 14, 80,175, 241, 19, 77, 206, 144, 114, 44, 109, 51, 209, 143, 12, 82, 176, 238,50, 108, 142, 208, 83, 13, 239, 177, 240, 174, 76, 18, 145, 207, 45, 115,202, 148, 118, 40, 171, 245, 23, 73, 8, 86, 180, 234, 105, 55, 213, 139,87, 9, 235, 181, 54, 104, 138, 212, 149, 203, 41, 119, 244, 170, 72, 22,233, 183, 85, 11, 136, 214, 52, 106, 43, 117, 151, 201, 74, 20, 246, 168,116, 42, 200, 150, 21, 75, 169, 247, 182, 232, 10, 84, 215, 137, 107, 53}; 上⾯这个庞⼤的数组是根据,CRC8的多项式X^8+X^5+X^4+X^0 计算出来的,但该数组到底是如何被计算出来的?如果以后想换⼀个多项式时要怎么办?这就需要我们理解CRC表的计算原理了。

三种常用的CRC16校验算法的C51程序的优化

};

union{

unsigned char c[2];

unsigned int x;

}data crc;

unsigned char t;

crc.x =0;

while(len!=0) {

t = (crc.c[0]>>4) ^ (*ptr >>4);

crc.c[1] ^=crcl[t];

ptr++;

len--;

}

return crc.x;

}

优化前后的代码长度分别为1ห้องสมุดไป่ตู้5字节和146字节(包括了32字节的表格空间)。

代码测试:仅代码长度变短是不够的,衡量优化后的程序一个重要的标准是看优化前后两个函数执行相同的计算量使用的时间,或者说执行的效率是否提高了。如果优化后的函数需要时间少,就说明我们优化后的函数确实提高了效率,否则就是反而降低了程序的效率,优化失败。我在 Keil C51 下编写了一个测试程序,在程序中调用了上面的六个函数,共同计算一个长度为200字节的CRC校验,并记录下每个函数使用的时间。测试方法为:使用 Keil C51 的软件仿真功能(采用带计时功能的硬件仿真器也可以),在每个函数上加上断点,记录下执行到每个断点的时间,然后前后相减就得出每个函数的执行时间。仿真时使用的单片机型号为AT89C51,晶体频率为12MHz。

三种常用的CRC16校验算法的C51程序的优化

CRC校验又称为循环冗余校验,是数据通讯中常用的一种校验算法。它可以有效的判别出数据在传输过程中是否发生了错误,从而保障了传输的数据可靠性。

CRC校验有多种方式,如:CRC8、CRC16、CRC32等等。在实际使用中,我们经常使用CRC16校验。CRC16校验也有多种,如:1005多项式、1021多项式(CRC-ITU)等。在这里我们不讨论CRC算法是怎样产生的,而是重点落在几种算法的C51程序的优化上。

循环冗余码(crc)及计算方法

循环冗余码(crc)及计算方法循环冗余校验码,简称CRC(Cyclic Redundancy Check),是一种数据传输异常检测方法,已经被广泛应用于数据链路层和物理层等数据通信领域。

在传输过程中,所传输的信息数据可能被多次修改,或者有噪声或干扰。

这就导致了所接收到的数据并不是最初发出的特定数据,使得传输失败或受到破坏。

作为一种效果比较好的校验技术,CRC校验码技术就派上用场了,它通过数据发送者事先计算出一串特定长度(字节)的校验码放入发送的数据帧中,接收者收到数据帧时会对数据帧进行检测,以查看接收的数据帧校验码与数据是否原来发出数据时相同,如果不同,就表示数据帧损坏,接收者通知发送者重发。

CRC校验码单元通过将发出方所发送的原始数据(数据帧data)与一个固定长度的多项式(CRC多项式)按位依次做按位异或的运算,来生成新的检验码,称之为CRC校验码(check)。

如果接收res方收到了与发送snd方发出的数据帧内容相同的数据帧,那么接收res方也可以使用CRC多项式对收到的数据帧做相同的计算,如果生成的CRC校验码与原始数据帧中存储的CRC校验码相同,说明数据接收是无误的。

如果不一致,说明中间可能发生了数据传输错误,数据接收存在错误,这可能是由于传输和接收途经的环境中有噪声或是由于数据本身的丢失/"随机"改变或添加其他数据导致的。

CRC校验码的计算方法通常有两种,查表法和无查表法。

查表法即在发送前定义好一张查表,根据查表给出CRC-Code。

无查表法是一种比较复杂的算法,该法首先根据CRC多项式,将多项式拆解成一个个单项式数及其系数,然后,根据定义式进行模2加,一直进行运算,得出最后的CRC校验值,该校验值就作为原来数据在发送前附加上去。

CRC校验码是目前数据链路层较为安全的一种编码技术,它可以在较大的概率内检测出传输中的比特错误。

而且,CRC校验的编码效率高,而且相当安全,是一种能够在低价值硬件中实现的有效的编码和校验技术。

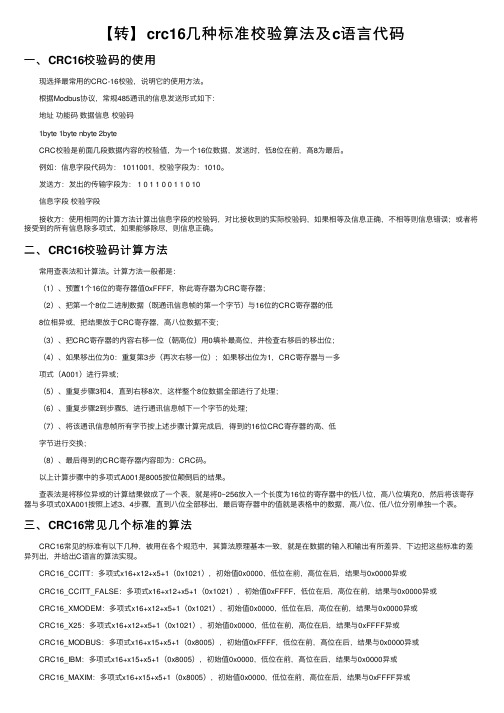

【转】crc16几种标准校验算法及c语言代码

【转】crc16⼏种标准校验算法及c语⾔代码⼀、CRC16校验码的使⽤ 现选择最常⽤的CRC-16校验,说明它的使⽤⽅法。

根据Modbus协议,常规485通讯的信息发送形式如下: 地址功能码数据信息校验码 1byte 1byte nbyte 2byte CRC校验是前⾯⼏段数据内容的校验值,为⼀个16位数据,发送时,低8位在前,⾼8为最后。

例如:信息字段代码为: 1011001,校验字段为:1010。

发送⽅:发出的传输字段为: 1 0 1 1 0 0 1 1 0 10 信息字段校验字段 接收⽅:使⽤相同的计算⽅法计算出信息字段的校验码,对⽐接收到的实际校验码,如果相等及信息正确,不相等则信息错误;或者将接受到的所有信息除多项式,如果能够除尽,则信息正确。

⼆、CRC16校验码计算⽅法 常⽤查表法和计算法。

计算⽅法⼀般都是: (1)、预置1个16位的寄存器值0xFFFF,称此寄存器为CRC寄存器; (2)、把第⼀个8位⼆进制数据(既通讯信息帧的第⼀个字节)与16位的CRC寄存器的低 8位相异或,把结果放于CRC寄存器,⾼⼋位数据不变; (3)、把CRC寄存器的内容右移⼀位(朝⾼位)⽤0填补最⾼位,并检查右移后的移出位; (4)、如果移出位为0:重复第3步(再次右移⼀位);如果移出位为1,CRC寄存器与⼀多 项式(A001)进⾏异或; (5)、重复步骤3和4,直到右移8次,这样整个8位数据全部进⾏了处理; (6)、重复步骤2到步骤5,进⾏通讯信息帧下⼀个字节的处理; (7)、将该通讯信息帧所有字节按上述步骤计算完成后,得到的16位CRC寄存器的⾼、低 字节进⾏交换; (8)、最后得到的CRC寄存器内容即为:CRC码。

以上计算步骤中的多项式A001是8005按位颠倒后的结果。

查表法是将移位异或的计算结果做成了⼀个表,就是将0~256放⼊⼀个长度为16位的寄存器中的低⼋位,⾼⼋位填充0,然后将该寄存器与多项式0XA001按照上述3、4步骤,直到⼋位全部移出,最后寄存器中的值就是表格中的数据,⾼⼋位、低⼋位分别单独⼀个表。

crc校验查表法原理

crc校验查表法原理CRC校验是一种常用的错误检测方法,通过对数据进行计算生成校验码,可以快速检测出数据传输过程中是否出现错误。

而CRC校验的查表法则是其中一种较为高效的实现方式。

本文将详细介绍CRC 校验查表法的原理和实现方法。

一、CRC校验概述CRC(Cyclic Redundancy Check)校验是一种循环冗余校验方法,常用于数据通信领域。

它通过对数据进行多项式除法运算,得到余数作为校验码。

接收方根据发送方传输的数据和校验码进行计算,如果计算出的余数为0,则认为数据传输正确;否则,认为数据传输出现错误。

二、CRC校验查表法原理CRC校验查表法是CRC校验的一种高效实现方式。

它通过预先计算出一张查表,将多项式除法运算转化为简单的查表操作,从而提高计算效率。

1. 多项式转化为二进制将CRC校验中使用的多项式转化为二进制形式。

例如,CRC-8校验中使用的多项式为x^8 + x^2 + x + 1,将其转化为二进制形式为100000111。

2. 初始化查表根据CRC校验的位数,初始化一个256个元素的查表。

以CRC-8为例,查表长度为256个元素。

3. 生成查表从0到255的每一个数值,通过以下步骤生成查表的每个元素:(1)将当前数值左移8位,作为除数。

(2)循环8次,每次判断除数最高位是否为1:- 如果最高位为1,则将除数左移一位,并与多项式进行异或操作。

- 如果最高位为0,则将除数左移一位。

(3)将计算结果作为查表的当前元素。

4. CRC校验过程发送方在发送数据前,根据多项式和查表生成校验码。

接收方在接收到数据后,根据接收到的数据和查表进行校验。

(1)发送方:- 将数据按位划分为若干字节。

- 初始化CRC校验值为0。

- 依次取出每个字节,将其与CRC校验值进行异或操作。

- 根据异或的结果,在查表中查找对应的值,并更新CRC校验值。

- 重复以上步骤,直到所有字节处理完毕。

- 最终的CRC校验值即为校验码,将其附加到数据后发送。

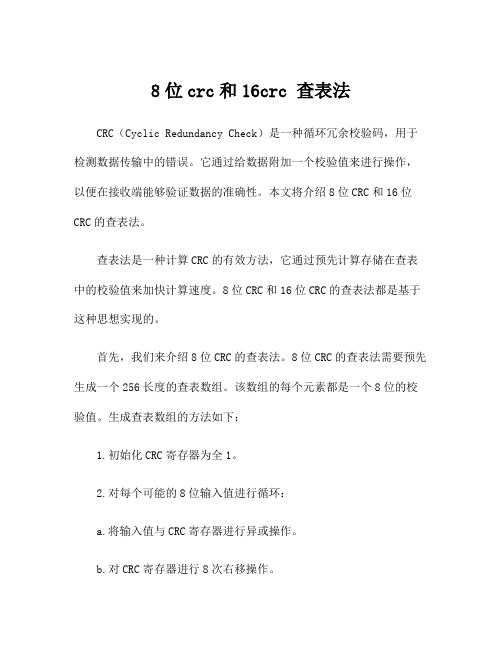

8位crc和16crc 查表法

8位crc和16crc 查表法CRC(Cyclic Redundancy Check)是一种循环冗余校验码,用于检测数据传输中的错误。

它通过给数据附加一个校验值来进行操作,以便在接收端能够验证数据的准确性。

本文将介绍8位CRC和16位CRC的查表法。

查表法是一种计算CRC的有效方法,它通过预先计算存储在查表中的校验值来加快计算速度。

8位CRC和16位CRC的查表法都是基于这种思想实现的。

首先,我们来介绍8位CRC的查表法。

8位CRC的查表法需要预先生成一个256长度的查表数组。

该数组的每个元素都是一个8位的校验值。

生成查表数组的方法如下:1.初始化CRC寄存器为全1。

2.对每个可能的8位输入值进行循环:a.将输入值与CRC寄存器进行异或操作。

b.对CRC寄存器进行8次右移操作。

3.根据CRC寄存器的最终值,将对应输入值的校验值存储在查表数组中。

生成查表数组后,我们可以使用该数组对数据进行CRC计算。

计算方法如下:1.初始化CRC寄存器为全1。

2.对每个输入字节进行循环:a.将当前输入字节与CRC寄存器进行异或操作,得到查表数组的索引。

b.根据索引从查表数组中取出对应的校验值。

c.将CRC寄存器与校验值进行异或操作。

d.对CRC寄存器进行8次右移操作。

3.根据CRC寄存器的最终值得到计算得到的校验值。

接下来,我们来介绍16位CRC的查表法。

与8位CRC类似,16位CRC的查表法也需要预先生成一个65536长度的查表数组。

生成查表数组的方法如下:1.初始化CRC寄存器为全1。

2.对每个可能的16位输入值进行循环:a.将输入值与CRC寄存器进行异或操作。

b.对CRC寄存器进行16次右移操作。

3.根据CRC寄存器的最终值,将对应输入值的校验值存储在查表数组中。

生成查表数组后,我们可以使用该数组对数据进行CRC计算。

计算方法如下:1.初始化CRC寄存器为全1。

2.对每个输入字节进行循环:a.将当前输入字节与CRC寄存器进行异或操作,得到查表数组的索引。

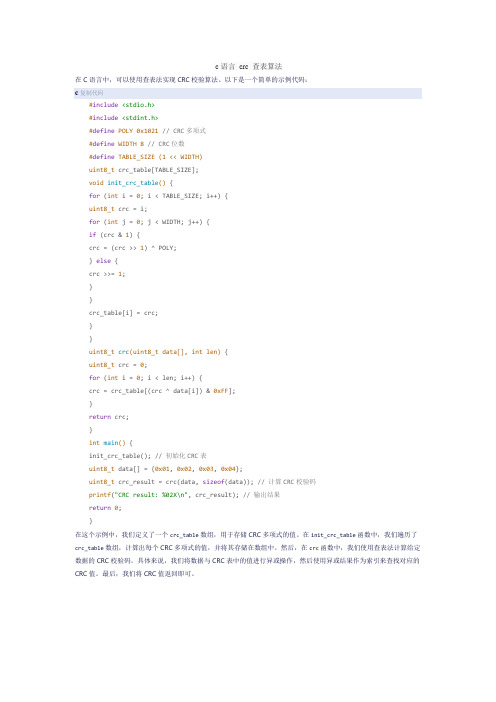

c语言 crc 查表算法

c语言crc 查表算法在C语言中,可以使用查表法实现CRC校验算法。

以下是一个简单的示例代码:c复制代码#include<stdio.h>#include<stdint.h>#define POLY 0x1021 // CRC多项式#define WIDTH 8 // CRC位数#define TABLE_SIZE (1 << WIDTH)uint8_t crc_table[TABLE_SIZE];void init_crc_table() {for (int i = 0; i < TABLE_SIZE; i++) {uint8_t crc = i;for (int j = 0; j < WIDTH; j++) {if (crc & 1) {crc = (crc >> 1) ^ POLY;} else {crc >>= 1;}}crc_table[i] = crc;}}uint8_t crc(uint8_t data[], int len) {uint8_t crc = 0;for (int i = 0; i < len; i++) {crc = crc_table[(crc ^ data[i]) & 0xFF];}return crc;}int main() {init_crc_table(); // 初始化CRC表uint8_t data[] = {0x01, 0x02, 0x03, 0x04};uint8_t crc_result = crc(data, sizeof(data)); // 计算CRC校验码printf("CRC result: %02X\n", crc_result); // 输出结果return0;}在这个示例中,我们定义了一个crc_table数组,用于存储CRC多项式的值。

crc查表法计算实例

crc查表法计算实例CRC查表法计算实例什么是CRC查表法CRC (Cyclic Redundancy Check) 是一种校验算法,常用于网络通信、数据存储等领域,用于检测数据在传输过程中是否发生错误。

CRC查表法是一种高效的计算CRC的方法,通过提前生成一个CRC校验表,能够大幅加快CRC的计算速度。

CRC查表法的原理CRC查表法的原理是通过一个CRC校验表来进行CRC的计算,而不是像传统的Bit-by-Bit方式一位一位地计算。

CRC校验表是预先计算好的,根据CRC算法的不同,表的大小也有所不同。

计算CRC时,只需要将数据按字节与CRC校验表进行查表,最后得到的结果即为CRC 值。

CRC查表法的步骤CRC查表法的计算步骤如下:1.初始化CRC校验值为特定的初始值。

2.将第一个字节与CRC校验表进行查找,得到对应的新的CRC校验值。

3.重复步骤2,将后续的字节与CRC校验表进行查找,并更新CRC校验值。

4.最后得到的CRC校验值即为计算结果。

CRC查表法计算实例假设需要计算一个16位CRC校验值,初始值为0xFFFF,数据为0x。

计算过程如下:1.初始化CRC校验值为0xFFFF。

2.将第一个字节0x12与CRC校验表进行查找,得到新的CRC校验值为0x6F87。

3.继续查表操作,将后续字节0x34、0x56、0x78依次与CRC校验表进行查找,并更新CRC校验值。

4.最后得到的CRC校验值为0xAEE7,即为计算结果。

通过CRC查表法,只需要对每个字节进行一次查找操作,计算速度较快,尤其对于大量数据的CRC校验非常高效。

总结CRC查表法通过预先生成CRC校验表,大大加快了CRC的计算速度。

它是一种高效可靠的校验算法,被广泛应用于各个领域。

对于创作者来说,了解CRC查表法的原理和步骤,能够更好地理解和运用CRC 校验算法,提高代码的效率和可靠性。

CRC查表法的优势CRC查表法相较于传统的Bit-by-Bit方式,具有以下几个优势:1.计算速度更快:使用CRC查表法,只需要进行查表操作,而不是逐位计算。

查表法计算CRC

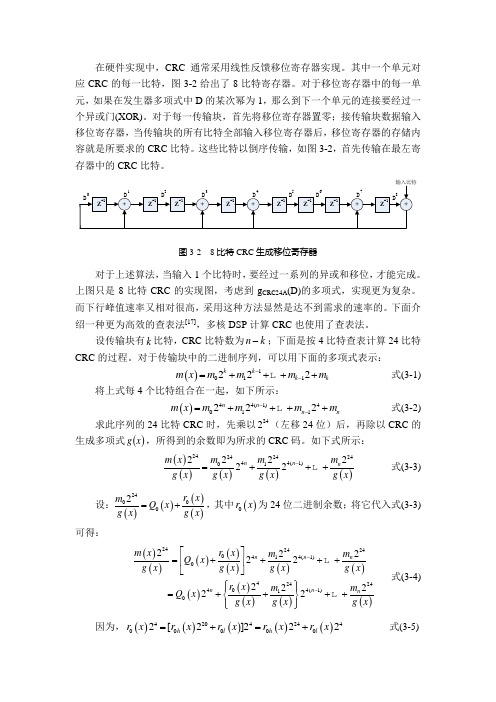

在硬件实现中,CRC 通常采用线性反馈移位寄存器实现。

其中一个单元对应CRC 的每一比特,图3-2给出了8比特寄存器。

对于移位寄存器中的每一单元,如果在发生器多项式中D 的某次幂为1,那么到下一个单元的连接要经过一个异或门(XOR)。

对于每一传输块,首先将移位寄存器置零;接传输块数据输入移位寄存器,当传输块的所有比特全部输入移位寄存器后,移位寄存器的存储内容就是所要求的CRC 比特。

这些比特以倒序传输,如图3-2,首先传输在最左寄存器中的CRC 比特。

图3-2 8比特CRC 生成移位寄存器对于上述算法,当输入1个比特时,要经过一系列的异或和移位,才能完成。

上图只是8比特CRC 的实现图,考虑到g CRC24A (D)的多项式,实现更为复杂。

而下行峰值速率又相对很高,采用这种方法显然是达不到需求的速率的。

下面介绍一种更为高效的查表法[17],多核DSP 计算CRC 也使用了查表法。

设传输块有k 比特,CRC 比特数为k n -;下面是按4比特查表计算24比特CRC 的过程。

对于传输块中的二进制序列,可以用下面的多项式表示:()1011222k k k k m x m m m m --=++++ 式(3-1) 将上式每4个比特组合在一起,如下所示:()44(1)4011222n n n n m x m m m m --=++++ 式(3-2)求此序列的24比特CRC 时,先乘以242(左移24位)后,再除以CRC 的生成多项式()x g ,所得到的余数即为所求的CRC 码。

如下式所示:()()()()()2424242444(1)01222222n n n m x m m m g x g x g x g x -=+++式(3-3) 设:()()()()240002r x m Q x g x g x =+,其中()0r x 为24位二进制余数;将它代入式(3-3)可得:()()()()()()()()()()()()242424044(1)1042424044(1)102222222222n n n nn n m x r x m m Q x g x g x g x g x r x m m Q x g x g x g x --⎡⎤=++++⎢⎥⎣⎦⎧⎫⎪⎪=++++⎨⎬⎪⎪⎩⎭式(3-4)因为,()()()()()4204244000002[2]222h l h l r x r x r x r x r x =+=+ 式(3-5)其中()0h r x 是()0r x 的高4位,()0l r x 是()0r x 的低20位。

crc8查表法原理

crc8查表法原理

crc8查表法原理是一种计算CRC校验值的方法,它基于查表法来实现CRC校验。

CRC校验是一种常用的数据校验方式,它可以检测数据传输中出现的任何错误,从而保证数据的准确性。

CRC校验使用了一个称为“循环冗余校验”的算法,通过对数据进行一系列的计算,生成一个校验值,将该校验值与接收到的数据进行比较,以判断数据是否正确。

在CRC8查表法中,将所有可能的8位数据的CRC校验值预先计算出来并存储在一个256个元素的查表数组中。

当需要校验一段数据时,将数据中的每个字节与CRC查表进行查找,然后将结果与已经计算出来的CRC校验值进行异或运算,最终得到校验值。

这种方法的优点是速度快,适用于需要快速计算CRC校验值的场合,例如在网络通信、存储介质中使用。

需要注意的是,CRC8查表法并不一定适用于所有的数据,因为它只能生成8位的校验值。

如果需要更高精度的校验值,需要使用更复杂的算法,例如CRC16、CRC32等。

- 1 -。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在硬件实现中,CRC 通常采用线性反馈移位寄存器实现。

其中一个单元对应CRC 的每一比特,图3-2给出了8比特寄存器。

对于移位寄存器中的每一单元,如果在发生器多项式中D 的某次幂为1,那么到下一个单元的连接要经过一个异或门(XOR)。

对于每一传输块,首先将移位寄存器置零;接传输块数据输入移位寄存器,当传输块的所有比特全部输入移位寄存器后,移位寄存器的存储内容就是所要求的CRC 比特。

这些比特以倒序传输,如图3-2,首先传输在最左寄存器中的CRC 比特。

图3-2 8比特CRC 生成移位寄存器

对于上述算法,当输入1个比特时,要经过一系列的异或和移位,才能完成。

上图只是8比特CRC 的实现图,考虑到g CRC24A (D)的多项式,实现更为复杂。

而下行峰值速率又相对很高,采用这种方法显然是达不到需求的速率的。

下面介绍一种更为高效的查表法[17],多核DSP 计算CRC 也使用了查表法。

设传输块有k 比特,CRC 比特数为k n -;下面是按4比特查表计算24比特CRC 的过程。

对于传输块中的二进制序列,可以用下面的多项式表示:

()1011222k k k k m x m m m m --=++++ 式(3-1) 将上式每4个比特组合在一起,如下所示:

()44(1)4011222n n n n m x m m m m --=++

++ 式(3-2)

求此序列的24比特CRC 时,先乘以242(左移24位)后,再除以CRC 的生成多项式()x g ,所得到的余数即为所求的CRC 码。

如下式所示:

()()()()

()

242424

2444(1)

01222222n n n m x m m m g x g x g x g x -=+++

式(3-3) 设:()()()()24

0002r x m Q x g x g x =+

,其中()0r x 为24位二进制余数;将它代入式(3-3)可得:

()()()()()()()()()()()()2424

24044(1)1042424

044(1)102222222222

n n n n

n n m x r x m m Q x g x g x g x g x r x m m Q x g x g x g x --⎡⎤=++++⎢⎥⎣

⎦⎧⎫⎪⎪=++++⎨⎬⎪⎪⎩⎭

式(3-4)

因为,()()()()()4204244000002[2]222h l h l r x r x r x r x r x =+=+ 式(3-5)

其中()0h r x 是()0r x 的高4位,()0l r x 是()0r x 的低20位。

将式(3-5)带入式(3-4)经整理得:

()()()()()()()

24424

24

044(1)01022[]2222

l n

n h n m x r x r m m Q x g x g x g x g x -⎧⎫+⎪⎪=++++⎨⎬⎪⎪⎩

⎭ 式(3-6) 再设:()()()()()()42401

0112[]2l h r x r x r m Q x g x g x g x ++=+,其中()1r x 仍是24位二进制余数。

根据上面的推导过程,以次类推可得:

()()

()()()()

()

24

44(1)01222n n n n m x r x Q x Q x Q x g x g x -=++++

式(3-7) 其中24位二进制余数()n r x 即为要求的CRC 比特。

式(3-7)是按4比特计算CRC 比特的递推公式。

从式子可以看出,输入本4比特后的CRC 比特等于输入本4比特前的CRC 码的低20位左移4位后再加上它右移20位(即取高4位)与将要输入字节之和后的CRC 值。

所以,如果将4位二进制序列的CRC 全部计算出来再存储在表中,则可以通过查表来计算CRC 。