S3C2440中断控制器痛点详解

mini2440调试进不了中断解决方案

ldr r0,=SRCPND str r1,[r0] ldr r0,=INTPND str r1,[r0] ldr r0,=INTSUBMSK ldr r1,=0x7fff @all sub interrupt disable, 2002/04/10 str r1,[r0] @@@设置频率 mov r1, #CLK_CTL_BASE ldr r2, clock_locktime str r2, [r1, #oLOCKTIME] mov r1, #CLK_CTL_BASE ldr r2, clkdivn_value str r2, [r1, #oCLKDIVN] mrc p15, 0, r1, c1, c0, 0 @ read ctrl register orr r1, r1, #0xc0000000 @ Asynchronous mcr p15, 0, r1, c1, c0, 0 @ write ctrl register mov r1, #CLK_CTL_BASE ldr r2, mpll_value @ clock default str r2, [r1, #oMPLLCON] @@@@初始化串口 InitUART: @set GPIO for UART mov r1, #GPIO_CTL_BASE add r1, r1, #oGPIO_H ldr r2, gpio_con_uart str r2, [r1, #oGPIO_CON] ldr r2, gpio_up_uart str r2, [r1, #oGPIO_UP] ldr r1, SerBase mov r2, #0x0 str r2, [r1, #oUFCON] str r2, [r1, #oUMCON] mov r2, #0x3 str r2, [r1, #oULCON] ldr r2, =0x245 str r2, [r1, #oUCON] .equ UART_BRD , ((UART_PCLK / (UART_BAUD_RATE*16)) - 1) mov r2, #UART_BRD str r2, [r1, #oUBRDIV] mov r3, #100 InitUART1:

实验5 S3C2440中断实验

LOOP0

stmfd sp!,{r0,r1,lr}; 保存现场 ldr r0,=0x20005000 ; 取LED灯驱动器端口地址 ldr r1,=0x01 str r1,[r0] ; 点亮第1个LED灯 bl Delay ; 延迟 ldr r0,=0x20005000 ; ldr r1,=0x03 str r1,[r0] ; 点亮第2个LED灯 bl Delay ; 延迟 ldr r0,=0x20005000; ldr r1,=0x07 str r1,[r0] ; 点亮第3个LED灯 bl Delay ; 延迟 ldr r0,=0x20005000 ; 点亮第4个LED灯 ldr r1,=0x0f str r1,[r0] bl Delay ;延迟 ldr r0,=0x20005000 ;熄灭所有LED灯 ldr r1,=0x00 str r1,[r0] ldr r0,=pSRCPND ; 清0中断源悬挂寄存器EINT3位 mov r1,#8 str r1,[r0] ldr r0,=pINTPND ; 清0中断悬挂寄存器EINT3位 str r1,[r0] ldmfd sp!,{r0,r1,pc}; 返回‘wait_server b.’下条指令

实验目的

掌握ARM处理器的中断处理机制及中断响应过程。 掌握S3C2440的中断控制寄存器的使用及中断处理程序

编程。

掌握基于嵌入式裸机系统的中断应用程序设计实现

实验内容

一、验证实验

输入并调试实验教程提供的参考程序,实现当按下与实 验箱外部中断3引脚EINT3连接的按键时,使8位LED中的低 4位LED依次点亮后再熄灭。

nCS_SEG1

D31~D0

EINT3(GPF3)

将INT3接之以按键 开关作为中断信号 输入端,每按一次 按键产生一次中断 请求,中断处理程 序使低4位LED逐个 点亮然后再熄灭。

S3C2440外部中断操作

1

20100831

编写:小龍

吧把 INTPND 中相应位置 1,所以同一时间只有一位是 1。也就是说前面的寄存 器置 1 是表示发生了,只有 INTPND 置 1,CPU 才会处理。 INTOFFSET :用来表示 INTPND 中哪一位置 1 了,好让你查询,普 通中断跳转时查询用。清除 INTPND、SRCPND 时自动清除。 4.各寄存器关系:

5

20100831 case 0x2000: if(rGPBDAT & 0x80) LED3_ON(); else LED3_OFF(); break; case 0x4000: if(rGPBDAT & 0x100) LED4_ON(); else LED4_OFF(); break; case 0x8000: LED_ON(); break; case 0x80000: LED_OFF(); break;

下面看图说明: 5.中断过程。 a 如果是不带子中断的内部中断:发生后 SRCPND 相应位置 1,如果没有被 INTMSK 屏蔽,那么等待进一步处理。 b 如果是带子中断的内部中断:发生后 SUBSRCPND 相应位置 1,如果没有被 INTSUBMSK 屏蔽,那么 SRCPND 相应位置 1,等待进一步处理,几个 SUBSRCPND 可能对应同一个 SRCPND,对应表如下: SRCPND SUBSRCPND INT_UART0 INT_RXD0,INT_TXD0,INT_ERR0 INT_UART1 INT_RXD1,INT_TXD1,INT_ERR1 INT_UART2 INT_RXD2,INT_TXD2,INT_ERR2 INT_ADC INT_ADC_S, INT_TC INT_CAM INT_CAM_C, INT_CAM_P INT_WDT_AC97 INT_WDT, INT_AC97

mdk下2440裸机中断

MDK下S3C2440裸机中断,断断续续将耗费了我将近了一个月的时间,在贵师大图书馆里几乎翻遍了有关图书,有关这方面的介绍寥寥而过,想必出书的人也未必弄得清楚。

网上的资料也五花八门,有些说MDK自带的2440的启动代码有误(确实跟2410的启动代码不同,但经过这段时间的验证,启动代码绝对没有任何问题);有些说必须内存映射到正确的地址,才可以进入相应异常(从NORFLASH启动绝对可以进入IRQ中断);大部分在书写中断服务程序时,__irq关键字都放在函数名的前面(ADS编译器__irq关键之放置在函数名前面,但MDK必须将__irq关键字放在函数最末端);有些说必须修改2440启动代码才能进入中断(没有对启动代码做任何修改,实现了IRQ中断)……在这些一大堆乱七八糟的资料中,我差点都放弃了ARM的学习。

为了实现IRQ中断而很吃力地学习了ARM汇编,试着修改2440的启动代码;学习了内存管理,试着映射异常向量的地址;如今回过头去看,能挺过来挺欣慰的。

为实现简单IRQ中断其实很简单的,真是踏破铁鞋无觅处,得来全不费功夫。

以下是关键的几点程序说明,希望对后面学习的朋友,有些帮助。

void irq_init() //irq初始化,这个函数其实比较简单,适当看看2440PDF就应该能设定寄存器了{GPFCON = 0xaaaa;SRCPND = 0x17;INTMSK &= ~(0x17);INTPND = 0x17;EINTPEND =(1<<4);__asm{nop}EINTMASK &=~(1<<4);__asm{nop}EXTINT0 = 0x0;}//这是个很关键的函数,但其实也简单中断服务函数照着这个形式写就应该没能进入IRQ中断了。

void IRQ_Handler(void) __irq //irq中断函数{int j=0;__asm{nop};__asm{nop};j= INTOFFSET;SRCPND = SRCPND | 0x17;INTPND = INTPND | 0x17;switch(j){case 0:irq_ent0();//为中断0break;case 1:irq_ent1();//外中断1break;case 2:irq_ent2();//外中断2break;case 4:irq_ent4();//外中断4irq_init();break;}}以上两个函数式实现IQR中断的关键函数,能弄清楚上面的两个函数,IRQ中断应该就没什么大问题了。

S3C2440源未决寄存器SRCPND和中断未决寄存器INTPND以及外部中断未决寄存器EINTPEND分析

S3C2440中断分析中断源未决寄存器(SRCPND)和中断未决寄存器(INTPND)以及外部中断未决寄存器(EINTPEND)分析2013年04月13日飞梦缘整理中断源未决寄存器SRCPND寄存器由32位构成,每一位与一个中断请求信号相关联。

当某个中断源请求中断服务时,SRCPND寄存器中相应位被置为1,即首先在源未决寄存器中做登记,因此该寄存器记录了哪个中断源的请求在等待处理。

注意SRCPND寄存器的每一位由中断源自动设置,而不管中断屏蔽寄存器中对应的位是否被屏蔽,此外,SRCPND寄存器也不受中断控制器的优先级逻辑影响。

当多个中断源提出中断请求后,SRCPND寄存器中相应位均被置为1,然后裁决逻辑基于优先级寄存器来进行处理,选中优先级最高的中断请求,对中断未决寄存器中相应的位设置为1。

注意:INTPND寄存器中只有一位可以被设置为1,如果该中断被屏蔽,SRCPND寄存器中相对应的位被设置为1,但不会导致INTPND寄存器中相应位也被设置为1,SRCPND寄存器是可读可写的,在某个特定中断源的中断服务程序中,SRCPND寄存器的相应位必须被清除,从而保证能收到同一中断源的下一次中断请求,如果从中断服务程序返回时没有清除相应的未决位,中断控制器会误以为该中断源产生了另一个中断请求,换句话说,如果SRCPND寄存器的某位始终设置为1,则被认为始终有一个与该位相对应的中断源,即一个有效的中断请求等待处理,何时进行清除相应的未决位取决于用户需求,如果想在中断服务程序中,再收到相同的中断源提出的另一个有效的中断请求,则应该首先清除相应的未决位,用户可以通过写数据“1”到SRCPND寄存器来清除相应的未决位,数据位为“1”表示该位置的未决位将被清除,而0表示该位置的未决位保持不变。

———————————————————————————————————————————————————前几天把外部中断基本搞好了,但对几个中断寄存器的具体含义和区别不是很了解。

S3C2440按键中断LED控制(详细注解)

按键与LED灯,四个中断控制四个灯LED引脚连接按键引脚连接://===================================================================== =// 开发板:GT2440// 工程名称:KEY_EINT// 功能描述:外部中断0 2 11 19 控制四个LED小灯//===================================================================== =/******************************************************************************4 个用户按键四个输入引脚:EINT0 -----( GPF0 )----INPUT---K1EINT2 -----( GPF2 )----INPUT---K2EINT11 -----( GPG3 )----INPUT---K3EINT19 -----( GPG11 )----INPUT---K4******************************************************************************/ #include "def.h"#include "2440addr.h"#include "2440lib.h"#include "string.h"#include "uart.h"#define LED1ON 0xFDE //LED1点亮值为0x7DE(低电平点亮)#define LED2ON 0xFBE#define LED3ON 0xF7E#define LED4ON 0xEFE#define LEDOFF 0xFFF //LED熄灭值为0xFFFvoid __irq EintHandler0(void);void __irq EintHandler2(void);void __irq EintHandler8_23(void);void Main(void){memcpy((unsigned char *)0x0,(unsigned char *)0x30000000,0x1000);SetSysFclk(FCLK_400M); //设置系统时钟400MChangeClockDivider(2, 1); //设置分频1:4:8CalcBusClk(); //计算总线频Uart_Select(0);Uart_Init(0,115200);Uart_Printf("KEY EINT TEST\n");Uart_Printf("Use Eint 0,2,11,19 falling edge\n");rGPBCON = (rGPBCON | 0xFFFFFFF) & 0xFFFd57FC; //GPB5--GPB8设置为output rGPBUP = rGPBUP & 0xFE1F; //使能GPB5 6 7 8上拉电阻rGPBDAT = 0x7FE; //GPB5 6 7 8位初始化为1/***********************************************************//GPF0 GPF2设置为EINT[0],EINT[2] 10 = EINT[2] 10 = EINT[0]//设置GPGCON的3,11为中断功能,分别对应EINT[11] EINT[19]*************************************************************/rGPFCON = (rGPFCON|0xFFFF)&0xFFFFFFEE;rGPGCON = (rGPGCON|0xFFFFFFFF)&0xFFBFFFBF;/*************************************************************** START:外部中断控制寄存器3位一个设置触发沿, 设置外部中断0 ,2下降沿触发外部中断控制寄存器3位设置一个触发沿, 设置外部中断11下降沿触发外部中断控制寄存器3位设置一个触发沿, 设置外部中断19下降沿触发01x = 下降沿触发*****************************************************************/ rEXTINT0 &= ~(7<<0 | 7<<8 );rEXTINT0 |= (2<<0 | 2<<8) ;rEXTINT1 &= ~(7<<12 );rEXTINT1 |= (2<<12) ;rEXTINT2 &= ~(7<<12 );rEXTINT2 |= (2<<12) ;/*************************************************************** END*****************************************************************//********************************************************//外部中断0~3保留为0 不用使能EINTPEND和EINTMASK rEINTPEND |= (1<<0|1<<2); //clear eint 4 rEINTMASK &= ~(1<<0|1<<2); //enable eint************************************************************//********************************************************//外部中断11,19需要对EINTPEND(外部中断挂起寄存器)清零并对EINTMASK(外部中断屏蔽寄存器)清零使能EINTPEND写1清零使能中断,EINTMASK清零使能中断************************************************************/ rEINTPEND |= (1<<11|1<<19);rEINTMASK &= ~(1<<11|1<<19);/***********************************************************清源挂起(SRCPND)寄存器和中断挂起(INTPND)寄存器,可以直接操作寄存器这两个函数在2440addr.h中定义*************************************************************/ ClearPending(BIT_EINT0);ClearPending(BIT_EINT2);ClearPending(BIT_EINT8_23);/***********************************************************pISR_EINT0,2中断的入口地址,定义在2440addr.inc中2440addr.inc文件内定义了用于汇编的s3c2440寄存器变量和地址*************************************************************/ pISR_EINT0 =(unsigned)EintHandler0;pISR_EINT2 =(unsigned)EintHandler2;pISR_EINT8_23 =(unsigned)EintHandler8_23;/*********************************************************** 使能或禁止中断,这是个宏定义,其原型为rINTMSK &= ~(bit)这里的操作就是取消了屏蔽,中断就开始了*************************************************************/ EnableIrq(BIT_EINT0);EnableIrq(BIT_EINT2);EnableIrq(BIT_EINT8_23);while(1);}//外部中断0,服务函数void __irq EintHandler0(void){if(rINTPND==BIT_EINT0){ClearPending(BIT_EINT0);Uart_Printf("KEY To LED1 ON \n");rGPBDAT = LED1ON;Delay(500);rGPBDAT = LEDOFF;}}//外部中断2,服务函数void __irq EintHandler2(void){if(rINTPND==BIT_EINT2){ClearPending(BIT_EINT2);Uart_Printf("KEY To LED2 ON \n");rGPBDAT = LED2ON;Delay(500);rGPBDAT = LEDOFF;}}//外部中断11,19服务函数void __irq EintHandler8_23(void){if(rINTPND==BIT_EINT8_23){ClearPending(BIT_EINT8_23);if(rEINTPEND&(1<<11)){Uart_Printf("KEY To LED3 ON \n");rGPBDAT = LED3ON;Delay(500);rGPBDAT = LEDOFF;rEINTPEND |= 1<< 11;//写1清零该位}if(rEINTPEND&(1<<19)){Uart_Printf("KEY To LED4 ON \n");rGPBDAT = LED4ON;Delay(500);rGPBDAT = LEDOFF;rEINTPEND |= 1<< 19;//写1清零该位}}}。

S3C2440的中断控制

1.3.中断的作用

中断在系统中具有十分重要的作用,应该说整个系统都是依靠中断驱动起来的,中断的 主要作用如下:

1) CPU 与外部设备并行工作 图 9.1 是 CPU 与一台外部设备并行工作的时间关系图。现行程序和中断服务程序都是在 同一个 CPU 上执行的,因此,他们必须串行执行。但是,外部设备工作与 CPU 执行现行程序 或执行中断服务程序可以同时进行,使各自的效率得到充分发挥。

ARM 体系结构与编程参考资料 V1.01

S3C2440 的中断控制

1. 中断体系结构

1.1.概述

CPU 在正常执行程序的过程中,CPU 运行过程中,突然发生了一些不可预期的事件,比 如某个按键按下、串口收到新数据、USB 接口插入设备。但是 CPU 如何获得这些信息?主要 有以下两种方法: � 查询方式:程序循环查询各个设备的状态并作出相应的反应。这种方式显现简单,常用

了。 采用中断方式,当出现例外事件时,就向 CPU 发出中断服务请求,CPU 可以立即停止执

行现行程序,及时处理这些例外事件,避免发生计算错误,或造成更大的损失。

3) 实现实时处理 在实时控制系统中,处理机必须及时响应外部请求,及时处理,否则,可能丢失数据或 造成无法弥补的损失。例如,在过程控制中,当出现温度过高、压力过大的情况时,处理机 只有通过中断系统才能及时响应并给予处理。

运行时间

图 9.1 CPU 与外部设备并行工作的时间关系

处理器 外设设备

系统程序

中断响应

中断返回

中断处理

系统程序

中断响应

中断返回

中断处理

中断请求

中断请求

正常工作

正常工作

正常工作

当 CPU 在执行现行程序中启动外部设备之后,不需要象程序控制方式那样反复查询外部 设备的状态,而能够与外部设备并行工作。当外部设备的数据准备就绪后,主动向 CPU 发出 中断请求。CPU 接到外部设备的中断请求后,如果没有更加紧急的任务(如 DMA 服务等), 就暂停正在执行的现行程序,转去执行中断服务程序,为外部设备服务。当中断服务完成之 后,再返回到原先的现行程序中继续执行。

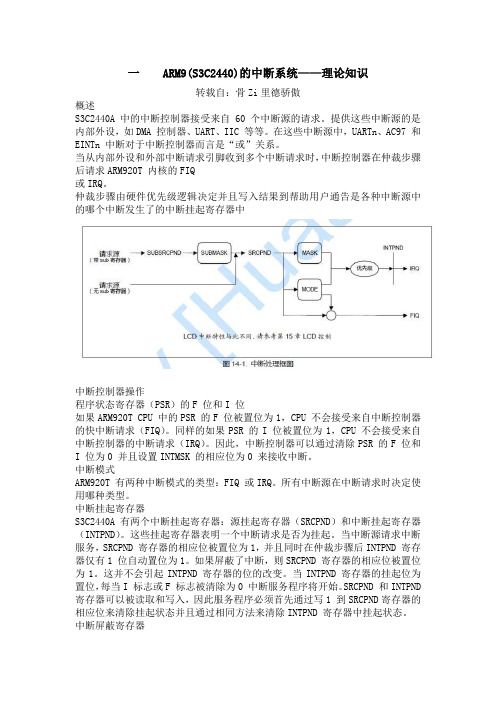

ARM9(S3C2440)之一中断系统理论知识

一 ARM9(S3C2440)的中断系统——理论知识转载自:骨Zi里德骄傲概述S3C2440A 中的中断控制器接受来自60 个中断源的请求。

提供这些中断源的是内部外设,如DMA 控制器、UART、IIC 等等。

在这些中断源中,UARTn、AC97 和EINTn 中断对于中断控制器而言是“或”关系。

当从内部外设和外部中断请求引脚收到多个中断请求时,中断控制器在仲裁步骤后请求ARM920T 内核的FIQ或IRQ。

仲裁步骤由硬件优先级逻辑决定并且写入结果到帮助用户通告是各种中断源中的哪个中断发生了的中断挂起寄存器中中断控制器操作程序状态寄存器(PSR)的F 位和I 位如果ARM920T CPU 中的PSR 的F 位被置位为1,CPU 不会接受来自中断控制器的快中断请求(FIQ)。

同样的如果PSR 的I 位被置位为1,CPU 不会接受来自中断控制器的中断请求(IRQ)。

因此,中断控制器可以通过清除PSR 的F 位和I 位为0 并且设置INTMSK 的相应位为0 来接收中断。

中断模式ARM920T 有两种中断模式的类型:FIQ 或IRQ。

所有中断源在中断请求时决定使用哪种类型。

中断挂起寄存器S3C2440A 有两个中断挂起寄存器:源挂起寄存器(SRCPND)和中断挂起寄存器(INTPND)。

这些挂起寄存器表明一个中断请求是否为挂起。

当中断源请求中断服务,SRCPND 寄存器的相应位被置位为1,并且同时在仲裁步骤后INTPND 寄存器仅有1 位自动置位为1。

如果屏蔽了中断,则SRCPND 寄存器的相应位被置位为1。

这并不会引起INTPND 寄存器的位的改变。

当INTPND 寄存器的挂起位为置位,每当I 标志或F 标志被清除为0 中断服务程序将开始。

SRCPND 和INTPND 寄存器可以被读取和写入,因此服务程序必须首先通过写1 到SRCPND寄存器的相应位来清除挂起状态并且通过相同方法来清除INTPND 寄存器中挂起状态。

ARM_S3C2440中断分析

ARM S3C2440中断分析1.什么是中断所谓中断,是指CPU在正常运行程序时,由于内部/外部事件或由程序预先安排的事件,引起CPU中断正在运行的程序,而转到为内部/外部事件或为预先安排的事件服务的中断程序中去,服务完毕,再返回去执行刚才被中断的程序。

2.什么是中断优先级中断优先级是指,中断源被响应和处理的优先等级。

设置优先级的目的是为了在有多个中断源同时发出中断请求时,CPU能够按照预定的顺序(如:按事件的轻重缓急处理)进行响应并处理。

3.什么是中断嵌套中断嵌套是指当CPU正在处理某个中断源即正在执行中断服务程序时,会出现优先级更高的中断源申请中断,为了使更急的中断源及时得到服务,需要暂时中断(挂起)当前正在执行的级别较低的中断服务程序,去处理更高级别的中断源,待执行完毕后再返回来执行低优先级的中断服务程序。

但中断级别低的中断源不能中断级别高的中断服务,这就是中断嵌套,并且称这种中断嵌套方式为完全嵌套方式。

4.什么是中断向量中断向量是中断服务程序的入口地址,中断向量一般是固定的,我们需要把我们写好的中断服务程序(ISR)的入口地址写道中断向量表中,这样在发生中断时,CPU就会自动跳转到中断向量表中找到它要执行的中断服务程序了。

5.什么是硬中断,什么是软中断硬中断是由外部事件引起的因此具有随机性和突发性;软中断是执行中断指令产生的,无面外部施加中断请求信号,因此中断的发生不是随机的而是由程序安排好的。

S3C2440/S3C2410中断体系结构:6.ARM体系 CPU的7种工作模式:·用户模式(usr): ARM处理器正常的程序执行状态·快速中断模式(fiq): 用于高速数据传输或通道处理·中断模式(irq):用于通用的中断处理·管理模式(svc):操作系统使用的保护模式·数据访问终止模式(abt): 当数据或指令预取时进入该模式,可用于虚拟存储及存储保护·系统模式(sys):运行具有特权操作系统任务·未定义指令中止模式(und): 当为定义的指令执行时进入该模式,可用于支持硬件协处理的软件仿真可以通过软件来进行模式切换,或者发生各类中断,异常时CPU自动进入相应的模式。

2440的中断知识

S3C2440A 中的中断控制器可以从60 个中断源接收中断请求。

这些中断源由内部的外围器件提供的,例如DMA 控制器、UART 、IIC 等。

在这些中断源中,AC97 和外部中断 UARTn 、EINTn 对于中断控制器来说是或逻辑。

当接收来自内部外设和外部中断请求引脚的多个中断请求时,在仲裁过程后中断控制器请求ARM920T 的FIR 或IRQ 中断。

1.0 程序状态寄存器(PSR )的F 位和L 位如果PSR的F 位置1 ,CPU 不能接收FIR请求,PSR的 L 位置1,CPU 不能接收IRQ请求。

如果要接受中断,则相应位清零并且INTMSK的相应位也清零。

1.1 中断模式ARM920T 有两个类型的中断模式:FIR 和IRQ 。

所有的中断源决定了哪种模式的中断请求。

1.2 中断挂起寄存器两个中断挂起寄存器SRCPND (源挂起寄存器)和INTPND(中断挂起寄存器),当中断源发起中断请求时,SRCPND 寄存器相应位被置位,当允许中断请求时,INTPND 相应位会被置位,否则INTPND 相应位不会被置位。

对寄存器清0 时,分别向他们相应位写入 1.1.3中断屏蔽寄存器:相应位置1时,中断被屏蔽,如果为0则正常服务中断。

当某位为 1 时,中断请求时,SRCPND 里相应位会被置1,但不会置INTPND 的相应位。

1.4中断源:60 个中断源(具体参见S3C2440手册)1.5. 中断次级源:15 个子中断源(具体参见S3C2440手册)1.6中断优先级生成模块和中断优先级2.0 中断特殊功能寄存器:2.1源挂起寄存器(SRCPND )寄存器由32 位数据组成,每位代表相应的一个中断,当中断发生的时候,无论是否屏蔽了这个中断,SRCPND 相应位都会自动置 1 ,表明此中断发生中断请求,如果此中断没有被屏蔽,则程序响应中断,注意:在进入中断服务程序中时要清除SRCPND 相应位。

2.2中断挂起寄存器(INTPND )寄存器由32 位数据组成,每位代表相应的中断,当INTPND 寄存器在优先级逻辑后被定位了,那么它每次只有一位能被设置为 1 ,并且产生IRQ 到CPU 。

S3C2440启动代码2440init.s彻底解析

S3C2440启动代码2440init.s彻底解析2440可以选择nand启动和nor启动,这两者之间的关系通过⼀个按键来选择这个OM0有何⽞机,在数据⼿册中有这么⼀段可以看到,只要将OM1接地,那么通过OM0选择1或选择0就可以选择NAND启动或者16位宽RAM启动了(当然,还得设置⼀些东西,下⾯就说),Nanaflash启动经历的过程相当于⾸先,2440⾃动从nand⾥⾯读取4K的代码,这4K代码将nand⾥⾯的数据拷贝到ram中,然后跳转到ram中执⾏代码,为什么是4K,因为2440.s的启动代码需要包含⼏个⽂件2440addr.inc包含2440内部寄存器地址Memcfg.inc包含2440各个bank的内存配置数据Option.inc包含2440的各种时钟配置代码Nand.c包含nanaflash的读写函数好了,分析开始;REFRESH寄存器[22]bit : 0- auto refresh; 1 - self refreshBIT_SELFREFRESH EQU (1<<22) ;⽤于节电模式中,SDRAM⾃动刷新;处理器模式常量: CPSR寄存器的后5位决定⽬前处理器模式 M[4:0]USERMODE EQU 0x10FIQMODE EQU 0x11IRQMODE EQU 0x12SVCMODE EQU 0x13ABORTMODE EQU 0x17UNDEFMODE EQU 0x1bMODEMASK EQU 0x1f ;M[4:0]//模式计算掩码NOINT EQU 0xc0 //除去模式之后的剩余值CPSR的说明;定义处理器各模式下堆栈地址常量UserStack EQU (_STACK_BASEADDRESS-0x3800) ;0x33ff4800 ~ _STACK_BASEADDRESS定义在option.inc中SVCStack EQU (_STACK_BASEADDRESS-0x2800) ;0x33ff5800 ~UndefStack EQU (_STACK_BASEADDRESS-0x2400) ;0x33ff5c00 ~AbortStack EQU (_STACK_BASEADDRESS-0x2000) ;0x33ff6000 ~IRQStack EQU (_STACK_BASEADDRESS-0x1000) ;0x33ff7000 ~FIQStack EQU (_STACK_BASEADDRESS-0x0) ;0x33ff8000 ~剩下的请查看以下代码;汇编不能使⽤include包含头⽂件,所有⽤Get;汇编也不认识*.h ⽂件,所有只能⽤*.incGET option.inc ;定义芯⽚相关的配置GET memcfg.inc ;定义存储器配置GET 2440addr.inc ;定义了寄存器符号;REFRESH寄存器[22]bit : 0- auto refresh; 1 - self refreshBIT_SELFREFRESH EQU (1<<22) ;⽤于节电模式中,SDRAM⾃动刷新;处理器模式常量: CPSR寄存器的后5位决定⽬前处理器模式 M[4:0]USERMODE EQU 0x10FIQMODE EQU 0x11IRQMODE EQU 0x12SVCMODE EQU 0x13ABORTMODE EQU 0x17UNDEFMODE EQU 0x1bMODEMASK EQU 0x1f ;M[4:0]NOINT EQU 0xc0;定义处理器各模式下堆栈地址常量UserStack EQU (_STACK_BASEADDRESS-0x3800) ;0x33ff4800 ~ _STACK_BASEADDRESS定义在option.inc中SVCStack EQU (_STACK_BASEADDRESS-0x2800) ;0x33ff5800 ~UndefStack EQU (_STACK_BASEADDRESS-0x2400) ;0x33ff5c00 ~AbortStack EQU (_STACK_BASEADDRESS-0x2000) ;0x33ff6000 ~IRQStack EQU (_STACK_BASEADDRESS-0x1000) ;0x33ff7000 ~FIQStack EQU (_STACK_BASEADDRESS-0x0) ;0x33ff8000 ~;arm处理器有两种⼯作状态 1.arm:32位这种⼯作状态下执⾏字对准的arm指令 2.Thumb:16位这种⼯作状;态执⾏半字对准的Thumb指令;因为处理器分为16位 32位两种⼯作状态程序的编译器也是分16位和32两种编译⽅式所以下⾯的程序⽤;于根据处理器⼯作状态确定编译器编译⽅式;code16伪指令指⽰汇编编译器后⾯的指令为16位的thumb指令;code32伪指令指⽰汇编编译器后⾯的指令为32位的arm指令;;Arm上电时处于ARM状态,故⽆论指令为ARM集或Thumb集,都先强制成ARM集,待init.s初始化完成后;再根据⽤户的编译配置转换成相应的指令模式。

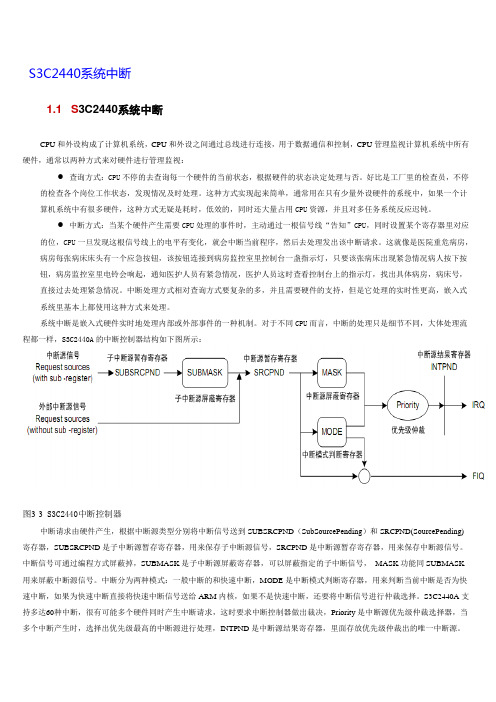

S3C2440系统中断

S3C2440系统中断1.1S3C2440系统中断CPU和外设构成了计算机系统,CPU和外设之间通过总线进行连接,用于数据通信和控制,CPU管理监视计算机系统中所有硬件,通常以两种方式来对硬件进行管理监视:●查询方式:CPU不停的去查询每一个硬件的当前状态,根据硬件的状态决定处理与否。

好比是工厂里的检查员,不停的检查各个岗位工作状态,发现情况及时处理。

这种方式实现起来简单,通常用在只有少量外设硬件的系统中,如果一个计算机系统中有很多硬件,这种方式无疑是耗时,低效的,同时还大量占用CPU资源,并且对多任务系统反应迟钝。

●中断方式:当某个硬件产生需要CPU处理的事件时,主动通过一根信号线“告知”CPU,同时设置某个寄存器里对应的位,CPU一旦发现这根信号线上的电平有变化,就会中断当前程序,然后去处理发出该中断请求。

这就像是医院重危病房,病房每张病床床头有一个应急按钮,该按钮连接到病房监控室里控制台一盏指示灯,只要该张病床出现紧急情况病人按下按钮,病房监控室里电铃会响起,通知医护人员有紧急情况,医护人员这时查看控制台上的指示灯,找出具体病房,病床号,直接过去处理紧急情况。

中断处理方式相对查询方式要复杂的多,并且需要硬件的支持,但是它处理的实时性更高,嵌入式系统里基本上都使用这种方式来处理。

系统中断是嵌入式硬件实时地处理内部或外部事件的一种机制。

对于不同CPU而言,中断的处理只是细节不同,大体处理流程都一样,S3C2440A的中断控制器结构如下图所示:图3-3 S3C2440中断控制器中断请求由硬件产生,根据中断源类型分别将中断信号送到SUBSRCPND(SubSourcePendi ng)和SRCPND(SourcePending)寄存器,SUBSRCPND是子中断源暂存寄存器,用来保存子中断源信号,SRCPND是中断源暂存寄存器,用来保存中断源信号。

中断信号可通过编程方式屏蔽掉,SUBMASK是子中断源屏蔽寄存器,可以屏蔽指定的子中断信号,MASK功能同SUBMASK 用来屏蔽中断源信号。

S3C2440中断编程相关知识复习

中断处理过程

一次完整的中断过程由中断请求、中断响应和中 断处理三个阶段组成。 ◎中断请求:是由中断源发出的并送给CPU的控 ◎中断请求:是由中断源发出的并送给CPU的控 制信号,由中断源设备通过将接口卡上的中断触 发器置“ 发器置“1”完成。 接口卡上还有一个中断屏蔽触发器 中断屏蔽触发器置“ 中断屏蔽触发器置“1”,表示要屏蔽该设备的中 断请求; 中断屏蔽触发器置“ 中断屏蔽触发器置“0”,表示允许该设备发出中 断请求;

中断处理过程

◎中断处理过程: 关中断 保存断点、保护现场 (区别断点和现场) 判中断源转中断服务 开中断 执行中断服务程序 关中断 恢复现场、恢复断点(区别断点和现场) 开中断 返回断点

S3C2440的中断体系 S3C2440的中断体系

ARM体系CPU的 ARM体系CPU的7种工作模式 两种工作状态(只需关心ARM状态即可) 两种工作状态(只需关心ARM状态即可) 31个通用寄存器和6个程序状态寄存器 31个通用寄存器和6 ARM920T CPU中断过程,主要关心 CPU中断过程,主要关心 ARM920T CPU在中断响应后自动完成哪些 CPU在中断响应后自动完成哪些 工作。

S3C2440处理器的中断 S3C2440处理器的中断

中断的概念

中断是指在计算机执行期间,系统内发生 任何非寻常的或非预期的急需处理事件, 使得CPU暂时中断当前正在执行的程序而转 使得CPU暂时中断当前正在执行的程序而转 去执行相应的时间处理程序。待处理完毕 后又返回原来被中断处继续执行或调度新 的进程执行的过程。

中断处理过程

◎中断响应:当CPU接到中断请求,若满足下列 中断响应:当CPU接到中断请求,若满足下列 条件,就会响应中断。 响应中断的条件: ※允许中断触发器为“1”状态; 允许中断触发器为“ ※ CPU结束了一条指令的执行过程; CPU结束了一条指令的执行过程; ※新请求的中断优先级较高; 中断响应要进行的工作: 保存程序计数器PC的内容或许包括程序状态字的 保存程序计数器PC的内容或许包括程序状态字的 内容到堆栈(中断隐指令)

S3C2440的中断控制

系统程序 处理器 中断响应 中断处理 中断请求 外设设备 正常工作 中断返回

系统程序 中断响应 中断返回 中断处理 中断请求 正常工作 正常工作

当 CPU 在执行现行程序中启动外部设备之后, 不需要象程序控制方式那样反复查询外部 设备的状态,而能够与外部设备并行工作。当外部设备的数据准备就绪后,主动向 CPU 发出 中断请求。CPU 接到外部设备的中断请求后,如果没有更加紧急的任务(如 DMA 服务等), 就暂停正在执行的现行程序,转去执行中断服务程序,为外部设备服务。当中断服务完成之 后,再返回到原先的现行程序中继续执行。 当有多台外部设备需要同时工作时, CPU 可以在不同时刻根据需要分别启动这些外部设 备, 被启动的外部设备能够与 CPU 分别同时独立工作。 当某一台外部设备的数据准备就绪时, 就向 CPU 发出中断服务请求。如果有多台外部设备同时要求中断服务,CPU 能够根据这些外 部设备的优先级从高到低分别响应这些中断请求,为外部设备服务。 2) 能够处理例外事件 计算机在运行过程中,可能发生例外事件,如电源掉电、硬件故障、运算溢出、地址越 界、非法指令等。依靠程序控制方式根本不可能处理好这些例外事件,因为 CPU 不可能一直 不间断地查询是否有电源掉电,是否发生了硬件故障,如果这样,计算机就什么事也干不了

RTC 闹钟中断

ARM 体系结构与编程参考资料 V1.01

INT_SPI1/[29] INT_ERR0/SUBSRCPND[2] INT_UART0/[28] INT_IIC/[27] INT_USBH/[26] INT_USBD/[25] INT_NFCON/[24] INT_UART1/[23] INT_SPI0/[22] INT_SDI/[21] INT_DMA3/[20] INT_DMA2/[19] INT_DMA1/[18] INT_DMA0/[17] INT_LCD/[16] INT_UART2/[15] INT_TIMER4/[14] INT_TIMER3/[13] INT_TIMER2/[12] INT_TIMER1/[11] INT_TIMER0/[10] INT_WDT_AC97/[9] INT_TICK/[8] nBATT_FLT/[7] INT_CAM/[6] INT_CAM_P/SUBSRCPND[12] INT_CAM_C/SUBSRCPND[11] EINT23/EINTPND[23] EINT22/EINTPND[22] EINT21/EINTPND[21] EINT20/EINTPND[20] 外部中断 EINT8_23/[5] EINT19/EINTPND[19] EINT18/EINTPND[18] EINT17/EINTPND[17] EINT16/EINTPND[16] EINT15/EINTPND[15] EINT14/EINTPND[14] INT_AC97/SUBSRCPND[14] INT_WDT/SUBSRCPND[13] INT_ERR2/SUBSRCPND[8] INT_TXD2/SUBSRCPND[7] INT_RXD2/SUBSRCPND[6] INT_ERR1/SUBSRCPND[5] INT_TXD1/SUBSRCPND[4] INT_RXD1/SUBSRCPND[3] INT_TXD0/SUBSRCPND[1] INT_RXD0/SUBSRCPND[0]

S3C2410中断处理

S3C2410中断处理在介绍2410的中断处理之前,我们不得不先看看先把ARM的异常向量表(Exception Vectors),下面对异常向量表(Exception Vectors),做一个简单的介绍:ARM的异常向量表一般存放在0x00000000处,ARM920T能处理有7个异常,他们分别是:Reset(复位),Undefined instruction,Software Interrupt,Abort 舍弃(prefetch),Abort (data),IRQ,FIQ下面是系统源码片段:上面这部分片段一般出现在一个名叫“head.s”的汇编文件里,“b Handle_Reset”这条语句就是系统上电之后运行的第一条语句。

因为上电后CPU会从SDRAM的0x00000000处取第一条指令并执行。

上所示会放在0x00000000地址处,以后每当系统有异常出现,则CPU会根据异常号,从内存0x00000000地址处开始查中断向量表并做相应的处理,比如系统触发了一个IRQ异常,IRQ为6号异常,则CPU将把PC指向0x00000000地址处运行,调用中断服务程序。

S3C2410芯片可以接收56个中断源,产生32个中断请求。

这些中断源来自两部分:内部外设,如DMA控制器,UA RT等和外部引脚线。

A RM920T具有两种类型的中断模式:FIQ和IRQ,通过判定优先级产生IRQ或FIQ中断。

如果在ARM920T的CUP中的PSR(程序状态寄存器)的控制位F位置1,则CPU从中断控制器中不接受FIQ中断,如果在A RM920T的CUP中的PSR (程序状态寄存器)的控制位I位置1,则CPU从中断控制器中不接受IRQ中断,因此中断控制器通过清除F-bit位或I-bit位产生中断。

S3C2410的中断异常处理模块有以下寄存器构成:∙ SRCPND,∙INTMODE,∙INTMSK,∙PRIORITY,∙INTPND,∙INTOFFSET,∙SUBSRCPND,∙INTSUBMSK。

实验5 S3C2440中断实验

interrupt

END

中断处理程序

主程序内与中断相关的初始化程序实现

主程序及中断控制器初始化流程框图

InitStacks

设置IRQ及USER堆栈指针 设置GPF3为EINT3外中断 设置EINT3为上升沿触发

设置中断模式寄存器 设置二级向量表EINT3表项

mrs r0,cpsr bic r0,r0,#MODEMASK|NOINT orr r1,r0,#IRQMODE

8D 锁 存

总

驱

线

nCS_SEG2 动

驱

8D

动

锁 存

驱

nCS_SEG1 动

8D

锁

存

驱

动

将INT3接之以按键 开关作为中断信号 输入端,每按一次 按键产生一次中断 请求,中断处理程 序使低4位LED逐个 点亮然后再熄灭。

S3C2440中断响应流程图解

注:在响应中断请求之前需要构建好异常向量表和二级中断向量表 (1)某IRQ中断源发出中断请求 (2)CPU自动转移到异常向量表内地址0x018去运行。 (3)运行地址0x018中存放的跳转指令,转移到用户编写的中断源识别程序段IsrIRQ。 (4)寻址二级向量表内HandleXXX地址单元获取向量IsrXXX(地址)并将其置入PC。 (5)跟随PC内容转移到起始地址IsrXXX对应的中断处理程序运行。

PC=0x00000018

用. 户主程序 . 指令i 指令i+1

.

.

① 外设经序号为XXX的中 断源向CPU发中断请求并 触发IRQ类型异常。

⑥中断返回

二级中断向量表

.

HandleEINT0 (起始地址)

HandleXXX

. IsrEINT0

S3C2440中断代码的深层次分析

S3C2440中断代码的深层次分析在前一段时间分析了ARM异常处理机制的处理方式,分析了在异常产生以后CPU自动完成的相关处理以及程序员应该完成的基本操作。

着重分析了异常代码的返回地址分析已经采用通用代码处理各种异常的可能性。

异常处理的基本过程如下:异常产生(在指令的临界中检测CPU的状态,一般实质在这条指令被执行完成,但是还没有执行下一条指令之前检测)——>;保存状态寄存器,切换状态寄存器,保存LR=PC-4,强制PC跳转到对应异常向量(以上的过程都是CPU自动完成)——》调整返回地址,在栈中保存寄存器,便于恢复寄存器的值——》异常处理函数——》退出异常。

中断处理机制的两种形式:1、采用在中断向量中存储简单的跳转指令,跳转到异常处理函数中,但是这种方式存在的缺点就是跳转指令的范围是有局限性的。

2、采用更新PC值的方法进行,具体的实现形式是在另一个固定地址处(handle_addr)保存对应异常处理函数的地址,然后采用LDR PC [PC, offset],其中offset = handle_addr – vect – 0x08;这种机制只要保证选择的地址恰当就能实现不同距离的跳转。

以上的分析和处理在上一次中已经分析,这次分析中断的处理过程,中断只是异常的一种特殊情况,对异常的处理得到了好的理解,那么对中断的处理也就比较方便了。

在ARM内核中只支持IRQ和IFQ两种类型的中断,但是不同的厂商提供不同类型的中断控制器实现对中断的扩展,使得实际的芯片更加适合我们的使用。

但是中断控制器的差别也使得不同厂商的中断处理也有差别,但是基本的思想是一致的。

S3C2440的中断控制器一个支持60种中断源,基本的实现如上图所示。

S3C2440的UART详解

1、UART原理简介在介绍2440的UART控制器之前,我们首先来了解一下UART的原理UART:Universal Asynchro no us Receiver/Transmitter(通用异步收发送器),用来传输串行数据,发送数据时,CPU将并行数据写入UART,UART按照一定格式在TxD线上串行发出;接收数据时,UART检测到RxD线上的信号,将串行收集放到缓冲区中,CPU即可读取UART获得的这些数据。

UART最精简的连线形式只有3根线,TXD用于发送,RXD用于接收,GND用于提供参考电平。

UART 之间以帧作为数据传输单位,帧由具有完整意义的若干位组成,它包含开始位、数据位、校验位和停止位。

发送数据之前,互相通信的UART之间要约定好数据传输速率(波特率的倒数)、数据的传输格式(多少个数据位、是否使用校验位、奇校验还是偶校验、多少个停止位)。

2、S3C2440 UART的特性S3C2440的通用异步收发器(UART)配有3个独立异步串行I/O(SIO)端口,每个都可以通过产生中断或DMA请求来进行CPU和UART之间的数据传输。

如图1所示:每个UART包含一个波特率发生器、发送器、接收器和一个控制单元,图1 2440UART方框图(带FIFO)波特率发生器可以由PCLK、FCLK/n或UEXTCLK(外部输入时钟)时钟驱动。

UART通过使用系统时钟可以支持最高115.2Kbps的比特率。

如果是使用外部器件提供UEXTCLK的UART,则UART可以运行在更高的速度。

发送器和接收器各包含一个64字节的FIFO和数据移位器。

要发送数据时,先将数据写入到FIFO接着在发送前复制到发送移位器中,随后将数据从发送数据引脚(TXDn)移出;接收数据时,从接收数据引脚(RXDn)移入收到的数据,接着从移位器复制到FIFO。

3、S3C2440 UART的使用对于S3C2440,使用UART之前,首选需要对2440的UART模块进行初始化,需要设置波特率、传输格式(多少个数据位、是否使用校验位、奇校验或偶校验、多少个停止位、是否使用流量控制)、选择所涉及的管脚为UART功能、选择UART通道的工作模式为中断模式或DMA模式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中断详解

1、S3C2440官方手册最权威:

手册是最芯片IP开发者最直接的描述,最准确;但对英文阅读能力要求高、因详细而繁杂;适合参考和深入研究;

另外参考网上相关短文较容易入门,并短文是有套路的:基本是围绕几个较优秀的文章(优秀短文要多研读几遍理解透作者的每个心思)。

2、支持60个中断源:

S3C2440中断控制器总共支持60个中断源(内部外设和外部管脚):详细数下表中Descriptions中的中断源个数正好60;

子中断源分解如下:

注:INT_LCD也有两个中断但没有包含在子中断源寄存器中

3、一种中断源分类方法:

1、独立的外部中断源(EINT0-EINT3):4个;

2、合并的外部中断源(EINT4-EINT23):20个,合并后对应EINT4_7和EINT8_23;

注意:对应的相关寄存器在IO模块中,手册中的做法有点特殊;

3、带子中断的内部中断源:15个中断源,体现为6个bit(INT_WDT_AC97/ INT_CAM/ INT_ADC/ INT_UART2/ INT_UART1/ INT_UART0);

4、不带子中断的内部中断源:21个;

注意:INT_LCD实际对应两个中断源但是没有作为带子中断的内部中断源(如下图手册中有提到,TMD隐蔽!);

综上理解中断过程可以总结为:

4、中断优先级解析:

优秀的SOC对外设中断的处理都比较用心,基本能照顾到用户的各种场景,和LPC2292以及作者工作期间参与开发的一款SOC相比,作者经历到的三款SOC对中断的处理各有千秋(原谅不细说,因为没有必要);

可以总结为易用和特性的平衡,如果极特殊的场景下的实时性得不到满足,那就换个SOC 呗!没有必要使用一款SOC打遍天下,也不可能,而且厂家也没有强迫你呀!

言归正传:

S3C2440A支持60种中断,多个硬件可能同时产生中断请求,由于CPU只能处理一个中断,中断控制器怎么选择出一个最佳的中断,交给ARM内核进行处理呢?中断控制器采用优先级仲裁比较的方式进行选择,找出优先级最高的中断源。

中断控制器将60种中断源分成7组,如下图所示,它类似体育赛事里的比赛方式,所有参赛选手在小组赛PK,选择出小组赛最优秀选手,然后进入决赛阶段和其它小组最优先选择再PK,最后优胜者就是总冠军。

其中ARBITER0~ARBITER5为“小组赛”阶段,中断源信号在各自小组里进行优先级仲裁,选择出最高优先级中断信号,每小组选出的中断信号送到ARBITER6,也就是决赛阶段,选择出最高优先级中断信号,交给ARM内核。

中断信号在7个分组里PK时的优先级是可编程的,通过PRIORITY寄存器进行优先级设置。

如下表(只列出PRIORITY寄存器部分位):

表3-6 中断优先级控制寄存器(PRIORITY)

如果不是极特殊场景要求,我们就让这套机制留着三星自己的开发人员慢慢研究吧!

我们使用默认模式即可!

5、中断服务函数的入口:

重点说下920T内核外中断控制器对各种中断的入口函数处理,如果读者对X86保护模式程序员模型熟悉的话,2440的机制和其有异曲同工之妙!

支持定义的总入口,根据不同中断的编号偏移取得对应的中断服务函数入口。

分享下作者中断函数管理机制:

irq_handler irq_table[IRQ_HANDLE_SIZE];

即使用一个全局变量保存32个向量,根据INTOFFSET寄存器的中断号计算偏移取得入口地址;

这种机制比官网提供的各个中断有固定地址的机制有较大的灵活性,另外要注意Cache一致性的问题(如果遇到bug就是一个隐蔽性很强的bug):注册了中断服务函数就要flushcache。

6、中断模式:

FIQ模式业内认为是鸡肋,就像thumb模式这个大鸡肋一样!

总之一句话:不管、不问、任他去!不要用arm的错误惩罚自己!。