GPIB接口的FPGA实现

基于 FPGA 方案 GPIB 接口的功能测试方法

试、 串查 功 能 测试 。测 试 结 果 证 明 该 基 于 F P GA 方 案 高 速数 据 发 生 器 的 GP I B接 口各 项指 标 符 合 国标 标 准 。该 方 法 可 靠 易

王 术群 ( 西南民族大学电气信息工程 学院, 四川 成都 6 1 0 0 4 1 )

摘 要

讨 论 了一 种 基 于 F P GA 方 案 高速 数 据 发 生 器 的 GP I B接 口 的功 能 测 试 方 法 ,通 过 带 I S A 口的 计 算 机 、 GP I B接 口卡 和

址为 1 0;

( N A T 9 9 1 4 ) , 但 存 在 购 买 困难 , 价 格 昂 贵等 缺 点 。 同时 , 作 为 测 试

3 ) 设置母 线分析仪 : 接 通 电源 , l i n e挡 拨 至 o n , me mo r r y挡

仪 器具 备 GP I B的接 1 : 3, 一般 不需控 、 并查 功 能 , 只需 具有 听 、

“ ” ’ 后第 二 个 字节 ’ 是 发 不 出去 的 , 所 以受 者 功 能正 常 ; 再 单 步 触 发, 相 应 的 逐次 读 到 “ D” 、 “ N ” 。由 此 判断 , 高速 数 据 发 生 器 GP I B

行, 对仪 器 开发 者 有 一 定借 鉴 价 值 。 关键词 : F P G A 方案 , G P I B接 口 , 功能测试 , 传 输速 率 , 地 址

Abs t r a c t

Th i s p ape r di s c u s s es a f u nc t i on a l t es t i n g m e ts e d on t h e F PGA o f hi gh-s p ee d da t a ge ne r  ̄or . T hi s t es t s y s t em i n cl u di n g a c om p ut er wi t h I SA, GPI B i n t e fa r ce ca r d an d s e v er al G PI B i n s t r u me n t m a k e s us e o f di gi t a l o s ci l —

GPIB接口的FPGA实现

NR同Dt_0:NDACt=0:end S2:begin if(ATNIrdy)

next=S3: else next_S2;ANRS=l;

NRFDt-1:NDACt=1:end S3:begin if(~(ATNIrdy))

毫

~

≤: >一~“、 、

f“一i √ ‘~

=::=I≤

=:二“

、:?'

譬芝 ~、一 要乏 <

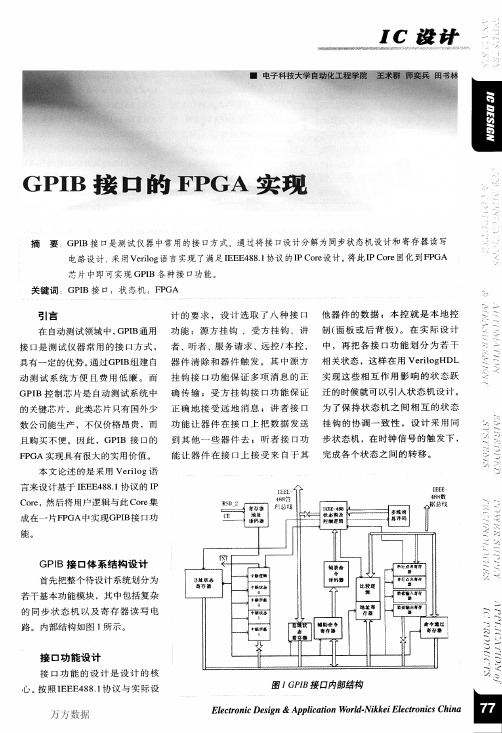

GPlB接口体系结构设计 首先把整个待设计系统划分为 若干基本功能模块,其中包括复杂 的同步状态机以及寄存器读写电 路。内部结构如图1所示。

接口功能设计 接口功能的设计是设计的核 心。按照IEEE488.1协议与实际设

next=S2:

else if(DAV)next=S4; else next=S3;ACRS=1; NRFDt=0;NDACt=1;end S 4: b e g i n i f( (ATN)l(—ATN)&(卅-dy))next=S5; else next=S4:ACDS=1: NRFDt=1;NDACt=l:end S5:begin if( ̄DAV)next=S2;

万方数据

E跆cfro以站DPs辔n&4即矗cn缸DH’砌以办ⅣZ站五百E跆cfro聆站s C娩伽n

j考j三20r。,i=鼻z ~,li≮冀力Z乏0、≮、}-

≥

毫:;

“j,

耄享

3=

暑言 麦}

≮

z’“【,

譬{j i乏童

肇三

童C竣谚

戮掰÷{#黜W¥糟ii俐#龋女#黼im|涨㈣㈣‘㈣㈣m牌㈣“《;蝴|群*瓣㈣#㈣i#镕

else present=next;end

gpib原理

gpib原理GPIB原理GPIB(General Purpose Interface Bus)是一种通用的接口总线标准,广泛应用于科学仪器、测试设备和工业自动化等领域。

本文将介绍GPIB的原理及其应用。

一、GPIB的基本原理GPIB接口采用并行传输方式,由一个主控设备(通常是计算机)和多个从控设备组成。

主控设备通过GPIB控制器与从控设备进行通信。

GPIB总线上的每个设备都有一个唯一的地址,主控设备通过发送命令和查询来控制每个设备的操作。

GPIB总线使用了差分信号传输方式,可以在比较长的距离上传输数据,同时能有效地抵抗噪声干扰。

它采用了令牌传递的控制方式,只有获得令牌的设备才能发送数据,从而确保通信的顺序性和可靠性。

二、GPIB的通信协议GPIB的通信协议是基于SCPI(Standard Commands for Programmable Instruments)命令集的。

SCPI是一种通用的仪器控制语言,可以实现设备之间的互操作性。

在GPIB通信中,主控设备通过发送命令和查询来控制从控设备的操作。

命令可以是设定参数、启动测量等操作,而查询则是获取设备状态、读取测量结果等操作。

从控设备接收到命令后,执行相应的操作并将结果返回给主控设备。

SCPI命令由一系列的关键字和参数组成,通过一定的语法规则进行解析和执行。

主控设备需要了解每个设备支持的命令和参数,才能正确地与设备进行通信。

三、GPIB的应用领域GPIB接口在科学仪器、测试设备和工业自动化等领域有着广泛的应用。

在科学仪器领域,GPIB接口常用于控制实验室中的各种仪器,如示波器、信号发生器、频谱分析仪等。

通过GPIB接口,可以实现对仪器的远程控制和数据采集,提高实验效率。

在测试设备领域,GPIB接口广泛应用于自动测试系统(ATE)。

自动测试系统通常由多个测试设备组成,通过GPIB接口与主控计算机连接。

主控计算机可以发送测试任务到各个测试设备,并读取测试结果,实现高效的自动化测试。

fpga 对gpio的处理

fpga 对gpio的处理

FPGA(现场可编程门阵列)是一种集成电路,它可以通过编程

来实现特定的逻辑功能。

GPIO(通用输入/输出)是指可以用于输入

和输出的通用引脚。

FPGA对GPIO的处理可以从多个角度来看。

首先,FPGA可以通过内部资源来实现GPIO功能。

FPGA内部资

源可以被配置为输入或输出引脚,从而实现GPIO的功能。

这意味着FPGA可以通过编程来控制这些引脚的状态,使其可以作为输入来接

收外部信号,或作为输出来驱动外部设备。

其次,FPGA还可以通过外部接口来处理GPIO。

通常情况下,FPGA会与外部器件(如传感器、执行器等)进行通信,以实现对外

部信号的采集和控制。

这些外部器件通常通过标准接口(如SPI、

I2C、UART等)或专有接口与FPGA连接,从而实现对GPIO的处理。

此外,FPGA还可以通过硬件描述语言(如Verilog、VHDL等)

来描述GPIO的功能和行为。

通过编写相应的代码,可以定义GPIO

的输入输出特性、时序要求、状态转换规则等,从而实现对GPIO的

灵活控制。

最后,FPGA对GPIO的处理还涉及到时序和时钟控制。

由于FPGA是一种可编程的硬件,因此需要考虑时钟分配、时序约束等问题,以确保GPIO的稳定和可靠性。

总的来说,FPGA对GPIO的处理涉及到内部资源的配置、外部

接口的应用、硬件描述语言的编写以及时序和时钟控制等多个方面。

通过合理的设计和编程,FPGA可以灵活、高效地处理GPIO,从而实

现各种复杂的数字逻辑功能。

PCIE接口的FPGA实现方式

E p s 接 口提供 了流控功能 . xr s e 通过流控 . 发送方 向可 以确保在接收Байду номын сангаас 有足够 的缓存 时进行数据发送。

X LN CI x rs IIX P pe s结 构 图 E

数据链路层 ( a i yr 于传输 层和物理 层之间 . 一层 D t L kL e) a n a 介 这 主要提供了 Ln ik管理和数据完整性校验 . 包括错误检测和纠正。发送 方 向, 数据链路层 接收来 自传输层 的数据 , 添加 1 P序列号 。 并 ’ L 同时添 加 Ln RC, ikC 再将报文送入物 理层 。 在送入 物理层 的同时 . 该层会 复 制报 文 , 并将报文保存 到重试 缓存 ( e yB f r 中 , 无效 的报文会 R t u e) 但 r f 从该缓存 中删除。接收方向较简单 , 该层会接收来 自物理层的任何数 据。

21 年 3 02 第2 期

科技 一向导

◇ 信息技术◇

P I 口的 F G C E接 P A实现方式

于 佳

( 中央 电视 台

中国

北京

1 00 ) 0 0 0

【 摘 要】 口带宽需求的迅猛增长 , 接 导致普通 的 P I C 等接 口已无法满足 系统要 求。 使得 更高效的 P I 接 口将越来越 多的应 用在视 频与 CE 监控、 广播 、 通信 、 工控、 医疗、 金融等各种领域 。本文介绍 了 P I P I x r s C 与 C pe 的区别 , E s 并重点介绍 X LN 芯片的内置 P I x r s PC r II X C p sI o E e e 的结构、 工作 原理及接 口时序 , 为用 F G P A实现 P I 接 口 CE 提供参考 。 【 关键词 】C xrsFG XIIX; ie一 P I pe ;P A; LN Vrx 5 E s t

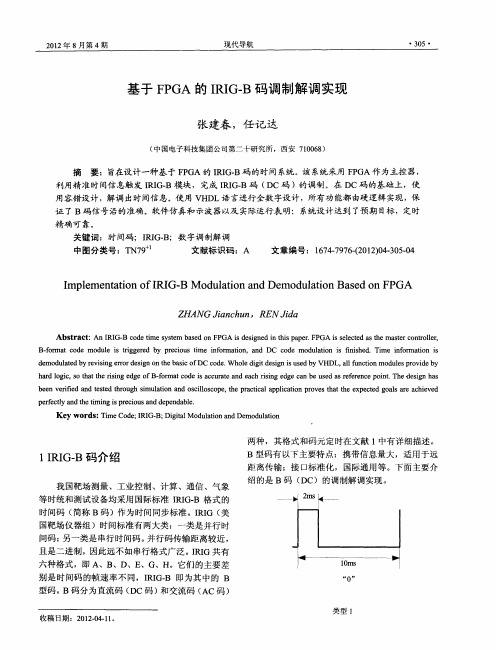

基于FPGA的IRIG—B码调制解调实现

等 时统和 测试设 备均 采用 国 际标 准 I I . 格 式 的 RGB 时 间码 ( 简称 B码 )作 为时 间 同步 标准 。I I ( R G 美 国靶 场仪 器组 )时 间标 准有 两大类 :一类 是 并行 时 间码 : 一类 是 串行 时 间码 。 另 并行 码传输 距 离较近 ,

K e r s Ti d ;RI B: gtl d lt na dDe d lto y wo d : meCo e I G- Dii a Mo uai n mo uain o

两种 ,其格式 和码 元定 时在 文献 1中有 详细 描述 。

1 R G B码 介 绍 I— I

d m o u ae y r v sn ro e in o eb s f e d lt d b e ii g e r rd sg nt a i o o e W h l i i d sg s d b h c DC c d . o e dg t e i n i u e y VHDL, l f n t nm o u e r v d y s a l u c i d l s o i eb o p

别是 时 间码 的帧速 率 不 同 ,I I B 即 为其 中 的 B R G—

“0”

型码 。B码 分 为直流 码 ( DC码 )和交 流码 ( C码 ) A

类型 1

收稿 日期:2 1.41 。 0 20.1

・0 3 6・

现 代 导 航

21 0 2芷

B 码 利用 脉 宽调制 方式 进行 调制 和解 调 。图 1 中类 型一 的码元 表示 0 ,类 型二 的码 元表 示 1 ,类 型三 的码元 表示 尸标 志位 。 B码 的一帧 的长 度 为 1 , s 每 帧含 有 10个 码元 ,每个码 元长 度 为 1ms 一 帧 0 0 。

GPIB接口的FPGA实现

开发 环 境 的移植 ,而且 在 功能 调试 以及 对 局部 修

改 都能 带来 很 大 的方便 。其 内部逻 辑 划分 可基 本

参 照1 公 司 的T 9 1 芯 片 来 进 行 。 图 1 示 是 r I MS 9 4 所

收 稿 1期 :0 7 l一 4 5 2 0 一 l 0 t

4 电 予 元 器 件 盔 用 20 . 删 . d.n 0 0 85 e a c c

2 系统 分 解

根据GPB 制器 的内部 逻辑 框 图 .可 以把整 I控 个 系统 划分 为几 个 子系 统 。其 中包 括 和微 处 理器

公 司 生产 基 于I E 一 8 协议 的G I 控 制器 芯 片 , E E 48 PB 而且 价 格 昂 贵 ,购 买 不 便 。 因此 ,G I 接 口 的 PB FG P A实 现 就 具 有 很 大 的 实 用 价 值 。本 文 论 述 的 是 采 用 V r o L 言来 设 计 基 于 IE 4 81 ei gHD 语 l E E 8 . 协

关 键 词 :G I 接 口 ;F G PB P A; 源 方 挂 钩

0 引言

在 自动 测 试 领 域 中 ,GPB ( e ea P roe I G n rl up s

G I 控制 器 的体系 结构 图 。 PB 在 完成 基本 模 块 以后 ,即可对 每 个模 块 生 成

图形 化 的 符 号 (y o 。 在 组 建 整 个 系 统 的 时 S mb 1 ) 候 ,可 以用 类似 画 电路 图的方 法直 接 对这 些 符 号

I E 4 8协议 有深 刻 的认 识 .而且 在 接 口功 能 子 E E8

片F G P A中从 而 实现G I 接 口功 能 的一种新 方法 。 PB

GPIB接口功能电路设计

GPIB接口功能电路设计哈理工李博文20111 GPIB 接口总线概述GPIB ( General - Purpose Interface Bus) 是一种面向程控仪器的通用接口总线, 它是由国际电子电气工程师协会于1974 年9 月制定的一种标准接口总线,又称IEEE488 总线。

由于具有数据传输稳定可靠,能够实现有效跟踪等特点, 因此, GPIB 自推出以来, 一直受到各仪器厂商的青睐, 经久不衰。

同时GPIB 本身也在不断的发展, 1990 年出现的SCPI 对仪器命令实施了标准化, 使GPIB 系统互换性和互操作性更强。

1993 年推出的HS488 使GPIB 的最高传输速率从1MBp s 提高到8MBp s。

GPIB 总线是一种24 芯的并行无源总线, 其中16 条被用作信号线, 包括8 条数据线(DIO1 ~DIO8) , 3 条握手线A V、NRFD、NDAC) 和5条管理线(A TN、REN、IFC、EOI、SRQ) , 其余8条为地线。

数据传输采用位并行, 字节串行的双向异步传输方式。

消息采用负逻辑, 低电平( ≤018V)为逻辑1 , 高电平( ≥210V) 为逻辑0 。

2 GPIB接口硬件电路的实现(1)软件模拟实现GPIB接口功能电路硬件框图软件模拟实现GPIB接口功能电路硬件框图(2)硬件电路相关芯片STC89C52 : STC89C52系列单片机是从引脚到内核都完全兼容标准8051的单片机,有PDIP-40、PLCC-44、PQFP-44三种封装形式。

其中51/52/53型号后缀为RC,表明片内集成了512字节RAM。

STC89C系列单片机是高速/低功耗的新一代8051单片机,最高工作频率可分别达到25MHz~50MHz。

STC89C系列单片机有较宽的工作电压,5V型号的可工作于3.4V~6.0V,3.3V型号的可工作于2.0V~4.0V。

正常工作模式下的典型耗电为4mA~7mA,空闲模式为2mA,掉电模式’(可由外部中断唤醒)下则小于0.1μA。

gpib芯片

gpib芯片GPIB芯片,全称为General Purpose Interface Bus,即通用目标接口总线,是一种用于仪器间通信和控制的标准接口协议。

GPIB芯片是用于实现GPIB接口的芯片,它集成了一系列功能和电路,使得仪器可以通过GPIB接口与计算机或其他仪器进行通信和控制。

GPIB芯片的主要功能包括:1. GPIB控制器:GPIB芯片集成了GPIB协议的控制器,负责控制GPIB总线上的数据传输和仪器的操作。

控制器可以通过发送命令和查询数据来控制仪器的各种功能和参数。

2. 数据传输:GPIB芯片支持高速的数据传输,可以实现仪器和计算机之间的快速数据交换。

它提供了一种可靠的数据传输方式,可以有效减少数据传输的错误和丢失。

3. 仪器控制:GPIB芯片可以通过发送命令来控制仪器的各种操作,例如设置仪器的参数、进行测量和测试、控制仪器的开关等。

通过仪器控制,可以实现对仪器的灵活和精确的控制。

4. 通信协议:GPIB芯片支持GPIB协议,这是一种开放的、标准化的通信协议,可以实现不同品牌和型号的仪器之间的互联互通。

通过遵循GPIB协议,可以实现多个仪器之间的联网和远程控制。

5. 软件支持:GPIB芯片通常会提供软件开发工具和驱动程序,以便开发人员可以方便地使用GPIB接口进行编程和开发。

这些软件支持可以大大简化软件开发过程,提高开发效率和准确性。

GPIB芯片在科学实验室、工业自动化、测试仪器等领域应用广泛。

它能够实现多个仪器的联网和控制,方便实时监测和远程操作。

同时,GPIB芯片还可以通过连接各种外部设备和传感器,实现更加复杂的实验和测试任务。

在选择GPIB芯片时,需要考虑以下因素:1. 功能和性能:不同的GPIB芯片会提供不同的功能和性能,如数据传输速度、支持的仪器类型和通信协议等。

根据具体的应用需求,选择最适合的芯片。

2. 兼容性:GPIB芯片需要与其他设备和仪器进行配合使用,因此需要考虑其兼容性。

基于FPGA的GPIB总线接口IP核设计【文献综述】

毕业设计(论文)文献综述题目:基于FPGA的GPIB总线接口IP核设计专业:电子信息工程1前言部分(阐明课题的研究背景和意义)随着科学技术的发展,许多现代化的系统,例如庞大的通信网、复杂的过程控制、反应快速的武器系统等等,它们的研制、调试、维修等工作,对测试系统的依赖性很强。

测试系统需要GPIB(通用接口总线)控制器,而控制器本质上是协议转换器。

用户给计算机输入特定命令,计算机操作系统通过驱动程序向挂接在PCI/ISA总线上的控制器发起一个相应的数据交易。

控制器则把交易中所得到的数据转换成一个符合GPIB协议的控制信号和数据信号,这样用户就可以通过对计算机的操作来控制挂接在GPIB母线上的各个测量仪器进行控制。

GPIB虽然己经有了很长的历史,但是这种测量总线方便易用,组建自动测试系统方便,而且费用低廉。

虽然近来出现了VXI等更加快速先进的测试总线,但他们大多昂贵而又麻烦,大多是插卡式的。

所以,GPIB总线在使用台式机组建测试系统的时候有不可替代的作用。

此外,在很多对测试速度要求不高,测试仪器的体积不作要求的情况下,GPIB总线也有相当的优势。

而GPIB控制芯片(NAT9914)是自动测试系统中的关键芯片,因此对GPIB控制芯片有一定的需求量。

集成电路的飞速发展使得它在各行各业中发挥着越来越大的重要性。

特别是ASIC技术的发展,用FPGA/CPLD对各类芯片进行设计和仿真,再在底层对FPGA 进行布线,实现专用芯片的功能己经得到广泛的应用。

此课题的研究,正是针对ASIC的发展而开展的。

设计基于FPGA芯片的GPIB接口的IP Core不仅量身定做,不浪费资源,而且通用性极强,具有自主知识产权,仪器研发人员拿来稍作修改就可以应用。

有了IEEE-488协议的IP核,再加上以后继续深入的研发,就能实现测控领域的NAT9914芯片的自主化,所以用FPGA实现GPIB接口芯片有一定的意义和价值。

本课题正是基于这样的契机以及业界的需求而决定选用FPGA 实现完全独立自主的GPIB控制器。

GPIB接口控者功能的FPGA实现

邓先荣 , 等

GI PB接 口控 者 功 能 的 F G P A实现

Re l a i n o h n r l rF n to a e PGA o t ra e ai t ft e Co to l u c i n B s d on F z o e f rGPI I e f c B n

邓 先 劳 饧 墨 常 庞 金 互 雩镥

( 西华 大学 电气信 息 学院 , 四川 成都 60 B控制 芯 片价格 昂贵 、 买困难 等问题 , 购 采用低 成本 的 F G P A器件替 代专 用 G I PB控制 芯 片来 实现 GP IB接 口控

线 。数据传输采用位并 行 、 字节 串行 的双 向异步 传输 方式。消息采用负逻辑 , 低电平( .V) ≤0 8 为逻辑 1高 ,

电平 为 逻辑 0 。

普遍 认 可 , 被 接 收 为 IE 8 — 7 并 E E 4 81 5标 准 和 A s/ 9 NI , IE 8 .- 8 E E48 11 7标准 。在美 国, 9 常把这 种标 准称为 IE 8 标准或 H — ; E E48 PI 在欧洲 , B 一般称为 ICI E— B或者 G I (eea proei eae u ) PB gnrl u s n r c b s 。 — p tf 在 自动测试领域 , PB总线 占有很重 要 的地位 , GI GI PB通用接 口是测试仪器常用 的一种 接 口方式 , 在组 建 自动测试 系统 时 , 几乎 均要 求 系统具 备这 种接 口。 但在实际的研 发过程 中 , 只有 国外几家公 司生产 G I PB 芯片 , 价格昂贵且很难购买 。因此 , PB接 口的 F G GI PA 实现具有很大的实用价值 。

嵌入GPIB控制和DDS模块的低成本信号发生器的实现

嵌入GPIB控制和DDS模块的低成本信号发生器的实现【摘要】本文通过对FPGA(可编程逻辑门阵列)的资源、GPIB控制器和直接数字频率合成技术DDS工作原理的分析,全面描述了在FPGA内嵌入GPIB 控制模块和DDS模块实现低成本、高频率信号发生器的方法。

通过实际测试,验证了仪器的性能完全符合设计指标的要求。

【关键词】GPIB DDS FPGA1 GPIB接口功能设计GPIB具有10种接口功能:控、听、讲、源挂钩联络、受挂钩联络、服务请求、并行点名、远地/本地、设备清除、设备触发功能。

目前NAT9914是常用的GPIB接口芯片之一,本设计中采用模块化设计方法(其模块是以GPIB接口的功能来划分的),按照GPIB接口的功能协议,利用AHDL语言在FPGA芯片上进行设计。

以听功能为例,设计如下:SUBDESIGN Listen_function(pon,IFC,UNL,ACDS,MTA,lun,CACS,ATN,ltn,lon,MAL: INPUT;LIDS,LADS,LACS,x0,y0 : OUTPUT;)V ARIABLEX0,Y0:NODE;BEGINX0 =!(!pon & !IFC & !(UNL & ACDS) & !(ACDS & MTA) & !(lun & CACS) & Y0);Y0 =!(!lon & !(MAL & ACDS) # !(ltn & CACS) & x0 );LIDS=X0;LADS=Y0 & ATN;LACS=y0 & !ATN;END;以上各输入输出信号沿用GPIB的统一标准定义,此处不再分诉。

经过编译仿真后,生成L功能模块的符号图,如图2所示。

由于其他功能模块设计方法类似,因此不再重复叙述。

当把这些设计好的功能进行系统综合时只需充分考虑NAT9914的各寄存器的数据位对这些功能块的连接和控制即可。

FPGA接口协议之PCIE

FPGA接⼝协议之PCIE这个问题应该分为两个:FPGA⾼速接⼝协议, FPGA PCIE 功能运⽤。

如果FPGA 来做PCIE 的话,X,A ⼚的PCIE phy,link,都是硬核 + logic实现,并且IP接⼝,驱动, ⼚商均已经提供好,如果要运⽤PCIE 的话,直接使⽤对应的IP+Driver即可。

FPGA⾼速:Phy需要⽤到,Tranciver(收发器单lane可达30Gbps) 和 Serdes(普通⾼速IO 单lane可达 1.5Gbps)。

所以只需要熟悉并掌握对应的⽂档和应⽤即可,最好结合实际硬件进⾏学习。

协议IP最主要的是阅读协议⽂档,并了解⾃⼰需要实现协议的哪⼀部分。

可以去 opencore,github上去翻翻看别⼈的代码。

Eth 提供的Phy + Mac 层IP, 上层需要⾃⼰实现。

(阅读相关⽂档,或者使⽤IP 对应的driver, 嵌⼊式软件实现)。

Sata ⼚商提供 Phy。

link, trans layer + driver 均需要⾃⼰实现。

Pcie 可以不⽤管协议直接使⽤xdma 等IP,或者使⽤⽐较基础的pcie IP(xdma 内部就是 pcie ip + dma ip)⾃⼰实现TLP (传输层协议)。

⼤部分运⽤使⽤官⽅IP即可(xilinx windows 驱动问题较多)。

FPGA PCIE 功能运⽤:以xilinx为例第⼀个IP 直接封装硬核需要⾃⼰去封装TLP 包,可以⽣成Example 去查看TLP 相关协议如何⼯作。

运⽤的使⽤还需要再stream外层对数据进⾏打包,⽐较复杂。

第⼆个IP 就是将IP 封装为AXI Mem接⼝,对外直接读写数据,⽆法看到协议控制等内容。

并且驱动以及IP控制没有提供sgdma 的⽅式,应⽤层内存管理较为复杂。

第三个IP 算是⽤的最多的,在第⼆个基础上增加了SGDMA 的功能,Root端运⽤⾮常⽅便。

Example 直接可以在 windows/linux/mac 上运⾏。

基于FPGA的GPIB接口IP核的研究与设计的开题报告

基于FPGA的GPIB接口IP核的研究与设计的开题报告1. 研究背景和意义GPIB(General Purpose Interface Bus)是一种常见的仪器控制接口协议,被广泛应用于科研、生产等领域。

FPGA(Field Programmable Gate Array)是一种可编程的逻辑门阵列,拥有很高的灵活性和性能,可以实现复杂的数字电路设计。

将GPIB接口与FPGA结合起来,可以实现高速、高可靠性的仪器控制方案。

本项目将针对GPIB接口协议进行研究,设计一个基于FPGA的GPIB接口IP核,可以实现GPIB接口的收发等功能。

该IP核可以应用于各种GPIB接口设备,如波形发生器、虚拟仪器等,也可以被用于其他数字电路设计中,具有广泛的应用前景。

2. 研究内容和技术路线研究内容包括:1)GPIB接口协议的研究。

了解GPIB接口的物理层、信号电平、通信协议、命令格式等基础知识,为后续设计提供理论基础。

2)FPGA芯片的选型和设计。

根据所需信号处理速度、逻辑门数量等参数,选取合适的FPGA芯片,并进行设计和优化。

3)GPIB接口IP核的设计和开发。

包括接收GPIB接口信号、解析命令、发送响应信号等功能。

4)测试和验证。

通过实验验证该IP核的可靠性、准确性和性能等指标,同时对GPIB接口套件的兼容性进行测试。

技术路线:1)研究和了解GPIB接口协议,对各个协议层进行分析和设计。

2)选取合适的FPGA芯片,进行适当的设计和优化。

3)使用Verilog HDL语言编写IP核的设计,并进行仿真验证。

4)将IP核集成到FPGA芯片中,进行测试和验证。

3. 研究计划和进度研究计划:第1-2周:研究GPIB接口协议,了解信号电平、通信协议、命令格式等基础知识;第3-4周:选取合适的FPGA芯片,并开始设计和优化;第5-6周:使用Verilog HDL语言编写GPIB接口IP核的设计,并进行仿真验证;第7-8周:将IP核集成到FPGA芯片中,并进行初步测试;第9-10周:进行系统测试和验证,测试该IP核的可靠性、准确性和性能等指标。

基于FPGA的通用接口总线(GPIB)控制器的IP核设计

引言

术 的 高 速 发 展 与广 泛 应 用 , 必 将 给 网 络 这

时 代 的 测 试 仪 器 和 测 试 技 术 带 来 革 命 性 变 仪 器 的 网 络 化 发 展 趋 势 。 建 网 络 化 测 试 组 建 系 统 的 费 用 , 可 以 提 高 测 试 系 统 的 功 还 能 , 宽 其应 用 的 范 围 。 文 采 用 F GA芯 拓 本 P 片 实 现 GP B 制 器 的 I 核 设 计 完 成 芯 片 I控 P TMS 9 4 9 l 的产 权 自主 化 。

统 一 的标 准 , 大地 推 动 了 自动 测试 技 术 的 极 发展。 由于 G I 总 线 为并 行 外 总 线 , 仅 保 PB 不 持 了并 行总 线 传 送速 度 快 、 效 数 据速 率 高 有 的 优点 , 而且 增 强 了驱动 能力 , 通 讯距 离可 达 2 m, 有 良好 的 抗 干 扰 能 力 和通 用性 , 0 并 总 线 上 最 多可 挂 接 1 台 设 备 并且 传输 速 度 5

通路 模 块 。 口功 能状 态 机 模块 设 计 包括 八 号 线为 8 数 据 线 ( I ~D O8 、根 握 手 接 根 D Ol I )3 个小模块( 如源 方挂 钩 、 方 挂 钩 等 ) 并采 线 ( 受 , DAV、 NRFD、 NDAC) 5 管 理 线 和 根 ( TN、 N、F 、 O 、 R ) 数据传 输采 用 A RE I C E IS Q 。 最 后 调 用 各 个 子 模 块 并 用原 理 图的 方 式 进 位 并 行 , 节 串行 的 双 向 异 步 传输 方 式 。 字 需

u ru Ⅱ平 台 下进 行 分 析 和仿 真 。 数 据 通 平 ( . v) 逻辑 1 高 电 平 ( . v) at s 对 ≤0 8 为 , ≥2 o 为逻

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

的状态挂钩的协调一致, 设计时应采用同步状态 循环, 而且没有可供使用的消息比特。

机, 以在时钟信号的触发下, 完成各个状态之间

源方产生态 (SGNS) 用于在源方产生态器件

www.ecda.cn 2008.5

41

第10卷 第5期 2008年5月

Electronic Component & Device Applications

系统中的内部寄存器由13个寄存器组成, 其 中包括只读寄存器和只写寄存器。它们是完成微 处理器端到GPIB接口功能端的数据桥梁, 其中一

第10卷 第5期 2008年5月

设计参考

Vol.10 No.5 May. 2008

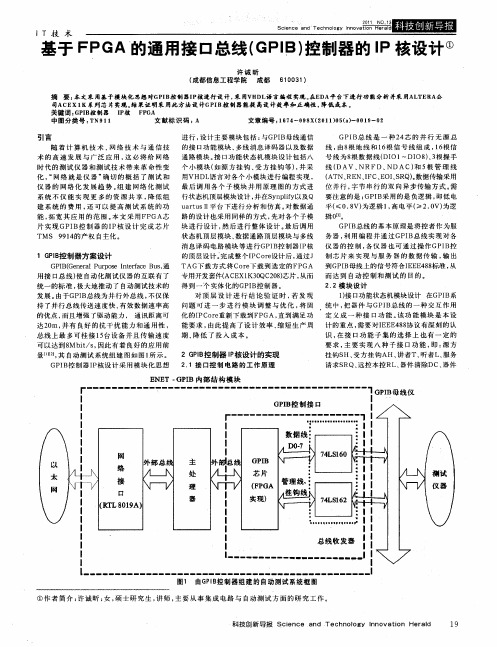

图1 GPIB控制器体系结构简图

些寄存器还赋予了GPIB控制器的若干片内附加功 的转移。

与微处理器接口的读写电路设计可以利用组 合逻辑电路设计方法来实现, 其基本模块有译码 电路, 读写电路等在设计时, 只要对其基本功能 深刻理解, 就很容易实现。

需 要 对 IEEE488 协议有深刻的认识, 而且在接口功能子 集的选择上也有一定的要求。为了让各接口功能 子集能协调一致的工作, 必须采用同步状态机。

1 GPIB控制器的总体结构

用FPGA实现GPIB控制器可采用ISP (系统可 编程) 的设计方法。先把整个待设计系统划分为 若干基本功能模块, 其中包括基本组合逻辑电路 以及复杂的同步状态机设计。

在基本单元实现方法上, 可采用语言描述方 式完成基本模块的设计, 这不仅可以方便将来跨 开发环境的移植, 而且在功能调试以及对局部修 改都能带来很大的方便。其内部逻辑划分可基本 参 照TI公 司 的TMS9914芯 片 来 进 行 。 图1所 示 是

息。

reg rDAV;

(2) 表语

parameter [5:0]

在这组状态图中, 箭头用来表示一个接口功 sSIDS = 6' b000001,//采用一位热码编码格式

能中各状态之间的一切允许的变迁。每一项变迁 sSGNS = 6'b000010,sSDYS = 6'b000100,sSTRS =

都由一个表语来限定, 表语之间可以为真, 也可 6' b001000,sSWNS = 6' b010000,

第10卷 第5期 2008年5月

Electronic Component & Device Applications

Vol.10 No.5 May. 2008

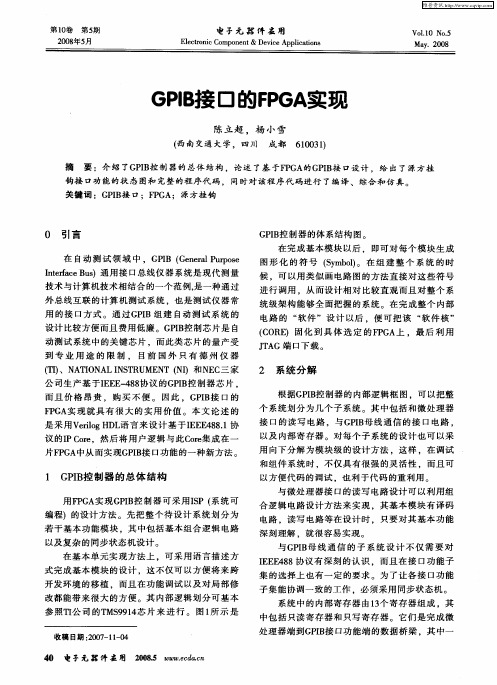

GPIB接口的FPGA实现

陈立超, 杨小雪 (西南交通大学, 四川 成都 610031)

摘 要: 介绍了GPIB控制器的总体结构, 论述了基于FPGA的GPIB接口设计, 给出了源方挂 钩接口功能的状态图和完整的程序代码, 同时对该程序代码进行了编译、综合和仿真。 关键词: GPIB接口; FPGA; 源方挂钩

息; 讲者接口功能可让器件在接口上把数据发送 的控制。其状态图如图2所示。

到其他一些器件中去; 听者接口功能让器件在接

(1) 状态图

口上接受来自于其他器件的数据; 本控就是本地

源方空闲态 (SIDS) 可在电源接通时使SH功

控制 (面板或后背板)。为了保持状态机之间相互 能进入 SIDS态。在这一态, SH功 能 不 参 与 挂 钩

能。

每一个接口功能由一组或多组相互联系而又

在整个设计中, 对接口功能的设计是设计的 相互独立的状态来定义。在一个时刻, 一组互联

核心, 接口功能的完成必须依赖于各子接口功能 又互斥的状态中必须有一个而且也仅有一个状态

的 实 现 。 在 实 现 子 接 口 功 能 的 时 候 , 按 照 起作用。在IEEE488协议中对接口功能的每一个

begin if ( rst ) state = sSIDS; else state = next; end

always@ ( state or ATN or CACS or CTRS or TACS or SPAS or nba or DAC or RFD ) //组合逻辑

begin SIDS = 0; SGNS = 0; SDYS = 0; STRS = 0;

接口功能可以有一个或多个容许的子集, 其中源 步传递。SH 功能控制着多线 消 息 比 特 传 递 的 开

方挂钩接口功能保证多项消息的正确传输; 受方 始和结束。它接收由受方器件传来的 RFD和DAC

挂 钩 接 口 功 能 主 要 用 于 保 证 正 确 地 接 受 远 地 消 消息, 并产生 DAV 消息来实现对数据 比 特 传 递

收稿日期: 2007- 11- 04

40

2008.5 www.ecda.cn

GPIB控制器的体系结构图。 在完成基本模块以后, 即可对每个模块生成

图 形 化 的 符 号 (Symbol)。 在 组 建 整 个 系 统 的 时 候, 可以用类似画电路图的方法直接对这些符号 进行调用, 从而设计相对比较直观而且对整个系 统级架构能够全面把握的系统。在完成整个内部 电路的 “软件”设计以后, 便可把该 “软件核” (CORE) 固 化 到 具 体 选 定 的 FPGA上 , 最 后 利 用 JTAG 端口下载。

SWNS = 0; SIWS = 0; rDAV = 0; case ( state ) sSIDS:

begin if ( TACS | SPAS | CACS ) //状态表语 next = sSGNS; else next = sSIDS; SIDS = 1; rDAV = 1; //rDAV = 0; passive DAV_

2 系统分解

根据GPIB控制器的内部逻辑框图, 可以把整 个系统划分为几个子系统。其中包括和微处理器 接口的读写电路, 与GPIB母线通信的接口电路, 以及内部寄存器。对每个子系统的设计也可以采 用向下分解为模块级的设计方法, 这样, 在调试 和组件系统时, 不仅具有很强的灵活性, 而且可 以方便代码的调试, 也利于代码的重利用。

Vol.10 No.5 May. 2008

图2 SH功能状态图

产生一个新的消息比特, 以使SH功能正等待的新 以为假。如果限定变迁到另一个状态的一切表语

消息变成可供使用的消息。DAV消息应被发送为 均为假, 则接口功能必须停留当前的状态。并在

假态 (- DAV), 器件可以改变正在通过讲者功能 若 且 仅 若 表 语 之 一 变 为 真 之 后 的 任 何 时 间 内 进

上的多线消息。

SIWS, DAV, clk, rst, ATN, CACS, CTRS, TACS,

源方闲等态 (SIWS) 中, SH功能对外部比特 SPAS,nba, DAC, RFD ); // 对模块信号进行定义

传递过程不起作用, 但在内部等待器件开始一次 input clk, rst;

新的消息循环产生过程中仍 起 作 用 。 这 个 SIWS input ATN, CACS, CTRS, TACS, SPAS, nba, DAC,

42

2008.5 www.ecda.cn

第10卷 第5期 2008年5月

设计参考

Vol.10 No.5 May. 2008

sSIWS = 6'b100000; reg [5:0] state, next; assign DAV = ( SGNS | SDYS | STRS | SWNS | SIWS ) ? rDAV : 1'bz; always@ ( negedge clk or posedge rst ) //时序逻辑

源方挂钩 (SH) 功能主要是赋予器件确保多

挂钩 、受方挂钩、讲者、听者、控者、并行查 线消息正确传递的能力。源方挂钩功能与一个至

询、服务 请 求 、 远 控/本 控 、 器 件 清 除 和 器 件 触 多个受方挂钩功能 (分别含于各个仪器之中) 之

发。每种接口功能按照特殊的规约来行事。一个 间的链锁挂钩序列, 可保证每一个多线消息的异

还必须停留在 SDYS态等待, 直到参加挂钩的AH (ATN=假) 方式。

功能表明它们已经准备好接收消息比特为止。在

(3) 基于Verilog HDL的状态机实现

这一态, 必须仍然发送 DAV=假, 而器件则不能

根据以上分析, 状态机的组成一般分由组合

改变正在发送的消息。

逻辑和时序逻辑, 这样, 在描述状态机的时候,

message end

sSGNS: begin if ( nba ) next = sSDYS;

else if ( ( ATN & ( ~( CACS | CTRS ) ) ) | ( ( ~ATN ) & ( ~( TACS | SPAS ) ) ) )

(TACS=真) 或控 者 功 能 (CACS=真) 发 送 的 多 线 入。

消息。

通过状态表语 TACS | SPAS | CACS 可以看到

在源方延迟态 (SDYS), SH功能等待在SGNS SIDS跃迁到 SGNS, 由此可知, 该源方挂 钩 功 能

态改变了的消息比特在母线上稳定下来。SH功能 设 计 包 括 命 令 工 作 方 式 (ATN=真) 及 数 据 工 作

在 源 方 传 递 态 (STRS), SH功 能 向 受 方 挂 钩 只要对接口电路的状态图分析清楚, 即可用相同

功能表明器件正在继续发送有效的消息比特, 此 的语言进行描述, 即代码结构都相同。值得注意

时, DAV消息必须被发送为真消息。不 言 而 喻 , 的是如何把 IEEE488对接口功能描述转化为相应

这时的器件不能改变或结束正在传递的多线消 的状态图。

息。

鉴于 SH 模块十分重要, 而且作为其它状态

在源方等待新循环态 (SWNS), SH功能等待 机 的 标 准 代 码 模 板 , 本 文 特 给 出 该 状 态 机 的 代

器件开始一轮新的消息循环。此时DAV消息可发 码: