ISE时序仿真

ISE仿真CORDIC模块总结

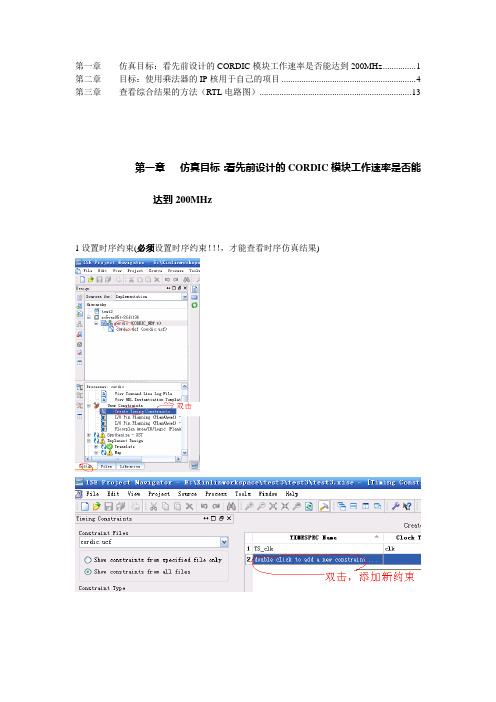

第一章仿真目标:看先前设计的CORDIC模块工作速率是否能达到200MHz (1)第二章目标:使用乘法器的IP核用于自己的项目 (4)第三章查看综合结果的方法(RTL电路图) (13)第一章仿真目标:看先前设计的CORDIC模块工作速率是否能达到200MHz1设置时序约束(必须设置时序约束!!!,才能查看时序仿真结果)2.综合3. 翻译,映射,布线,产生编程文件。

4.查看静态时序仿真结果第二章 目标:使用乘法器的IP 核用于自己的项目1. 编译IP 核库,目的:这样才能用questasim 对包含该乘法器的项目进行仿真这个过程可能要半个多小时。

这一步的目的是:编译xinlinx FPGA自带的库,经过这次操作后,以后就不用再编译了。

然后打开Qestasim,把上面编译了的库包含进来,具体操作忘记了!包含库后的Qestasim界面如下:2 .注意:要记住该保存地址,因为生成的IP核的.v文件就保存在这个目录下,在Questasim 中仿真时,要把该.v文件包含进来!成功产生IP 核后的界面如下:2. 在qustasim 中,把生成的乘法器的.v 文件(在ISE 中利用IP 核生成乘法器的时候的保存地址中的.v 文件)包含到工程中来,这一步很关键。

然后就可以在qustasim 中例化刚刚产生的乘法器Multipler ,并设计相关程序例如,可在Testbench 中设计如下代码:Multipler1 DUT2(.clk(clk),.a(a),.b(b),.p(p),.sclr(SCLR),.ce (CE))注意:我们在设计好包含层次模块的verilog 代码后,全部添加到Qustasim 或者ISE 中,软件会自动根据代码的里描述的关系生成层次结构!!!第三章查看综合结果的方法(RTL电路图)在频偏校正模块中,我设计的代码结果如下:。

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法作者:毕成炜2012年1月30日星期一我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

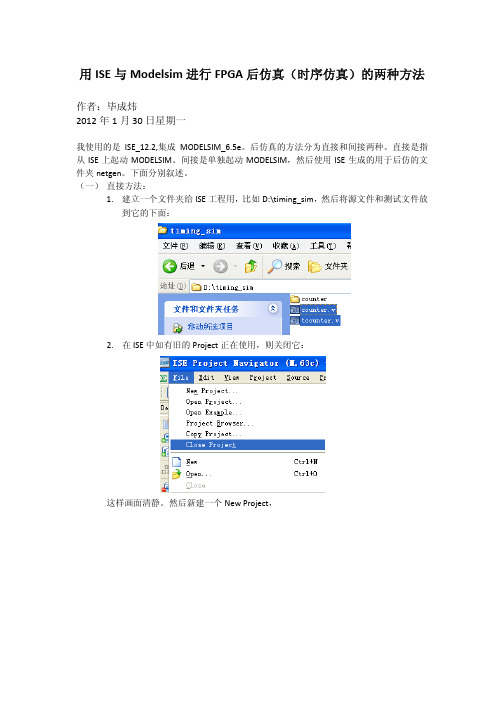

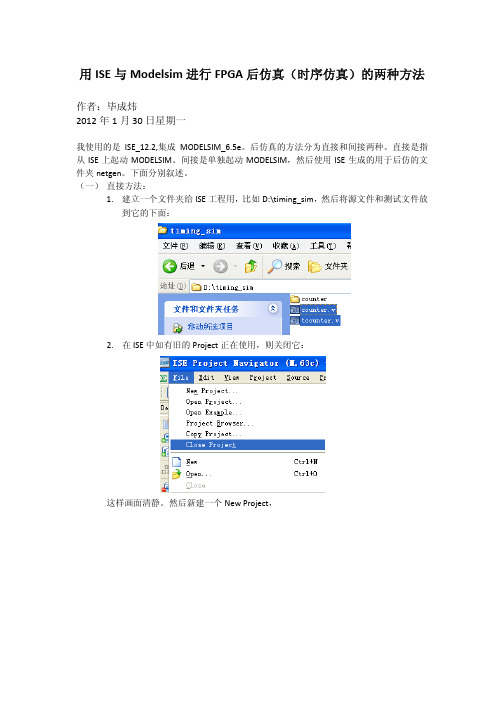

(一) 直接方法:1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放到它的下面:2.在ISE中如有旧的Project正在使用,则关闭它:这样画面清静。

然后新建一个New Project,点Next,选好器件和仿真器:点Next,点Finish.为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:双击器件:保证下图红圈处选中你要的仿真器:点OK后,在主菜单中点:保证在红圈处指定好MODELSIM执行文件所在的位置编译仿真库可以在这里双击Compile HDL Simulation Libraries,也可以在C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿真过程可能出问题。

点Next,点Next,选定你针对什么器件编译仿真库,点Next,点Next,注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法作者:毕成炜2012年1月30日星期一我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

(一) 直接方法:1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放到它的下面:2.在ISE中如有旧的Project正在使用,则关闭它:这样画面清静。

然后新建一个New Project,点Next,选好器件和仿真器:点Next,点Finish.为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:双击器件:保证下图红圈处选中你要的仿真器:点OK后,在主菜单中点:保证在红圈处指定好MODELSIM执行文件所在的位置编译仿真库可以在这里双击Compile HDL Simulation Libraries,也可以在C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿真过程可能出问题。

点Next,点Next,选定你针对什么器件编译仿真库,点Next,点Next,注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

XilinxISE下的静态时序分析与时序优化

XilinxISE下的静态时序分析与时序优化单击Design Summary中的Static Timing就可以启动时序分析器(Timing Analyzer)。

在综合、布局布线阶段ISE就会估算时延,给出⼤概的时延和所能达到的最⼤时钟频率,经过PAR后,在Static Timing中给出的是准确的时延,给出的时序报告可以帮助我们找到关键路径,然后针对其进⾏优化,提⾼系统的时钟频率。

这⾥的Minimum period指的是最⼩的逻辑延迟;造成时序性能差的原因很多,主要缘由以下⼏种:1. 布局太差⼀般和代码本⾝没有关系。

解决⽅案:只能从软件⾃⾝的布局算法考虑(调整布局的努⼒程度)或者使⽤⾼端芯⽚2. 逻辑级数太多逻辑级数越多,资源的利⽤率越⾼,但是对⼯作频率的影响也越⼤。

解决⽅案:1.使⽤流⽔线技术;2.如果是多周期路径,添加多周期约束;3.良好的编码习惯,不要过多嵌套if-else,尽量使⽤case代替if语句。

3. 信号扇出过⾼⾼扇出会造成信号传输路径过长,从⽽降低时序性能。

解决⽅案:1.逻辑复制;2.区域约束,想过逻辑放置在⼀起。

4. 不要同时使⽤双边沿触发FPGA的底层⼯艺都是单向的同步电路,所以本⾝不⽀持统⼀信号的双边沿触发,ISE在实际处理的时候,会⾃动将该信号2倍频,然后利⽤第⼀个沿处理上升沿,第⼆个沿处理下降沿。

这样在分析时序时,⾃动把约束升级为ucf⽂件中的两倍。

5. Xilinx最优时序解决⽅案1.I/O约束 根据Xilinx器件的特点,控制信号置于器件的顶部或底部,且垂直布置;数据总线的I/O置于器件的左右两侧,且⽔平布置,这样可以最⼤程度的利⽤芯⽚底层结构。

2.ISE实现⼯具 ISE中的⼯具具备不同的努⼒程度,直接使⽤最⾼级别的可以提⾼时序性能,但是会耗费很多时间,所以应该逐步调整努⼒程度。

第⼀遍使⽤默认的参数选项,如果不满⾜再调整综合、映射、布局布线的参数。

时序优化的若⼲策略优化⽅向⼀:合理使⽤Blcok RAM和Distributed RAM1. 均衡Block RAM和Distributed RAM的使⽤。

基于ISE的仿真

基于ISE的仿真在代码编写完毕后,需要借助于测试平台来验证所设计的模块是否满足要求。

I SE提供了两种测试平台的建立方法,一种是使用HDL Bencher的图形化波形编辑功能编写,另一种就是利用HDL语言。

由于后者使用简单、功能强大,所以本节主要介绍基于Verolog语言的测试平台建立方法。

1.测试波形法在ISE中创建testbench波形,可通过HDL Bencher修改,再将其和仿真器连接起来,再验证设计功能是否正确。

首先在工程管理区将Sources for设置为B ehavioral Simulation,然后在任意位置单击鼠标右键,在弹出的菜单中选择“Ne w Source”命令,然后选中“Test Bench WaveForm”类型,输入文件名为“test_ bench”,点击Next进入下一页。

这时,工程中所有Verilog Module的名称都会显示出来,设计人员需要选择要进行测试的模块。

由于本工程只有一个模块,所以只列出了test,如图4-30所示。

图4-30选择待测模块对话框用鼠标选中test,点击“Next”后进入下一页,直接点击“Finish”按键。

此时HDL Bencher程序自动启动,等待用户输入所需的时序要求,如图4-31所示。

图4-31时序初始化窗口时钟高电平时间和时钟低电平时间一起定义了设计操作必须达到的时钟周期,输入建立时间定义了输入在什么时候必须有效,输出有效延时定义了有效时钟延时到达后多久必须输出有效数据。

默认的初始化时间设置如下:∙时钟高电平时间(Clock High Time):100ns∙时钟低电平时间(Clock Low Time):100ns∙输入建立时间(Input Setup):15ns∙输出有效时间(Output Valid):15ns∙偏移时间(Offset):100ns单击“OK”按钮,接受默认的时间设定。

测试矢量波形显示如图4-32所示。

ISE的使用说明

ISE的使用说明ISE(Integrated Software Environment)是一种集成软件环境,用于设计和验证硬件开发项目。

它由Xilinx公司开发,旨在为FPGA(Field-Programmable Gate Array)和SoC(System-on-a-Chip)设计提供完整的解决方案。

ISE具有多种功能和工具,可以帮助工程师在整个开发过程中完成各种任务。

ISE的安装:ISE的主要功能:ISE为硬件设计和验证提供了全面的解决方案。

以下是ISE的主要功能:2.综合和优化:ISE包含了综合和优化工具,将HDL代码转换为布尔函数表示。

综合工具会分析代码并生成等效的硬件电路电路。

优化工具会尝试将电路改进为更有效的形式,以提高性能和减少资源消耗。

3.约束和分析:在设计过程中,您通常需要对硬件进行约束,以满足特定的要求。

ISE提供了工具来定义时序约束、电气约束和物理约束,并分析设计是否满足这些约束。

4.实现和布局:一旦设计和优化完成,ISE将使用实现和布局工具将电路映射到目标FPGA或SoC中。

这些工具将选择适当的逻辑资源,并将其布局在特定的芯片区域,以最大程度地提高性能和效率。

5.仿真和调试:在设计过程中,您需要对硬件进行仿真和调试,以验证其正确性和性能。

ISE提供了仿真工具,可以对设计进行功能仿真、时序仿真和混合信号仿真。

它还提供了调试功能,可帮助您定位和解决问题。

以下是使用ISE的一般步骤:1.创建新工程:在ISE中,您需要先创建一个新的工程,用于存储和组织设计文件。

可以在ISE中创建一个新的工程,并选择适当的目标设备。

2. 添加设计文件:一旦工程创建完成,您可以添加设计文件到工程中。

通过右键单击工程文件夹,并选择“Add Source”来添加设计文件。

选择适当的文件类型,并在文件对话框中选择要添加的文件。

3. 设置约束:在设计过程中,您需要为硬件设计设置约束,以满足特定的要求。

通过右键单击工程文件夹,并选择“Add Constraints”来添加约束文件。

在xilinx ise12.2 环境下用自带的isim仿真详解

在xilinx ise12.2 环境下用自带的isim仿真详解最近项目用到FPGA,也开始了FPGA的学习历程,硬件为红色飓风的E45,FPGA是spartan6系列的,软件开发环境是xilinx ise12.2的版本。

之前一直在做单片机,有一定的C基础,对FPGA的学习也算快吧,花了一天的时间移植了一个FPGA的串口程序,测试通过,收发正常,心里美滋的,在第三天的时候要做一个SPI的时序,由于程序是自己写的,所以对时序没把握,就需要仿真,看一下波形,可谁知道这一仿真就是2天的时间,搞得我头疼闹热的,到处查资料,看网站,弄得我好不痛苦啊,明明很简单的事情,却花了两天的时间,哎,在此也深感一个人学习的痛苦,也感到资源的可贵啊,为了我的两天时间,我决定写下记录,以此让跟我一样遇到问题的人能够少花时间。

以下是我从网上收集的在xilinx ise12.2 环境下用自带的isim 仿真步骤:/view/fce6e53c0912a21614792981.html该链接的资料是OK的,但是有些小的细节需要说了,同时也我遇到的问题。

1.在生成verilog hex fixture 之后,一定要记得在Addstimulus here之后加上你的动作代码,要不然仿真是不会有动作的,问题很幼稚,但是他花了我2个小时的时间,回头看了好几遍文档在注意到有自己要添加的东西。

一般的添加格式为:initialbeginclk = 1'b0;rst = 1'b0;#5clk = 1'b1;rst = 1'b1;endalways #10 clk = ~clk;2.对于isim的界面,需要用好几个工具。

1所指的10us的选项,一般默认都很小,所以要根据具体的时间自己修改,小问题,也花了我不少时间2所指的功能键是一次运行10us,很有用的3所指的放大器在看波形的很好用如果仿真出现红线和蓝线,证明仿真失败!这是我两天以来出现的最多的仿真界面,到现在才明白如果信号不是绿色的证明都是有问题的,仿真是失败的!之所以会出现这种问题都是因为自己的设计功底太差。

关于Xilinx ISE简单使用方法介绍

output [7:0] y_out,

);

assign y_out = flag ? x_in : 8'b00000000;

endmodule

3.程序语法检查

如下图所示:

或者:

4.创建测试文件(功能仿真数据的建立)

ProjectNew Source。如输入文件名:Two2One_tf(*.v)。

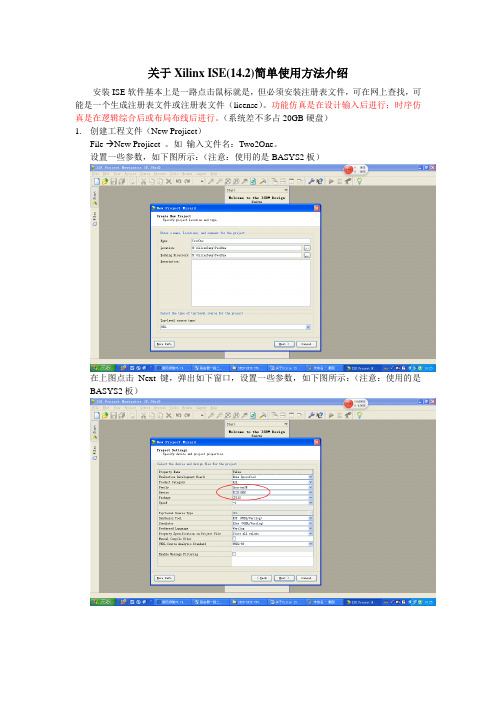

关于Xilinx ISE(14.2)简单使用方法介绍

安装ISE软件基本上是一路点击鼠标就是,但必须安装注册表文件,可在网上查找,可能是一个生成注册表文件或注册表文件(license)。功能仿真是在设计输入后进行;时序仿真是在逻辑综合后或布局布线后进行。(系统差不多占20GB硬盘)

1.创建工程文件(New Projiect)

将运行另外一个程序产生仿真波形图,如下图所示:

详细波形图:

6.管脚适配(为下载做准备)

先创建*.UCF文件

弹出窗口,点击Yes,创建.UCF文件

之后,系统会启动管脚配置程序,然后设计人员根据情况配置管脚,下图为BASYS2板管脚情况,所示:

适配后:

配置好管脚后保存好文件。

7.综合与实现

管脚分配完成之后,必须进行布局布线,如下图所示:

FileNew Projiect。如输入文件名:Two2One。

设置一些参数,如下图所示:(注意:使用的是BASYS2板)

在上图点击Next键,弹出如下窗口,设置一些参数,如下图所示:(注意:使用的是BASYS2板)

2.创建资源文件(New Source)

ProjectNew Source。如输入文件名:One2Two。

选择,如Verilog Test Fxiture,建立用于测试以上资源文件(电路)用的数据文件。建立不同时间段的输入数据,用于产生相应时段的输出波形。

ISE入门教程

ISE整体开发流程:建工程→编写工程代码→检查语法错误→行为仿真→综合→管脚约束→实现→时序仿真→生成bit流文件→下载到板子上调试;实验是用ISE10.1做的,与ISE9.1不同的地方在文中也有相关说明。

一:建工程1.工程命名file→new projiect(如下图所示:在工程名处填:jishuqi 资源类型选:HDL)2.器件类型选择及仿真综合工具、硬件描述语言设置点击Next,出现如下图所示界面:图中设置的有:Family:virtex2P; Device :XC2VP30;Package:FF896;Speed:-7(这个是根据VIRTEX2P开发板设置的数据,不同的开发板设置的数据不一样)。

3.完成工程的建立.一直点击next,出现如下图界面后,点Finish完成工程的建立:二.编写HDL代码(工程此部分是在Implementation下完成的)1.在Sources区域点击右键选择new source,出现如下图所示的界面,按照如下图设置,然后一直点Next,一直到Finish完成代码文件界面:3.接下来开始HDL代码编写,这里是一个简单的十进制计数器的编写:代码编写好后,点击保存,然后检查看编写代码是否有错误,如上图所示,Check Syntax 点击检查后是绿色的勾,则代码没有语法错误,可以进行下一步功能仿真;module jishuqi(clk,rst,q);input clk,rst;output[3:0] q;reg[3:0] q;always@(posedge clk)beginif(rst==0)q<=4'b0;elsebeginif(q==4'b1010)q<=0;elseq<=q+1;endendendmodule三、行为(功能)仿真1.同样在Sources 区域右键添加New Source 如下图所示,添加图形仿真文件:2.一直点Next,最后finish掉到如下图所示的,时钟设置界面:如上图所示:1.选择Rising Edge 时钟上升沿有效;2.选择对应设计的时钟信号;3.设置clk的频率,高低电平持续时间;4.设置仿真时间为1000ns;3.点Finish进入波形编辑界面,如下图所示:(rst是要编辑的波形)编辑之后波形如下所示:点击保存;3.如下图选择:在Sources for 选择Behavioral Simulations4.依次点击1,2,然后双击,待运行后,最后出现如下图的仿真结果:到此时完成了行为仿真。

ISE使用

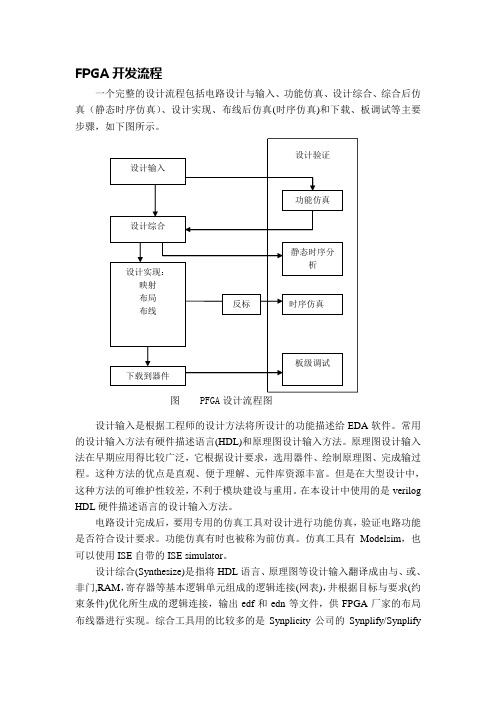

FPGA 开发流程一个完整的设计流程包括电路设计与输入、功能仿真、设计综合、综合后仿真(静态时序仿真)、设计实现、布线后仿真(时序仿真)和下载、板调试等主要步骤,如下图所示。

图 PFGA 设计流程图设计输入是根据工程师的设计方法将所设计的功能描述给EDA 软件。

常用的设计输入方法有硬件描述语言(HDL)和原理图设计输入方法。

原理图设计输入法在早期应用得比较广泛,它根据设计要求,选用器件、绘制原理图、完成输过程。

这种方法的优点是直观、便于理解、元件库资源丰富。

但是在大型设计中,这种方法的可维护性较差,不利于模块建设与重用。

在本设计中使用的是verilog HDL 硬件描述语言的设计输入方法。

电路设计完成后,要用专用的仿真工具对设计进行功能仿真,验证电路功能是否符合设计要求。

功能仿真有时也被称为前仿真。

仿真工具有Modelsim ,也可以使用ISE 自带的ISE simulator 。

设计综合(Synthesize)是指将HDL 语言、原理图等设计输入翻译成由与、或、非门,RAM ,寄存器等基本逻辑单元组成的逻辑连接(网表),井根据目标与要求(约束条件)优化所生成的逻辑连接,输出edf 和edn 等文件,供FPGA 厂家的布局布线器进行实现。

综合工具用的比较多的是Synplicity 公司的Synplify/Synplify 功能仿真设计输入 设计综合 设计实现:映射布局布线 下载到器件 静态时序分析反标 板级调试时序仿真 设计验证pro,以及各大FPGA厂商的集成开发环境中提供的综合工具,如Xilinx ISE中的XST。

使用Synplify/Synplify pro进行综合,该综合工具综合出的结果占用面积小、工作频率高,综合速度快。

综合完成后需要检查综合结果是否与原设计一致,需要做综合后仿真。

在仿真时,把综合生成的延时文件反标到综合仿真模型中去,可估计门延时带来的影响。

综合后仿真虽然比功能仿真精确一些,但是只能估计门延时,而不能估计线延时,仿真结果与布线后的实际情况还有一定的差距,并不十分难确。

利用ise联合modelsim几种仿真

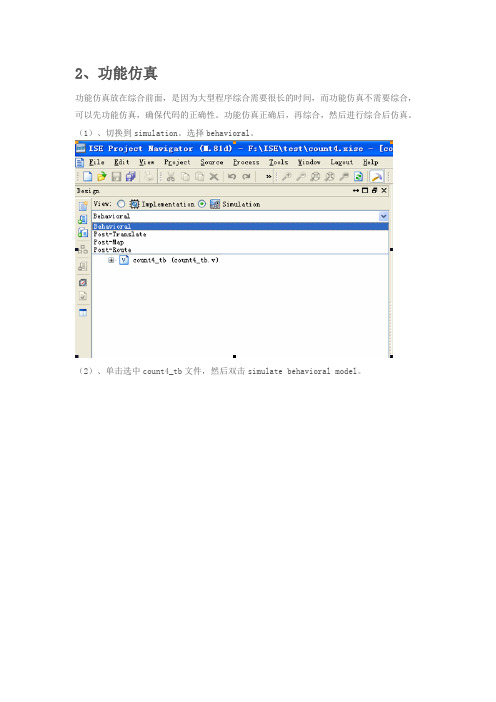

2、功能仿真功能仿真放在综合前面,是因为大型程序综合需要很长的时间,而功能仿真不需要综合,可以先功能仿真,确保代码的正确性。

功能仿真正确后,再综合,然后进行综合后仿真。

(1)、切换到simulation。

选择behavioral。

(2)、单击选中count4_tb文件,然后双击simulate behavioral model。

(3)、在modelsim,查看波形等内容。

3、时序(综合后)仿真时序仿真将时延考虑进去,包括综合后产生的(与、或、非)门时延,还有布局布线产生的时延。

综合(Synthesize),就是将HDL语言设计输入翻译成由与、或、非门和RAM、触发器等逻辑单元组成的网表。

综合后可生成综合后仿真模型(Generate Post-Synthesis Simulation Model)。

综合后,进行ISE的实现(Implement),包括翻译、映射、布局布线。

在这三个过程中都可以生成一个仿真模型(翻译和映射不会产生延时,因此常用布局布线后产生的仿真模型进行时序仿真)(1)、进行综合,双击 Synthesize – XST ,想生成 Post-Synthesis Simulation Model,双击Generate Post-Synthesis Simulation Model即可,会在工程文件夹下生成netgen\synthesis\count4_synthesis.v等文件(2)、进行实现,双击 Implement Design ,完成后,双击Generate Post-Place & Route Simulation Model.。

生成布局布线后仿真模型。

(3)、切换到 Simulation ,选中Post-route。

(4)、然后选中count4_tb文件,双击下面的Simulate Post-Place&Route Model,启动modelsim。

(5)、在modelsim中观察仿真波形。

FPGA设计开发软件ISE使用技巧之:编译与仿真设计工程

FPGA设计开发软件ISE使用技巧之:编译与仿真设计工程6.5 编译与设计工程编写代码完成之后,一个很重要的工作就是验证代码功能的正确性,这就需要对代码举行编译与仿真。

编译主要是为了检查代码是否存在语法错误,仿真主要为了验证代码实现的功能是否正确。

编译和仿真设计工程在囫囵设计中占有很重要的地位。

由于代码功能不正确或代码的编写风格不好对后期的设计会有很大的影响,所以需要花无数时光在设计工程的仿真上。

在这一节中将通过一个详细的实例来介绍如何对编译工程代码以及如何用法ISE自带的仿真工具ISE Simulator举行仿真。

1.编译工程代码编译主要是为了检测代码是否存在语法错误。

在ISE下,源代码的编写是在HDL Editor下完成的,但在HDL Editor下没有特地用于编译代码的选项。

不过在HDL Editor下完成代码的编写后,单击“保存”按钮,HDL Editor就会自动对代码举行编译。

假如代码存在语法错误,就会在信息显示窗中显示出来,用户可以按照显示的提醒,查找语法错误并修改。

6.17所示为在输写代码时遗忘分号,保存后就会有提醒信息。

当不存在错误时,提醒信息就不会浮现“Warning”。

ISE下对于代码的编译功能并不是很强大,有无数错误是检测不出来的。

例如在编写代码时,写case语句时漏写了end case语句,在HDL Editor下是检查不出来的。

但这些错误在仿真或综合阶段是可以检测出来的,因此即使完成了编译没有错误,也一定要举行仿真,检查是否还存在其他的错误。

2.仿真设计工程这里以一个详细的实例来介绍ISE下自带的仿真工具ISE Simulator 的用法,代码参见本书实例代码。

该例程的主要功能是按照拨码开关第1页共7页。

XilinxISE仿真步骤

module test1_test1_sch_tb();

// Inputs

reg ina;

reg inb;

// Output

wire outb;

wire outa;

reg clk;

reg clk1;

// Bidirs

// Instantiate the UUT

XilinxISE仿真步骤

1.建好原理图,或VHD等. 选择

;

2.选择后出现如图;

3.新建测试文件:;

4.在里面输入需要仿真的输入信号,如红字;

// V erilog test fixture created from schematic D:\test\test1.sch - Fri Nov 05 11:14:37 2010

xilinx ise仿真步骤 1.建好原理图,或vhd等.选择 ; 2.选择后出现如图; 3.新建测试文件:; 4.在里面输入需要仿真的输入信号,如红字; // v erilog test fixture created from schematic d:\test\test1.sch - fri nov 05 11:14:37 2010 `timescale 1ns / 1ps module test1_test1_sch_tb(); // inputs reg ina; reg inb; // output wire outb; wire outa; reg clk; reg clk1; // bidirs // instantiate the uut test1 uut ( .ina(clk), .inb(clk1), .outb(outb), .outa(outa) ); // initialize inputs initial begin clk = 0; clk1 = 0; ina = 0; inb = 0; #50000; $stop; end always #10 clk = ~clk; always #200 clk1 = ~clk1; endmodule 5.选中测试文件,双击 ,,检查语法错误,成功后,双击 弹出仿真界面; 7.点击放大, 观察波形. 下载文档原格式( word原格式 ,共3页)

基于ISE的数字秒表的设计与仿真

数字秒表设计实验报告学院(系):专业:学号:学生姓名:指导教师:目录摘要 (4)1 引言 (6)1.1FPGA的开发 (6)1.2VHDL语言的使用 (7)1.3 ISE简介 (8)1.4modelsim仿真软件的使用 (8)2 数字秒表的设计 (9)2.1 时间的概念 (9)2.2 实验任务及要求 (9)2.3 系统需求和解决方案 (10)2.3.1分频器设计 (12)2.3.2按键消抖电路设计 (12)2.3.3控制器设计 (13)2.3.4计数器设计 (13)2.3.5锁存器设计 (14)2.3.6扫描显示和控制电路设计 (14)2.3.7模块综合 (15)3 数字秒表的仿真结果 (15)3.1各仿真结果 (16)3.2分频器仿真 (16)3.3计数器仿真 (16)4实验结论 (16)参考文献 (17)附录 (17)摘要本次实验设计使用的软件ISE主要功能包括设计输入、综合、仿真、实现和下载,涵盖了可编程逻辑器件开发的全过程,从功能上讲,完成CPLD/FPGA的设计流程无需借助任何第三方EDA软件。

而本次设计目的在于设计一个可以自动计数、清零、锁存、暂停的、显示范围为59分59秒,精确度为百分之一秒的数字秒表并熟练利用modelsim仿真软件进行仿真并从中不断检验错误,修改程序达到学习提高的效果。

为达到实验目的,本设计分为:分频器,锁存器,计数器,控制器及消抖电路。

关键词:ISE;modelsim仿真;数字秒表设计;FPGA可编程逻辑器件;检验;学习AbstractThe ISE software used in experimental design the main function including design, implementation, integration, simulation and download, covers the whole process of the development of programmable logic devices, tell from the function, completed the design of CPLD/FPGA without using any third-party EDA software. And the purpose of the design is to design an automatic counting, reset, latches, suspended, display area for 59 minutes and 59 seconds, accuracy of one percent second digital stopwatch and skilled use of the modelsim simulation software simulation and continuous inspection error, modify the program to improve learning effect. For the purpose of the experiment, the design is divided into: frequency divider, latch, counter, controller and shake circuit.Key words: ISE; modelsim; digital stopwatch; The FPGA programmable logic devices;check;learn1引言在传统的硬件电路设计中, 主要的设计文件是电路原理图, 而采用硬件描述语言(VHDL) 设计系统硬件电路时主要使用VHDL 编写源程序。

第9章 设计实现和时序仿真

第9章 设计实现和时序仿真 -设置实现属性参数

图9.1 静态时序报告属性设置

第9章 设计实现和时序仿真 -设置实现属性参数

5、单击Post-Map Static Timing Report Properties类型; 6、将报告类型改为Verbose Report,这个报告将会在映 射完成之后产生; 7 7、单击Post-Place & Route Static Timing Report Post-Place Properties(布局布线后静态时序报告)类型; 8、将报告类型改为Verbose Report,这个报告将会在布 局布线完成之后产生; 9、单击Place & Route Properties类型; 10、如图9.2,将Place & Route Effort Level (Overall)设置 为High,这个选项将提高在实现过程中全局布局布线的水 平;

第9章 设计实现和时序仿真-实现过程概述 设计实现和时序仿真在ISE中的实现(Implement)过程,是将综合输出的逻 辑网表翻译成所选器件的底层模块与硬件原语,将设计映 射到器件结构上,进行布局布线,达到在选定器件上实现 设计的目的。 实现过程主要分为3个步骤:翻译(Translate)逻辑网 表,映射(Map)到器件单元与布局布线(Place & Route)。

第9章 设计实现和时序仿真-时序约束 设计实现和时序仿真当运行创建时序约束(Create Timing Constraints) 时,这时自动执行翻译步骤,然后打开约束编辑器。约束 编辑器的作用主要包括以下几个方面的内容: 1、编辑在原有UCF文件中的约束; 2、在设计加入新的约束; 约束编辑器中的输入文件包括: 1、NGD(Native Generic Database)文件 NGD文件为映射的输入文件,然后输出NCD (Native Circuit Description)文件; 2、UCF (User Constraint File)文件 默认情况下,当NGD文件打开后,那么使用现存的 UCF文件,当然也可重新指定UCF文件;

ise仿真步骤

八位全加器****************【转】ModelSim,synplify,ISE后仿真流程首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSi m后仿真的问题,那就可能是软件版本的问题。

1, ModelSim Se 6.1b2, Synplify Pro 7.5.13, ISE 5.2i (这个是老了点)4, WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

一、为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

以下凡是要根据自己系统环境改变的内容,我都会用红色标出,并加一个下划线。

编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。

ISE环境下基于Verilog代码的仿真测试

5

中要在测试代码中增加产生 10MHz 频率时钟的代码,可增添如下代码: always #50 F10M=~F10M;

同时,将 initial 模块的代码修改为如下: initial begin RESET=1; F10M=0; #100 RESET=0; #100 RESET=1; #10000 $stop; end

//实例引用,进行信号的连接

initial begin // Initialize Inputs RESET = 0; F10M = 0;

// Wait 100 ns for global reset to finish #100;

// Add stimulus here //需要增加测试代码的地方 end endmodule 从上面可以看出,ISE 自动生成了测试平台的完整架构,包括所需信号、端 口声明以及模块调用的完成。所需的工作就是在 initial…end 模块中的“// Add stimulus here”后面添加测试代码,并在其他地方进行相应的增添测试代码。本例

8

图 10 仿真结果

9

所示),对源代码进行综合,综合通过后表明源代码无语法错误且代码 可综合。如果综合不对,那么就需要修改源代码。

图 1 过程管理窗口中双击“Synthesize-XST”

第三步:综合通过后,接下去就可以利用 Verilog 语言来建立源代码的仿真测试 平 台 。 首 先 在 工 程 管 理 区 中 将 “Sources for” 设 置 为 Behavioral Simulation(打开下拉框选择),如图 2 所示。

图 2 工程管理区中将“Sources for”设置为 Behavioral Simulation

2

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

当仿真时间不确定不易计算定值时,可在testbench中加入$stop命令来控制仿真时间,随后运行时选择Run All即可。

标签: ISE Xilinx 时序仿真

ห้องสมุดไป่ตู้

使用ISE仿真器进行时序仿真

虽然ISE也同样支持使用ModelSim,但ISE既然自带了时序仿真工具,还是使用它本身的仿真工具来得快一些。

步骤基本如下:

大前提:先写好了功能模块和testbench文件,并且综合后没有问题。

(1)在Source下,选择Post-Route Simulation。

(5)Simulation Model Properties类:里面参数设置NetGen在生成仿真网表时使用的选项。(确保设置显示级别到Advanced。可默认使用默认仿真模型参数)

(6)ISE Simulator Properties类:里面参数设置仿真器运行时序仿真的相关选项。根据testbench文件中设置的仿真参数修改。

(7)单击OK,关闭Process Properties对话框。

(8)双击Simulate Post-Place & Route Model运行仿真。

注意事项:

当需要修改testbench文件时,需注意,我们之前是选择Add Cope of Source...所以修改原来文件是不会对仿真有什么改变的。

(2)将testbench文件添加进去。右键->Add Cope of Source...,选择testbench文件。

(3)在Source下选择testbench文件,在Processes下,单击Xilinx ISE Simulator展开。

(4)右键Simulate Post-Place & Route Model,选择Properties。