基于VHDL语言的简易洗衣机控制器

基于Verilog_HDL的洗衣机程序

EDA 嵌入式系统课程设计印刷学院课程设计报告——嵌入式系统EDA 课程设计名称:EDA 技术课程设计课程设计题目:洗衣机控制电路专业:电子信息工程专业班级:XX XXX学生姓名:XXXXXXXXXXXXXXXXXXXXXXXX指导老师:XXXXXXX时间:XXXXXX至XXXXX 年XXXX 月XXXX 日目录一、设计任务要求 (3)1、基本要求 (3)二、总体设计方案 (3)1、系统功能 (3)2、系统设计 (3)1)系统结构框图 (3)2)模块分析 (3)1、分频模块 (3)2、七段数码管显示模块 (3)3、洗衣机主程序模块 (3)三、应用设备及软件介绍 (3)1、主要仪器设备(实验用的软硬件环境) (3)2、实验的软件环境 (4)3、操作方法与实验步骤 (4)四、调试过程分析、遇到的问题及解决方法 (4)1、分频模块 (3)2、七段数码管显示模块 (3)3、洗衣机主程序模块 (3)五、设计结论 (3)六、DE2管脚分配说明 (3)七、参考文献 (3)八、附录 (3)附录一分频模块 (9)附录二七段数码管显示模块 (9)附录三洗衣机主程序模块 (9)一、设计任务要求1、基本要求:1)洗衣机的状态为待机5s→正转60s→待机5s→反转60s→,并用3个LED灯和7段显示器分别表示其工作状态和显示相应工作状态下的时间。

2)可自行设定洗衣机的循环次数,这里设置最大的循环次数为15次。

3)具有紧急情况的处理功能。

当发生紧急情况时,立即转入待机状态,紧急情况解除后,继续执行后续步骤。

4)洗衣机设定循环次数递减到零时立即报警,以表示洗衣机设定的循环次数已经结束。

二、设计方案1、系统功能基本功能:能够实现洗衣机在设置洗衣次数后待机5s→正转60s→待机5s→反转60s的四种基本状态,并且可显示循环次数,当遇到紧急状态时可打开紧急开关,暂停洗衣机的工作。

当洗衣机循环次数递减到0时洗衣机自动报警。

2、系统设计1)系统结构框图,如图1-1所示:通过分频模块得到1Hz clk作为标准时钟输入到洗衣机主程序模块中,rst,en,start,add,四个输入信号作为洗衣机主程序模块的总输入,所得到的led信号分别用三个红灯显示,alarm信号用一个红灯显示,numa 信号、numb信号、tim信号用七段数码管显示,最终实现了洗衣机的各项功能。

基于Verilog HDL的FPGA程序(智能洗衣机)

华中科技大学电子线路课程设计题目:智能洗衣机院系:控制科学与工程系班级:自动化100X班姓名:联系方式:fanjunchao1991@指导老师:目录一题目分析。

1二系统流程图.。

2三主要模块介绍.。

5四各按键功能.。

6 五仿真波形.。

7 六实验总结。

8 七附录。

9一:题目分析本次课程设计要求以Verilog HDL硬件描述语言为基础,以DE2开发板为工具,编写智能洗衣机的模拟程序。

首先,我在熟悉题目要求的前提下,将题目要求划分为以下几个小的项目,每个项目尽量用单独的模块实现其功能:①洗衣过程的转换:控制洗衣过程在每个过程对应的状态机之间转换,用control.v模块实现。

②洗衣时间的显示:通过直接调用上学期编写的24小时智能时钟程序的计时模块,并用总时间减去已用时间得到剩余时间,用led_show.v实现。

本程序的特色:①led灯表示水位:通过一定的算法,实现用led灯的亮灭表示水位。

Led依次点亮表示注水过程,相反,表示排水和甩干过程。

②1602 LCD液晶屏:用LCD显示所有操作步骤和过程,包括选择模式,当前洗衣模式和状态,洗衣完毕等。

这些过程都是用LCD液晶屏具体显示。

③按键使用和去抖:因为要使用按键进行模式的选择,所以我用软件去抖的方式实现按键按动时的去抖。

④暂停键模拟断电保护:设计了一个暂停键,模拟真实情况中的断电保护。

当暂停时模拟现实中的断电;暂停结束模拟现实中的重新上电,程序从断点继续运行。

二:系统流程图MODE 1 OR MODE 2 OR MODE 3:MODE 4MODE 5流程图说明:第一个为总的控制系统的流程图,后面三个为总流程图中,每种模式的详细流程图。

三:主要模块介绍module my_start:顶层模块,调用下层模块。

module HZ_1:分频模块,通过10分频和5分频将50Mhz分频成为1hz。

module control:控制模块,控制洗衣模式状态机的转换。

eda课程设计 基于VHDL 的 洗衣机控制器

子信息科学与技术专业课程设计任务书说明:本表由指导教师填写,由教研室主任审核后下达给选题学生,装订在设计(论文)首页1 设计任务及要求(1)设计一个洗衣机控制器,控制洗衣机如下运转:定时启动-正转20秒-暂停10秒-反转10秒-暂停10秒-定时未到回到“正转20秒-暂停10秒-……”,定时到停止;(2)若定时到,则停机发出音响信号;(3)用两个数码管显示洗涤的预置时间(分钟数),按倒计时方式对洗涤过程作计时显示,直到时间到停机;洗涤过程由“开始”信号开始;(4)三只LED灯表示“正转”、“反转”、“暂停”三个状态。

设计出的洗衣机控制器可以实现按预置的时间对衣服进行洗涤,并在结束后发出音响提示。

本次设计分工如下,有预置洗涤时间模块、倒计时减法计数器、状态控制模块、发出音响模块和译码模块。

2设计原理及总体框图(1)设计的总体框图(2)设计总原理洗衣机控制器的设计主要是定时器的设计。

由一片FPGA (Field Programmable Gate Array)和外围电路构成了电器控制部分。

FPGA接收键盘的控制命令,控制洗衣机的进水、排水、水位和洗衣机的工作状态、并控制显示工作状态以及设定直流电机速度、正反转控制、制动控制、起停控制和运动状态控制。

对FPGA芯片的编程采用模块化的VHDL (硬件描述语言)进行设计,设计分为三层实现,顶层实现整个芯片的功能。

顶层和中间层多数是由VHDL的元件例化语句实现。

中间层由无刷直流电机控制、运行模式选择、洗涤模式选择、定时器、显示控制、键盘扫描以及对直流电机控制板进行速度设定、正反转控制、启停控制等模块组成,它们分别调用底层模块。

3 程序设计(1)VHDL语言(VHSIC Hardware Description Language,甚高速集成电路硬件描述语言)是一种设计、仿真、综合的标准硬件描述语言,是对可编程逻辑器件进行开发与设计的重要工具,其优点是:支持自上而下和基于库的设计,支持范围广,具有多层次描述系统硬件功能的能力。

洗衣机VHDL控制器实验报告

数字电路和逻辑设计综合实验实验报告实验名称:洗衣机控制器班级:班内序号:姓名:学号:数电设计综合实验—洗衣机控制器一.设计课题的任务要求设计制作一个全自动洗衣机的控制器:●洗衣机的工作步骤为洗衣、漂洗和脱水三个过程,工作时间分别为:洗衣20秒,漂洗30 秒,脱水15 秒;●用一个按键实现洗衣程序的手动选择:A、单洗涤;B、单漂洗;C、单脱水;D、漂洗和脱水;E、洗涤、漂洗和脱水全过程;●用显示器件显示洗衣机的工作状态(洗衣、漂洗和脱水),并倒计时显示每个状态的工作时间,全部过程结束后,应提示使用者;●用一个按键实现暂停洗衣和继续洗衣的控制,暂停后继续洗衣应回到暂停之前保留的状态;●选做:三个过程的时间有多个选项供使用者选择。

●选做:可以预约洗衣时间。

●选做:自拟其它功能。

二.系统设计(包括设计思路、总体框图、分块设计)◆设计思路首先从题目进行分析,采用VHDL模块化的设计方法来进行洗衣机控制器的设计,即自顶向下,从系统总体要求出发,自上至下地将设计任务分解为不同的功能模块.最后将各功能模块连接形成顶层模块,完成系统硬件的整体设计。

本控制器基本功能描述洗衣机控制器可工作于五种模式下:单洗涤、单漂洗、单脱水、漂洗十脱水、洗涤十漂洗+脱水,可以使洗衣机控制器工作在任意一种模式,并显示出洗衣机的工作状态和剩余工作时间,在剩余时间结束后有报警声提示使用者,并且可实现暂停洗衣和继续的功能,此外,加入附加功能,可自选三个过程是使用时间并且可预约洗衣时间。

由此分析可将洗衣机控制器分为控制模块、倒计时模块,初始模式选择模块,报警模块,洗衣时间选择模块,选通译码模块和分频器模块。

【设计过程】:1)审题,初步确定思路。

2)用VHDL语言进行编程。

3)适时对程序进行修改。

4)编译成功后,进行仿真,观察波形图。

5)将程序下载到实验板上,调试各功能。

6)通过计算机仿真和下载调试,发现问题,返回原程序进行修改。

7)进行总体的调试。

基于VHDL的洗衣机控制器设计说明

数字系统设计与硬件描述语言期末考试作业题目:洗衣机控制器的设计学院:电子信息工程学院专业:物联网工程学号:3014204328姓名:刘涵凯2016-12-10一、选题设计描述1.功能介绍洗衣机控制器,能够实现开始与暂停、注水,洗涤、排水、脱水和警报提醒的功能,并且可以随时更改洗衣模式。

洗衣机提供两种模式:模式1:注水-洗涤-排水-注水-洗涤-排水-脱水;模式2:脱水。

洗衣模式决定洗衣时间。

默认模式为模式2。

洗衣机界面如下图所示:运转方式如下图所示:2.算法简介总程序描述:总程序通过调用5种模块,在洗衣机控制器输入变化时,立刻转换模式并产生对应输出。

当开关关闭时,所有输出为0;暂停时,除显示开关状态的输出外,所有输出为0。

开关开启后,设置洗衣模式,之后按下“开始”即可开始工作。

在洗衣机控制器输入变化时,立刻转换模式并产生对应输出。

电子元器件模型如下图所示:switch为开关信号,modelselect为开关选择信号,clkin为系统时序脉冲信号,sorp为开始/暂停信号。

waterstate为注水程序的工作状态,washrstate为洗涤程序的工作状态,drainstate为排水程序的工作状态,drystate为脱水程序的工作状态。

alarmout为警报提醒的状态。

switchstate为数码管显示的开关的状态(0/1),spstate为数码管显示的开始/暂停的状态(0/1),state为数码管显示的洗衣机工作状态(0~4),currentmodel为数码管显示的当前模式(0~2),timedecade为数码管显示的剩余时间的十位,timeunit为数码管显示的剩余时间的个位。

下面介绍各模块功能与算法:1)开关与模式选择模块a接收开关信息,b接收模式选择信息。

c输出总电路的开关信息(开启洗衣机并且设置完毕电路后,即可准备工作,等待“开始”信号)。

e为开关信息,将输入到数码管中显示。

time1与time2分别代表洗衣时间的十位和个位,将输入到计数器与警报模块中。

EDA设计基于VHDL的简易全自动控制洗衣机

华东理工大学2009 -2010 学年第2学期《电子综合设计DEA》课程设计作业 2010.6班级:XXXX 学号: XXX 姓名:XXXX电子综合设计EDA综合设计题设计一简易全自动洗衣机控制器。

该控制器由两大状态A和B组成,每个状态分三个子状态,每个状态分别由选择A和选择B控制。

其中A为步进选择按纽,每步跳转一个子状态、B也为步进选择按纽,但每步选择B中的所有组合中的一种。

当启动时,时间序列控制器按已选的B类子状态顺序执行。

过程启动由启动/暂停键控制(暂停键在过程启动后任意时间可暂停/恢复过程)过程启动后机盖开启应均能暂停过程,复盖间停30秒后重新继续原过程。

A:强洗标准弱洗B:洗涤漂洗甩干(脱水)(洗涤,漂洗时电机分别正转、反转)强洗:(共36分钟)洗涤 18分漂洗 14分甩干 4分(洗涤时电机分别正转4分、反转4分,正反转间停30秒;漂洗时电机分别正转3分、反转3分,正反转间停30秒;甩干时电机分别正转1.5分,间停30秒)标准:(共26分钟)洗涤 14分漂洗 8 分甩干 4分(洗涤时电机分别正转3分、反转3分,正反转间停30秒;漂洗时电机分别正转1.5分、反转1.5分,正反转间停30秒;甩干时电机分别正转1.5分,间停30秒)弱洗(共20分钟)洗涤 10分漂洗 6分甩干4分(洗涤时电机分别正转2分、反转2分,正反转间停30秒;漂洗时电机分别正转1分、反转1分,正反转间停30秒;甩干时电机分别正转1.5分,间停30秒)设定秒脉冲已给定,指示为LED,整过程完成后,蜂鸣器响30秒。

整个设计为正逻辑。

一、程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY student ISPORT(COUNT_N,COUNT_M,START,COOK,CLK:IN STD_LOGIC;LOOK:OUT STD_LOGIC;DOUT :OUT STD_LOGIC_VECTOR(1 DOWNTO 0));END STUDENT;ARCHITECTURE BEHAV OF student ISSIGNAL DT1,DT2:STD_LOGIC_VECTOR(1 DOWNTO 0);SIGNAL DICSOUNT,TEM:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DCP:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL CT:STD_LOGIC_VECTOR(5 DOWNTO 0);SIGNAL CT1,CT2:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL SG,CMKS:STD_LOGIC;BEGINPROCESS(COUNT_N,SG)BEGINIF SG='1' THENDT1<="00";ELSIF COUNT_N'EVENT AND COUNT_N='1' THENIF DT1=3 THENDT1<="01";ELSEDT1<=DT1+1;END IF;END IF;END PROCESS;PROCESS(COUNT_M,SG)BEGINIF SG='1' THENDT2<="00";ELSIF COUNT_M'EVENT AND COUNT_M='1' THENIF DT2=3 THENDT2<="01";ELSEDT2<=DT2+1;END IF;END IF;END PROCESS;PROCESS(START)BEGINIF SG='1' THENCMKS<='0';ELSIF START'EVENT AND START='1' THENDICSOUNT<=DT1&DT2;CMKS<=CMKS XOR '1';END IF;END PROCESS;PROCESS(CLK,START,COOK)BEGINIF START='1' AND DCP="0000" THENDCP<=DICSOUNT;ELSIF CLK'EVENT AND CLK='1' THENIF COOK='1' THENDOUT<="00";ELSIF START='1' AND DCP>"0000" THENDOUT<="00";ELSIF SG='1' THENIF CT1<"0001" THENCT1<="0000";SG<='0';END IF;ELSIF CMKS='1' THENCASE DCP ISWHEN "0101"=>IF CT<35 THENCT<=CT+1;IF CT1<8 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=8 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<8 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=8 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="0110";CT<="000000";CT1<="0000";CT2<="0000";DOUT<="00";END IF;WHEN "0110"=>IF CT<27 THENCT<=CT+1;IF CT1<6 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=6 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<6 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=6 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="0111";CT<="000000";CT1<="0000";CT2<="0000";DOUT<="00";END IF;WHEN "0111"=>IF CT<8 THENCT<=CT+1;IF CT1<3 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=3 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<3 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=3 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="0000";CT<="000000";CT1<="0000";CT2<="0000";SG<='1';END IF;WHEN "1001"=>IF CT<27 THENCT<=CT+1;IF CT1<6 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=6 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<6 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=6 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="1010";CT<="000000";CT1<="0000";CT2<="0000";DOUT<="00";END IF;WHEN "1010"=>IF CT<15 THENCT<=CT+1;IF CT1<3 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=3 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<3 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=3 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="1011";CT<="000000";CT1<="0000";CT2<="0000";DOUT<="00";END IF;WHEN "1011"=>IF CT<8 THENCT<=CT+1;IF CT1<3 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=3 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<3 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=3 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="0000";CT<="000000";CT1<="0000";CT2<="0000";SG<='1';END IF;WHEN "1101"=>IF CT<19 THENCT<=CT+1;IF CT1<4 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=4 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<4 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=4 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="1110";CT<="000000";CT1<="0000";CT2<="0000";DOUT<="00";END IF;WHEN "1110"=>IF CT<11 THENCT<=CT+1;IF CT1<2 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=2 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<2 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=2 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="1111";CT<="000000";CT1<="0000";CT2<="0000";DOUT<="00";END IF;WHEN "1111"=>IF CT<8 THENCT<=CT+1;IF CT1<3 THENDOUT<="01";CT1<=CT1+1;ELSIF CT1=3 THENDOUT<="00";CT1<=CT1+1;ELSIF CT2<3 THENDOUT<="10";CT2<=CT2+1;ELSIF CT2=3 THENDOUT<="00";CT1<="0000";CT2<="0000";END IF;ELSEDCP<="0000";CT<="000000";CT1<="0000";CT2<="0000";SG<='1';END IF;WHEN OTHERS=>DOUT<="00";END CASE;END IF;END IF;END PROCESS;LOOK<=SG;END BEHAV;二、仿真波形如下强洗全部过程强洗漂洗、甩干强洗(甩干)标准全部过程标准(漂洗、甩干)标准(甩干)弱洗(漂洗、甩干)九、弱洗(甩干)一、强洗强开盖一、标准强开盖二、弱洗强开盖暂停和启动一、强洗暂停二、强洗重新启动三、标准暂停四、标准重新启动五、弱洗暂停六、弱洗重新启动两次洗衣: 两次强洗两次标准(漂洗、甩干)一、两次弱甩三、设计思想讨论设计时参考了已有程序,此芯片有五个输入和三个输出,输入COUNT_M和输入COUNT_N是状态控制键,输入START是输入启动和暂停键,以及一个时钟CLK。

VHDL洗衣机设计说明

EDA课程实训报告一、实训课题:洗衣机控制器的设计二、设计的内容及要求:1.设计一个洗衣机控制器,要求为:1) 洗衣机控制器可以驱动洗衣机进行洗涤、漂洗或烘干;2) 洗衣机控制器可以设置洗衣机的工作时间,工作时间最短1分钟,最长30分钟,在工作过程中,工作时间以倒计时显示,若时间为0洗衣机停止工作;3) 洗衣机在待机状态时,洗衣机控制器可以设置洗衣机的工作方式和工作时间;4) 可以暂停或停止洗衣机工作;5) 利用四个数码管显示洗衣机待机时的设置时间和工作时的运行时间,利用一位数码管显示洗衣机待机时所设置的工作方式运行时的工作方式;6)利用三个LED分别表示驱动洗衣机进行洗涤、漂洗或烘干。

2.洗衣机控制器可以划分为状态机模块、计时器模块、设置模块和显示选择模块。

在QuartusII 中输入各个模块的代码,编译综合,仿真,完成各个模块的软件设计;4.把各个模块组合起来,综合编译,仿真,完成整个交通灯控制器系统的软件设计;5. 选择电路方案锁定管脚,把程序下载到实验箱中,利用实验箱进行硬件实现;6. 完成实训报告。

实训报告包括:1)设计的任务和要求;2)模块的划分和系统总框图;3)各个模块的实现,包括模块的作用,模块的输入与输出情况,模块状态图,模块的代码以及注释,模块的波形图;4)系统的实现,包括系统总原理图,系统的波形图;5)管脚的锁定关系;三.设计思路:◆状态切换>>>有限状态机◆按定时时间及时>>> 定时计数器◆显示时间>>> 数码管译码驱动器◆接收设置时间>>>时间设置键盘扫描器◆接收设置模式>>> 模式设置键盘扫描器◆切换显示运行时间和设置时间>>>二路选择器◆切换显示运行模式和设置模式>>>二路选择器整体设计示意图:四.系统组成以及系统各部分的设计:1.状态机的设计:状态机要完成的功能:●能设置工作模式;●控制洗涤、漂洗、干衣的驱动输出;●能启动、暂停、停止洗衣机控制器;●能重启、暂停和停止定时器;●能接收定时器的到时标志;●能使能键盘扫描计数器;●能控制二路选择器。

利用WHDL设计洗衣机控制器

利用VHDL设计洗衣机控制器1 引言2 选题研究的意义2.1 课题来源2.2 课题研究的背景2.3 研究的目的和意义.4 应解决的主要问题及应达到的技术要求2.4.1 需解决的主要问题洗衣机控制系统的核心部件是控制器。

洗衣机控制电路包括控制器、控制对象、状态显示电路、计时器及报警电路。

它是一闭环系统,内部结构有洗衣机状态转换时间信号产生器、状态计数器、数据选择器和状态译码器,它能自动发出顺序循环控制信号(S、R、L),并同时完成在该状态下的计时功能。

另外,它还向控制对象提供一个工作过程的周期信号(T),作循环次数累计。

控制对象是由4位二进制计数器和4位数值比较器构成,它对T作计数,与此同时与人工输入的预置循环数比较,随时将反应受控器自身状态的信号反馈给控制器,从而实现系统的控制功能。

2.4.2 需实现洗衣机控制器的控制功能⑴洗衣机的状态为待机5s→正转60s→待机5s→反转60s,并用3个LED灯和7段显示器分别表示其工作状态和显示相应工作状态下的时间。

⑵自行设定洗衣机的循环次数,这里设最大的循环次数为15次。

⑶具有紧急情况的处理功能。

当发生紧急情况时,立即转入到待机状态,紧急情况解除后继续执行后续步骤。

⑷洗衣机设定循环次数递减到零时立即报警,以表示洗衣机设定的循环次数已经结束。

⑸输入变量:时钟CLK,直接清零RD,暂停/连续EN,设定洗衣机的循环次数SET。

⑹输出变量:三个工作状态S、R、L,一个过程周期T(T4),8421BCD码Q7…Q0输出及报警信号。

2.5 国内外研究现状,发展趋势及存在的主要问题2.6设计工具介绍3 洗衣机控制器设计的方案论证3.1 洗衣机控制器设计的方案选择设计洗衣机控制器,通常可以用三种方法来实现。

方法一,可以用纯机械式来设计控制器。

本方法利用机械原理来设计定时器。

例如可以利用弹簧储存能量和释放能量的过程得到定时时间。

其原理如同机械式(上发条)的钟表。

由于长时间工作,金属容易疲劳,一旦出现这样的情况,其定时的误差变大,导致定时不准确。

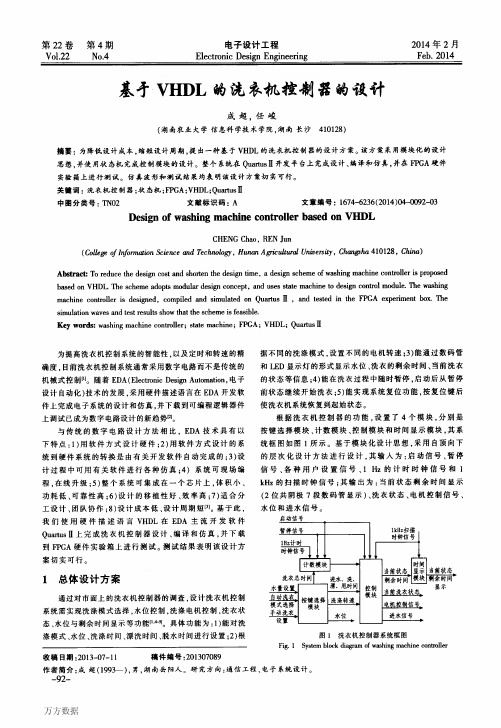

基于VHDL的洗衣机控制器设计

Th De n O a h e sg fW s erCo to l r nrl e

bas or ed 1 VHDL

LI BoW ANG , Zha -ui AO Yib ng r , G ・o

( o twe tP toe m ie st,Ch n u S u h s er lu Unv ri y egd 60 0 ,Chn ) 150 i a

文章编号: 1 711 4 ( O 7 O - O 7 O -0 12 O )6 O 5 -2 6

I】梁星彦 。和卫星 .L b iw实现 远程数据采集与传输 .20 3 a ve 04 【】周求湛 ,钱志鸿 ,刘萍萍 . 4 虚拟仪器与 L b I wT 7 E pe s a V E M x rs 程 序设计 . 北京 :北京航 空航天大学 出版 社, 2 0 。8—9 . 041 91 1 作者 简介:张聪玲.女,天津工业 大学信息与通信工程学院硕士研 究生;王 金海。 男,教授 ,天 津工业大学信息 与通信工程学院副院长 :姚银花 ,女 , 天津工业大学信 息与通信 工程学院硕 士研究生

关键词 :V D ; H L 控制 器:模块化设计 :状态机 中图分类号: T 2 .3 文献标识码: A M9 53

设置异常 的工作时间时,洗衣机发出警告后 ,就会 自动调整用户设 定 的工作时间。

2 控制器 的模块化设计

根据洗衣机 控制器 功能的描述 ,可将洗衣机控 制器划分为若千 功能模块。如图 l 所示.其中状态机模块的设计是关键 .它控制着 整个系统的_作 过程 .包括控 制各状态间的转换.各模块的启用 与 T 停止,是系统的核心部分 。

维普资讯

仪器仪表用户

T P 传送 ,完 全可以应用到 分布 式的现场监控 中。本方法利用现 . C 存的 It n t网络可 以有效提高资源 的使用率 、削减应用成本 ,而 ne e r 实现采用面向连接 的传输模式,更能保证数据传送 的正确性 。

Verilog数字电子技术-洗衣机控制器

Verilog数字电子技术-洗衣机控制器2010学年度第一学期电子技术基础课程设计——智能洗衣机控制器院系: 控制科学与工程系专业: 自动化班级: 1006班姓名: ******* 学号: ********指导教师:课程设计名称智能洗衣机控制器的设计设计内容及要求设计一个智能洗衣机控制器~能够实现洗衣~漂洗和脱水的功能。

要求能够使用按键模拟对洗衣机的控制~能够设置工作模式~为了便于观察~将洗衣机设定的工作模式(1~5)和整个过程所剩的工作时间用数码管显示出来(时间分辨率为1分钟)~能够将洗衣机当前所处的状态,注水~洗衣~排水~甩干,用发光管或者数码管显示出来。

【模式1】: 洗衣模式,,强力洗, 洗衣30分钟, 【模式2】 :洗衣模式,,普通洗 ,洗衣20分钟, 【模式3】 :洗衣模式,,轻柔洗,洗衣10分钟, 【模式4】 :漂洗模式【模式5】 :甩干模式注:在以上5个模式中~每次注水1分钟~漂洗5分钟~排水1分钟,甩干1分钟~模式1,3的洗衣时间如上所示~具体的洗衣步骤如下:【模式1,3】:注水->洗衣->排水->甩干->注水->漂洗->排水->甩干->注水->漂洗->排水->甩干。

【模式4】:注水->漂洗->排水->甩干->注水->漂洗->排水->甩干。

【模式5】:甩干。

【要求】:实现逻辑控制过程~可以选择性的加入注水口无水报警等人性化的状态提示~操作完毕使用蜂鸣器鸣叫两秒提示。

画出洗衣机控制器的状态机~写出状态编码方案。

用Verilog语言对设计进行描述~设计一个测试方案~并能够下载到实验板上调试成功。

写出设计性实验报告~并打印各层次的源文件和仿真波形~然后作简要说明。

并谈谈此次实验的收获、感想及建议系统设计1 系统框图与说明本次设计的重点在于智能控制器状态之间转换的条件和关系~并且在此基础上输出相应的显示。

VHDL语言的洗衣机控制器设计

目录一、目的 (2)二、内容及要求 (2)1、设计的主要内容 (2)2、设计的主要要求 (3)三、原理 (3)1.基于状态机的控制电路设计 (3)2.洗衣机控制器的工作原理 (3)(1)洗衣机的工作状态 (3)(2)全自动洗衣过程 (4)(3)单独执行某个洗衣程序 (4)(4)设计思路 (5)四、步骤及仿真图 (7)五、程序设计 (10)(1)时钟分频模块 (10)(2)数码管显示 (11)(3)定时器电路 ......................................................................................................... 12。

(4)预置时间和编码电路 (13)(5)时序电路 (13)(6)译码器 (14)六、心得体会 (14)七、参考文献 (15)一、目的1.学习掌握全自动洗衣机的控制原理。

2.掌握基于有限状态机的控制电路设计方法.二、内容及要求1、设计的主要内容:设计一个全自动洗衣机控制器电路,实现对洗衣机的全自动控制。

根据全自动洗衣机的控制原理设计一个控制电路,使之能够控制全自动洗衣机完成整个工作过程。

洗衣机工作过程分为两种情况:(1)全部自动完成当按下复位按钮时,洗衣机上电,控制电路复位到初始状态(默认水位为“中”;使用)者可根据衣服的多少,按下水位控制按钮,改变水位设置,以控制上水时加水的多少;当按下启动/暂停按钮时,洗衣机开始洗衣的第一个操作:进水阀门打开,开始上水,并根据水位设置(高、中、低、少)历时不同的时间timeadd(8s、7s、6s、5s);然后进水阀门关闭,电机开始运转,开始洗衣过程,并历时 9s;然后电机停止运转,排水阀门打开,开始排水,并根据水位设置(高、中、低、少)历时不同的时间timedrain(7s、6s、5s、4s);然后排水阀门关闭,进水阀门打开,开始第二次上水,并历时timeadd……当甩干结束后,整个洗衣过程完成,扬声器发出持续 15 秒的急促的“嘀嘀”音,提示用户洗衣结束。

简易洗衣机VHDL程序

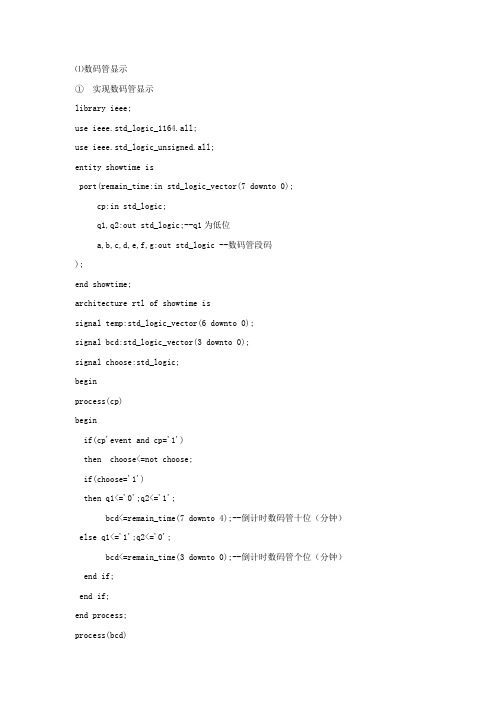

⑴数码管显示①实现数码管显示library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity showtime isport(remain_time:in std_logic_vector(7 downto 0);cp:in std_logic;q1,q2:out std_logic;--q1为低位a,b,c,d,e,f,g:out std_logic --数码管段码);end showtime;architecture rtl of showtime issignal temp:std_logic_vector(6 downto 0);signal bcd:std_logic_vector(3 downto 0);signal choose:std_logic;beginprocess(cp)beginif(cp'event and cp='1')then choose<=not choose;if(choose='1')then q1<='0';q2<='1';bcd<=remain_time(7 downto 4);--倒计时数码管十位(分钟) else q1<='1';q2<='0';bcd<=remain_time(3 downto 0);--倒计时数码管个位(分钟) end if;end if;end process;process(bcd)begincase bcd is -–(段码表)when "0000"=> temp<= "1111110" ;when "0001"=> temp<= "0110000" ;when "0010"=> temp<= "1101101" ;when "0011"=> temp<= "1111001" ;when "0100"=> temp<= "0110011" ;when "0101"=> temp<= "1011011" ;when "0110"=> temp<= "1011111" ;when "0111"=> temp<="1110000" ;when "1000"=> temp<="1111111" ;when "1001"=> temp<= "1111011" ;when others=>temp<="1111011";end case;a<=temp(6);b<=temp(5);c<=temp(4);d<=temp(3);e<=temp(2);f<=temp(1);g<=temp(0);end process;end rtl;○2数码管显示编码--bcd编码为数码管显示编码library ieee;use ieee.std_logic_1164.all;entity encode isport(bcd : in std_logic_vector(3 downto 0);a,b,c,d,e,f,g: out std_logic);end encode;architecture rtl of encode issignal temp:std_logic_vector(6 downto 0);begintablebcd => temp;"0000"=> "1111110" ;"0001"=> "0110000" ;"0010"=> "1101101" ;"0011"=> "1111001" ;"0100"=> "0110011" ;"0101"=> "1011011" ;"0110"=> "1011111" ;"0111"=> "1110000" ;"1000"=> "1111111" ;"1001"=> "1111011" ;end table;a<=temp(6);b<=temp(5);c<=temp(4);d<=temp(3);e<=temp(2);f<=temp(1);g<=temp(0); end rtl;⑵时序电路控制洗衣机按的顺序运行,待机5秒,正转10秒,待机5秒,反转10秒,直到时间结束信号的到来library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity shixu isport(cp,en,rd:in std_logic;q1,q2:out std_logic--00为停机,10为正转,01为反转);end shixu;architecture rtl of shixu isbeginprocess(cp)variable wash_time:integer range 0 to 9;variable wait_time:integer range 0 to 4;variable state:std_logic; --0代表正转,1代表反转variable wash_time:integer := 11;--变量赋值variable wait_time:integer := 4;beginif(en='0')wash_time:='9';wait_time:='4';state:='0';end if;if(en='0')then wash_time:=21;Q1<='0';Q2<='0';--停机状态else if(cp'event and cp='1')then if(rd='1')then if(wash_time>0)then wash_time:=wash_time-1;wait_time:=4;--等待时间恢复elseif(wait_time>0)--运行时间结束,等待时间未到 then wait_time:=wait_time-1; --等待时间减1 else wash_time:=10; --等待时间结束,继续运行 state:=not state; end if;end if;-- end if; 将译码也加入同步时序,可以减少毛刺if(wash_time=0)then Q1<='0';Q2<='0';--暂停else if(state='0')--正转then Q1<='1';Q2<='0';else Q1<='0';Q2<='1';--反转end if;end if;else Q1<='0';Q2<='0';--暂停end if;end if;end if;end process;end rtl;⑶预置时间和编码电路--预置时间与编码寄存电路,将输入的1-10分钟编为2个4位的BCD码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity settime isport(load:in std_logic;k:in std_logic_vector(9 downto 0);o:out std_logic_vector(7 downto 0));end settime;architecture rtl of settime issignal p1:std_logic_vector(7 downto 0);beginprocess(load)beginif(load'event and load='1')then --开始译码case k is --将时间分钟when "1000000000"=>p1<="00000001";when "010*******"=>p1<="00000010";when "0010000000"=>p1<="00000011";when "0001000000"=>p1<="00000100";when "0000100000"=>p1<="00000101";when "0000010000"=>p1<="00000110";when "0000001000"=>p1<="00000111";when "0000000100"=>p1<="00001000";when "0000000010"=>p1<="00001001";when "0000000001"=>p1<="00010000";when others=>p1<="00000000";end case;end if;end process;o<=p1;end rtl;⑷译码器--将时序电路的信号翻译为暂停,正转,反转library ieee;use ieee.std_logic_1164.all;entity decoder isport(Q1,Q2: in std_logic;REV,RUN,PAUSE: out std_logic--rev反转,run正转,pause暂停 );end decoder;architecture rtl of decoder is--signal choose:std_logic_vector(1 downto 0);beginchoose(1)<=q1;choose(0)<=q2;process(choose)begincase choose iswhen "00"=>REV<='0';RUN<='0';PAUSE<='1';when "10"=>REV<='0';RUN<='1';PAUSE<='0';when "01"=>REV<='1';RUN<='0';PAUSE<='0';when others=>REV<='0';RUN<='0';PAUSE<='0';end case;end process;REV<=Q2;RUN<=Q1;PAUSE<=not(Q1 OR Q2);end rtl;⑸定时器电路①计时器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity b2d isport(time_in,clk:in std_logic_vector(9 downto 0); time_out:BUFFER STD_LOGIC_VECTOR(15 DOWNTO 0); );end b2d;architecture rtl of b2d isbeginprocess(clk)variable time_temp:intbeginif(clk'event and clk='1')then if(start='0')then time_remain<=k;--k为分钟数else if(time_remain>0)--防止时间无限计数then time_remain<=time_remain-start;--只有开始时候才开始计时 end if;end if;end if;if(time_remain=0)--时间是否结束的判定then time_is_up<='0';else time_is_up<='1';end if;end process;end rtl;②减法计数器--十进制BCD码减法计数器,实现输入的为分钟数,每隔60秒计数器减1 library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter isport(clk,start:in std_logic;k:in STD_LOGIC_VECTOR(7 downto 0);time_remain:BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0);time_is_up:out std_logic);end counter;architecture rtl of counter isbeginprocess(clk)variable time_second:integer:=60;--integer为整数variable time_second:integer:=0;beginif(clk'event and clk='1') --检测上升沿触发thenend if;--秒表计数的实现if(time_second>0 and start='1')then time_second:=time_second-1;else time_second:=59;end if;--装载时间并将秒赋值if(start='0')thentime_remain<=k;time_second:=60;time_second:=0;elseif(time_second=0)then if(time_remain(3 downto 0)>0)--防止时间无限计数then --time_remain(3 downto 0)<=time_remain(3 downto 0)-start;--只有开始时候才开始计时--上条语句执行实际结果为减3,原因未明time_remain(3 downto 0)<=time_remain(3 downto 0)-1;time_second:=59;else if(time_remain(7 downto 4)>0)then --time_remain(7 downto 4)<=time_remain(7 downto 4)-start;time_remain(7 downto 4)<=time_remain(7 downto 4)-1;time_remain(3 downto 0)<="1001";time_second:=59;end if;end if;else --if(time_second=0 and time_second=1) --以下语句除脉冲上升沿语句之外将产生毛刺if(time_remain=0)--时间是否结束的判定then time_is_up<='0';else time_is_up<='1';time_second:=time_second-1;--秒表计数的实现end if;end ifend if;end if;end process;end rtl;。

VHDL洗衣机设计

EDA课程实训报告一、实训课题:洗衣机控制器的设计二、设计的容及要求:1.设计一个洗衣机控制器,要求为:1) 洗衣机控制器可以驱动洗衣机进行洗涤、漂洗或烘干;2) 洗衣机控制器可以设置洗衣机的工作时间,工作时间最短1分钟,最长30分钟,在工作过程中,工作时间以倒计时显示,若时间为0洗衣机停止工作;3) 洗衣机在待机状态时,洗衣机控制器可以设置洗衣机的工作方式和工作时间;4) 可以暂停或停止洗衣机工作;5) 利用四个数码管显示洗衣机待机时的设置时间和工作时的运行时间,利用一位数码管显示洗衣机待机时所设置的工作方式运行时的工作方式;6)利用三个LED分别表示驱动洗衣机进行洗涤、漂洗或烘干。

2.洗衣机控制器可以划分为状态机模块、计时器模块、设置模块和显示选择模块。

在QuartusII 中输入各个模块的代码,编译综合,仿真,完成各个模块的软件设计;4.把各个模块组合起来,综合编译,仿真,完成整个交通灯控制器系统的软件设计;5. 选择电路方案锁定管脚,把程序下载到实验箱中,利用实验箱进行硬件实现;6. 完成实训报告。

实训报告包括:1)设计的任务和要求;2)模块的划分和系统总框图;3)各个模块的实现,包括模块的作用,模块的输入与输出情况,模块状态图,模块的代码以及注释,模块的波形图;4)系统的实现,包括系统总原理图,系统的波形图;5)管脚的锁定关系;三.设计思路:◆状态切换>>>有限状态机◆按定时时间及时>>> 定时计数器◆显示时间>>> 数码管译码驱动器◆接收设置时间>>>时间设置键盘扫描器◆接收设置模式>>> 模式设置键盘扫描器◆切换显示运行时间和设置时间>>>二路选择器◆切换显示运行模式和设置模式>>>二路选择器整体设计示意图:四.系统组成以及系统各部分的设计:1.状态机的设计:状态机要完成的功能:●能设置工作模式;●控制洗涤、漂洗、干衣的驱动输出;●能启动、暂停、停止洗衣机控制器;●能重启、暂停和停止定时器;●能接收定时器的到时标志;●能使能键盘扫描计数器;●能控制二路选择器。

基于VHDL语言的简易洗衣机控制器

电子课程设计——简易洗衣机控制器设计学院:班级:姓名:学号:指导老师:2013年12月目录第一部分:设计任务与要求 (1)第二部分:总体框图 (1)第三部分:选择器件 (2)第四部分:功能模块 (3)4.1时间预置编码寄存模块(settime) (3)4.2减法计数器模块(counter) (4)4.3数码管显示模块(showtime) (7)4.4时序电路模块(analyse) (9)4.5译码器模块(move)………………………………………1 1 第五部分:总体设计电路图 (13)5.1总体(顶层)设计电路图 (13)5.2顶层文件仿真 (13)5.3管脚分配图 (14)5.4硬件实验效果图 (14)第六部分:课程设计心得体会 (15)简易洗衣机控制器设计一、设计任务与要求设计一个洗衣机洗涤程序控制器,控制洗衣机的电动机按下图所示的规律运转:用两位数码管预置洗涤时间(分钟数),洗涤过程在送入预置时间后开始运转,洗涤中按倒计时方式对洗涤过程作计时显示,用LED 表示电动机的正、反转,如果定时时间到,则停机并发出音响信号。

二、总体框图RUN REV PAUSEK5K6K1 K2 K3 K4各个部分的具体功能描述如下:(一)预设时间和编码电路(settime ):接受用户通过按钮预置的时间信息,编码成八位之后转给减法计数器。

(二)减法计数器电路(counter):接收编码之后的预置时间信息,向电机运转控制电路传递运行信号,并将预置时间信息和剩余时间信息发给数码管显示电路进行实时显示。

(三)数码管显示电路(showtime):接收减法计数器电路传来的时间信息,进行实时译码显示。

(四)电机运转时序控制电路(analyse):接收运行起止信号,安排电机运行状态并编码输出。

(五)译码器(move):接收电机运行状态信号,译码后实时控制电机的正传、反转和暂停。

三、选择器件1、pc机一台。

2、CPLD/FPGA适配器板:标准配置EPF10K10LC84-4接口板,下载接口是数字芯片的下载接口(DIGITAL JTAG),主要用于CPLD/FPGA芯片的数据下载。

基于Verilog HDL的洗衣机控制电路设计

信息与电HChina Computer&Communication 秋件开茨爲惑用2021年第2期基于Verilog HDL的洗衣机控制电路设计杨凯饪王颖*(大连理工大学城市学院电子与自动化学院,辽宁大连116024)摘要:随着人们的生活水平提高,人们对洗衣机的需求越来越大,因此洗衣机的市场逐步扩大,洗衣机行业竞争也愈演愈烈。

在此背景下,本文以Verilog HDL为基础实现了以洗衣机控制电路为核心,结合所需的外围电路,共同对洗衣机的工作状态进行自由控制。

关键词:Verilog HDL;硬件描述语言;中心控制模块;洗衣机控制电路中图分类号:TN702文献标识码:A文章编号:1003-9767(2021)02-151-02Design of Washing Machine Control Circuit Based on Verilog HDLYANG Kaiyu,WANG Ying*(School of Electronics and Automation,City Institute,Dalian University of Technology,Dalian Liaoning116024,China)Abstract:With the improvement of people's living standards,people's demand for washing machines is increasing.Therefore, the market for washing machines is gradually expanding,and the competition in the washing machine industry is intensifying.In this context,this article uses Verilog HDL as the basis to realize the washing machine control circuit as the core,combined with the required peripheral circtdts,to jointly control the working state of the washing machine freely.Keywords:Verilog HDL;hardware description language;central control module;washing machine control circuit1总体设计系统包括中心控制模块、分频模块、按键去抖模块、BCD码转换电路和数码显示电路21。

基于VHDL语言的简易洗衣机控制器

电子课程设计——简易洗衣机控制器设计学院:班级:姓名:学号:指导老师:2013年12月目录第一部分:设计任务与要求 (1)第二部分:总体框图 (1)第三部分:选择器件 (2)第四部分:功能模块 (3)4.1时间预置编码寄存模块(settime) (3)4.2减法计数器模块(counter) (4)4.3数码管显示模块(showtime) (7)4.4时序电路模块(analyse) (9)4.5译码器模块(move)………………………………………1 1 第五部分:总体设计电路图 (13)5.1总体(顶层)设计电路图 (13)5.2顶层文件仿真 (13)5.3管脚分配图 (14)5.4硬件实验效果图 (14)第六部分:课程设计心得体会 (15)简易洗衣机控制器设计一、设计任务与要求设计一个洗衣机洗涤程序控制器,控制洗衣机的电动机按下图所示的规律运转:时间到 用两位数码管预置洗涤时间(分钟数),洗涤过程在送入预置时间后开始运转,洗涤中按倒计时方式对洗涤过程作计时显示,用LED 表示电动机的正、反转,如果定时时间到,则停机并发出音响信号。

二、总体框图RUN REV PAUSEtime_over clkK5 startK6 load K1 K2 K3 K4 各个部分的具体功能描述如下:(一)预设时间和编码电路(settime ):接受用户通过按钮预置的时间信息,编码成八位之后转给减法计数器。

(二)减法计数器电路(counter ):接收编码之后的预置时间信息,向电机运转控制电路传递运行信号,并将预置时间信息和剩余时间信息发给数码管显示电路进行实时显示。

(三)数码管显示电路(showtime ):接收减法计数器电路传来的时间信息,进行实时译码显示。

(四)电机运转时序控制电路(analyse ):接收运行起止信号,安排电机运行状态并编码输出。

(五)译码器(move ):接收电机运行状态信号,译码后实时控制电机的正传、反转和暂停。

智能洗衣机控制器 VHDL语言

智能洗衣机控制器的设计YIEEKUU一、设计内容与要求①设计一个智能洗衣机(全自动洗衣机)控制器,能够实现洗衣,漂洗和脱水的功能。

②要求能够使用按键模拟对洗衣机的控制,能够设置工作模式,为了便于观察,将洗衣机的工作模式和所剩的工作时间用数码管显示出来,能够将洗衣机当前所处的状态用发光管或者数码管显示出来。

【模式1】:洗特别脏的衣服(洗衣30秒钟)【模式2】:洗脏的衣服(洗衣20秒钟)【模式3】:洗一般的衣服(洗衣10秒钟)【模式4】:漂洗(每次漂洗5秒钟)【模式5】:脱水(每次脱水3秒钟【洗衣过程】:洗衣+脱水+漂洗+脱水+漂洗+脱水,注水完成使用外部传感器S=1表示。

【漂洗模式】:漂洗+脱水+漂洗+脱水,注水完成使用外部传感器S=1表示。

【脱水模式】:脱水。

【注】:操作完毕使用蜂鸣器鸣叫两秒提示二、系统设计(包括设计思路、总体框图、分块设计)设计思路:首先从题目进行分析,采用VHDL模块化的设计方法来进行洗衣机控制器的设计,即自顶向下,从系统总体要求出发,自上至下地将设计任务分解为不同的功能模块,最后将各功能模块连接形成顶层模块,完成系统硬件的整体设计。

本控制器基本功能描述洗衣机控制器可工作于五种模式下,可以使洗衣机控制器工作在任意一种模式,并显示出洗衣机的工作状态和剩余工作时间,在剩余时间结束后有报警声提示使用者,并且可实现暂停蜥蜴和继续的功能。

由此分析可将洗衣机控制器分为控制模块、倒计时模块、初始模块选择模块、报警模块、洗衣时间选择模块、选通译码模块和分频器模块。

设计过程:1)审题,初步确定思路。

2)用VHDL语言进行编程。

3)适时对程序进行修改。

4)编译成功后,进行仿真,观察波形图。

5)将程序下载到实验板上,调试各功能。

6)通过计算机仿真和下载调试,发现问题,返回原程序进行修改。

7)进行总体的调试。

分块设计核心控制选择模块:此模块是本程序的核心部分,要识别模式选择器送来的基本工作方式依次执行。

基于VHDL的洗衣机控制器的设计

万方数据

万方数据

万方数据

万方数据

基于VHDL的洗衣机控制器的设计

作者:成超, 任峻, CHENG Chao, REN Jun

作者单位:湖南农业大学信息科学技术学院,湖南长沙,410128

刊名:

电子设计工程

英文刊名:Electronic Design Engineering

年,卷(期):2014,22(4)

参考文献(6条)

1.郭忠;李涛;李勇基于FPGA的洗衣机控制系统设计 2012(13)

2.杨海钢FPGA器件设计技术发展综述 2010(03)

3.谭会生;瞿遂春EDA技术综合应用实例与分析 2004

4.姚毅;陈艳风基于EDA的洗衣机控制器设计 2012(16)

5.李波;王章瑞;高一波基于VHDL的洗衣机控制器设计 2007(06)

6.黄任VHDL入门@解惑@经典实例@经验总结 2005

引用本文格式:成超.任峻.CHENG Chao.REN Jun基于VHDL的洗衣机控制器的设计[期刊论文]-电子设计工程 2014(4)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子课程设计——简易洗衣机控制器设计学院:班级:姓名:学号:指导老师:2013年12月目录第一部分:设计任务与要求 (1)第二部分:总体框图 (1)第三部分:选择器件 (2)第四部分:功能模块 (3)4.1时间预置编码寄存模块(settime) (3)4.2减法计数器模块(counter) (4)4.3数码管显示模块(showtime) (7)4.4时序电路模块(analyse) (9)4.5译码器模块(move)………………………………………1 1 第五部分:总体设计电路图 (13)5.1总体(顶层)设计电路图 (13)5.2顶层文件仿真 (13)5.3管脚分配图 (14)5.4硬件实验效果图 (14)第六部分:课程设计心得体会 (15)简易洗衣机控制器设计一、设计任务与要求设计一个洗衣机洗涤程序控制器,控制洗衣机的电动机按下图所示的规律运转:用两位数码管预置洗涤时间(分钟数),洗涤过程在送入预置时间后开始运转,洗涤中按倒计时方式对洗涤过程作计时显示,用LED 表示电动机的正、反转,如果定时时间到,则停机并发出音响信号。

二、总体框图RUN REV PAUSEK5K6K1 K2 K3 K4各个部分的具体功能描述如下:(一)预设时间和编码电路(settime ):接受用户通过按钮预置的时间信息,编码成八位之后转给减法计数器。

(二)减法计数器电路(counter):接收编码之后的预置时间信息,向电机运转控制电路传递运行信号,并将预置时间信息和剩余时间信息发给数码管显示电路进行实时显示。

(三)数码管显示电路(showtime):接收减法计数器电路传来的时间信息,进行实时译码显示。

(四)电机运转时序控制电路(analyse):接收运行起止信号,安排电机运行状态并编码输出。

(五)译码器(move):接收电机运行状态信号,译码后实时控制电机的正传、反转和暂停。

三、选择器件1、pc机一台。

2、CPLD/FPGA适配器板:标准配置EPF10K10LC84-4接口板,下载接口是数字芯片的下载接口(DIGITAL JTAG),主要用于CPLD/FPGA芯片的数据下载。

3、实验箱:装有七段数码管及蜂鸣器等,七段数码管字形及真值表如下七段数码管字形如下:七段数码管真值表如下:四、功能模块4.1时间预置编码寄存模块(settime)1、时间预置编码寄存模块settime如图1所示,time_input为通过开发板上拨码开关K1、K2、K3、K4输入的信号,load为输入确认信号。

本模块将输入的四位时间信号编码成八位二进制数输出到减法计数器电路。

图1 时间预置编码寄存模块settime2、仿真图图2 时间预置编码寄存模块仿真图用K1、K2、K3、K4给time_input输入一个二进制数0111,让load有效,输出time_set为00000111。

3、时间预置编码寄存模块源代码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity settime isport(load:in std_logic;time_input:in std_logic_vector(3 downto 0);time_set:out std_logic_vector(7 downto 0));end settime;architecture settime of settime issignal p1:std_logic_vector(7 downto 0);beginprocess(load)beginif(load'event and load='1')thencase time_input iswhen "0000"=>p1<="00000000";when "0001"=>p1<="00000001";when "0010"=>p1<="00000010";when "0011"=>p1<="00000011";when "0100"=>p1<="00000100";when "0101"=>p1<="00000101";when "0110"=>p1<="00000110";when "0111"=>p1<="00000111";when "1000"=>p1<="00001000";when "1001"=>p1<="00001001";when others=>p1<="00000000";end case;end if;end process;time_set<=p1;end settime;4.2减法计数器模块(counter)1、减法计数模块counter如图3所示,本模块中clk为系统时序脉冲信号,start为系统开始运行的信号,time_set接收编码之后的预置时间信息,向电机运转控制电路传递运行信号,并将预置时间信息和剩余时间信息发给数码管显示电路进行实时显示。

time_remain为输出到数码管显示电路的时间信号,time_over为系统运行结束信号,可以用来控制蜂鸣器的通断。

图3 减法计数模块2、仿真图图4 减法计数模块仿真图3、减法计数模块源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter isport(clk,start:in std_logic;time_set:in std_logic_vector(7 downto 0);time_remain:buffer std_logic_vector(7 downto 0); time_over:buffer std_logic);end counter;architecture counter of counter isbeginprocess(clk)variable time_second:integer range 0 to 59 :=59;beginif(clk'event and clk='1')thenif(start='0')thenif(time_remain(7 downto 0)=0)thentime_remain<=time_set;elsetime_remain(7 downto 4)<=time_remain(3 downto 0); time_remain(3 downto 0)<=time_set(3 downto 0); end if;time_second:=59;time_over<='1';elseif(time_over='1')thenif(time_second=0 and time_remain(7 downto 0)=0) thentime_over<='0';elseif(time_second=0)thenif(time_remain(3 downto 0)=0)thentime_remain(7 downto 4)<=time_remain(7 downto 4)-1; time_remain(3 downto 0)<="1001";time_second:=59;elsetime_remain(7 downto 4)<=time_remain(7 downto 4); time_remain(3 downto 0)<=time_remain(3 downto 0)-1; time_second:=59;end if;elsetime_second:=time_second-1;end if;end if;end if;end if;end if;end process;end counter;4.3数码管显示模块(showtime)1、数码管显示模块showtime如图5所示,本模块clk为系统时序脉冲信号,time_remain接收减法计数器电路传来的时间信息,进行实时译码显示,a,b,c,d,e,f,g分别对应数码管的七段,minute和second分别位选两个数码管,显示十位和个位。

图5 数码管显示模块2、仿真图图6 数码管显示模块仿真图3、数码管显示模块源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity showtime isport(time_remain:in std_logic_vector(7 downto 0); clk:in std_logic;minute,second:out std_logic;a,b,c,d,e,f,g:out std_logic);end showtime;architecture showtime of showtime issignal temp:std_logic_vector(6 downto 0);signal bcd:std_logic_vector(3 downto 0);signal choose:std_logic;beginprocess(clk)beginif(clk'event and clk='1')thenchoose<=not choose;if(choose='1')thenminute<='0';second<='1';bcd<= time_remain(7 downto 4); elseminute<='1';second<='0';bcd<= time_remain(3 downto 0); end if;end if;end process;process(bcd)begincase bcd iswhen "0000"=>temp<="1111110";when "0001"=>temp<="0110000";when "0010"=>temp<="1101101";when "0011"=>temp<="1111001";when "0100"=>temp<="0110011";when "0101"=>temp<="1011011";when "0110"=>temp<="1011111";when "0111"=>temp<="1110000";when "1000"=>temp<="1111111";when "1001"=>temp<="1111011";when others=>temp<="1111011";end case;a<=temp(6);b<=temp(5);c<=temp(4);d<=temp(3);e<=temp(2);f<=temp(1);g<=temp(0);end process;end showtime;4.4时序电路模块(analyse)1、时序电路模块analyse如图7所示,本模块由start控制使能控制,通过时钟的输入进行计算当前系统所处的状态,并进行编码输出电机的运转状态,out_1为高位时表示电机正转,out_2为高位时表示电机反转。