汽车电子网关-XC2000及XE166家族ADC模块浅解应用攻略

英飞凌单片机选型

24 / 30/40

最多10 1 1 4 最多2 QFP 144 / 176

16 / 24

最多8 0 1 4 QFP 64/100 / 144 - 40°C to +125°C

16 / 24

最多6 0 1 4 QFP 100 / 144 - 40°C to +125°C

9 / 16

最多6 0 1 2 QFP 64 / 100

程序 [PSRAM]

数据 [DSRAM] 双端口[DPRAM]

SB RAM CAN ADC Standby 通道数 通道数 8 最多3 最多24 最多6 0 1 最多4 可选 QFP 100 / 144 - 40°C to +125°C

112

24 2 8 3 24 8 0 1 4 2 通道 QFP 144 - 40°C to +125°C

XC874

Vector Computer

XC878

Vector Computer

52kB

XC874

Vector Computer

XC878

Vector Computer

32kB

XC886

Vector Computer

XC888

Vector Computer

XC886

XC888

Vector Computer

工作温度 (T环境)

- 40°C to +125°C

- 40°C to +125°C

-40°C to +125°C

* **

USIC: CCU:

可配置成UART, LIN, SPI/QSPI, IIC, IIS 用于PWM, D/A

04.05.2012

英飞凌MCU新手入门应用笔记中文版

新手导1. 82.163.32声明:英飞凌社区应用笔记部分资料内容来源英飞凌社区请来信告知。

本人尊重原创作者。

2012/6新手导航中文版位单片机介绍位单片机介绍位单片机介绍凌社区热心网友奉献资料整理和网络,应用笔记心得整理,内容仅供参考。

如果侵犯Infineon (MCU 新手门篇)英飞凌社区新导航笔记 Ken2012/6/3 果侵犯你的版权,新手入社区新手关于英飞凌总部位于德国纽必堡的英飞凌科技股份公司,为现代社会的三大科技挑战领域——高能效、移动性和安全性提供半导体和系统解决方案。

2010财年(截止到9月30日),公司实现销售额40亿欧元,在全球拥有约26,000名雇员。

英飞凌科技公司的业务遍及全球,在美国苗必达、亚太地区的新加坡和日本东京等地拥有分支机构。

英飞凌公司目前在法兰克福股票交易所(股票代码:IFX)和美国柜台交易市场(OTCQX)International Premier(股票代号:IFNNY)挂牌上市英飞凌在中国英飞凌科技股份公司于1995年正式进入中国市场。

自1996年在无锡建立第一家企业以来,英飞凌的业务取得非常迅速的增长,在中国拥有1300多名员工,已经成为英飞凌亚太乃至全球业务发展的重要推动力。

英飞凌在中国建立了涵盖研发、生产、销售、市场、技术支持等在内的完整的产业链,并在销售、技术研发、人才培养等方面与国内领先的企业、高等院校开展了深入的合作。

☺☞Infineon XC800系列8位元MCU(8位单片机)超级耐高温150℃工业级 8位MCU XC800专为汽车应用设计XC800 150℃系列是汽车产品的理想之选,例如涡轮增压器、发动机风扇、节流阀或阀控制装置、EPS、燃料/燃油传感器以及水/机油/燃油泵等。

潜在的工业应用包括加热控制装置、锅炉系统或电机内部的电子控制系统等。

AEC-Q100是由汽车电子设备委员会(AEC)制定的可靠性压力测试标准。

测试表明,英飞凌全新推出的系列高温微控制器,经过符合AEC-Q100 Grade 0 (-40℃至150℃)标准要求的测试和认证。

汽车电子车身控制-XC2000系统控制单元驱动应用攻略

1 功能概述英飞凌为用户提供软件方面的例子,使得用户在对系统控制单元(SCU)这个强大而复杂的模块没有详细的了解的情况下,也能根据自己的需要配置和使用XC2000系列的这个模块。

SCU的驱动程序提供了函数接口,可以用于实现以下几个主要目的:∙系统时钟的控制(Normal模式下)∙省电模式的控制提供以下几种类型的函数接口:∙典型应用所需要的全局函数。

∙该驱动内部使用的私有函数。

这些函数通过文档记录下来作为参考之用。

用户可以通过复制、粘贴这些函数作为特殊用途之用。

∙测试函数帮助用户使其应用程序能够运行起来。

所有这些函数的特性将在下面的章节中进行阐述。

1.1 Normal模式复位之后,系统将通过SCU驱动函数进入Normal工作模式:Scu_GoFromBaseModeToNormalMode通过配置,下面时钟源之一可以被选择作为Normal模式工作之用:∙晶振或者与通过晶振输入引脚输入的外部时钟信号∙通过CLKIN1输入的外部时钟信号∙均流控制的内部时钟源(5MHz)注意:该应用笔记从此处开始,均流控制的内部时钟源这个名词都将由内部时钟来代替。

时钟源的频率由用户来配置。

控制器的压控振荡器(VCO)用于产生一个高达80MHz的可配置的系统时钟。

系统时钟可通过引脚2.8输出作为测试之用。

如果使用的是晶振的话,SCU的驱动函数Scu_EnableHighPrecOsc可能会在初始化的初期被调用,从而减少Scu_GoFromBaseModeToNormalMode函数中晶振振荡稳定所需的等待时间。

1.2 省电模式1.2.1 进入省电模式通过SCUScu_GoFromNormalModeToPowerSavingMode这个SCU驱动函数进入省电模式。

这个函数的参数结构指定省电模式和唤醒的细节。

支持以下省电模式:∙Normal Stop-over 模式∙晶振保持持续工作的Stop-over模式∙Normal Standby模式∙带有快速启动(FSM)的Standby模式可以由下列事件将单片机从省电模式下唤醒:∙唤醒定时器(WUT)∙外部服务请求(ESR)引脚∙复用ESR引脚(CAN、LIN、SPI)WUT还提供一些参数供用户设置:∙定时器间隔时间∙触发后自动停止或者不采用自动停止(用于固定的休眠时间或者固定的唤醒周期)∙定时器分频在进入休眠模式之前,用户需要注意以下事项:∙用到的外设需要关闭以减小电流消耗∙输入/输出需要被设置成电流消耗最小的状态∙中断需要被禁止如果省电模式在整个应用程序中都不需要被用到,则省电模式这个模块可以被禁止以减小代码空间。

英飞凌MCU新手入门应用笔记中文版

新手导1. 82.163.32声明:英飞凌社区应用笔记部分资料内容来源英飞凌社区请来信告知。

本人尊重原创作者。

2012/6新手导航中文版位单片机介绍位单片机介绍位单片机介绍凌社区热心网友奉献资料整理和网络,应用笔记心得整理,内容仅供参考。

如果侵犯Infineon (MCU 新手门篇)英飞凌社区新导航笔记 Ken2012/6/3 果侵犯你的版权,新手入社区新手关于英飞凌总部位于德国纽必堡的英飞凌科技股份公司,为现代社会的三大科技挑战领域——高能效、移动性和安全性提供半导体和系统解决方案。

2010财年(截止到9月30日),公司实现销售额40亿欧元,在全球拥有约26,000名雇员。

英飞凌科技公司的业务遍及全球,在美国苗必达、亚太地区的新加坡和日本东京等地拥有分支机构。

英飞凌公司目前在法兰克福股票交易所(股票代码:IFX)和美国柜台交易市场(OTCQX)International Premier(股票代号:IFNNY)挂牌上市英飞凌在中国英飞凌科技股份公司于1995年正式进入中国市场。

自1996年在无锡建立第一家企业以来,英飞凌的业务取得非常迅速的增长,在中国拥有1300多名员工,已经成为英飞凌亚太乃至全球业务发展的重要推动力。

英飞凌在中国建立了涵盖研发、生产、销售、市场、技术支持等在内的完整的产业链,并在销售、技术研发、人才培养等方面与国内领先的企业、高等院校开展了深入的合作。

☺☞Infineon XC800系列8位元MCU(8位单片机)超级耐高温150℃工业级 8位MCU XC800专为汽车应用设计XC800 150℃系列是汽车产品的理想之选,例如涡轮增压器、发动机风扇、节流阀或阀控制装置、EPS、燃料/燃油传感器以及水/机油/燃油泵等。

潜在的工业应用包括加热控制装置、锅炉系统或电机内部的电子控制系统等。

AEC-Q100是由汽车电子设备委员会(AEC)制定的可靠性压力测试标准。

测试表明,英飞凌全新推出的系列高温微控制器,经过符合AEC-Q100 Grade 0 (-40℃至150℃)标准要求的测试和认证。

16位微控制器XE166的设计

EBC

对内部存储器的访问通常由CPU执行,对片外外设或外部存储 器的访问通过片上外部总线控制器(EBC)实现。当程序或数 据地址指向外部地址空间时,CPU会自动调用EBC来实现该操 作。 外部总线控制器(EBC)处理访问外部存储器或外设。它的寄 存器的功能分成三组: •模式寄存器 - 用于编程的基本行为。 •功能,定时和地址寄存器。 - 功能寄存器指定的外部总线周期地址 (MUX / DEMUX),数据(16-bit/8-bit),芯片选择启用和 READY控制

返回

IMB

RF(寄存器文件)

通用寄存器(GPR)位于全局寄存器组、或两个局部寄 存器组之一,占用16个字长的连续地址。全局寄存器 组被映射到DPRAM区。上下文指针(CP)寄存器指定当 前有效的全局寄存器组的基地址。寄存器组由最多16 个字GPR(R0,R1,…R15)和/或最多16个字节GPR (RL0,RH0,…RL7,RH7)组成。16个字节GPR被映射 到前8个字GPR上。

XE166内核主要特点

C166SV2内核

MCU

主频高达100MHz 单指令执行周期 2级指令预取流水线,5级执行 流水线 分支检测和预测指令 (JMPA,CALLA.) 零周期跳转(分支预测单元) 快速上下文切换(单周期) 灵活的中断系统 PEC单元实现类DMA数据传送

返回

返回

IFU

指令读取单元(IFU)通过64位宽的总线从程序 管理单元(PMU)中至少同时读取两条指令(形 成连续的指令流),预取出来的指令存储在指令 FIFO中。CPU开始执行从指令FIFO中读取的指令 时,IFU通过PMU从预测的目标地址中读取一条新 指令,在执行期间下一条指令缓存在FIFO中(不 存在指令访问的延迟时间)。 IFU包括两级流水线:预取指阶段和取指阶段

03车身电器--D16网络

高速GMLAN 底盘GMLAN 低速GMLAN 500千字节/秒 500千字节/秒 33.33千字节/秒

DLC通讯接口

针 1 2 3 4 接地(端子31) 脚 信 号 低速单线 CAN总线

5 6

7 8 9 10 11 12 13 14 15 16

信号接地(端子31) 高速CAN-High

CE CAN H CE CAN L 高速CAN-Low

供电电源(端子30)

高速GMLAN

高速GMLAN

BCM

VCIM

EPS

EBCM

TCM

ECM

AFL

高速GMLAN部分模块定位图

BCM在乘客舱内,在中央控制台前部之下

车辆通讯接口模块 在乘客舱内,在仪表板中央之后 靠近收音机

启用醒线

此处搭铁会出现什么故障现象? 此处与电源短路会出现什么故障 现象?

12V

底盘GMLAN

低速GMLAN

低速GMLAN部分模块定位图

SDM 在乘客舱内,在中央控制台下,靠近车身控制模块

收音机 在乘客舱内,在仪表板中央之后

驻车辅助模块 在行李区内,靠近左侧尾灯总成

HVAC 在乘客舱内,在仪表板的中央

LIN 网络

XC2000系列引脚配置说明

XC2000/XE166家族AP16146引脚配置、电源供电以及复位应用笔记V1.0 2009-09Edition 2009-09 08Published byInfineon Technologies AG81726 Munich, Germany© 2009 Infineon Technologies AGAll Rights Reserved.LEGAL DISCLAIMERTHE INFORMATION GIVEN IN THIS APPLICATION NOTE IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.InformationFor further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office WarningsDue to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.AP16146版本信息: V1.0, 2009-09 先前的版本: 无目录1简介 (5)2基本配置 (5)2.1测试引脚 (5)2.2电源引脚 (5)2.3复位引脚 (5)2.4启动模式 (6)2.5从F LASH进行内部启动 (6)2.6调试配置 (8)3电源电压 (8)3.1单电源供电 (8)3.2双电源供电 (9)4特殊的复位配置 (10)4.1利用ESR引脚来触发一个上电复位 (10)4.2通过ESR引脚产生复位输出(RSTOUT)延迟 (12)5总结 (13)1 简介英飞凌的XC2000/XE166系列单片机提供了以高性能C166S V2内核为基础的新一代16位单片机,并带有新的特性从而降低了系统的成本。

汽车电子车身控制-XC2000及XE166引脚配置电源供电以及复位的说明应用攻略

1 简介英飞凌的XC2000/XE166系列单片机提供了以高性能C166S V2内核为基础的新一代16位单片机,并带有新的特性从而降低了系统的成本。

本应用笔记着重于与基本硬件相关的特性,比如EVR(嵌入式片内电压调节器)、PORST(上电复位)和特殊功能引脚的配置。

本笔记涵盖了以下产品系列的功能:∙XC22xxM、 XC22xxN、XC22xxH∙XC23xxA、XC23xxB∙XC27x5X、XC27x4X∙XE166M、 XE166N、XE166H2 基本配置为了正确的操作,必须考虑一些引脚的连接:∙测试引脚 ( /TRST, /TESTM)∙电源引脚 (VDDIM, VDDI1,VDDPA, VDDPB,VSS)∙复位引脚 (/PORST, ESR0, ESR1,ESR2)∙启动引脚 (Port 10)2.1 测试引脚/ TESTM引脚使能工厂测试模式。

对于正常操作模式,/ TESTM必须直接连接到VDDPB(数字电源供电电源域B)在/PORST上电复位之后,内部启动软件通过/ TRST管脚的初始值来决定初始化模式:内部正常启动模式、其它启动模式或者调试模式。

对于正常操作来说,/ TRST管脚应该通过下拉电阻连接到Vss(数字地)。

该引脚上的高电平加上/PORST引脚上的一个上升沿,将激活调试系统或者其它启动模式。

2.2 电源引脚该器件的工作电压范围在3.0V至5.5V之间。

芯片上的嵌入式片内电源供电由两个独立的电压调节器VDDIM和VDDI1组成,产生1.5V的内核电压。

不同的省电模式减少或关闭了内核电压。

片上有两组I / O引脚,它们即可以工作在相同的电压下,也可以工作在不同电压下。

例如A / D转换器和其他一些引脚需要5V,而外部数据存储器需要 3.3V。

在这种情况下,引脚VDDPA(数字电源供电电源域A)连接到5V,而VDDPB(数字电源供电电源域B)引脚连接到3.3V。

嵌入式片内电压调节器分为域M(引脚VDDIM)和域1(引脚VDDI1)。

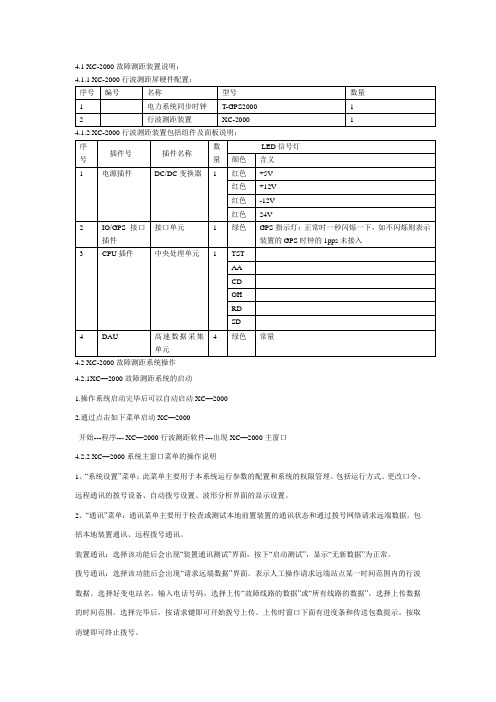

XC-2000故障测距装置说明

4.1 XC-2000故障测距装置说明:4.1.1 XC-2000行波测距屏硬件配置:4.1.2 XC-2000行波测距装置包括组件及面板说明:4.2 XC-2000故障测距系统操作4.2.1XC—2000故障测距系统的启动1.操作系统启动完毕后可以自动启动XC—20002.通过点击如下菜单启动XC—2000开始---程序--- XC—2000行波测距软件---出现XC—2000主窗口4.2.2 XC—2000系统主窗口菜单的操作说明1、“系统设置”菜单:此菜单主要用于本系统运行参数的配置和系统的权限管理。

包括运行方式、更改口令、远程通讯的拨号设备、自动拨号设置、波形分析界面的显示设置。

2、“通讯”菜单:通讯菜单主要用于检查或测试本地前置装置的通讯状态和通过拨号网络请求远端数据。

包括本地装置通讯、远程拨号通讯。

装置通讯:选择该功能后会出现“装置通讯测试”界面,按下“启动测试”,显示“无新数据”为正常。

拨号通讯:选择该功能后会出现“请求远端数据”界面。

表示人工操作请求远端站点某一时间范围内的行波数据。

选择好变电站名,输入电话号码,选择上传“故障线路的数据”或“所有线路的数据”,选择上传数据的时间范围。

选择完毕后,按请求键即可开始拨号上传。

上传时窗口下面有进度条和传送包数提示。

按取消键即可终止拨号。

3、“行波测距”菜单人工测距:人工输入某条线路单端或双端的行波采样时间,自动计算测距结果。

主要用于系统无法获取单端或双端的行波数据,只能人为获得单端或双端的装置记录时间。

(一)若“请求远端数据”成功,则可将“人工测距”界面的右侧选择为“搜索故障时间”,其“微秒”显示框会显示出一组数字。

左侧选择“输入故障时间”,可将XC—2000主窗口相应故障显示的时间数组输入其“微秒”显示框。

(二)若“请求远端数据”不成功,则通过电话联系麦元站工作人员,得到你需要的故障的时间数组,在选择“人工测距”界面的右侧“输入故障时间”后,将时间数组输入其“微秒”显示框。

ECAT-2000 系列 EtherCAT 从站 I O 模块使用手册说明书

ECAT-2000 系列EtherCAT 從站I/O 模組使用手冊繁體中文 1.9版本, 2019年 09月承諾鄭重承諾: 凡泓格科技股份有限公司產品從購買後,開始享有一年保固,除人為使用不當的因素除外。

責任聲明凡使用本系列產品除產品品質所造成的損害,泓格科技股份有限公司不承擔任何的法律責任。

泓格科技股份有限公司有義務提供本系列產品詳細使用資料,本使用手冊所提及的產品規格或相關資訊,泓格科技保留所有修訂之權利,本使用手冊所提及之產品規格或相關資訊有任何修改或變更時,恕不另行通知,本產品不承擔使用者非法利用資料對第三方所造成侵害構成的法律責任,未事先經由泓格科技書面允許,不得以任何形式複製、修改、轉載、傳送或出版使用手冊內容。

版權版權所有 © 2018 泓格科技股份有限公司,保留所有權利。

商標文件中所涉及所有公司的商標,商標名稱及產品名稱分別屬於該商標或名稱的擁有者所持有。

聯繫我們如有任何問題歡迎聯繫我們,我們將會為您提供完善的咨詢服務。

Email:支援ECAT-2024/2028 ECAT-2045/2045-32ECAT-2050/2051/2051-32 ECAT-2052/2052-NPN ECAT-2053/2055/2055-32ECAT-2057/2057-NPN/2057-8P8N/2057-32 ECAT-2060 ECAT-2061目錄1.簡介 (4)1.1配件清單 (5)1.2產品資訊 (7)1.3選型指南 (9)2.硬體資訊 (11)2.1配置圖 (11)2.2規格 (15)2.2.1系統規格 (15)2.2.2I/O規格 (16)ECAT-2024/2028 (16)ECAT-2045/2045-32 (16)ECAT-2051/2051-32 (16)ECAT-2052/2052-NPN (17)ECAT-2053 (17)ECAT-2055/2055-32 (18)ECAT-2057/2057-NPN/2057-8P8N (18)ECAT-2057-32 (19)ECAT-2050 (19)ECAT-2060/2061 (20)2.3腳位定義 (21)EtherCAT介面 (21)ECAT-2024 (21)ECAT-2028 (21)ECAT-2045/2057/2057-NPN/2057-8P8N (22)ECAT-2051 (22)ECAT-2052/2052-NPN (22)ECAT-2053 (23)ECAT-2055 (23)ECAT-2060 (23)ECAT-2050 (25)ECAT-2045-32/2057-32 (25)ECAT-2051-32 (26)ECAT-2055-32 (26)ECAT-2061 (27)2.4接線圖 (28)輸入接線 (28)輸出接線 (29)2.5信號線連接至模組連接器 (30)2.6機構圖 (32)ECAT-2024/2028/2045/2050/2051/2052/2053/2055/2057/2060 系列 (32)ECAT-2045-32/2051-32/2055-32/2057-32/2061 系列 (32)3.啟用ECAT-2000模組 (33)3.1連接主站與電源 (33)3.2配置運作模式 (35)進入至EtherCAT網路 (35)4.OBJECT 說明及參數設定 (37)4.1標準O BJECT(0X1000-0X1FFF) (37)[ALL]Index 1000 Device Type (37)[ALL]Index 1008 Device Name (37)[ALL]Index 1009 Hardware Version (39)[ALL]Index 100A Software Version (39)[ALL]Index 1018 Identity (39)[ECAT-2050]Index 160n(0<=n<=3) DO Outputs Process Data Mapping (41)[ECAT-2055-32]Index 1600 DO Outputs Process Data Mapping (41)[ECAT-2045-32/2057-32]Index 1600 DO Outputs Process Data Mapping (42)[ECAT-2024/2028]Index 160n AO Outputs Process Data Mapping (43)[ECAT-2050]Index 1A0n(0<=n<=C) DI Outputs Process Data Mapping (43)[ECAT-2055-32]Index 1A00 DI Outputs Process Data Mapping (43)[ECAT-2051-32]Index 1A00 DI Outputs Process Data Mapping (44)[ALL]Index 1C00 Sync Manager Type (45)[ECAT-2050]Index 1C12 SyncManager 2 Assignment (45)[ECAT-2055-32/2045-32/2057-32]Index 1C12 SyncManager 2 Assignment (45)[ECAT-2024/2028]Index 1C12 SyncManager 2 Assignment (45)[ECAT-2055-32/2051-32]Index 1C13 SyncManager 3 Assignment (46)[ECAT-2050]Index 1C13 SyncManager 3 Assignment (46)4.2特定O BJECTS(0X6000-0X7FFF) (47)[ECAT-2050]Index 60n0(0<=n<=C) Digital Inputs (47)[ECAT-2055-32]Index 6000 Digital Inputs (47)[ECAT-2051-32]Index 6000 Digital Inputs (48)[ECAT-2050]Index 70n0(0<=n<=C) Digital Outputs (49)[ECAT-2055-32]Index 7000 Digital Outputs (49)[ECAT-2045-32/2057-32]Index 7000 Digital Outputs (50)[ECAT-2024/2028]Index 70n0 AO Outputs Channel (51)4.3特定O BJECTS(0X8000-0X8FFF) (51)ECAT-2024/2028處理資料流程圖 (51)校正計算 (52)[ECAT-2024/2028]Index 80n0 AO Channel Settings (54)[ECAT-2024/2028]Index 80nE AO Channel Internal Data (55)[ECAT-2024/2028]Index 80nF AO Channel Internal Data (55)附錄: 手冊修訂記錄 (56)1.簡介ECAT-2000 系列是工業EtherCAT Slave 遠端I/O 模組且支援了EtherCAT 協定,還能夠建構Daisy Chain 網路拓撲(如,星形、線形或環形),可簡化線路配置與維護的複雜度,降低佈線成本與交換器的需求,使安裝更具靈活性。

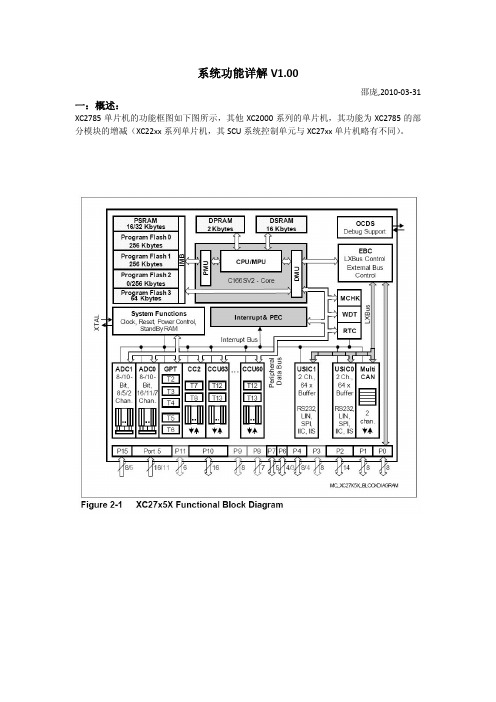

XC2000系统说明

系统功能详解V1.00邵庞,2010‐03‐31 一:概述:XC2785单片机的功能框图如下图所示,其他XC2000系列的单片机,其功能为XC2785的部分模块的增减(XC22xx系列单片机,其SCU系统控制单元与XC27xx单片机略有不同)。

XC2785x的MCU如上图所示,依次为:左上: 576K/832K的片内FLASH供存储程序使用。

16K/32K的片内PSRAM(程序SRAM)供存储片内RAM程序使用,一般为BootLoad 程序临时存放下载程序使用。

IMB内部存储器控制接口,控制FLASH和PSRAM的读和写控制,Bootload时主要控制IMB进行FLASH的擦除和写入操作。

中上: 2K的DPRAM双口RAM,做快速RAM操作,堆栈操作和GPRs寄存器操作使用。

16K的DSRAM普通静态RAM,做相对慢速RAM操作使用,也可作为堆栈操作。

CPU/MPU进行计算使用,含MAC运算单元。

PMU和DMU分别管理指令操作和数据操作。

右上: OCDS调试接口,供板上调试芯片使用。

用户可在实际目标板上仿真程序。

EBC外部总线控制系统,包括USIC和MultiCAN均作为被外部总线控制的单元。

左中: SCU系统控制单元,包含时钟,休眠,RAM休眠控制等单元。

中中: 中断和PEC外围模块事件处理系统。

右中: MCHK存储器检查单元用来检查和保护数据和寄存器。

WDT独立的看门狗单元监控程序运行。

RTC独立的实时时钟系统,独立于系统时钟运行。

左下: 为内部SFR/ESFR寻址的外围单元。

2路独立/同步ADC模块,8/10BitAD精度,最多24路,可外扩。

2组独立的通用定时器,包括T2/T3/T4和T5/T6共5路独立/级联/捕获/重载定时器。

16路捕获/比较定时器单元,包括T7/T8两个独立定时器和16路捕获/比较单元。

4路各自独立的CC6U单元,每路均能产生含死区时间和故障保护的三相电机PWM 控制或者普通的时钟捕获/比较功能。

英飞凌CAN功能系列MCU介绍

收发器 CAN未规定必须使用哪种收发器

¬ 由于有许多不同类型的CAN收发器,因此微控制器未集成收发器

通常使用双绞线 有些CAN收发器使用单线,有些CAN收发器具有容错能力

2009-11-17

Copyright © Infineon Technologies 2009. All rights reserved.

EMI

40m / 130 ft @ 1 Mbps

120 Ohm

Page 10

如何将CAN嵌入到系统中 ---硬件要求

CAN控制器 硬件处理位时序、CRC检查和产生、位填充、错误计数器、重新同步、 错误帧产生等。 可作为微控制器的片上外设或独立器件

¬ 提示信息:英飞凌公司不再提供独立的CAN控制器,可用新型低成本XC800 微控制器家族CAN衍生产品来替代。

报文1

报文2

报文3

报文4

源总线 速度A

节点A

无 需

MultiCAN/TwinCAN

节点B

CP U干 预

目标总线 速度B

报文1

报文2

报文3

报文4

至FIFO 对象n

2009-11-17

至FIFO 对象n+1

至FIFO 对象n+2

至FIFO 对象n+3

Page 19

Copyright © Infineon Technologies 2009. All rights reserved.

英飞凌哪些MCU器件具有 -- Bosch CAN? C161JC C161CS

2x Bosch CAN

C164CM C164CI C505CA C515C C164CL C167CR C167CS

高性能实时信号处理器XE166家族简介

16x16位乘法运算:5个周期 16x16位乘法运算:5个周期 32/16位除法运算:10个周期 32/16位除法运算:10个周期 C166指令集 C166指令集 ROM ROM OTP OTP CAN CAN PWM PWM ADC、SSC、ASC、定时器 ADC、SSC、ASC、定时器 80 引脚 M-QFP 80 引脚 M-QFP 100 引脚 M-QFP 100 引脚 M-QFP 144 引脚 M-QFP 144 引脚 M-QFP

9/4/2009 Copyright © Infineon Technologies 2009. All rights reserved. Page 9

XE166 架构 (以XE167FM系列为例)

9/4/2009

Copyright © Infineon Technologies 2009. All rights reserved.

C166SV2 128-320 26-34 8-16 16 2 0 / 2 (64) 9 / 11 / 16 4/6 0 1 2 QFP 64 / 100 - 40°C - +125°C

程序 [PSRAM] 数据 [DSRAM] 双口 [DPRAM]

CAN ADC 节点数(报文对象数) 通道数 CCU 1 CCU 2 CCU 6 封装 温度 (Tambient)

9/4/2009

Copyright © Infineon Technologies 2009. All rights reserved.

Page 11

1. 集成度最高 – 节约成本

2.5 V电压调节器

单电源供电 (嵌入式电压调节器) 用于产生内核电压 由电源验证电路来监控电压 欠压检测

电源看门狗

EtherCAT ECAT-2000 数字输入输出模块用户指南说明书

EtherCAT® is a registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany.Copyright © 2013 by ICP DAS Co., Ltd. All rights are reserved.U ser Manual forSlave Modules ECAT ‐2000 with Digital Inputs andOutputsWarrantyAll products manufactured by ICP DAS are under warranty regarding defective materials for a period of one year, beginning from the date of delivery to the original purchaser.WarningICP DAS assumes no liability for any damage resulting from the use of this product. ICP DAS reserves the right to change this manual at any time without notice. The information furnished by ICP DAS is believed to be accurate and reliable. However, no responsibility is assumed by ICP DAS for its use, nor for any infringements of patents or other rights of third parties resulting from its use.CopyrightCopyright © 2013 by ICP DAS. All rights are reserved.TrademarksNames are used for identification purpose only and may be registered trademarks of their respective companies.Technology SupportIf you have any question for our products, please contact us directly or email to ******************.The shipping package includes the following items:NOTICEIf any of these items is missing or damaged, please contact your local distributor for more information. Keep the shipping materials and overall package in case you want to ship the module back in the future.More⏹ Manual:CD: \fieldbus_cd \ethercat\slave \ecat-2000\manual /pub/cd/fieldbus_cd/ethercat/slave/ecat-2000/manual/ ⏹ ENI:CD: \fieldbus_cd \ethercat \slave \ecat-2000\software/pub/cd/fieldbus_cd/ethercat/slave/ecat-2000/software/ ⏹ FAQ:/root/support/faq/faq.htmlECAT ‐2000 CDQuick StartTable of Contents1 INTRODUCTION (1)2 HARDWARE INFORMATION (2)2.1 ECAT‐2000 G ENERAL T ECHNICAL D ATA (2)2.1.1 E THER CAT I NTERFACE (3)2.1.2 P OWER AND F.G. C ONNECTOR (3)2.1.3 P OWER LED (3)2.1.4 S TATUS LED S (3)2.1.5 I/O S TATUS LED S (3)2.1.6 D IMENSIONS (4)2.2 ECAT‐2045 (5)2.2.1 S PECIFICATIONS (5)2.2.2 I/O C ONNECTOR (P IN A SSIGNMENT) (6)2.2.3 I/O S TATUS LED S (7)2.2.4 W IRE C ONNECTION (7)2.3 ECAT‐2051 (8)2.3.1 S PECIFICATIONS (8)2.3.2 I/O C ONNECTOR (P IN A SSIGNMENT) (9)2.3.3 I/O S TATUS LED S (10)2.3.4 W IRE C ONNECTION (10)2.4 ECAT‐2052 (11)2.4.1 S PECIFICATIONS (11)2.4.2 I/O C ONNECTOR (P IN A SSIGNMENT) (12)2.4.3 I/O S TATUS LED S (13)2.4.4 W IRE C ONNECTION (13)2.5 ECAT‐2052‐NPN (14)2.5.1 S PECIFICATIONS (14)2.5.2 I/O C ONNECTOR (P IN A SSIGNMENT) (15)2.5.3 I/O S TATUS LED S (16)2.5.4 W IRE C ONNECTION (16)2.6 ECAT‐2053 (17)2.6.1 S PECIFICATIONS (17)2.6.2 I/O C ONNECTOR (P IN A SSIGNMENT) (18)2.6.3 I/O S TATUS LED S (19)2.6.4 W IRE C ONNECTION (19)2.7 ECAT‐2055 (20)2.7.1 S PECIFICATIONS (20)2.7.2 I/O C ONNECTOR (P IN A SSIGNMENT) (21)2.7.3 I/O S TATUS LED S (22)2.7.4 W IRE C ONNECTION (22)2.8 ECAT‐2057 (23)2.8.1 S PECIFICATIONS (23)2.8.2 I/O C ONNECTOR (P IN A SSIGNMENT) (24)2.8.3 I/O S TATUS LED S (25)2.8.4 W IRE C ONNECTION (25)2.9 ECAT‐2057‐NPN (26)2.9.1 S PECIFICATIONS (26)2.9.2 I/O C ONNECTOR (P IN A SSIGNMENT) (27)2.9.3 I/O S TATUS LED S (28)2.9.4 W IRE C ONNECTION (28)2.10 ECAT‐2060 (29)2.10.1 S PECIFICATIONS (29)2.10.2 I/O C ONNECTOR (P IN A SSIGNMENT) (30)2.10.3 I/O S TATUS LED S (31)2.10.4 W IRE C ONNECTION (31)3 SOFTWARE COMMUNICATIONS (32)3.1 S TARTUP (32)3.2 C ONFIGURATION (32)A GLOSSARY (37)A.1 O RDERING I NFORMATION (37)A.2 T ECHNICAL S UPPORT (37)The ECAT-2000 series are industrial EtherCAT slave remote I/O modules and equipped with the EtherCAT protocol and installed by daisy chain connection which permits the flexibility in devices installation and reduces infrastructure and operation costs. All the modules can be deployed in the network topologies such as star, line or ring. The isolated input and output design protects the ECAT-2000 against the harmful interference and environment.The ECAT-2000 has passed and verified by the conformance test tool, therefore eligible EtherCAT Master or configurator can manipulate it simply and implement your various applications easily. Fig 1.1 is shown a typical EtherCAT application.F igure 1.1 Typical Application of ECAT-2000.2.1 ECAT ‐2000 General Technical DataF igure 2.1 Appearance of ECAT-200021 Power LED4IN: to Master I/O Status LEDs 6OUT: to Next the EtherCAT Slave EtherCAT Interface I/O Connector 7DIN-Railinstallation3Power and F .G.Connector Status LEDs 52.1.1 EtherCAT InterfaceNotationDescription INEtherCAT data processing, direction to the EtherCAT master OUT EtherCAT data processing, direction to the next slave device 2.1.2 Power and F.G. ConnectorNotationDescription +VsPower Supply with +10~+30VDC GNDPower Supply Ground F.G. Frame Ground; i.e. Earth Contact2.1.3 Power LEDNotationColor States Description PWR RED On The device is powered up 2.1.4 Status LEDsNotation Color StatesDescription OffThe device is in state INIT BlinkingThe device is in state PRE ‐OPERARIONAL Single FlashThe device is in state SAFE ‐OPERARIONAL RUN Green OnThe device is in state OPERARIONAL OffNo link BlinkingLink and activity Link Activity IN/OUT Green On Link without activity2.1.5 I/O Status LEDsNotationColor States Description OffInput voltage is below the lower switching threshold voltage DI Green OnInput voltage is higher than the upper switching threshold voltage OffDigital output status is “Off” DO GreenOn Digital output status is “On”2.1.6DimensionsLeft Side View Front ViewTop ViewRight Side ViewBottom ViewRear ViewUnit: mm2.2 ECAT ‐2045The ECAT-2045 is an industrial EtherCAT slave I/O module which is built in 16 isolated digital outputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.2.1 SpecificationsDigital OutputChannels16 Output TypeOpen Collector (Sink) Load Voltage+3.5 ~ +50 V Max. Load Current700mA per Channel Isolation Voltage3750 Vrms PowerInput Voltage Range10V ~ 30VDC Power ConsumptionMax. 4W Communication InterfaceConnector2 x RJ ‐45 ProtocolEtherCAT Distance between StationsMax. 100 m (100BASE ‐TX) Data Transfer MediumEthernet/EtherCAT Cable (Min. CAT 5), Shielded MechanismInstallationDIN ‐Rail Dimensions110mm x 90mm x 33mm (H x W x D, without connectors) Case Material UL 94V ‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class A Surge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.2.2I/O Connector (Pin Assignment)2.2.3I/O Status LEDsNotation Color States DescriptionOff Digital output status is “Off”DO GreenOn Digital output status is “On”2.2.4Wire Connection2.3 ECAT ‐2051The ECAT-2051 is an industrial EtherCAT slave I/O module which is built in 16 isolated digital inputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.3.1SpecificationsDigital Input Channels 16Input TypeDry (Source) Wet (Sink/Source) Off Voltage Level Open +4V Max. On Voltage Level Close to GND +10 V ~ +50 VIsolation Voltage 3750 VDCPowerInput Voltage Range 10V ~ 30VDC Power Consumption Max. 4WCommunication Interface Connector 2 x RJ ‐45 ProtocolEtherCATDistance between Stations Max. 100 m (100BASE ‐TX)Data Transfer Medium Ethernet/EtherCAT Cable (Min. CAT 5), ShieldedMechanism Installation DIN ‐RailDimensions 110mm x 90mm x 33mm (H x W x D, without connectors) Case MaterialUL 94V ‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class A Surge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.3.2I/O Connector (Pin Assignment)2.3.3I/O Status LEDsNotation Color States DescriptionOff Input voltage is lower than +4VDC(Max.)DI GreenOn Input voltage is higher than “Off” state2.3.4Wire Connection2.4 ECAT ‐2052The ECAT-2052 is an industrial EtherCAT industrial slave I/O module built in 8 isolated digital inputs and 8 isolated digital outputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.4.1SpecificationsDigital Input Channels 8Input TypeWet (Sink/Source) Off Voltage Level +2V Max. On Voltage Level Close to GND +3.5 V ~ +50 VIsolation Voltage 3750 VDCDigital Output Channels 8Output Type Open Source (Source) Load Voltage +3.5 ~ +50 V Max. Load Current 100mA per Channel Isolation Voltage 3750 VrmsCommunication Interface Connector 2 x RJ ‐45 ProtocolEtherCATDistance between Stations Max. 100 m (100BASE ‐TX)Data Transfer Medium Ethernet/EtherCAT Cable (Min. CAT 5), ShieldedPowerInput Voltage Range 10V ~ 30VDCPower Consumption Max. 4WMechanismInstallation DIN‐RailDimensions 110mm x 90mm x 33mm (H x W x D, without connectors) Case Material UL 94V‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class ASurge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.4.2I/O Connector (Pin Assignment)2.4.3I/O Status LEDsNotation Color States DescriptionOff Input voltage is lower than +3.5VDC(Max.)DI GreenOn Input voltage is higher than “Off” stateOff Digital output status is “Off”DO GreenOn Digital output status is “On”2.4.4Wire Connection2.5 ECAT ‐2052‐NPNThe ECAT-2052-NPN is an industrial EtherCAT industrial slave I/O module built in 8 isolated digital inputs and 8 isolated digital outputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.5.1SpecificationsDigital Input Channels 8Input TypeWet (Sink/Source) Off Voltage Level +2V Max. On Voltage Level +3.5 V ~ +50 V Isolation Voltage 3750 VDCDigital Output Channels 8Output Type Open Collector Load Voltage +3.5 ~ +50 V Max. Load Current 100mA per Channel Isolation Voltage 3750 VrmsCommunication Interface Connector 2 x RJ ‐45 ProtocolEtherCATDistance between Stations Max. 100 m (100BASE ‐TX)Data Transfer Medium Ethernet/EtherCAT Cable (Min. CAT 5), ShieldedPowerInput Voltage Range 10V ~ 30VDC Power ConsumptionMax. 4WMechanismInstallation DIN‐RailDimensions 110mm x 90mm x 33mm (H x W x D, without connectors) Case Material UL 94V‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class ASurge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.5.2I/O Connector (Pin Assignment)2.5.3I/O Status LEDsNotation Color States DescriptionOff Input voltage is lower than +3.5VDC(Max.)DI GreenOn Input voltage is higher than “Off” stateOff Digital output status is “Off”DO GreenOn Digital output status is “On”2.5.4Wire Connection2.6 ECAT ‐2053The ECAT-2053 is an industrial EtherCAT slave I/O module which is built in 16 isolated digital inputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.6.1SpecificationsDigital Input Channels 16Input TypeWet (Sink/Source) Off Voltage Level +2V Max. On Voltage Level +3.5V ~ +50 V Isolation Voltage 3750 VDCPowerInput Voltage Range 10V ~ 30VDC Power Consumption Max. 4WCommunication Interface Connector 2 x RJ ‐45 ProtocolEtherCATDistance between Stations Max. 100 m (100BASE ‐TX)Data Transfer Medium Ethernet/EtherCAT Cable (Min. CAT 5), ShieldedMechanism Installation DIN ‐RailDimensions 110mm x 90mm x 33mm (H x W x D, without connectors) Case Material UL 94V ‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class A Surge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.6.2I/O Connector (Pin Assignment)2.6.3I/O Status LEDsNotation Color States DescriptionOff Input voltage is lower than +3.5VDC(Max.)DI GreenOn Input voltage is higher than “Off” state2.6.4Wire Connection2.7 ECAT ‐2055The ECAT-2055 is an industrial slave I/O module built in 8 isolated digital inputs and 8 isolated digital outputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.7.1 SpecificationsDigital Input Channels 8Input Type Dry (Source) Wet (Sink/Source) Off Voltage Level Open +4V Max. On Voltage Level Close to GND +10 V ~ +50 VIsolation Voltage 3750 VDCDigital Output Channels 8Output Type Open Collector (Sink) Load Voltage +3.5 ~ +50 V Max. Load Current 700mA per Channel Isolation Voltage 3750 Vrms Communication Interface Connector 2 x RJ ‐45 ProtocolEtherCATDistance between Stations Max. 100 m (100BASE ‐TX)Data Transfer MediumEthernet/EtherCAT Cable (Min. CAT 5), ShieldedPowerInput Voltage Range 10V ~ 30VDCPower Consumption Max. 4WMechanismInstallation DIN‐RailDimensions 110mm x 90mm x 33mm (H x W x D, without connectors) Case Material UL 94V‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class ASurge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.7.2I/O Connector (Pin Assignment)2.7.3I/O Status LEDsNotation Color States DescriptionOff Input voltage is lower than +4VDC(Max.)DI GreenOn Input voltage is higher than “Off” stateOff Digital output status is “Off”DO GreenOn Digital output status is “On”2.7.4Wire Connection2.8 ECAT ‐2057The ECAT-2057 is an industrial EtherCAT slave I/O module which is built in 16 isolated digital outputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.8.1SpecificationsDigital OutputChannels16Output Type Open Source (Source) Load Voltage +3.5 ~ +30 V Max. Load Current 100mA per Channel Isolation Voltage 3750 VrmsPowerInput Voltage Range 10V ~ 30VDC Power Consumption Max. 4WCommunication Interface Connector 2 x RJ ‐45 ProtocolEtherCATDistance between Stations Max. 100 m (100BASE ‐TX)Data Transfer Medium Ethernet/EtherCAT Cable (Min. CAT 5), ShieldedMechanism Installation DIN ‐RailDimensions 110mm x 90mm x 33mm (H x W x D, without connectors) Case MaterialUL 94V ‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class A Surge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.8.2I/O Connector (Pin Assignment)2.8.3I/O Status LEDsNotation Color States DescriptionOff Digital output status is “Off”DO GreenOn Digital output status is “On”2.8.4Wire Connection2.9 ECAT ‐2057‐NPNThe ECAT-2057-NPN is an industrial EtherCAT slave I/O module which is built in 16 isolated digital outputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.9.1SpecificationsDigital OutputChannels16Output Type Open Collector (Sink) Load Voltage +3.5 ~ +30 V Max. Load Current 100mA per Channel Isolation Voltage 3750 VrmsPowerInput Voltage Range 10V ~ 30VDC Power Consumption Max. 4WCommunication Interface Connector 2 x RJ ‐45 ProtocolEtherCATDistance between Stations Max. 100 m (100BASE ‐TX)Data Transfer Medium Ethernet/EtherCAT Cable (Min. CAT 5), ShieldedMechanism Installation DIN ‐RailDimensions 110mm x 90mm x 33mm (H x W x D, without connectors) Case MaterialUL 94V ‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class A Surge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.9.2I/O Connector (Pin Assignment)2.9.3I/O Status LEDsNotation Color States DescriptionOff Digital output status is “Off”DO GreenOn Digital output status is “On”2.9.4Wire Connection2.10 ECAT ‐2060The ECAT-2060 is an industrial slave I/O module built in 6 isolated digital inputs and 6 isolated relay outputs. Users can obtain the input and output status not only via the process data but also from its LED indicators.2.10.1 SpecificationsDigital Input Channels 6Input Type Dry (Source) Wet (Sink/Source) Off Voltage Level Open +4V Max. On Voltage Level Close to GND +10 V ~ +50 VIsolation Voltage 3750 VDCDigital Output Channels 6Output TypeForm A (SPST ‐NO)Contact Rating (Resistive Load) 5A@30VDC; 5A@125/250VAC(47~63Hz) Operate Time 10 ms Max. Release Time 5 ms Max. Mechanical Endurance 2 x 107 Ops. Electrical Endurance 105 Ops. PowerInput Voltage Range 10V ~ 30VDC Power ConsumptionMax. 4WCommunication InterfaceConnector 2 x RJ‐45Protocol EtherCATDistance between Stations Max. 100 m (100BASE‐TX)Data Transfer Medium Ethernet/EtherCAT Cable (Min. CAT 5), Shielded MechanismInstallation DIN‐RailDimensions 110mm x 90mm x 33mm (H x W x D, without connectors) Case Material UL 94V‐0 LevelEnvironmentOperating Temperature ‐25°C ~ 75°CStorage Temperature ‐30°C ~ 80°CRelative Humidity 10 ~ 90%, No CondensationESD (IEC 61000‐4‐2) 4 KV Contact for Each ChannelEFT (IEC 61000‐4‐4) Power: 1 KV Class A; Signal: 1 KV Class ASurge (IEC 61000‐4‐5) 1 KV Class AHi‐Pot 1KV Class A2.10.2 I/O Connector (Pin Assignment)2.10.3 I/O Status LEDsNotation Color States DescriptionOff Input voltage is lower than +4VDC(Max.)DI GreenOn Input voltage is higher than “Off” stateOff Digital output status is “Off”DO GreenOn Digital output status is “On”2.10.4 Wire Connection3 Software Communications3.1StartupEtherCAT devices are described in an XML file, ESI (EtherCAT Slave Information) file, which describes the modules of the ECAT-2000 series named "ICPDAS ECAT‐2000.xml."1.Download the ESI file, ICPDAS ECAT‐2000.xml, from the website/pub/cd/fieldbus_cd/ethercat/slave/ecat-2000/software/ or from the CD in the shipping packageCD: \fieldbus_cd\ethercat\slave\ecat-2000\software2.Copy the file "ICPDAS ECAT‐2000.xml" to the destination folder of EtherCATMaster Tools(Beckhoff EtherCAT Configurator or TwinCAT etc.)C:\EtherCAT Configurator\EtherCAT\ICPDAS ECAT-2000.xmlC:\TwinCAT\Io\EtherCAT\ICPDAS ECAT-2000.xmlOtherwise, if you are using another tool, to the folder set for that tool.3.2ConfigurationThis section is described the configuration using the example of ECAT-2055 and the EtherCAT Configurator supplied by Beckhoff. Otherwise, if another tool is used, choose a configuration method as applicable.1.Start your EtherCAT Configurator.2.Choose File, New to create a new I/O Configuration.3.Click I/O Device with the right mouse button and choose Append Device...in the menu, and then the dialog window Insert Device is opened.4.Select the EtherCAT type in this dialog window and confirm with OK.5.Device 1 (EtherCAT) is added to to your configuration, i.e. a new EtherCATline. Click Device 1(EtherCAT) with the right mouse button and choose Scan Boxes... in the menu.6.Choose the correct network device which is connected to ECAT-2000.7.If the hint is shown, click Yes/OK and continue.8.Click Yes to start scanning for ECAT-2000.9.Click Yes to activate the free run mode for EtherCAT Configurator.10.The ECAT‐2000 (Box 1)is now shown in the EtherCAT Configurator.11.The input and output variables contained in the ESI (*.xml) file of theECAT-2000 are displayed as CANopen Process Data Objects(PDO). The PDOs are listed in the PDO List of the Process Data tab.A GlossaryA.1Ordering InformationEtherCAT Slave DIO ModulesECAT‐2045CR EtherCAT Slave I/O Module with Isolated 16‐ch DO (RoHS)ECAT‐2051 CR EtherCAT Slave I/O Module with Isolated 16‐ch DI (RoHS)ECAT‐2055 CR EtherCAT Slave I/O Module with Isolated 8‐ch DO and 8‐ch DI (RoHS)ECAT‐2060 CR EtherCAT Slave I/O Module with Isolated 6‐ch Relay DO and 6‐ch DI (RoHS)A.2Technical SupportIf you have any difficulties using your ECAT-2000 series modules, please contact us or send a description for the problem to ******************.。

XC2000使用说明书

XC-2000行波测距软件用户手册淄博科汇电气有限公司Kehui Electric Co. Ltd.,Zibo目录1绪论 (2)2XC-2000行波测距软件的安装 (3)2.1 XC-2000运行的硬件环境 (3)2.2 XC-2000运行的软件环境 (3)2.3 XC-2000的安装步骤 (3)2.4 XC-2000系统的外部连接 (4)2.5 XC-2000系统的启动 (4)2.6 XC-2000系统的卸载 (4)3XC-2000的使用方法 (5)3.1 XC-2000的主窗口 (5)3.1.1主窗口布局 (5)3.1.2主窗口操作 (6)3.1.3双端波形分析窗口 (7)3.1.4单端波形分析窗口 (9)3.2 XC-2000的主菜单 (10)3.2.1系统设置菜单 (10)3.2.2通讯菜单 (13)3.2.3行波测距 (15)3.2.4数据维护菜单 (16)3.2.5帮助菜单 (18)1 绪论本手册为您提供了行波测距分析软件(XC-2000)2.0版本的各项功能和操作方法的介绍。

借助于本软件,您可以收集本站XC-11或XC-21装置采集的行波数据,请求线路对端装置采集的行波数据,自动实现故障的双端定位分析。

同时可以实现本端行波数据的自动对端远传和主站上传,对于熟练的用户借助本软件能够实现直观的波形分析,根据自己的经验校正测距结果。

本章从全局的角度向您介绍了XC-2000行波测距分析软件,对于使用XC-2000的用户,请详细阅读本章。

以下向您简要介绍一下XC-2000的功能概要以及本用户手册的组织结构。

XC-2000软件包概要本软件可在Windows 98或Windows NT 2000环境下的PC机上安装并运行,具体功能包括:u 收集本站装置采集的行波数据u 行波数据的自动远传u 人工请求远方数据u 人工计算测距结果u 行波数据的软盘拷贝u 波形的单端及双端辅助分析本用户手册的组织结构您在使用XC-2000 V2.0时,所遇到的各种问题,在本手册中都会得到详细的解释。

英飞凌CAN功能系列MCU介绍

Page 4

CAN出现之前 – 点对点连线

空调 引擎 控制 防抱死 制动 照明 电控 门锁

仪表 盘 气囊 电控 车窗

变速箱 控制

主动 悬架

电控 座椅

Page 5

CAN总线拓扑图

空调 引擎 控制 CAN 高速 防抱死 制动 CAN CAN 仪表盘 CAN 照明 CAN CAN 低速 CAN CAN 变速箱 控制 CAN 主动 悬架 电控 座椅 CAN 电控 车窗 CAN 气囊 电控 门锁 CAN

收发器 CAN未规定必须使用哪种收发器

¬ 由于有许多不同类型的CAN收发器,因此微控制器未集成收发器

通常使用双绞线 有些CAN收发器使用单线,有些CAN收发器具有容错能力

2009-11-17

Copyright © Infineon Technologies 2009. All rights reserved.

报文1

报文2

报文3

报文4

源总线 速度A

节点A

无 需

MultiCAN/TwinCAN

节点B

CP U干 预

目标总线 速度B

报文1

报文2

报文3

报文4

至FIFO 对象n

2009-11-17

至FIFO 对象n+1

至FIFO 对象n+2

至FIFO 对象n+3

Page 19

Copyright © Infineon Technologies 2009. All rights reserved.

英飞凌哪些MCU器件具有 -- Bosch CAN? C161JC C161CS

2x Bosch CAN

C164CM C164CI C505CA C515C C164CL C167CR C167CS

Verifone v200c支付终端快速入门指南说明书

Contents

Contents:

• Installation and Activation • Performing a Sale • Performing a Refund • Performing a Reconciliation

BACK TO START

PREVIOUS

NEXT

Installation and Activation

PREVIOUS

NEXT

Performing a Refund

Touch the main logo at the top of the screen. From the main menu, select Onetime Transactions and then select Refund.

BACK TO CONTENTS

Installation and Activation

BACK TO CONTENTS

PREVIOUS

NEXT

Installation and Activation

Turn the v200c over. Remove the backplate by lifting the tab. The backplate will separate from the device.

BACK TO CONTENTS

VIOUS

NEXT

Performing a Reconciliation

A report will be printed for your records.

BACK TO CONTENTS

PREVIOUS

If selected, the second receipt is to be given to the customer. If the customer’s payment card was inserted, it can now be removed.

基于XC166单片机的DSP优化方法

基于XC166单片机的DSP优化方法

王光宇

【期刊名称】《单片机与嵌入式系统应用》

【年(卷),期】2006(000)004

【摘要】XC166系列单片机是英飞凌推出的新一代16位单片机系列,在国际上已被广泛应用于汽车电子及工业控制,目前也在中国大力推广.XC166系列单片机是最早在单片机中引入数字信号处理(DSP)模块的16位单片机,比其他16位单片机具有更强的DSP处理能力.文中介绍几种基于XC166单片机的DSP优化方法,其中的通用优化方法也可以用于其他的单片机或数字信号处理器.

【总页数】4页(P20-23)

【作者】王光宇

【作者单位】英飞凌科技公司

【正文语种】中文

【中图分类】TN43

【相关文献】

1.基于DSP的数字图像预处理算法优化方法 [J], 陈松;郑红;吴兴华;隋强强

2.基于ADSP-TS201的混合汇编优化方法 [J], 崔倩;张朗

3.基于DSP的图像去雾算法优化方法 [J], 杨梦雯;李宝明;陈付亮;王洪玉

4.基于DSP软加固下的功耗优化方法 [J], 姚天问;周海芳;方民权;申小龙

5.基于TMS320C64xDSP的汇编优化方法 [J], 郑回青;林嘉宇;张镔

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 简介

1.1 概述

本应用笔记提供了一些关于XC2000/XE166家族16位微控制器的模拟数字转换模块(ADC)的主要功能单元的详细信息。

本应用笔记将结合一个能给模块的使用很好启示的例子来讨论ADC模块的功能描述和配置选项。

1.2 背景

为了满足应用程序的实时要求,能减轻CPU负载的自主ADC模块是必需的。

XC2000/XE166家族的微控制器提供了一个最适合汽车和工业应用的需求的专门的ADC模块。

此ADC模块利用自身专有的硬件电路自主工作,从而减少CPU负载。

因此,CPU可以用于其它主要的任务。

ADC 模块包含两个独立的内核(ADC0、ADC1),它们可独自工作、也可同步工作。

ADC 内核用于进行模数转换,并提供多种触发转换、数据处理和结果保存的方式。

有了这个结构,便可支持高达两个模拟输入通道的并行转换。

1.3 ADC模块的特点

XC2000/XE166系列微控制器包括16路多路模拟输入的10位模拟- 数字转换通道。

该ADC模块采用逐次逼近技术以8个不同的电源来转换模拟电压。

ADC模块的特点包括:

∙3个转换请求源,可选外部事件或定时器事件触发,自动扫描,可编程序列及软件触发等转换方式。

∙两个ADC 内核可同步工作,用于同时开始转换、对模拟输入信号并行采样和测量(如用于测量AC 驱动器的相电流)。

∙外部模拟复用器的控制功能,考虑附加的建立时间和扫描支持。

∙采样时间可调整,从而可和不同模拟信号源(传感器等)的输出阻抗匹配。

∙可取消正在执行的转换、并根据需要自动重新启动转换。

∙灵活的中断产生(支持PEC)。

∙极限检查功能用于降低中断负载(如用于温度测量或过载检测,只有当数值超过可编程边界值时才产生中断)。

∙可编程数据压缩滤波器(如用于数字抗混叠滤波),可叠加多个(个数可编程)转换结果。

∙独立的结果寄存器(8 个独立的寄存器)。

∙支持转换结果FIFO 缓存机制,从而允许更长的中断延迟。

∙支持挂起和省电模式。

∙每路通道的参考输入可单独编程选择,从而可通过同一个ADC 内核对3.3V 和5V 范围内的信号进行测量。

2 ADC模块的工作规则

2.1 ADC模块的功能简介

在16位单片机的XC2000/XE166家族中,ADC模块由两个独立内核(ADC0、ADC1)组成。

它们可独自工作、也可同步工作。

图1给出了ADC模块的大致框图。

Figure 1 ADC模块框图

每个ADC内核包括:

∙模数转换器,最多带有16 路模拟输入(CH0 - CH15)。

该模块选择一路输入信号CHx、将该通道上的模拟电压转换为数据值。

∙转换控制单元,定义诸如采样时间、转换精度和参考电压等转换参数。

采样时间和转换精度对于多个通道来说是相似的,因此可分组构成“输入组”。

每路通道可单独分配一个输入组来定义这些参数。

转换控制还用于处理转换的开始条件,比如立即开始(取消-插入-重复)、覆盖前一个转换结果(等待读取)、或ADC 内核同步(并行转换)。

∙请求控制单元,定义接下来将要转换哪路模拟输入通道。

它包含 3 个请求源,可根据不同的事件(如PWM 或定时器信号的跳变沿、或端口引脚上的事件)触发转换。

每个请求源可顺序触发1 路、4 路、至最多16 路转换。

∙结果处理单元,提供8 个结果寄存器用于保存转换结果。

结果处理模块还支持数据压缩(比如用于数字抗混叠滤波),通知CPU 新数据可用之前自动叠加4 次的转换结果。

此外,结果寄存器可级联构成FIFO 结构,从而可同时保存多个转换结果(前一个转换结果不被覆盖)。

该特性还有助于处理CPU 中断响应。

∙中断产生单元,根据ADC 事件向CPU 发送中断请求。

ADC 内核可基于不同的机制产生中断,如一些中断和转换结果所在范围(极限检查)有关,一些中断可将转换结果传送到内存单元中以备后续处理;在完成整个一系列转换之后也会产生一些中断。

2.2 ADC模块时钟方案

ADC 内核中的时钟信号均基于f ADC时钟产生。

图2给出了ADC内核时钟方案的示意图。

Figure 2 ADC时钟方案

和其它模块一样,ADC模块使用系统时钟来进行操作。

由于ADC时钟没有分频器,因此如果ADC模块被选择了,则f ADC = f SYS。

ADC模块使用两个内部时钟信号f ADCI(用于模数转换器)和f ADCD (用于仲裁器)。

所有其它数字结构(如中断等)直接由模块时钟f ADC驱动。

2.2.1 模数转换器的模拟时钟产生

模拟时钟f ADCI用作转换器的内部时钟,定义转换时间和采样时间。

f ADCI 可通过编程位域GLOBCTR.DIVA 进行修改。

见图3。

Figure 3 f ADCI模拟时钟调整

DIVA位定义转换器时钟f ADCI(用于计算转换时间和采样时间),由f ADC时钟周期数表示。

DIVA位的配置结果:

00H f ADCI = f ADC Array 01H f ADCI = f ADC/2

02H f ADCI= f ADC/3

• • •.

3F H f ADCI= f ADC/64。