计算机组成原理第三次实验报告

计算机组成原理实验报告

3)在增大合法码的码距时,所有码的码距应尽量均匀增大,以保证对所有码的检错能力平衡提高。

下面具体看一下对一个字节进行海明编码的实现过程。

只实现一位纠错两位检错,由前面的表可以看出,8位数据位需要5位校验位,可表示为H13H12…H2H1。

0

0

1

1

0

0

1

1

0

S1

0

0

1

0

1

0

1

0

1

0

1

0

1

由此可得校验后的数据位表达式为:

D1=D1 (S1•S2• • •S5)

D2=D2 (S1• •S3• •S5)

D3=D3 ( •S2•S3• •S5)

D4=D4 (S1•S2•S3• •S5)

D5=D5 (S1• • •S4•S5)

D6=D6 ( •S2• •S4•S5)

答:我们认为16位数据位的编码原理与8位数据位的hamming编码原理基本相同。即:,在k个数据位之外加上r个校验位,从而形成一个k+r位的新的码字,使新的码字的码距比较均匀地拉大。把数据的每一个二进制位分配在几个不同的偶校验位的组合中,当某一位出错后,就会引起相关的几个校验位的值发生变化,这不但可以发现出错,还能指出是哪一位出错,为进一步自动纠错提供了依据。

《计算机组成原理》

实验报告

实验室名称:S402

任课教师:邹洋

小组成员:王娜任芬

学号:2010212121 2010212119

实验一_Hamming码2

实验二_乘法器7

xx大学计算机组成原理实验报告(全)

上海大学计算机组成原理实验报告(全)《计算机组成原理实验》报告一姓名学号时间地点行健楼 609机房评阅一.数据传送实验1. 实验内容及要求在试验箱上完成以下内容:将58H写入A寄存器。

将6BH写入W寄存器。

将C3H 写入R1寄存器。

2. 实验环境本实验箱用74HC574构成各种寄存器。

3. 实施步骤或参数①注视仪器,打开电源,手不要远离电源开关,随时准备关闭电源,注意各数码管、发光管的稳定性,静待10秒,确信仪器稳定、无焦糊味。

②设置实验箱进入手动模式。

③K2接AEN,K1和K2接EX0和EX1,设置K2K1K0=010,设置K23~K16=01011000。

④注视A及DBUS的发光管,按下STEP键,应看到CK灯灭、A旁的灯亮。

记住看到的实际显示情况。

⑤放开STEP键,应看到CK灯亮、A寄存器显示58。

记住看到的实际情况。

⑥重复上述实验步骤,在做6BH时,K2接WEN,K1和K2接EX2和EX3,设置K2K1K0=010,设置K23~K16=01101011;重复上述实验步骤,在做C3H时,K2接RWR,K1和K2接SB 和SA,设置K2K1K0=001,设置K23~K16=10100011。

⑦关闭实验箱电源。

4. 测试或者模拟结果A寄存器显示58,W寄存器显示6B,R1寄存器显示C3,完成实验目的。

5. 体会本次实验相对简单,只需要三根线便可以完成整个实验,但是,今天认识了实验箱。

124并且在老师的带领下较为完整的认识了整个试验箱,还是很开心的,今后实验箱将是我们学习计算机组成原理的重要工具,也是我们的好朋友。

《计算机组成原理实验》报告二姓名学号时间地点行健楼 609机房评阅二.运算器实验1. 实验内容及要求在试验箱上完成以下内容:计算07H+6AH后左移一位的值送OUT输出。

把39H取反后同64H相或的值送入R2寄存器。

通过人工译码,加深对译码器基本工作原理的理解。

理解命令的顺序执行过程。

计算机组成实验报告

计算机组成实验报告计算机组成实验报告(共3篇)篇一:《计算机组成与结构》实验报告11 .实验目的:1).学习和了解TEC-2000 十六位机监控命令的用法;2).学习和了解TEC-2000 十六位机的指令系统;3).学习简单的TEC-2000 十六位机汇编程序设计;2.实验内容:1).使用监控程序的R 命令显示/修改寄存器内容、D 命令显示存储器内容、E 命令修改存储器内容;2).使用 A 命令写一小段汇编程序,U 命令反汇编刚输入的程序,用G 命令连续运行该程序,用T、P 命令单步运行并观察程序单步执行情况;3、实验步骤1).关闭电源,将大板上的COM1 口与PC 机的串口相连;2).接通电源,在PC 机上运行PCEC.EXE 文件,设置所用PC 机的串口为“1”或“2”, 其它的设置一般不用改动,直接回车即可;3).置控制开关为00101(连续、内存读指令、组合逻辑、16 位、联机),开关拨向上方表示“1”,拨向下方表示“0”,“X”表示任意。

其它实验相同;4).按一下“RESET”按键,再按一下“START”按键,主机上显示:TEC-2000 CRT MONITOR Version 1.0 April 2001Computer Architectur Lab.,Tsinghua University Programmed by He Jia >5).用R 命令查看寄存器内容或修改寄存器的内容a.在命令行提示符状态下输入:R↙;显示寄存器的内容图片已关闭显示,点此查看图片已关闭显示,点此查看b.在命令行提示符状态下输入:R R0↙;修改寄存器R0 的内容,被修改的寄存器与所赋值之间可以无空格,也可有一个或数个空格主机显示:寄存器原值:_在该提示符下输入新的值,再用R 命令显示寄存器内容,则R0 的内容变为0036。

图片已关闭显示,点此查看6).用D 命令显示存储器内容在命令行提示符状态下输入:D 2000↙会显示从2000H 地址开始的连续128 个字的内容;连续使用不带参数的 D 命令,起始地址会自动加128(即80H)。

《计算机组成原理》学生实验报告

《计算机组成原理》学生实验报告(2011~2012学年第二学期)专业:信息管理与信息系统班级: A0922学号:10914030230姓名:李斌目录实验准备------------------------------------------------------------------------3 实验一运算器实验-----------------------------------------------------------7 实验二数据通路实验-------------------------------------------------------13 实验三微控制器实验--------------------------------------------------------18 实验四基本模型机的设计与实现------------------------------------------22实验准备一、DVCC实验机系统硬件设备1、运算器模块运算器由两片74LS181构成8位字长的ALU。

它是运算器的核心。

可以实现两个8位的二进制数进行多种算术或逻辑运算,具体由74181的功能控制条件M、CN、S3、S2、S1、S0来决定,见下表。

两个参与运算的数分别来自于暂存器U29和U30(采用8位锁存器),运算结果直接输出到输出缓冲器U33(采用74LS245,由ALUB信号控制,ALUB=0,表示U33开通,ALUB=1,表示U33不通,其输出呈高阻),由输出缓冲器发送到系统的数据总线上,以便进行移位操作或参加下一次运算。

进位输入信号来自于两个方面:其一对运算器74LS181的进位输出/CN+4进位倒相所得CN4;其二由移位寄存器74LS299的选择参数S0、S1、AQ0、AQ7决定所得。

触发器的输出QCY就是ALU结果的进位标志位。

QCY为“0”,表示ALU结果没有进位,相应的指示灯CY灭;QCY为“1”,表示ALU结果有进位,相应的指示灯CY点亮。

计算机组成原理实验报告

计算机组织与体系结构实验报告班级: ________学号: ____________姓名: ______实验地点: E-Ⅱ区 311 _实验时间:第三批实验一存储器实验1.FPGA中LPM_ROM定制与读出实验一.实验目的1、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性和配置方法。

2、用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于lpm_ROM中;3、在初始化存储器编辑窗口编辑mif文件配置ROM;4、验证FPGA中mega_lpm_ROM的功能。

二.实验原理ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。

CPU 中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB可以构成各种结构的存储器,lpm_ROM是其中的一种。

lpm_ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都是可以设定的。

由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。

图3-1-1中的lpm_ROM有3组信号:inclk——输入时钟脉冲;q[23..0]——lpm_ROM的24位数据输出端;a[5..0]——lpm_ROM的6位读出地址。

实验中主要应掌握以下三方面的内容:⑴ lpm_ROM的参数设置;⑵ lpm_ROM中数据的写入,即LPM_FILE初始化文件的编写;⑶ lpm_ROM的实际应用,在GW48_CP+实验台上的调试方法。

三.实验步骤(1)用图形编辑,进入mega_lpm元件库,调用lpm_rom元件,设置地址总线宽度address[]和数据总线宽度q[],分别为6位和24位,并添加输入输出引脚,如图3-1-1设置和连接。

上海大学计算机组成原理实验报告(全)

《计算机组成原理实验》报告一数据传送实验1.实验内容及要求在试验箱上完成以下内容:将58H写入A寄存器。

将6BH写入W寄存器。

将C3H写入R1寄存器。

2.实验环境本实验箱用74HC574(8D型上升沿触发器)构成各种寄存器。

3.实施步骤或参数①注视仪器,打开电源,手不要远离电源开关,随时准备关闭电源,注意各数码管、发光管的稳定性,静待10秒,确信仪器稳定、无焦糊味。

②设置实验箱进入手动模式。

③ K2接AEN,K1和K2接EX0和EX1,设置K2K1K0=010,设置K23~K16=0101 1000。

④注视A及DBUS的发光管,按下STEP键,应看到CK灯灭、A旁的灯亮。

记住看到的实际显示情况。

⑤放开STEP键,应看到CK灯亮、A寄存器显示58。

记住看到的实际情况。

⑥重复上述实验步骤,在做6BH时,K2接WEN,K1和K2接EX2和EX3,设置K2K1K0=010,设置K23~K16=0110 1011;重复上述实验步骤,在做C3H时,K2接RWR,K1和K2接SB和SA,设置K2K1K0=001,设置K23~K16=1010 0011。

⑦关闭实验箱电源。

4.测试或者模拟结果A寄存器显示58,W寄存器显示6B,R1寄存器显示C3,完成实验目的。

5.体会本次实验相对简单,只需要三根线便可以完成整个实验,但是,今天认识了实验箱,并且在老师的带领下较为完整的认识了整个试验箱,还是很开心的,今后实验箱将是我们学习计算机组成原理的重要工具,也是我们的好朋友。

运算器实验1.实验内容及要求1(1)在试验箱上完成以下内容:计算07H+6AH后左移一位的值送OUT输出。

把39H取反后同64H相或的值送入R2寄存器。

(2)通过人工译码,加深对译码器基本工作原理的理解。

理解(微)命令的顺序执行过程。

2.实验环境在实验箱上使用微程序来完成。

3.实施步骤或参数①注视仪器,打开电源,手不要远离电源开关,随时准备关闭电源,注意各数码管、发光管的稳定性,静待10秒,确信仪器稳定、无焦糊味。

计算机组成原理实验报告

实验一报告内容实验题目:运算器实验实验目的: 1、掌握简单运算器的数据传输方式 2、验证运算功能发生器( 74LS181)及进位控制的组合功能。

实验要求:完成不带进位及带进位算术运算实验、逻辑运算实验,了解算术逻辑运算单元的运用。

实验器材:电子试验箱运算器组成框图:ALU的功能图实验原理:实验中所用的运算器原理如图1-1所示。

其中运算器山两片74LS181以并/串形式构8位字长的ALU。

运算器的输出经过一个三态门(74LS245)和数据总线相连’运算器的两个数据输入端分别由-个锁存器(74LS273)锁存,锁存器的输入已连至数据总线,数据丌关(INPUT UNIT)用来给出参与运算的数据,经一三态门(74LS245)和数据总线相连,数据显示灯(BUS UNIT)已和数据总线相连,用来显示数据总线内容。

本实验装置的控制线(CTR-IN UNIT)应与(CTR-OUT UNIT)相连,数据总线、时序电路( TIME UNIT)产生的脉冲信号(T1-T4)、P(1)、P(2)、P(3)本实验装置已作连接, ( CLK UNIT)必须选择一档合适的时钟,其余均为电平控制信号(HC-UNIT)。

进行实验时,首先按动位于本实验装置右中则的复位按钮使系统进入初始待令状态,在LED显示器闪动出现“P.”的环境下,按动增址命令键使LED显示器自左向右第一位显示提示符H”,表示本装置已进入手动单元实验状态,在该状态下按动单步命令键,即可获得实验所需的单脉冲信号,而各电平控制信号用位于LED显示器左方的K25~KO二进制数据开关来模拟。

在进行手动实验时,必须先预置开关电平:,Load=l, /CE- 1,其余开关控制信号电平均置为0,这在以后手动实验时不再说明,敬请注意。

实验连接:按上图实验线路作以下连接:1、八付运算器控制信号连接:位于实验装置左上方的控制信号(CrR_OLff UNIT)中的(S3、S2. S1. SO.M、/CN. LDDRl. LDDR2. LDCZY. C、B.A)与位于实验装置右中方的(CTR-IN UNIT)、位于实验装置左中方的(UPC UNIT)、位于右J二方的(艮UNIT)作对应连接。

计算机组成原理实验报告

跳到* T1 18 C6FFFF 存贮器值EM 寄存器PC PC输出 A输出

T0 19 CBFFFF 指令寄存器IR PC输出 A输出

1A FFFFFF A输出

1B FFFFFF A输出

输入 A,#* T1 1C C7FFF7 存贮器值EM 寄存器A PC输出 A输出

0D FFFFFF A输出

0E FFFFFF A输出

0F FFFFFF A输出

A-W A,#* T2 10 C7FFEF 存贮器值EM 寄存器W PC输出 A输出

T1 11 FFFE91 ALU直通 寄存器A标志位C,Z 加运算

T0 12 CBFFFF 指令寄存器IR PC输出 A输出

13 FFFFFF A输出

asm文件:

L1:

输入 A,#55h

输出

输出

输出

输出

输出

输出

输出

输出

输出

输出

输入 A,#22h

输出

输出

输出

输出

输出

输出

输出

输出

输出

输出

输入 A,#55h

A-W A,#22h

输出

输出

输出

输出

输出

输出

输出

输出

输出

输出

跳到L1

END

4中修改的指令集:

mic:

_FATCH_ T0 00 CBFFFF 指令寄存器IR A输出

4.实验箱系统实现指令流水的技巧

一条指令的最后一个微操作与取指无关,就可以把二者合并成一个微指令。若取指令操作(CBFFFF)与它前面的微操作码没有相同的位为0,则这两个微操作码的“与”就是二者合并后的微指令。在程序中这条指令就会和它的后继指令形成二级流水模式。

计算机组成原理实验三报告

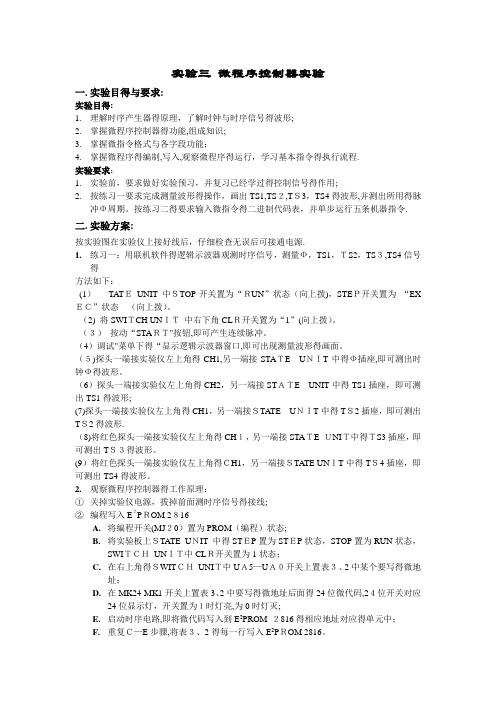

管理学院信息管理与信息系统专业 3 班______组、学号姓名协作者教师评定_____________实验题目_微程序控制器实验__________________1.实验目的与要求:实验目的:(1).理解时序产生器的原理,了解时钟和时序信号的波形。

(2).掌握微程序控制器的功能、组成知识。

(3).掌握微指令格式和各字段功能。

(4).掌握微程序的编制、写入、观察微程序的运行,学习基本指令的执行流程。

实验要求:(1).按练习一要求完成测量波形的操作,画出TS1、TS2、TS3、TS4的波形,并测出所用的脉冲Φ的周期。

(2).按练习二的要求输入微指令的二进制代码表,并单步运行五条机器指令。

(3).实验时,结合读、写微指令流程图,选择存储器地址和数据不断对RAM写入数据,执行时为循环重复执行微指令,直到有P2(CLR)清零信号作用时才停止。

(4)结合实验内容,将数据00H-002H存入存储器6116的00H-002H 单元,,写出实验步骤,并在实验中加以验证。

2.实验方案:(1)按要求在实验仪上接好线,仔细检查正确与否,无误后才接通电源,每次实验都要接一些线,先接线,后打开电源,养成不带电接线的习惯,这样可以避免烧坏实验仪器。

(2)编程写入E2PROM28161)将编程开关(MJ20)置为PROM(编程)状态;2)将STATE UNIT中的STEP置为“STEP”状态,STOP置为“RUN”状态;3)在UA5-UA0开关上置要写的某个微地址(八进制);4)在MK24-MK1开关上置要写的微地址相应的24位微代码,24位开关对应24位显示灯,开关量为“1”灯亮,为“0”灯灭;5)启动时序电路(按动启动按钮START),即将微代码写入到E2PROM2816的相应地址对应的单元中;6)重复(3)~(5)步骤将每一条微指令写入E2PROM2816。

(3)校验1)将编程开关置为READ状态;2)将STEP开关置为“STEP”状态,STOP开关置为“RUN”状态;3)在开关UA5~UA0上置好要读的某个微地址;4)按动START键,启动时序电路,观察显示灯MD24-MD1的状态,检查读出的微代码是否已写入的相同。

计算机组成原理实验总报告

计算机组成原理实验报告班级:0411202学号:2012211xxx姓名: kelory_lee2014年12月7日目录1.实验一Hamming码2.实验二乘法器3.实验三时序部件4.实验四CPU_算术逻辑单元5.实验五CPU_指令译码器6.实验六CPU_微程序控制器7.实验七-八CPU_无流水无cache实验1 Hamming码一.实验目的(1)对容错技术有初步了解,理解掌握海明码的原理(2)掌握海明码的编码以及校验方法二.实验内容(1)先连接JTAG线和USB线(CPU实验时才用接此线),然后接实验箱电源线,最后才可以打开电源。

(切记:不能带电插拔Jtag口,否则会损坏实验设备)(2)安装ByteBlaster:Quartus→tools→>programmer→HardwareSetup(在打开programmer窗口的左上角或从Edit菜单—> HardwareSetup 亦可打开)→选Hardware Settings→点击Add Hardware→Hardware type →Altera ByteBlaster→ok即可;Mode选Jtag。

(3)打开Quartus→tools→programmer→AddFile,将hamming.sof(在C盘的相应目录下)下载到FPGA中。

注意进行programmer时,应在program/configure下的方框中打勾,然后下载。

(4)在实验台上通过模式开关选择FPGA独立调试模式010。

首先输入的8位操作数对应开关SD15~SD8,编码后的hamming码在灯A0~A12上体现。

其次开关SA0是控制位,待校验的13位数据对应SD7~SD0与SA5~SA1。

最后比较的结果在灯R4~R0上体现。

观察实验现象并记录相应数据如对8位数据10101100进行hamming编码和校验。

第一,先手工计算校验位P5~P1=_10111__,编码后的hamming码为__1101001101011。

计算机组成原理实验报告

1、根据实验方案框图,调用PC模块,选用适当元器件,画出实验电路逻辑图,并组装成电路。

2、在电路上实现下列手动单功能操作,(控制信息可用电平开关输出电平)。

→ 、

→RAM

RAM→Bus

→

设计提示:

1、利用实验箱中提供的总线接口搭接总线结构,各器件再分别挂到总线上。

2、用一片74LS273作为存贮器的地址寄存器。

一、实验目的

1、了解总线的工作原理

2、掌握总线的传送技术

3、熟悉建立总线的器件特性

二、实验内容

1、根据图2-2所示的实验方案,如果要通过“输出显示”观察到“RAM地址寄存器(AR)”中的数据,请选用适当元器件设计实现。画出实验电路逻辑图,并组装成电路。

2、在设计的电路上实现下列手动单功能操作,并写出操作步骤:

从图中可看出,地址信息及数据信息都是通过同一组数据开关经三态传输门挂上总线,再发送相应的部件的。要区分送入总线的信息是地址还是数据,可以通过对操作时序的控制来实现,本实验由于地址值及内容数据都是通过数据开关人工加载的,因此区分总线上的地址和数据信息也就是人为地操作总线上的某些芯片,打入或读出信息。

图2-2总线传送技术实验方案(例)

图3-2 1k×8位的M2114

五、实验步骤

按照实验内容设计并连接电路,

对单个存贮器地址的写操作如下:

1、 =1,CS=1

2、 =0

3、输入端D3D2D1D0输入地址(0H~15H),打入MAR

4、输入端D3D2D1D0输入数据

5、W/R=0

6、CS=1→0→1

7、返回3,写下一个数据

读操作如下:

1、 =1,CS=1

图1-6简单的节拍脉冲发生器一周期的波形

计算机组成原理实验三报告

南京信息工程大学实验(实习)报告实验(实习)名称按题要求设计存储器日期 2012.4.21 得分指导教师马利系计软院专业计科年级 2010 班次 1班姓名学号一、实验目的综合使用Protel进行综合设计二、实验内容1.完成图纸设置(改图纸号)2.添加元器件库3.CPU采用8086,用4片8K*8位的ROM(采用2764)和10片8K*8位的RAM(采用6264)组成存储器,地址锁存器采用8282,数据缓冲器采用8286,控制信号为DT/R,译码器采用74ALS138;4.绘出完整的原理图。

三、实验练习题某机器中,已知ROM区域的地址空间为0000H~3FFFH(用8K*8位的ROM芯片(2764)构成),RAM的起始地址为6000H,地址空间为40K*16位(用8K*8位的RAM芯片(6264)构成)。

假设RAM芯片有CS和WE(上面有横杠)信号控制端,CPU(8086)的地址总线为A15~A0,数据总线为D15~D0,控制信号为T/W(W上面有横杠),MREQ(上面有横杠),(访存),要求、1。

画出地址译码方案2。

将ROM和RAM同CPU相连四、实验步骤1.新建一个SCH文件;2.place→→part→→→Browse→选择8088;3.Place→Parts→Browse→选择8282,添加两个;4.Place→Parts→Browse→选择8286,添加两个;5.Place→Parts→Browse→选择2764,连续添加四个;6.Place→Parts→Browse→选择6264,连续添加十个;7.Place→Parts→Browse→选择38译码器;8.所有元器件分布如图所示;9.划线并添加网络标签;CPU ALU-8282STB CPU DT/R*-8286T CPUDEN*-8286OE* CPURD*-6264、2764OE* CPU WR*-6264WE*10.将两个8282地址锁存器的OE/相连,并且接地;11.创建网络表Design→→Create Netlist→→OK;12.新建一个PCB文件;13.在keepoutlayer层上划一个6*6的方格14.导入元器件Design→→Load Nets→→Browse→→添加文件,确定后Excute;15. 手动布置原件,使各元件排列整齐。

计算机组成原理实验报告精品9篇

计算机组成原理实验报告课程名称计算机组成原理实验学院计算机专业班级学号学生姓名指导教师20年月日实验一:基础汇编语言程序设计实验1实验目的●学习和了解TEC-XP+教学实验监控命令的用法;●学习和了解TEC-XP+教学实验系统的指令系统;●学习简单的TEC-XP+教学实验系统汇编程序设计。

2实验设备及器材●工作良好的PC机;●TEC-XP+教学实验系统和仿真终端软件PCEC。

3实验说明和原理实验原理在于汇编语言能够直接控制底层硬件的状态,通过简单的汇编指令查看、显示、修改寄存器、存储器等硬件内容。

实验箱正如一集成的开发板,而我们正是通过基础的汇编语言对开发板进行使用和学习,过程中我们不仅需要运用汇编语言的知识,还需要结合数字逻辑中所学的关于存储器、触发器等基本器件的原理,通过串口通讯,实现程序的烧录,实验箱与PC端的通讯。

4实验内容1)学习联机使用TEC-XP+教学实验系统和仿真终端软件PCEC;2)学习使用WINDOWS界面的串口通讯软件;3)使用监控程序的R命令显示/修改寄存器内容、D命令显示存储内容、E命令修改存储内容;4)使用A命令写一小段汇编程序,U命令反汇编输入的程序,用G命令连续运行该程序,用T、P命令单步运行并观察程序单步执行情况。

5实验步骤1)准备一台串口工作良好的PC机器;2)将TEC-XP+放在实验台上,打开实验箱的盖子,确定电源处于断开状态;3)将黑色的电源线一段接220V交流电源,另一端插在TEC-XP+实验箱的电源插座里;4)取出通讯线,将通讯线的9芯插头接在TEC-XP+实验箱上的串口"COM1"或"COM2"上,另一端接到PC机的串口上;5)将TEC-XP+实验系统左下方的六个黑色的控制机器运行状态的开关置于正确的位置,再找个实验中开关应置为001100(连续、内存读指令、组合逻辑、联机、16位、MACH),6)控制开关的功能在开关上、下方有标识;开关拨向上方表示"1",拨向下方表示"0","X"表示任意,其他实验相同;7)打开电源,船型开关盒5V电源指示灯亮;8)在PC机上运行PCEC16.EXE文件,根据连接的PC机的串口设置所用PC机的串口为"1"或"2",其他的设置一般不用改动,直接回车即可; (8)按一下"RESET"按键,再按一下"START"按键,主机上显示:6实验截图及思考题【例3】计算1到10的累加和。

计算机组成原理的实验报告

计算机组成原理的实验报告一、实验目的本次实验的主要目的是深入理解计算机组成原理中的关键概念和组件,通过实际操作和观察,增强对计算机硬件系统的认识和掌握能力。

具体包括:1、了解计算机内部各部件的工作原理和相互关系。

2、熟悉计算机指令的执行流程和数据的传输方式。

3、掌握计算机存储系统的组织和管理方法。

4、培养分析和解决计算机硬件相关问题的能力。

二、实验设备本次实验使用的设备包括计算机、逻辑分析仪、示波器以及相关的实验软件和工具。

三、实验内容1、运算器实验进行了简单的算术运算和逻辑运算,如加法、减法、与、或等操作。

观察运算结果在寄存器中的存储和变化情况。

2、控制器实验模拟了指令的取指、译码和执行过程。

分析不同指令对计算机状态的影响。

3、存储系统实验研究了内存的读写操作和地址映射方式。

考察了缓存的工作原理和命中率的计算。

4、总线实验观察数据在总线上的传输过程和时序。

分析总线竞争和仲裁的机制。

四、实验步骤1、运算器实验步骤连接实验设备,将运算器模块与计算机主机相连。

打开实验软件,设置运算类型和操作数。

启动运算,通过逻辑分析仪观察运算过程中的信号变化。

记录运算结果,并与预期结果进行比较。

2、控制器实验步骤连接控制器模块到计算机。

输入指令序列,使用示波器监测控制信号的产生和变化。

分析指令执行过程中各个阶段的状态转换。

3、存储系统实验步骤搭建存储系统实验电路。

进行内存读写操作,改变地址和数据,观察存储单元的内容变化。

分析缓存的替换策略和命中率的影响因素。

4、总线实验步骤连接总线模块,配置总线参数。

多个设备同时发送数据,观察总线的仲裁过程。

测量数据传输的时序和带宽。

五、实验结果与分析1、运算器实验结果加法、减法等运算结果准确,符合预期。

逻辑运算的结果也正确无误。

观察到在运算过程中,寄存器的值按照预定的规则进行更新。

分析:运算器的功能正常,能够准确执行各种运算操作,其内部的电路和逻辑设计合理。

2、控制器实验结果指令能够正确取指、译码和执行,控制信号的产生和时序符合指令的要求。

计算机组成原理实验报告三

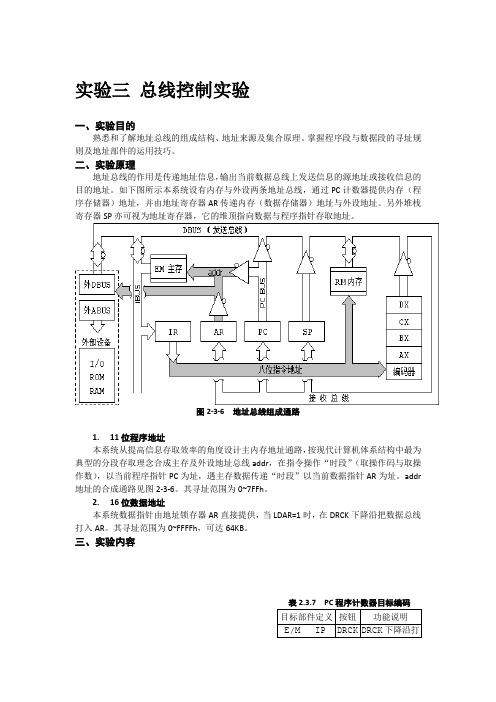

实验三总线控制实验一、实验目的熟悉和了解地址总线的组成结构、地址来源及集合原理。

掌握程序段与数据段的寻址规则及地址部件的运用技巧。

二、实验原理地址总线的作用是传递地址信息,输出当前数据总线上发送信息的源地址或接收信息的目的地址。

如下图所示本系统设有内存与外设两条地址总线,通过PC计数器提供内存(程序存储器)地址,并由地址寄存器AR传递内存(数据存储器)地址与外设地址。

另外堆栈寄存器SP亦可视为地址寄存器,它的堆顶指向数据与程序指针存取地址。

图2-3-6地址总线组成通路1.11位程序地址本系统从提高信息存取效率的角度设计主内存地址通路,按现代计算机体系结构中最为典型的分段存取理念合成主存及外设地址总线addr,在指令操作“时段”(取操作码与取操作数),以当前程序指针PC为址,遇主存数据传递“时段”以当前数据指针AR为址。

addr 地址的合成通路见图2-3-6。

其寻址范围为0~7FFh。

2.16位数据地址本系统数据指针由地址锁存器AR直接提供,当LDAR=1时,在DRCK下降沿把数据总线打入AR。

其寻址范围为0~FFFFh,可达64KB。

三、实验内容表2.3.7PC程序计数器目标编码目标部件定义按钮功能说明E/M IP DRCK DRCK下降沿打图2-3-7所示的PC框由3片161构成按字方式寻址的11位PC计数器,计数器的输入端与总线相连构成置数通路,计数器的输出端途经三态门缓冲分离为两条通路,其一与总线相连构成可读通路,其二与地址寄存器(数据)集合组成主存EM地址总线。

它的清零端由中央外理器单元直控,上电时PC计数器自动淸零,实验中按复位钮亦可实现计数器的手动淸零。

手控状态,本实验由表2.6.1定义的目的编码控制PC计数器的预置与加1操作,并以准双向I/O部件的S10~S0为计数器预置源。

当IP=1时按单拍按钮,遇E/M=1在脉冲下降沿把S10~S0的内容装入PC计数器;遇E/M=0在脉冲下降沿PC计数器加1。

计算机组成原理学生实习报告

计算机组成原理学生实习报告第一篇:计算机组成原理学生实习报告温岭市职业技术学校学生实习(实验)报告班级学号姓名指导教师实习时间实习课题: 计算机组装实习目的:熟悉计算机硬件组装硬件组装流程实习器材与设备:旧电脑数据线螺丝刀等实习过程:1.准备机箱2.安装主板上的部件3.将主板装入机箱4.连接机箱至主板的控制线5.实习小结:(写实习报告要求:1.有图纸的请附在报告反面2.写出具体过程包括编程、步骤)第二篇:计算机组成原理《计算机组成原理》实验任务计识。

算机原理是计算机科学与技术及相关专业的一门专业基础课,是一门重点科,在计算机硬件的各个领域中运会用到计算计原理的有关知本实验课程的教学目的和要求是使学生通过实验手段掌握计算机硬件的组成与设计、制造﹑调试﹑制造﹑维护等多方面的技能同时训练动手的能力,也使学生系统科学地受到分析问题和解决问题的训练. 第三篇:计算机组成原理上机实习报告总结经过这次课程设计我们了解了很多知识,也学到了一些课本中没有的知识点,实践给我们带来了很多快乐,但是在这快乐中我们有着艰辛,在我们接完线的时候,去运行机器总是出错,我们一步一步的检查,到最后一遍又一遍的重新连线,到最后终于成功了,心里有着一般人没有的喜悦。

计算机组成原理设计与实践实验课程不仅仅是对理论的验证,重要的是技术训练和能力培养,包括动手能力、分析问题和解决问题的能力、书写能力和表达能力、团队协作能力等的培养也就是要注重学生的工程能力,培养学生完成项目实践的能力,同时,要培养学生交流的能力,能够很好地表达自己的设计思想,这也是工程实践中必不可少的。

因此,在整个课程中,指导教师多次与学生交流设计方案,让学生在与老师的交流中逐渐理解处理器的工作原理。

同时,培养学生书写报告的能力,很多学生只注重编程序,而不重视课程报告的撰写,这需要老师的引导和成绩比例分配的导向,让学生真正理解报告不仅是写给老师看的,更重要的是真正通过报告的形式提交自己的设计思想。

计算机组成原理实验报告3 微程序控制器实验

实验三微程序控制器实验一.实验目得与要求:实验目得:1.理解时序产生器得原理,了解时钟与时序信号得波形;2.掌握微程序控制器得功能,组成知识;3.掌握微指令格式与各字段功能;4.掌握微程序得编制,写入,观察微程序得运行,学习基本指令得执行流程.实验要求:1.实验前,要求做好实验预习,并复习已经学过得控制信号得作用;2.按练习一要求完成测量波形得操作,画出TS1,TS2,TS3,TS4得波形,并测出所用得脉冲Ф周期。

按练习二得要求输入微指令得二进制代码表,并单步运行五条机器指令. 二.实验方案:按实验图在实验仪上接好线后,仔细检查无误后可接通电源.1.练习一:用联机软件得逻辑示波器观测时序信号,测量Ф,TS1,TS2,TS3,TS4信号得方法如下:(1)TATEUNIT 中STOP开关置为“RUN”状态(向上拨),STEP开关置为“EX EC”状态(向上拨)。

(2) 将SWITCH UNIT中右下角CLR开关置为“1”(向上拨)。

(3)按动“START"按钮,即可产生连续脉冲。

(4)调试"菜单下得“显示逻辑示波器窗口,即可出现测量波形得画面。

(5)探头一端接实验仪左上角得CH1,另一端接STATE UNIT中得Ф插座,即可测出时钟Ф得波形。

(6)探头一端接实验仪左上角得CH2,另一端接STATE UNIT中得TS1插座,即可测出TS1得波形;(7)探头一端接实验仪左上角得CH1,另一端接STA TE UNIT中得TS2插座,即可测出TS2得波形.(8)将红色探头一端接实验仪左上角得CH1,另一端接STATE UNIT中得TS3插座,即可测出TS3得波形。

(9)将红色探头一端接实验仪左上角得CH1,另一端接STATE UNIT中得TS4插座,即可测出TS4得波形。

2.观察微程序控制器得工作原理:①关掉实验仪电源,拔掉前面测时序信号得接线;②编程写入E2PROM 2816A.将编程开关(MJ20)置为PROM(编程)状态;B.将实验板上STA TE UNIT 中得STEP置为STEP状态,STOP置为RUN状态,SWITCHUNIT中CLR开关置为1状态;C.在右上角得SWITCHUNIT中UA5—UA0开关上置表3、2中某个要写得微地址;D.在MK24-MK1开关上置表3、2中要写得微地址后面得24位微代码,24位开关对应24位显示灯,开关置为1时灯亮,为0时灯灭;E.启动时序电路,即将微代码写入到E2PROM 2816得相应地址对应得单元中;F.重复C—E步骤,将表3、2得每一行写入E2PROM 2816。

(完整word版)计算机组成原理实验报告_微控制器

计算机组成原理实验报告题目:微程序控制器实验一、实验目的:(1)理解时序产生器的原理,了解时钟和时序信号的波形。

(2)掌握微程序控制器的功能、组成知识。

(3)掌握微指令格式和各字段功能。

(4)掌握微指令的编制、写入、观察微程序的运行二、实验设备PC机一台,TD—CM3+实验系统一套。

三、实验内容及要求:(一)实验原理:微程序控制电路与微指令格式(A)微程序控制电路微程序控制器的组成见图10,其中控制存储器采用3片2816的E2PROM,具有掉电保护功能,微命令寄存器18位,用两片8D触发器(74273)和一片4D(74175)触发器组成.微地址寄存器6位,用三片正沿触发的双D触发器(7474)组成,它们带有清“0”端和预置端。

在不判别测试的情况下,T2时刻打入微地址寄存器的内容即为下一条微指令地址。

当T4时刻进行测试判别时,转移逻辑满足条件后输出的负脉冲通过强置端将某一触发器置为“1”状态,完成地址修改。

在该实验电路中设有一个编程开关(位于实验板右上方),它具有三种状态:PROM (编程)、READ(校验)、RUN(运行)。

当处于“编程状态”时,实验者可根据微地址和微指令格式将微指令二进制代码写入到控制存储器2816中。

当处于“校验状态”时,可以对写入控制存储器中的二进制代码进行验证,从而可以判断写入的二进制代码是否正确。

当处于“运行状态”时,只要给出微程序的入口微地址,则可根据微程序流程图自动执行微程序。

图中微地址寄存器输出端增加了一组三态门,目的是隔离触发器的输出,增加抗干扰能力,并用来驱动微地址显示灯。

微程序控制器原理图图10(B) 微指令格式微指令字长共24位,其控制位顺序如图所示。

图11 微指令格式A字段B字段C字MA5—-MA0为A,B,C为三个译码字段,分别由三个C字段中的P(1)是测试字位。

,从而实现微程序的顺序、分支、循环运。

图中I7一I2为指令寄存器的第7-—2位输出,SE5—SE0为微程序控制器单元微地址锁存器的强置端输出.(C)二进制代码表二进制微代码表将全部微程序按照指令格式变成二进制微代码可得上表(二)实验内容1.按照实验接线图连接好实验线路,并且检查线路,确保无误。

计算机组成原理实验报告3

计算机组成原理实验报告3上海⼤学计算机组成原理实验报告三姓名:学号:座位号:上课时间:教师:报告成绩:⼀.实验⽬的1. 读出系统已有的微指令,并理解其含义。

2. 设计并实现微指令系统。

⼆.实验原理1.微指令构造①译码器:前两次实验的每⼀项操作都是通过⼈⼯设置电键ki的位置——Ki编码,然后给出⼀个CK脉冲来完成。

如果有⼀个器件能给出对应与每个操作的ki编码,这个器件就可以代替我们来为操作译码——产⽣控制信号,这个器件就是指令译码器,也叫控制器。

常见的控制器有两种:⽤组合逻辑电路实现控制信号的逻辑电路结构和⽤存储器实现控制信号的微程序结构。

前者将在《在系统编程技术及应⽤》课程中学习。

这⾥学习后者。

②微指令:把⼀个操作的控制总线编码放在⼀个存储单元中,同时给出调⽤这个单元的⽅法(例如:这个单元的地址),则对使⽤者⽽⾔,这个调⽤⽅法等价于控制总线编码本⾝,⼆者都称为微指令(不同场合具体指向不同或没有区别)。

对于操作:“ACH送⼊寄存器A”有ki编码:1111 11110,假定将其存⼊⼀个地址为F3H的随意选取的存储器单元中,且可以⽤“读F3”的⽅式取出这个内容并送上控制总线,则“读F3”和1111 11110是这个操作的微指令,这两个表达形式等价。

③操作序列的形式化表述:同理:把操作“BDH送⼊寄存器W”的ki编码1111 11101存⼊随意选取的FDH地址单元;操作“A-W”的ki编码1111 00111存⼊随意选取的B2H地址单元;操作“直通门D的内容送OUT寄存器”的编码0100 111111存⼊DCH地址单元。

④实验箱的微指令系统:制造⼚的⼯程师根据这个实验箱的功能、部件数量、必须的基本操作等要求,给它安排了24条控制线——控制总线宽度为24。

相应地,每条微指令有24位、微程序存储器的每个地址也必须是24位的存储单元。

于是⼚家把3⽚8位存储器的对应地址并接在⼀起,构成⼀个24位的存储器。

具体连接见下图1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、实验课题:

(1)主要元件设计 1.程序计数器

功能要求:8位二进制计数器,同步并行置数,同步复位(清零), 三态输出。

提示:注意程序计数器的“自动加一”功能。 2.数据寄存器 功能要求:8位,同步并行置数,双向三态输出。 3.地址寄存器 功能要求:8位,同步并行置数,三态输出。 4.指令寄存器 功能要求:8位,同步并行置数。 5.指令译码器 功能要求:3-8译码器。 (2)仿真 设计仿真波形数据,要考虑到所有可能的情况。在实验报告中必须清 楚说明仿真波形数据是怎样设计的。

load ,z ,clk : in std_logic; d : in std_logic_vector(7 downto 0); q : out std_logic_vector(7 downto 0) ); end address_register;

architecture behave of address_register is signal iq : std_logic_vector(7 downto 0); begin

architecture behave of instruction_register is signal save : std_logic_vector(7 downto 0); begin

process(clk , load) begin if rising_edge(clk) and load='1' then

D7 D6 D5 D2 D4 D3 D1 D0 Load clk

指令译码器 8位指令寄存器

端口说明: clk:时钟信号 load:同步置数端口 d:输入端口 q:输入端口

5、指令译码器的设计: 指令译码器系统框图

Y0 Y1 Y2 Y4 Y7

Y6 Y5 Y3 A2 A1 A0

端口说明: A:指令码输入端,高电平有效 Y:指令码译码后的输出端。低电平有效。

入的数据,三态,上一次计数时的输出数据。 8位数据寄存器仿真设计:

数据寄存器的仿真设计的要点在于验证: 1、 能否从q、d端口分别读入数据,能否在三态门打开时正确输出寄 存器中的数据。 2、 三态门是否有效。

仿真数据: 1、 在clk上升是从d端口置入数据11111111,同时l同步置数端loadd 打开,loadq=0,zd=0,zq=0. 2、 下一个时钟上升沿:loadq=0,loadd=0,zd=0,zq=1. 3、 下一个时钟上升沿:loadq=0,loadd=0,zd=1,zq=0 4、 下一个时钟上升沿,从q端口置入数据11110000,通知同步置数端 loadq打开,loadd=0,zd=0,zq=0 5、 下一个时钟上升沿:loadd=0,loadq=0,zd=1,zq=1. 6、 下一个时钟上升沿:loadq=1,loadd=0,zd=1,z1=0(用于验证一端 输入一端输出发生的情况) 7、 下一个时钟上升沿:zd=1,z1=1,loadd=0,loadq=0

end if; if loadq = '1' and zq = '0' then

iq<=q; q<=(others=>'Z'); end if; end if; if zd = '0' then --三态门关闭

d<=(others=>'Z'); else d<=iq; end if; if zq = '0' then--三态门关闭

8位指令寄存器: library ieee; use ieee.std_logic_1164.all;

entity instruction_register is port (

clk ,load : in std_logic; d : in std_logic_vector(7 downto 0); q : out std_logic_vector(7 downto 0) ); end instruction_register;

q<=(others=>'Z'); else q<=iq; end if; end process; end behave ;

8位地址寄存器 --address_register

library ieee; use ieee.std_logic_1164.all;

entity address_register is port ( --load同步并行置数 --z三态输出 z=1 is valide signal --d输入 --q输出

c<='Z'; q<=(others=>'Z'); end if; end process; end behave;

8位数据寄存器: --data register

library ieee; use ieee.std_logic_1164.all;

entity data_register is port ( --clk时钟信号 --zq控制q端口的三态 --zd控制d端口的三态 --load1,load2同步并行置数.loadd控制d,loadq控制q --d输入输出双向端口 --q输入输出端口

青岛理工大学

实验报告

实验课程: 计算机组成原理I

实验日期: 2013 年 11月3日, 交报告日期:2013 年11月22 日,成绩: 实验地点:现代教育技术中心101(计算机实验室) 计算机工程 学院,计算机科学与技术 专业, 班级:计算112

实验指导教师: 刘淑霞

批阅教师:

同组 姓 学生 名

学 号

architecture de_behave of decode is signal s: std_logic; begin

process(A) begin

case A is when "000"=> Y<="11111110"; when "001"=> Y<="11111101"; when "010"=> Y<="11111011"; when "011"=> Y<="11110111"; when "100"=> Y<="11101111"; when "101"=> Y<="11011111"; when "110"=> Y<="10111111"; when "111"=> Y<="01111111"; end case; end process; end de_behave;

8位地址寄存器的仿真设计:

地址寄存器的仿真设计要点在于验证: 1、 同步置数功能是否有效 2、 三态输出是否有效。

仿真数据: 1、 时钟上升沿d=11111111,load=1,z=0 2、 下一个时钟上升沿:load=0,d=00000001,z=0 3、 下一个时钟上升沿:load=1,d=00000010,z=0 4、 下一个时钟上升沿:load=1,d=00000011,z=1

save<=d; end if; q<=save; end process; end behave; 指令译码器(3-8译码器): --Decode library ieee; use ieee.std_logic_1164.all; entity decode is

port (

A : in std_logic_vector(2 downto 0);--输入 Y : out std_logic_vector(7 downto 0)--输出 ); end decode;

二、逻辑设计:

1、程序计数器的设计 8位程序计数器系统框图

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 c

Z

r ld et clk D7 D6 D5 D3 D2 D1 D4 D0

8位程序计数器

端口说明: et:控制程序计数器自动加一的控制端 ld:预置数控制端 r:同步清零端 clk:时钟信号 z:三态控制端口 c:进位输出端口 q:输出端口 d:预置数端口。

四、仿真设计:

8位程序计数器仿真设计: 程序计数器的仿真设计的要点在于验证:

1、 程序在加1控制端有效的时候是否具有自动加1的功能。 2、 r同步置数端口的有效性。 3、 ld预置数端口的有效性。 4、 z三态端口的有效性。 5、 控制加1端口et的有效性。

令数据从00000000开始计数,观察数据是否是相邻数据相差1位,同时 在加1的过程中间插入r=0,ld=0,z=1,et=0信号,已验证其功能是否实 现,如果这些功能实现了,则相应的输出端,分别会显示出0000000,置

et,clk,z,ld,r :in std_logic; c : out std_logic; d : in unsigned(7 downto 0); q : out unsigned(7 downto 0) ); end eight_count; architecture behave of eight_count is signal iq : unsigned(7 downto 0); begin process (clk,et,z,ld,r) begin

process(clk,zd,zq,loadd,loadq) begin

if rising_edge(clk) then if loadd = '1' and zd = '0' then--因为d是双向端口,当d作为输入端

口时, --d作为输出端口时应该是高阻态,否则会产生