计算机等级考试四级计算机组成与接口

计算机等级考试四级复习资料

TCP/IP联网主要内容:1、TCP/IP实现的基本原理2、Windows NT平台的联网3、UNIX平台的联网及LINUX网络的联网一、TCP/IP实现基本原理1、TCP/IP的实现方式:TSR常驻内存程序是一种安装在Windows之前在DOS上运行的程序。

缺点,不能动态分配内存,TSR需要动态链接库DLL帮助,才能让Windows程序访问网络。

目前只有在DOS 环境下才使用TSR方式。

DLL动态链接库是一个16位的Windows程序函数库,只有当用到其中的过程时才会被调用。

缺点,它们不能直接与网卡通信,它们依赖于Windows的调度程序。

VxD虚拟设备是在Windows 32位保护方式下实现的,用于实现一些关键的部分,如视频、鼠标及通信端口驱动程序。

它是通过硬件中断方式响应网络中的通信,可以彻底地访问Windwos和DOS程序。

2、网络配置基本参数:PC中网络适配卡基本参数,I/O端口地址、内存地址及中断号IRQ。

与Microsoft相关的网络信息,主机标识、工作组名、WINS服务器地址、DHCP服务器地址;与TCP/IP网络信息有关,IP地址、子网掩码、主机名、域名、域名服务器、默认网关IP地址。

二、Windows NT平台的TCP/IP联网三、UNIX平台的TCP/IP联网1、建立UNIX联网的几个步骤:设计物理和逻辑的网络结构;分配IP地址;安装网络硬件;为每个主机配置启动时候的网络接口;设立服务程序或者静态路由。

2、IP地址的获取和分配:可能通过/etc/hosts文件、DNS或者其他域名系统来实现。

3、网卡的配置:ifconfig命令可以设置网卡IP地址、子网掩码、广播地址、网卡的使能状态及其他选项参数。

Ifconfig interface [family] address up option ,其中interface是指定的网卡名,可以用netstat-i来检查当前系统网卡的芯片类型。

计算机等级考试四级

计算机等级考试四级

计算机四级指的是全国计算机等级考试的最高级别,科目种类有:四级操作系统原理、四级计算机组成与接口、四级数据库原理、四级软件工程、四级计算机网络。

考试从科目中任意选取两个科目进行考试,同时通过成绩方为合格。

考试时间为90分钟。

计算机四级与国际MBA同等级。

四级知识量是巨大的(看看那厚厚的教材就知道了),难点主要是离散数学和计算机英语。

笔试中有论述题。

计算机等级整数分四级,四级的最高。

一级:考核计算机基础知识及计算机基本操作能力,包括Office办公软件、图形图像软件。

二级:程序设计/办公软件高级应用级。

三级:分为“软件测试技术”、“信息安考核微型计算机基础知识和使用办公软件及因特网(Internet)的基本技能。

四级:分为“网络工程师”、“数据库工程师”和“软件测试工程师”、“信息安全工程师”、“嵌入式系统开发工程师”这几个类别。

扩展资料

计算机四级是针对计算机的熟练以及掌握程度进行评估的一种国家型等级考试。

考试为无纸化考试,不含操作题。

证书由教育部考试中心签发,本证书分别用中文、英文书写,可利于国际交流。

计算机四级是等级考试的最高级别。

之前的级别还有计算机一级、计算机二级、计算机三级。

全国计算机等级考试四级计算机组成与接口考试大纲(2022年版)

全国计算机等级考试4级计算机组成与接口考试大纲(2018年版) 基本要求 1.理解微型计算机结构。

2.掌握微型计算机各部件的工作原理及相互之间的关系。

3.掌握微型计算机设计的基本方法。

4.掌握接口芯片应用的程序设计技术。

考试内容1.计算机系统概述1.计算机的基本组成。

冯·诺依曼结构计算机和哈佛结构计算机的特点。

2.计算机主要性能指标。

3.CPU的基本结构和工作机理。

指令流水线技术和8086CPU的编程结构立即序。

4.数据的表示和运算。

数制与编码.定点数和浮点数的表示和运算。

5.指令格式。

指令的寻址方式.指令周期.机器周期和时钟周期。

2.存储器1.存储器的分类.存储器的层次结构.高速存储技术.虚拟存储技术。

2.映射技术.替换策略.Pentium微处理器的存储管理。

3.随机存取存储器RAM.只读存储器ROM。

4.存储器与CPU的连接方法。

5.辅助存储器。

硬磁盘存储器和光盘存储器的基本原理。

3.汇编语言程序设计1.8086汇编指令系统。

2.程序设计技术。

4.计算机中断技术1.中断基本概念.中断类型码.中断向量和中断服务程序。

2.中断接口控制器8259A的程序设计方法。

15.计算机和外设的数据交换技术1.CPU和外设之间的数据传送方式。

2.可编程串行通信接口8251A的程序设计方法。

3.可编程并行通信接口8255A的程序设计方法。

4.计数器/定时器8253的程序设计方法。

6.模/数.数/模转换技术1.模/数转换技术。

2.数/模转换技术。

7.人机接口1.鼠标及键盘的工作原理。

2.数字显示技术。

3.打印机及接口。

8.总线1.总线的概念和功能。

2.流行PC总线。

ISA总线.PCI总线和USB通用串行总线。

考试方式 上机考试,总分50分,考试时长90分钟。

包含:单选题30分,多选题20分。

2。

全国计算机等级考试四级试题精练及答案

全国计算机等级考试四级试题精练及答案

全国计算机等级考试四级试题精练及答案

全国计算机等级考试四级考试的科目种类有:四级操作系统原理、四级计算机组成与接口、四级数据库原理、四级软件工程、四级计算机网络。

以下是为大家分享的全国计算机等级考试四级试题精练及答案,供大家参考借鉴,欢迎浏览!

题目:

已知寄存器A存有带符号整数且只作算术移位, HA和LA分别代表其最高位和最低位。

寄存器B存有带符号整数且只作逻辑移位, HB 和LB分别代表其最高位和最低位。

当寄存器A与B都有左移位发生时, 下述哪一个命题是正确的?

和LB均成为0

与LB均成为1

变为0, 但LB保持原值

保持原值, 但LB的.值改变

参考答案:A

本题评析:

算术移位时,符号位(最高位)保持不变;而逻辑移位时,空出的位简单补0。

所以当有左移位发生时,不管是算术左移还是逻辑左移,其最低位总是0;当然,我们还知道的是:算术左移的最高位(符号位)保持不变。

所以本题答案为A。

题面:

下述哪一种情况称为指令周期?

A.取指令时间

B.取操作数时间

C.取指令和执行指令的时间

D.存储操作结果的时间

参考答案:C

本题评析:

指令周期包括读取指令和执行指令两个时期。

取操作数时间和存储操作结果的时间不属于指令周期。

【全国计算机等级考试四级试题精练及答案】。

计算机等级考试四级 计算机组成与接口

欢迎共阅计算机组成与接口冯诺依曼P1标志寄存器P16Pentium微处理器模式P498086复位P36全相联直接相连映像组相联映像技术P598259A中断控制器P1238251A串行通讯P1498255A并行通讯P1598253ADC0809USBA/Dtest flags 同理判断AX和假定80868086系统中,单步中断的中断向量在中断向量表中的位置固定在00004H开始的4个字节中8086CPU构成的微机系统中,中断向量表00084H单元开始依次存放有12H,33H,56H,90H,则该中断服务程序的入口地址是93872H8086CPU构成的微机系统中,中断优先权顺序由高到低的顺序是溢出中断,单步中断NMI,断点中断,INTR中断,intN8086微机系统中内部中断中断类型码由指令给定中断类型码是约定的8086微机系统中断硬件中断分为非屏蔽中断和可屏蔽中断可屏蔽中断需要执行2个中断响应总线周期溢出中断向量的地址是固定的8086微机系统中,NMI中断的中断向量位置固定在00008H开始的4个单元中可提供X86汇编指令操作数的是存储器寄存器不可以的是控制器I/O端口I/O设备由寄存器SS提供堆栈段的段基址,为堆栈段提供偏移地址的寄存器是SP另DS+SIES+DICS+IPDS+DI当8086CPU处于单步工作方式时,标志寄存器中必须为1的标志位是TFP178086CPU工作在最大工作模式下,产生ALE、DEN、INTA等控制信号的芯片是8288P38假设8086CPU的主频为5MHz,内存芯片的存取时间为250ns,读/写内存时不需要加入等待周期Tw8086系统中,已知中断类型码为16H,则其中断服务程序的入口地址存放在内存地址0000H∶0058H~0000H∶005BH8086CPU构成的微机系统中,在执行INTn指令或者响应硬件中断时,CPU保护现场的顺序依次是CS,IP,FR8086CPU中断响应和处理过程8086CPU执行完一条指令后对中断进行判断响应中断时,首先保护标志808680868086CPU若RD 为低8086CPU HLDA 的状态是8086X868086CPU82868086CPU存储体分为奇/8086对属于8086CPU当8086CPU8086的范围PentiumPentiumPentium处理器中,由CALL指令,中断或异常引起子程序被调用时,标志寄存器的嵌套标志位的值是NT=1Pentium微处理器配备了5个控制寄存器,其中未定义的控制寄存器是CR1Pentium微处理器的5个控制寄存器中,负责控制处理器工作模式的寄存器是CR0pentium微处理器中,程序员不能直接读写的32位寄存器是TRPentium微处理器的数据总线宽度是64位Pentium微处理器的结构被称为超标量结构的原因是Pentium微处理器内部含有多条指令流水线和多个执行部件Pentium微处理器的特点是内部集成了增强型浮点处理部件FPU设置了互相独立的片内代码cache和数据cache.采用分段和分页两级存储管理机制,并且允许页面大小可调采用了U、V二条流水线Pentium微处理器可访问的物理存储器的范围A)4GBPentium微处理器的分页存储管理系统可以把页的大小定义成4MBPentium的虚拟存储机制下A)虚拟存储器对应的地址也叫逻辑地B)虚拟存储器比主存储器容量大Pentium微处理器中,若当前工作在虚拟8086方式下,则标志寄存器的标志位设置正确的是B)VM=0Pentium存储管理由分段部件和分页部件协同完成分段部件将逻辑地址转换为线性地址分页部件将线性地址转换为物理地址段描述符为处理器提供段的访问控制及状态信息采用描述表结构进行管理PentiumPentiumPentiumPentium当PentiumPentiumPentiumPentiumPentium页表信息PentiumPentium12位8反码取反为已知[X]若浮点数异机器数,符号位也数值化了的数叫机器数原码格式表示的数是机器数补码格式表示的数是机器数CPU对存储器或I/O端口完成一次读/写操作所需的时间称为一个存储周期一个完整的指令周期应包括取指周期和执行周期闪速存储器(FlashMemory)主要特点是既可在不加电的情况下长期保存信息,又能在线进行快速擦除与重写虚拟存储器虚拟存储器将主存和辅存地址空间统一编址虚拟存储器的大小受辅助存储器容量的限制使主存的空间得到了扩充存储器与CPU之间连接时,应考虑的是合理分配内存地址空间存储芯片片选线的连接CPU内部总线的宽度DRAM芯片通常采用电容保存信息,常用刷新方式有集中式刷新分布式刷新异步式刷新)DRAM是一种随机存储器DRAM是一种易失性存储器,断电则丢失存储信息DRAM需要刷新操作,不定时刷新,数据会丢失DRAM是一种半导体存储器存储器映象编址,也称为统一编址,其特点是无专用的I/O指令Cache中存放的是主存储器中一部分信息的映像硬磁盘存储器的主要性能指标有A.存储密度B.存储容量C.转速D.平均存取时间E.数据传输率温切斯特磁盘主要特点是采用密封组合方式,将磁头、盘片、驱动部件以及读/写电路等组装成一个不能随意拆卸的整体8086CPU8086CPU在8086CPU为使8259A8259A8259A8259A主片和8259A若芯片范围是8259A方式8259A在级固定按8259A下列关于A.SRAM是一种随机存储器B.SRAM是一种易失性存储器,断电则丢失存储信息C.SRAM需要刷新操作,不定时刷新,数据会丢失D.SRAM速度快,通常用来制作高速缓存E.SRAM芯片与CPU连接时要注意时序匹配下列关于DRAM的叙述,正确的是ABCDA.DRAM是一种随机存储器B.DRAM是一种易失性存储器,断电则丢失存储信息C.DRAM需要刷新操作,不定时刷新,数据会丢失D.DRAM是一种半导体存储器E.DRAM芯片与CPU连接时要注意时序匹配存储器与CPU之间的连接时,下列各项中应考虑的是CDEA.数据线的连接B.CPU的时序应与存储器的存取速度相互配合C.合理分配内存地址空间D.存储芯片片选线的连接E.CPU内部总线的宽度内存需求量大,通常选用DRAM高速缓存要求速度快,通常选用SRAMEPROM可擦除可编程的只读存储器。

全国计算机等级考试四级网络工程师操作系统原理部分

操作系统原理第一章操作系统概论1.1操作系统的概念操作系统的特征:并发性,共享性,随机性。

研究操作系统的观点:软件的观点,资源管理的观点,进程的观点,虚拟机的观点,服务提供者的观点。

操作系统的功能:1.进程管理:进程控制,进程同步,进程间通信,调度。

2.存储管理:内存分配与回收,存储保护,内存扩充。

3.文件管理:文件存储空间管理,目录管理,文件系统安全性。

4.设备管理5.用户接口UNIX是一个良好的、通用的、多用户、多任务、分时操作系统。

1969年AT&T公司Kenneth L.Thompson 用汇编语言编写了Unix第一个版本V1,之后Unix用C语言编写,因此事可移植的。

1.3操作系统分类1.批处理操作系统:优点是作业流程自动化较高,资源利用率较高,作业吞吐量大,从而提高了整个系统的效率。

缺点是用户不能直接与计算机交互,不适合调试程序。

2.分时系统:特点是多路性,交互性,独占性,及时性。

3.实时操作系统4.嵌入式操作系统5.个人计算机操作系统6.网络操作系统7.分布式操作系统8.智能卡操作系统1.4操作系统结构1.整体式结构2.层次结构3.微内核(客户机/服务器)结构:①可靠,②灵活(便于操作系统增加新的服务功能),③适宜分布式处理的计算机环境第二章操作系统运行机制2.1中央处理器寄存器:用户可见寄存器:数据寄存器(通用寄存器),地址寄存器,条件码寄存器。

控制和状态寄存器:程序计数器,指令寄存器,程序状态字。

目态到管态的转换唯一途径是通过终端和异常。

管态到目态的转换可以通过设置PSW指令(修改程序状态字)实现。

PSW包括:①CPU的工作状态代码②条件码③中断屏蔽码2.2存储体系存储器设计:容量,速度,成本存储保护:①界地址寄存器(界限寄存器):产生程序中断-越界中断或存储保护中断②存储键2.3中断与异常机制分类:中断:时钟中断,输入输出(I/O)中断,控制台中断,硬件故障中断异常:程序性中断,访管指令异常2.4系统调用系统调用程序被看成是一个低级的过程,只能由汇编语言直接访问。

2024年全国计算机等级考试四级大纲

2024年全国计算机等级考试四级大纲全国计算机等级考试(National Computer Rank Examination,简称NCRE)是经原国家教育委员会(现教育部)批准,由教育部考试中心主办,面向社会,用于考查应试人员计算机应用知识与技能的全国性计算机水平考试体系。

其中,四级是 NCRE 考试的最高级别,对考生的计算机专业知识和综合应用能力有较高的要求。

以下是 2024 年全国计算机等级考试四级大纲的详细内容。

一、考试科目2024 年全国计算机等级考试四级共设五个科目:1、数据库工程师2、信息安全工程师3、嵌入式系统开发工程师4、移动互联网应用开发工程师5、云计算工程师考生可以根据自己的兴趣和专业背景选择其中一个科目报考。

二、考试形式四级考试采用无纸化考试形式,考试时长为 90 分钟。

三、考试内容(一)数据库工程师1、数据库应用系统分析及规划(1)掌握系统需求分析和规划的方法,能够进行数据库应用系统的需求分析和规划。

(2)了解数据库应用系统的设计流程和方法,能够进行数据库应用系统的总体设计。

2、数据库设计及实现(1)熟练掌握数据库设计的方法和技术,能够进行数据库的概念设计、逻辑设计和物理设计。

(2)掌握数据库实现的技术,包括数据库的创建、数据加载、存储过程和触发器的编写等。

3、数据库存储技术(1)了解数据库存储结构和存储方式,能够进行数据库存储的优化。

(2)掌握数据库备份和恢复的技术,能够制定合理的备份和恢复策略。

4、数据库运行与管理(1)掌握数据库性能优化的方法和技术,能够对数据库进行性能调优。

(2)熟悉数据库的安全管理机制,能够进行数据库的用户管理、权限管理和安全审计。

5、数据库新技术(1)了解数据库领域的新技术和发展趋势,如大数据、数据仓库、NoSQL 数据库等。

(2)能够将新技术应用到数据库应用系统的设计和开发中。

(二)信息安全工程师1、信息安全基础(1)了解信息安全的基本概念、原理和技术,包括密码学、网络安全、操作系统安全等。

全国计算机四级机试试题及答案

最新全国计算机四级机试试题及答案最新全国计算机四级机试试题及答案计算机四级指的是全国计算机等级考试的最高级别,科目种类有:四级操作系统原理、四级计算机组成与接口、四级数据库原理、四级软件工程、四级计算机网络。

为帮助考生们更好通过考试,特地为大家准备了以下四级模拟考试题,!1./* 请编写一个函数changeStr(char *s),函数的功能是把s串中所有的字母改写成该字母的下一个字母,字母z改写成字母a。

大写仍为大写字母,小写字母仍为小写字母,其它的字符不变。

函数ReadWrite实现从文件in2.dat中读取两个字符串,并调用函数changestr,最后把结果输出到文件out2.dat中。

注意:局部程序存在文件PROG1.C中。

请勿改动主函数main和其它函数中的任何内容,仅在函数changeStr的花括号中填入你编写的假设干语名。

*/#include#include#include#include#define N 81changeStr ( char *s ){}main( ){char a[N] ;clrscr( ) ;printf ( “Enter a stri ng :” ) ; gets ( a ) ;printf ( “The original string is :” ) ; puts( a ) ;changeStr ( a ) ;printf ( “The string after modified :”) ;puts ( a ) ;ReadWrite( ) ;}ReadWrite( ){int i ;char a[N] ;FILE *rf, *wf ;rf = fopen(“in2.dat”,“r”) ;wf = fop en(“out2.dat”,“w”) ;for(i = 0 ; i 《 10 ; i++) {fscanf(rf,“%s”, a) ;changeStr(a) ;fprintf(wf,“%s ”, a) ;}fclose(rf) ;fclose(wf) ;}2./* 程序PROG1.C的功能是:利用以下所示的简单迭代方法求方程:cos(x)-x=0的一个实根2023最新全国计算机四级机试试题及答案2023最新全国计算机四级机试试题及答案。

全国计算机等级考试

实施机构

教育部教育考试院标志教育部教育考试院负责实施考试,制定有关规章制度,编写考试大纲及相应的辅导材 料,命制试卷、答案及评分参考,进行成绩认定,颁发合格证书,研制考试必须的计算机软件,开展考试研究和 宣传等。

教育部教育考试院在各省(自治区、直辖市)设立省级承办机构,由省级承办机构负责本省(自治区、直辖 市)考试的宣传、推广和实施。

教育部教育考试院为已申请证书直邮的考生直接邮寄合格证书到考生指定地址(同时证书将不再发放到考 点)。合格证书将在直邮申请功能关闭后的15个工作日内使用邮政特快专递(EMS)进行邮寄,直邮费用统一为 20元(网上支付)。缴费成功后,不能取消直邮申请,也不能修改邮寄地址和联系**等信息。

考生证书若丢失,可登录中国教育考试网补办合格证明书。 补办合格证明书免费,合格证明书以特快专递 (EMS)方式寄出,邮寄费为20元。

NCRE网上报名流程

考生报名时须缴纳考试费,具体金额由各省级承办机构根据考试需要和当地物价水平确定,并报当地物价部 门核准。考点不得擅自加收费用。

1、NCRE报名一般不安排专门的补报。考生如果错过网上或报名点的报名时间,可以直接咨询当地考试院或 自考办报名。

2、同次考试,考生最多可报三个科目,但不允许重复报考同一个科目。禁止考生同时在多个省级承办机构报 名。

电子合格证书为PDF格式,带验证查询二维码,与纸质版证书具有同等效力,考生实名注册后可在中国教育 考试网的证书查询栏目查询、下载电子合格证书。

教育部教育考试院将在考后45个工作日内将纸质合格证书下发给省级承办机构,然后由各省级承办机构逐级 转发给考生。考生在成绩公布后,可登录中国教育考试网申请NCRE证书直邮服务。

NCRE二级合格证书样本

考核内容

计算机维修工四级题库

计算机维修工四级题库计算机维修工作是目前社会中一项非常重要的工作。

随着计算机的广泛应用,各种各样的问题出现在日常工作中。

因此,需要有专业技术人员来解决这些问题。

计算机维修工四级题库就是为了选拔合格的维修人员而设立的。

计算机维修工四级题库是一项涉及计算机硬件和软件方面的知识和技能的考试。

它涵盖了计算机的基本概念、组装与拆解、故障诊断与修复、操作系统和应用软件的安装与配置等方面。

下面将从这几个方面展开说明。

首先,计算机维修工四级题库会考察考生对计算机的基本概念的掌握。

比如,计算机的组成部分有哪些?CPU、内存、硬盘、显卡等等。

此外,考生还需要了解计算机硬件的工作原理,如什么是二进制、计算机是如何进行数据交换的等等。

其次,组装与拆解是计算机维修工十分重要的一项技能。

在组装计算机时,考生需要正确拆解各个硬件组件,连接好电源线,并将各个硬件组件安装到机箱内。

考生还需要了解各个硬件之间的连接方式,如CPU与主板的连接、内存条插槽的选择等。

故障诊断与修复是计算机维修工必备的技能之一。

计算机故障往往表现为无法正常启动、死机、蓝屏等问题。

考生需要通过故障现象,运用自己的专业知识,准确找到故障原因,并采取相应的修复措施。

故障诊断与修复涉及到硬件和软件方面的问题,考生需要懂得用一些专业的故障诊断工具来辅助诊断。

操作系统和应用软件的安装与配置是计算机维修工的日常工作之一。

操作系统是计算机的核心软件,负责管理和控制计算机的硬件资源。

考生需要了解不同操作系统的安装和配置方法,如Windows、Linux等。

另外,应用软件的安装和配置也是考生需要掌握的技能,如Microsoft Office、Adobe Photoshop等。

综上所述,计算机维修工四级题库是一项为选拔合格的维修人员而设立的考试。

它涵盖了计算机的基本概念、组装与拆解、故障诊断与修复、操作系统和应用软件的安装与配置等方面的知识和技能。

通过这项考试,能够评估考生的专业水平和综合能力。

计算机等级考试四级教程---操作系统原理

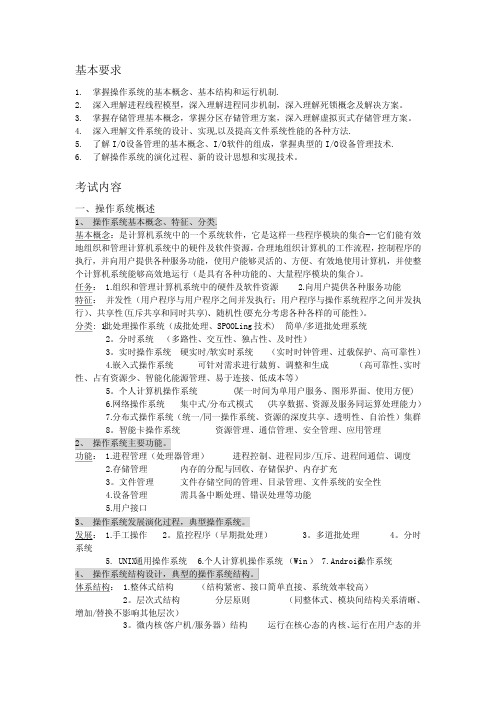

基本要求1.掌握操作系统的基本概念、基本结构和运行机制.2.深入理解进程线程模型,深入理解进程同步机制,深入理解死锁概念及解决方案。

3.掌握存储管理基本概念,掌握分区存储管理方案,深入理解虚拟页式存储管理方案。

4.深入理解文件系统的设计、实现,以及提高文件系统性能的各种方法.5.了解I/O设备管理的基本概念、I/O软件的组成,掌握典型的I/O设备管理技术.6.了解操作系统的演化过程、新的设计思想和实现技术。

考试内容一、操作系统概述1、 操作系统基本概念、特征、分类.基本概念:是计算机系统中的一个系统软件,它是这样一些程序模块的集合-—它们能有效地组织和管理计算机系统中的硬件及软件资源,合理地组织计算机的工作流程,控制程序的执行,并向用户提供各种服务功能,使用户能够灵活的、方便、有效地使用计算机,并使整个计算机系统能够高效地运行(是具有各种功能的、大量程序模块的集合)。

任务: 1.组织和管理计算机系统中的硬件及软件资源 2.向用户提供各种服务功能特征: 并发性(用户程序与用户程序之间并发执行;用户程序与操作系统程序之间并发执行)、共享性(互斥共享和同时共享)、随机性(要充分考虑各种各样的可能性)。

分类: 1.批处理操作系统(成批处理、SPOOLing技术) 简单/多道批处理系统 2。

分时系统 (多路性、交互性、独占性、及时性)3。

实时操作系统 硬实时/软实时系统 (实时时钟管理、过载保护、高可靠性)4.嵌入式操作系统 可针对需求进行裁剪、调整和生成 (高可靠性、实时性、占有资源少、智能化能源管理、易于连接、低成本等)5。

个人计算机操作系统 (某一时间为单用户服务、图形界面、使用方便)6.网络操作系统 集中式/分布式模式 (共享数据、资源及服务同运算处理能力)7.分布式操作系统(统一/同一操作系统、资源的深度共享、透明性、自治性)集群8。

智能卡操作系统 资源管理、通信管理、安全管理、应用管理2、 操作系统主要功能。

计算机组成与接口 四级

计算机组成与接口四级

计算机组成与接口技术是计算机科学与技术专业的一门核心课程,通常分为四级。

计算机组成部分包括中央处理器(CPU)、内存、输入设备、输出设备和存储设备等。

中央处理器是计算机的核心,负责执行指令和处理数据;内存用于存储程序和数据;输入设备用于将数据和指令输入计算机;输出设备用于将计算机处理的结果输出;存储设备用于长期存储数据和程序。

接口技术是指计算机系统中各个组成部分之间的连接和通信方式。

它包括硬件接口和软件接口。

硬件接口包括各种外部设备与计算机之间的接口,如 USB、以太网、串口等;软件接口包括操作系统、应用程序和设备驱动程序之间的接口。

在计算机组成与接口技术四级中,学生将深入学习计算机的各个组成部分的工作原理、性能评估和设计方法,以及各种接口技术的原理和应用。

他们将学习如何选择和配置适当的硬件组件,以满足特定的应用需求,并了解如何开发和实现高效的接口软件。

通过学习计算机组成与接口技术四级,学生将获得深入了解计算机系统内部工作原理的能力,为他们在计算机科学与技术领域的进一步发展打下坚实的基础。

全国计算机等级考试的成绩合格标准_评分标准

全国计算机等级考试的成绩合格标准_评分标准全国计算机等级考试的成绩合格标准①计算机等级考试实行百分制计分,但以等第分数通知考生成绩。

计算机等级考试等第分数分为“不及格”、“及格”、“良好”、“优秀”四等。

100-90分为“优秀”,89-80分为“良好”,79-60分为“及格”,59-0分为“不及格”。

少部分考点将会通报考生的计算机等级考试具体成绩分数,大部分考点及- -般的查询方法将会通报考生的等第,等第代号及含义如下:3.0–优秀,即不小于90分;2.0–良好,即不小于80分但小于90分;1.0–及格,即不小于60分但小于80分;0.0–不及格,即小于60分。

总成绩在及格及其以上者为通过计算机等级考试。

②计算机等级考试成绩在“及格”以上者,由教育部考试中心颁发计算机等级考试合格证书。

成绩“优秀”的,合格证书上会注明“优秀”字样。

对四级科目,只有所含两1门课程分别达到30分,该科才算合格。

一般在计算机等级考试考后30个工作日内由教育部考试中心将成绩处理结果下发给各省级承办机构。

考后50个工作日,考生可登录教育部考试中心综合查询网进行成绩查询。

计算机等级考试报名条件1、计算机等级考试考生不受年龄、职业、学历等背景的限制,任何人均可根据自己学习和使用计算机的实际情况报考。

每次计算机等级考试报名的具体时间由各省(自治区、直辖市)级承办机构规定。

考生按照有关规定到就近考点报名。

2、特殊人员报考条件:现役军人可使用军官证报考计算机等级考试,在其军官证号码前后各加入识别码,此办法也适用于没有身份证的未成年人,识别码的编码有统一格式,前6位后4位。

现役军人可以通过团以上单位集中向地方公安机关申请居民身份证。

3、其他报名注意:计算机等级考试一般不安排专门的补报。

考生如果错过报名点的报名时间,可以直接咨询当地考试院或自考办报名计算机等级考试。

4、计算机等级考试报名须知:需带上身份证以及相关的报名费。

考生报考计算机等级考试一定要亲自到场,不能由任何单位、个人代劳,逐一核实个人信息:姓名、身份证号、照片、报考科目、报考类别(是否补考)等,信息不一致要立刻更改。

计算机硬件与接口专升本试题解析

计算机硬件与接口专升本试题解析一、理论题解析1. 什么是计算机硬件?计算机硬件由哪些组成?计算机硬件是指计算机系统中的物理部分,包括了各种电子设备、机械设备和电路元件。

计算机硬件主要由以下几部分组成:- 中央处理器(CPU):负责执行计算机指令和控制计算机的操作。

- 存储器(内存):用于存储数据和程序,包括主存储器(RAM)和辅助存储器(硬盘、固态硬盘等)。

- 输入设备:用于将外部数据输入到计算机中,如键盘、鼠标、扫描仪等。

- 输出设备:用于将计算机处理后的结果输出,如显示器、打印机、音响等。

- 主板(内部设备):连接各个硬件组件的核心部分,包括芯片组、总线和插槽等。

- 硬盘控制器、声卡等外部设备。

2. 什么是接口?计算机中常见的接口有哪些?接口是计算机硬件之间或计算机硬件与外部设备之间进行数据交换的通道或连接点。

计算机中常见的接口有以下几种:- 并行接口(Parallel Interface):用于数据在多根线上同时传输的接口,如打印机接口(LPT口)。

- 串行接口(Serial Interface):用于数据逐位地顺序传输的接口,如串口(COM口)。

- 通用串行总线(Universal Serial Bus,USB):可同时支持多种设备接入的通用接口。

- 网络接口(Network Interface):用于计算机与计算机之间或计算机与网络之间进行数据通信的接口,如以太网接口。

- 显示接口:用于计算机和显示器之间的连接,如视频图形数组(VGA)接口、高清多媒体接口(HDMI)。

3. 请简述计算机硬件与接口之间的关系。

计算机硬件与接口之间有密切的联系和互相依赖的关系。

计算机硬件通过接口可以实现与其他硬件设备的连接和数据交互,而接口则是硬件设备之间进行数据交换的通道。

接口的不同类型和规范决定了硬件设备的兼容性和连接方式。

硬件和接口之间的匹配与协调,决定了计算机系统的稳定运行和性能优化。

二、分析题解析1. 设计一个简单的电路,使一个输入信号经过2个与门后输出一个灯亮的结果。

全国计算机等级考试考试大纲2021年版

115

全国计算机等级考试一级教程——计算机基础及MS Office应用(2021年版)

3

全国计算机等级考试一级教程——计算机基础及MS Office应用上机指导(2021年版)

4

116

全国计算机等级考试一级教程——计算机基础及Photoshop应用(2021年版)

5

117全国计算机等级考试一级 Nhomakorabea程——网络安全素质教育(2021年版)

二级

二级公共基础知识考试大纲(2020年版)

二级C语言程序设计考试大纲(2018年版)

二级Java语言程序设计考试大纲(2018年版)

二级Access数据库程序设计考试大纲(2021年版)

二级C++语言程序设计考试大纲(2018年版)

二级MySQL数据库程序设计考试大纲(2018年版)

二级Web程序设计考试大纲(2018年版)

19

338

全国计算机等级考试三级教程——信息安全技术(2021年版)

20

339

全国计算机等级考试三级教程——嵌入式系统开发技术(2021年版)

21

371

全国计算机等级考试三级教程——Linux应用与开发技术(2021年版)

22

401

全国计算机等级考试四级教程——操作系统原理(2021年版)

23

402

(2021年版)

15

266

全国计算机等级考试二级教程——Python语言程序设计(2021年版)

16

267

全国计算机等级考试二级教程——WPS Office高级应用与设计(2021年版)

17

335

全国计算机等级考试三级教程——网络技术(2021年版)

四级操作系统原理_考试真题复习资料_全国计算机等级考试NCRE

四级网络工程师操作系统局部1.操作系统概论计算机系统包括硬件系统,软件系统计算机系统的资源包括两大类硬件资源和软件资源硬件系统:中央处理器,存储器,外存储器,以及各种类型的输入输出设备〔键盘,鼠标显示器,打印机〕软件系统:各种程序和数据软件系统又分为:应用软件,支撑软件〔数据库,网络,多媒体〕,系统软件〔操作系统,编译器〕集中了资源管理功能和控制程序执行功能的一种软件称为操作系统2.操作系统的任务:组织和管理计算机系统中的硬件和软件资源向用户提供各种效劳功能〔一方面向程序开发和设计人员提供高效的程序设计接口二向使用计算机系统的用户提供接口〕3.操作系统的特征并发,共享,随机4。

操作系统的功能进程管理存储管理文件管理作业管理和设备管理,用户接口5.操作系统的开展1.手工制作2.早期批处理3.多道批处理4.分时系统6.UNI*系统C语言编写,多用户,多任务,分时操作系统,树形文件系统7.个人计算机操作系统20世纪70年代微软MS DOS 单用户单任务1984年苹果操作系统1992 微软交互式操作系统WINDOWS 3.11995 window951991 linu* linu*遵循UNI*标准POSI* 继承UNI*全部优点8.安卓系统操作系统分类1.按用户界面的使用环境和功能特征批处理操作系统,分时操作系统,实时操作系统随后的开展多了个人操作系统,网络操作系统,分布式操作系统,嵌入式操作系统批处理操作系统:特点成批处理。

目标系统资源利用率高作业吞吐率高〔单位时间计算机系统处理作业的个数〕缺点:不能直接与计算机交互不适合调试程序重点1.1一般指令和特权指令运行模式:用户模式,特权模式为用户效劳的用户模式称作为目态为系统专用的特权模式称为管态机器指令划分为一般指令和特权指令特权指令包括〔输入输出指令,停机指令〕1.2 SPOOLing多道程序的根本思想是在存中同时保持多大作业,主机可以以交替方式同时处理多个作业分时系统设计思想:分时操作系统将CPU的时间划分为假设干个小片段称为时间片特点:多路性,交互性,独占性,及时性分时系统追求的目标是及时响应用户输入的交互命令,用来衡量系统及时响应的指标是响应时间,响应时间越短越好实时系统是使计算机能在规定的时间及时响应外部事件的请求主要目标在严格时间围,对外部请求作出反响,系统具有高度可靠性几个方面的能力1实时时钟管理2.过载防护3.高可靠性嵌入式操作系统高可靠性,实时性,占有资源少,智能化能源管理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机组成与接口冯诺依曼 P1标志寄存器 P16Pentium微处理器模式 P498086复位 P36全相联直接相连映像组相联映像技术 P598259A 中断控制器 P1238251A 串行通讯 P1498255A 并行通讯 P1598253 计数器/定时器 P172ADC0809 模数转换器 P197USB通用总线 P232A/D转换器需要转换启动信号在矩阵式键盘结构中,识别按键位置的方法有B) 逐行扫描法 C) 行反转法采用查询传输方式的工作流程是D) 先读状态端口,再读/写数据端口test执行的就是and的指令,只不过不会保存and执行的结果,而是根据and的结果设置flags寄存器的各种标志test al, 08h 就是测试al的第4位是不是1,8h = 0000 1000同理test ax, 0200h 测试ax的第10位, 0200h = 0000 0010 0000 0000test cl, 01h 测试cl的第1位,01h = 0000 0001汇编程序设计中所使用的地址是逻辑地址汇编语言源程序经过编译后,生成的目标程序的扩展名为OBJ下列码制中,0的表示方法唯一的码制有C.补D.移码码不包含原码反码 -0没补码,移码在通用寄存器中,可以作为间址寄存器使用的有BP SI BX DI P91不可以做间址寄存器的有AX CX DS SS ES CS判断AX和BX中两数是否相等的方法可以采用指令CMP AX,BX SUB AX,BX XOR AX, BX以下指令中与LEA BX, BUFFER功能等价的是MOV BX, OFFSET BUFFER P93有关汇编程序指令 DB 3,100 的叙述中,正确的是指示编译程序分配存储空间和数据不生成机器指令假定 (SS)=2000H,(SP)=0100H,(AX)=2107H,执行指令PUSH AX后,存放数据07H的物理地址是200FEH 在汇编程序中,伪指令的作用是指示编译程序如何进行编译8086对字的存取有时需要两个总线周期来完成8086系统中,单步中断的中断向量在中断向量表中的位置固定在00004H开始的4个字节中8086CPU构成的微机系统中,中断向量表00084H单元开始依次存放有12H,33H,56H,90H,则该中断服务程序的入口地址是93872H8086CPU构成的微机系统中,中断优先权顺序由高到低的顺序是溢出中断,单步中断 NMI,断点中断,INTR 中断,int N8086微机系统中内部中断中断类型码由指令给定中断类型码是约定的8086微机系统中断硬件中断分为非屏蔽中断和可屏蔽中断可屏蔽中断需要执行2个中断响应总线周期溢出中断向量的地址是固定的8086微机系统中,NMI中断的中断向量位置固定在00008H开始的4个单元中可提供X86汇编指令操作数的是存储器寄存器不可以的是控制器 I/O端口 I/O设备由寄存器SS提供堆栈段的段基址,为堆栈段提供偏移地址的寄存器是SP 另DS+SI ES+DI CS+IP DS+DI当8086CPU处于单步工作方式时,标志寄存器中必须为1的标志位是 TF P178086CPU工作在最大工作模式下,产生ALE、DEN、INTA等控制信号的芯片是8288 P38假设8086CPU的主频为5MHz,内存芯片的存取时间为250ns,读/写内存时不需要加入等待周期Tw8086系统中,已知中断类型码为16H ,则其中断服务程序的入口地址存放在内存地址0000H∶0058H~0000H∶005BH8086CPU构成的微机系统中,在执行INT n 指令或者响应硬件中断时,CPU保护现场的顺序依次是CS,IP,FR 8086CPU中断响应和处理过程8086CPU执行完一条指令后对中断进行判断响应中断时,首先保护标志寄存器内容和断点执行中断处理程序前,判断是否有NMI请求,如有则处理该请求8086微处理器的引脚MN/MX接+5V,则执行OUT DX,AX指令时,其引脚M/IO和WR的状态是0和0 P378086有两种工作模式,最大工作模式的特点是需要总线控制器8086CPU在进行读内存操作时,控制信号M/IO 和DT/R 的状态是 1和0若8086 CPU工作在最小工作模式,进行I/O读操作时,M/IO和RD信号的状态为 D) M/IO为低,RD为低8086CPU工作在最小模式下,当其他总线控制部件控制系统总线期间,CPU引脚信号HOLD和HLDA的状态是D) 1和18086系统的DMA方式下,数据传送过程中CPU与总线的关系是C) 成高阻状态X86指令系统中,执行字符串指令时,提供目标串逻辑地址的寄存器是ES和DI8086CPU工作在最小工作模式下,则构成计算机系统的基本部件有 8284时钟发生器 8282地址锁存器8286数据驱动器8086CPU构成的微机系统中,CPU与存储器连接的特点是系统总线的数据总线宽度为8位D) 存储体分为奇/偶两个存储体 E) 系统总线的地址总线宽度为20位8086对字的存取有时需要两个总线周期来完成属于8086CPU的BIU部件是段地址寄存器地址加法器指令流队列8086 CPU中,控制信号DEN的作用是CPU发出的数据传输有效控制信号当8086 CPU采样到READY=0时,CPU将插入等待周期8086CPU构成的微机系统使用寄存器间址方式访问I/O端口时,DX中存放的是I/O端口地址8086微处理器中,标志寄存器中的OF位为1时,表示有符号的字运算结果超出-32768~32767的范围Pentium微处理器的引脚收到SMI请求信号,进入系统管理模式 P49Pentium微处理器中,若不允许虚拟8086模式下的中断,则标志寄存器的标志位设置正确的是 VIP=1 P47 Pentium处理器中,由CALL指令,中断或异常引起子程序被调用时,标志寄存器的嵌套标志位的值是NT = 1 Pentium微处理器配备了5个控制寄存器,其中未定义的控制寄存器是CR1Pentium微处理器的5个控制寄存器中,负责控制处理器工作模式的寄存器是CR0pentium微处理器中,程序员不能直接读写的32位寄存器是TRPentium微处理器的数据总线宽度是64位Pentium微处理器的结构被称为超标量结构的原因是Pentium微处理器内部含有多条指令流水线和多个执行部件Pentium微处理器的特点是内部集成了增强型浮点处理部件FPU 设置了互相独立的片内代码cache和数据cache .采用分段和分页两级存储管理机制,并且允许页面大小可调采用了U、V二条流水线Pentium微处理器可访问的物理存储器的范围A) 4GBPentium微处理器的分页存储管理系统可以把页的大小定义成4MBPentium的虚拟存储机制下 A) 虚拟存储器对应的地址也叫逻辑地B) 虚拟存储器比主存储器容量大Pentium微处理器中,若当前工作在虚拟8086方式下,则标志寄存器的标志位设置正确的是B) VM=0 Pentium存储管理由分段部件和分页部件协同完成分段部件将逻辑地址转换为线性地址分页部件将线性地址转换为物理地址段描述符为处理器提供段的访问控制及状态信息采用描述表结构进行管理Pentium系统段描述符每个任务可定义很多段,每段对应一个段描述符 D.段描述符中包含了段的大小、位置、状态信息和控制信息 E.段描述符的内容由操作系统生成Pentium采用描述符表的优点是可大大扩展存储空间可实现虚拟存储可实现多任务隔离Pentium微处理器工作在保护模式下,采取分段管理时,用来区分是系统段描述符还是非系统段描述符的字段是程序段描述符中的S字段 P46Pentium微处理器工作在保护模式下,每个段寄存器都有64位不可见部分,其中装载的是段描述符当Pentium微处理器工作在保护模式下时支持多任务操作Pentium系统在保护模式下,每一个程序都拥有它自己的存储空间以及段描述符Pentium微处理器在保护模式下,段寄存器内存放的是段选择符Pentium微处理器工作在保护模式下,采用门描述符的作用是控制访问的目标代码段的入口点Pentium微处理器工作在保护模式下使用门描述符控制访问目标代码的入口,是门描述符的是调用门描述符任务门描述符中断门描述符陷阱门描述符Pentium微处理器工作在保护模式下,分页管理机制中的页目录项的包含下一级页表的基址和有关页表信息Pentium微处理器工作在保护模式下时,组成虚拟地址的是 16位段选择符和32位偏移量Pentium保护模式下的分页管理机制中的物理地址是由10位页目录索引和10位页表索引与12位页内偏移量组成8位机器数80H作为补码表示时,对应的十进制真值是-128 1000 0000减一得反码0111 1111 反码取反为1000 0000 ,原码为1000 0000 -128已知[X]补,求[1/4X]补的方法是[X]补算术右移2位浮点数规格化A) 高浮点数的精度C) 浮点数的尾数左移实现的规格化叫左规 D) 浮点数的尾数右移实现的规格化叫右规若浮点数用补码表示,则判断运算结果是否为规格化数的方法是数符与尾数小数点后第一位数字相异机器数,符号位也数值化了的数叫机器数原码格式表示的数是机器数补码格式表示的数是机器数CPU对存储器或I/O端口完成一次读/写操作所需的时间称为一个存储周期一个完整的指令周期应包括取指周期和执行周期闪速存储器(Flash Memory)主要特点是既可在不加电的情况下长期保存信息,又能在线进行快速擦除与重写虚拟存储器虚拟存储器将主存和辅存地址空间统一编址虚拟存储器的大小受辅助存储器容量的限制使主存的空间得到了扩充存储器与CPU之间连接时,应考虑的是合理分配内存地址空间存储芯片片选线的连接 CPU内部总线的宽度DRAM芯片通常采用电容保存信息,常用刷新方式有集中式刷新分布式刷新异步式刷新) DRAM是一种随机存储器 DRAM是一种易失性存储器,断电则丢失存储信息 DRAM需要刷新操作,不定时刷新,数据会丢失 DRAM是一种半导体存储器存储器映象编址,也称为统一编址,其特点是无专用的I/O指令Cache中存放的是主存储器中一部分信息的映像硬磁盘存储器的主要性能指标有 A.存储密度 B.存储容量 C.转速 D.平均存取时间 E.数据传输率温切斯特磁盘主要特点是采用密封组合方式,将磁头、盘片、驱动部件以及读/写电路等组装成一个不能随意拆卸的整体8086CPU构成的微机系统中,中断源来自两个方面,即外部中断和内部中断硬件中断和软件中断的区别是中断的引发方式不同获取中断类型码的方式不同根据中断类型码转向中断服务程序的方式不同 E) 中断响应的条件不同8086CPU在响应INTR中断时中断类型码由I/O提供在8086CPU的下列4种中断中,需要由硬件提供中断类型码的是INTR8086CPU执行IRET指令,从堆栈当前栈顶弹出的字节数为6个字节为使8086CPU能响应NMI的中断请求不可屏蔽中断标志寄存器的IF置1/置0均可根据中断类型码转向中断服务程序的方式不同中断响应的条件不同8259A在特殊全嵌套方式下可以响应同级和更高级的中断请求8259A芯片可设置成脉冲边沿触发方式电平触发方式全嵌套方式(非)自动中断结束方式特殊屏蔽方式一般屏蔽方式8259A可编程中断控制器的中断服务寄存器ISR用于标识正在处理中的中断8259A芯片工作流程 8259A的操作命令字可根据需要使用,不必按照顺序使用级联的情况下,主片和从片必须分别进行初始化根据情况,OCW2可以不用初始化8259A工作在8086模式时,初始化命令字ICW2用来设置中断类型码的高5位若芯片8259A的IR3接一个外部中断请求,8259A的ICW2设为83H,则该片8259A所提供的中断类型码范围是80H~87H8259A可编程中断控制器可以用ICW4设置的工作方式是特殊全嵌套方式 B.缓冲方式 C.自动中断结束方式8259A在初始化时只进行ICW1和ICW2的设置,则该8259A工作在单片8259A,没有级联中断请求优先级固定按IR0-IR7排列非缓冲方式一般中断结束方式8259A芯片工作流程A) 8259A的操作命令字可根据需要使用,不必按照顺序使用C) 级联的情况下,主片和从片必须分别进行初始化 E) 根据情况,OCW2可以不用初始化下列关于SRAM的叙述,正确的是下列关于SRAM的叙述,正确的是 ABDEA. SRAM是一种随机存储器B. SRAM是一种易失性存储器,断电则丢失存储信息C. SRAM需要刷新操作,不定时刷新,数据会丢失D. SRAM速度快,通常用来制作高速缓存E. SRAM芯片与CPU连接时要注意时序匹配下列关于DRAM的叙述,正确的是 ABCDA. DRAM是一种随机存储器B. DRAM是一种易失性存储器,断电则丢失存储信息C. DRAM需要刷新操作,不定时刷新,数据会丢失D. DRAM是一种半导体存储器E. DRAM芯片与CPU连接时要注意时序匹配存储器与CPU之间的连接时,下列各项中应考虑的是 CDEA. 数据线的连接B. CPU的时序应与存储器的存取速度相互配合C. 合理分配内存地址空间D. 存储芯片片选线的连接E. CPU内部总线的宽度内存需求量大,通常选用DRAM高速缓存要求速度快,通常选用SRAMEPROM可擦除可编程的只读存储器。