第2章 存储器与总线架构.

STM32入门简易教程

器配置等详细信息。 3、 STM32F103RB 数据手册

a) 产品的基本配置(内置 FLASH 和 RAM 的容量、外设模块的种类和数量等); b) 管脚的数量和分配,电气特性,封装信息和订购代码等。 4、 STM32 开发板手册 与开发板配套的参考资料,有很多经验值得借鉴。 5、 stm32 固件库 a) 相关定义,文档约定和固件库规则; b) 库的架构,安装指南及使用实例; c) 每个外围模块的函数及解释。 6、 开发板原理图 必不可少的硬件电路参考。 7、 互联网 取之不尽的知识宝库。

意法半导体是市场上第一家提供基于 Cortex-M3 内核的无传感器的磁场定向电机控制

解决方案的厂商。这套工具证明 STM32 的内核和专用电机控制外设都有充足的处理能力来 优化驱动器的性能,最小化系统总体成本。STM 微控制器在 25 微秒内即可执行一整套无传 感器三相无刷永磁同步电机(PMSM)矢量控制算法,大多数应用任务占用 CPU 资源比率 小于 30%,为 CPU 执行其它应用任务(如需要)预留了充足的处理能力。永磁电机同步电 机控制解决方案的代码大小少于 16 千字节。

二、重要的参考资料

1、 Cortex-M3 权威指南 宋岩 译 权威资料的精简版,思路清晰,有条理,适合学 Cortex-M3 处理器的所有人。

2、 STM32 技术参考手册 a) STM32 微控制器产品的技术参考手册是讲述如何使用该产品的; b) 包含各个功能模块的内部结构、所有可能的功能描述、各种工作模式的使用和寄存

在性能方面,STM32 系列的处理速度比同级别的基于 ARM7TDMI 的产品快 30%,换 句话说,如果处理性能相同,STM32 产品功耗比同级别产品低 75%。同样地,使用新内核 的 Thumb 2 指令集,设计人员可以把代码容量降低 45%,几乎把应用软件所需内存容量降 低了一半。此外,根据 Dhrystones 和其它性能测试结果,STM32 的性能比最好的 16 位架构 至少高出一倍。

计算机组成原理——存储器和总线实验

实验六存储器和总线实验一、实验目的熟悉存储器和总线组成的硬件电路。

二、实验要求按照实验步骤完成实验项目,利用存储器和总线传输数据三、实验内容实验原理图如下(省略图):(1)实验原理按照实验所用的半导体静态存储器电路图进行操作,该静态存储器由一片6116(2K x 8)构成,其数据线(D0-D7)已和数据总线(BUS-DISP UNIT)相连接,地址线由地址锁存器(74LS273)给出,该锁存器的输入已连接至数据总线。

地址A0-A7与地址总线相连,显示地址内容。

数据开关经一三态门(74LS245)已连接至数据总线,分时给出地址和数据。

因为地址寄存器为8位,接入6116的地址A7-A0,而高三位A8-A10本实验装置已接地,其容量为256字节。

6116有三根控制线:/CS(片选线)、OE(读线)、WE(写线)。

当片选有效(/CS=0)时,同时OE=0时,(WE=0)时进行读操作。

本实验中将OE引脚接地,在此情况下,当/CS=0、WE=1时进行写操作,/CS=0、WE=0时进行读操作,其写时间与T3脉冲宽度一致。

实验时T3脉冲由“单步”命令键产生,其他电平控制信号由二进制开关模拟,其中/CE(存储器片选信号)为低电平有效,WE为写/读(W/R)控制信号,当WE=0时进行读操作、当WE=1时为写操作。

(2)实验步骤1、控制信号连接:位于实验装置右侧边缘的RAM片选端(/CE)、写/读线、(WE)、地址锁存信号(LDAR)与位于实验装置左上方的控制信号(/CE、WE、LDAR)之间对应相连接。

位于实验装置左上方CTR-OUT 的控制信号(/SW-B)与左下方INPUT-UNIT(/SW-B)对应相连接。

具体信号连接:/CW,WE,LDAR,/SW-B2、完成上述连接,仔细检查无误后方可进入本实验。

在闪动上的“P.”状态下按动增址命令键,使LED显示自左向右第一位显示提示符“H”,表示本装置已进入手动单元实验状态。

微处理器系统结构与嵌入式系统设计(第二版)答案全

“微处理器系统结构与嵌入式系统设计”第一章习题解答1.2 以集成电路级别而言,计算机系统的三个主要组成部分是什么?中央处理器、存储器芯片、总线接口芯片1.3 阐述摩尔定律。

每18个月,芯片的晶体管密度提高一倍,运算性能提高一倍,而价格下降一半。

1.5 什么是SoC?什么是IP核,它有哪几种实现形式?SoC:系统级芯片、片上系统、系统芯片、系统集成芯片或系统芯片集等,从应用开发角度出发,其主要含义是指单芯片上集成微电子应用产品所需的所有功能系统。

IP核:满足特定的规范和要求,并且能够在设计中反复进行复用的功能模块。

它有软核、硬核和固核三种实现形式。

1.8 什么是嵌入式系统?嵌入式系统的主要特点有哪些?概念:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积和功耗的严格要求的专用计算机系统,即“嵌入到应用对象体系中的专用计算机系统”。

特点:1、嵌入式系统通常是面向特定应用的。

2、嵌入式系统式将先进的计算机技术、半导体技术和电子技术与各个行业的具体应用相结合的产物。

3、嵌入式系统的硬件和软件都必须高效率地设计,量体裁衣、去除冗余,力争在同样的硅片面积上实现更高的性能。

4、嵌入式处理器的应用软件是实现嵌入式系统功能的关键,对嵌入式处理器系统软件和应用软件的要求也和通用计算机有以下不同点。

①软件要求固体化,大多数嵌入式系统的软件固化在只读存储器中;②要求高质量、高可靠性的软件代码;③许多应用中要求系统软件具有实时处理能力。

5、嵌入式系统和具体应用有机的结合在一起,它的升级换代也是和具体产品同步进行的,因此嵌入式系统产品一旦进入市场,就具有较长的生命周期。

6、嵌入式系统本身不具备自开发能力,设计完成以后用户通常也不能对其中的程序功能进行修改,必须有一套开发工具和环境才能进行开发。

第二章习题答案2.2 完成下列逻辑运算(1)101+1.01 = 110.01(2)1010.001-10.1 = 111.101(3)-1011.0110 1-1.1001 = -1100.1111 1(4)10.1101-1.1001 = 1.01(5)110011/11 = 10001(6)(-101.01)/(-0.1) = 1010.12.3 完成下列逻辑运算(1)1011 0101∨1111 0000 = 1111 0101(2)1101 0001∧1010 1011 = 1000 0001(3)1010 1011⊕0001 1100 = 1011 01112.4 选择题(1)下列无符号数中最小的数是( A )。

微机原理课件第二章 8086系统结构

但指令周期不一定都大于总线周期,如MOV AX,BX

操作都在CPU内部的寄存器,只要内部总线即可完成,不 需要通过系统总线访问存储器和I/O接口。

2021/8/17

17

• 8086CPU的典型总线时序,充分体现了总 线是严格地按分时复用的原则进行工作的。 即:在一个总线周期内,首先利用总线传 送地址信息,然后再利用同一总线传送数 据信息。这样减少了CPU芯片的引脚和外 部总线的数目。

• 执行部件(EU)

• 功能:负责译码和执行指令。

2021/8/17

5

• 联系BIU和EU的纽带为流水指令队列

• 队列是一种数据结构,工作方式为先进先出。写入的指令 只能存放在队列尾,读出的指令是队列头存放的指令。

2021/8/17

6

•BIU和EU的动作协调原则 BIU和EU按以下流水线技术原则协调工作,共同完成所 要求的任务: ①每当8086的指令队列中有空字节,BIU就会自动把下 一条指令取到指令队列中。 ②每当EU准备执行一条指令时,它会从BIU部件的指令 队列前部取出指令的代码,然后译码、执行指令。在执 行指令的过程中,如果必须访问存储器或者I/O端口, 那么EU就会请求BIU,完成访问内存或者I/O端口的操 作; ③当指令队列已满,且EU又没有总线访问请求时,BIU 便进入空闲状态。(BIU等待,总线空操作) ④开机或重启时,指令队列被清空;或在执行转移指令、 调用指令和返回指令时,由于待执行指令的顺序发生了 变化,则指令队列中已经装入的字节被自动消除,BIU会 接着往指令队列装入转向的另一程序段中的指令代码。 (EU等待)

•CF(Carry Flag)—进位标志位,做加法时最高位出现进位或 做减法时最高位出现借位,该位置1,反之为0。

STM32F407xx芯片手册第1到3章中文翻译

STM32F407xx芯⽚⼿册第1到3章中⽂翻译1⽂档约定寄存器缩写列表下⾯的缩写⽤于描述寄存器Read/Write(rw)软件可读写Read-Only(r)软件只读Write-only(w)软件只写Read/clear(rc_w1)软件可读,写1清除,写0⽆作⽤Read/clear(rc_w0)软件可读,写0清除,写1⽆作⽤Read/clear by read软件可读,读后⾃动清零,写0⽆作⽤Read/set(rs)软件可读,可置位,写0⽆作⽤Read-only writeTrigger(rt_w)软件可读,写0或1翻转此位Toggle(t)写1翻转,写0⽆作⽤Reserved(Res.)保留位,必须保持复位值2存储器和总线架构2.1系统架构主系统包括32位多层互联AHB总线阵列,连接以下部件:Height masters—Cortex TM-M4F内核I-Bus(指令总线),D-bus(数据总线)和S-bus(系统总线)—DMA1存储器总线—DMA2存储器总线—DMA2外设总线—以太⽹DMA总线—USB OTG HS DMA总线Seven slaves—内置Flash存储器指令总线—内置Flash存储器数据总线—主内置SRAM1(112KB)—辅助内置SRAM2(16KB)—AHB1外设,包括AHB到APB的桥以及APB外设—AHB2外设—FSMC接⼝总线矩阵提供从主设备到从设备的访问,即使在有若⼲⾼速外设同时运⾏的情况下也能并⾏访问并⾼效运转。

这个架构如图1所⽰。

注意:64KB的CCM(内核耦合存储器core coupled memory)数据RAM并不是总线矩阵的⼀部分,它只能通过CPU来访问。

图1系统架构2.1.1S0:指令总线这条总线连接Cortex TM-M4F内核的指令总线到总线矩阵,⽤于内核取指。

总线的Target是存储有代码的存储器(包括内置Flash存储器/SRAM以及通过FSMC外扩的外部存储器)。

单片机习题答案

《单片机应用技术》习题答案第一章概述1. 什么是总线?总线主要有哪几部分组成?各部分的作用是什么?总线是连接计算机各部件之间的一组公共的信号线。

一般情况下,可分为系统总线和外总线。

系统总线应包括:地址总线(AB)控制总线(CB)数据总线(DB)地址总线(AB):CPU根据指令的功能需要访问某一存储器单元或外部设备时,其地址信息由地址总线输出,然后经地址译码单元处理。

地址总线为16位时,可寻址范围为216=64K,地址总线的位数决定了所寻址存储器容量或外设数量的范围。

在任一时刻,地址总线上的地址信息是惟一对应某一存储单元或外部设备。

控制总线(CB):由CPU产生的控制信号是通过控制总线向存储器或外部设备发出控制命令的,以使在传送信息时协调一致的工作。

CPU还可以接收由外部设备发来的中断请求信号和状态信号,所以控制总线可以是输入、输出或双向的。

数据总线(DB):CPU是通过数据总线与存储单元或外部设备交换数据信息的,故数据总线应为双向总线。

在CPU进行读操作时,存储单元或外设的数据信息通过数据总线传送给CPU;在CPU进行写操作时,CPU把数据通过数据总线传送给存储单元或外设2.什么是接口电路? CPU与接口电路连接一般应具有哪些信号线?外部设备与接口电路连接一般应具有哪些信号线?CPU通过接口电路与外部输入、输出设备交换信息,一般情况下,外部设备种类、数量较多,而且各种参量(如运行速度、数据格式及物理量)也不尽相同。

CPU为了实现选取目标外部设备并与其交换信息,必须借助接口电路。

一般情况下,接口电路通过地址总线、控制总线和数据总线与CPU连接;通过数据线(D)、控制线(C)和状态线(S)与外部设备连接。

3. 存储器的作用是什么?只读存储器和随机存储器有什么不同?存储器具有记忆功能,用来存放数据和程序。

计算机中的存储器主要有随机存储器(RAM)和只读存储器(ROM)两种。

随机存储器一般用来存放程序运行过程中的中间数据,计算机掉电时数据不再保存。

第2章微型计算机系统的组成及工作原理

2.5.6 ISA总线的定义与应用

2. ISA总线的信号线定义 ——98芯插槽,包括地址线、数据线、控制线、时钟和电源线 (1)地址线:SA019和LA1723 (2)数据线:SD015 (3)控制线:AEN、BALE、 IOR 和 IOW、 SMEMR和 SMEMW

MEMR 和 MEMW、 MEM CS16 和 I/O CS16 、SBHE

2.1.2 微机系统的软件配置

系统软件、工具软件、应用软件、用户应用程序

.3 微机系统中的信息流与信息链

1. 微机系统中信息流与信息链的构成 信息流:存储器中的数据、程序代码;接口寄存器中的I/O数据、 状态、I/O命令 信息链:信息流在系统中流动的路径; 包括物理(硬件)环节和逻辑(软件)环节 2. 微机系统中信息流与信息链 ——早期微机系统/现代微机系统中的信息链 3. 研究信息流与信息链的意义 ——通过信息流从整体上认识微机体系结构和组成微机系统的各 部件之间的关系

2.5.7 现代微机总线技术的新特点

3. 总线桥 (1) 总线桥 ——总线转换器和控制器,是两种不同总线间的总线接口 内部包含兼容协议及总线信号和数据缓冲电路;把一条总线映 射到另一条总线上 北桥:连接CPU总线和PCI总线的桥 南桥:连接PCI总线和本地总线(如ISA)的桥 (2) PCI总线芯片组 ——实现总线桥功能的一组大规模集成专用电路 保持主板结构不变前提下,改变这些芯片组的设计,即可适应 不同微处理器的要求 4. 多级总线结构中接口与总线的连接

2.4 I/O设备与I/O设备接口

2.4.1 I/O设备及其接口的作用

1. I/O设备的作用 2. I/O设备接口的作用——连接与转换

2.4.2 I/O设备的类型及设备的逻辑概念

计算机第二章习题答案恢复版

一.简述计算机系统的组成。

计算机系统由硬件系统和软件系统两部分组成。

硬件系统是组成计算机系统的各种物理设备的总称,是计算机完成各项工作的物质基础。

软件是指用某种计算机语言编写的程序数据和相关文档的集合。

软件系统则是在计算机上运行的所有软件的总称。

其中,硬件系统包括主机和外设,主机又分为中央处理器(CPU)和内存,内存分为随机存取存储器(RAM),只读存储器(ROM),高速缓冲存储器(Cache),,中央处理器又分为运算器(ALU)和控制器(CU).。

外设分为输入设备(键盘,鼠标,触摸屏,扫描仪麦克风等)输出设备(显示器,打印机,绘图仪,音响等)外存(软盘,硬盘,光盘,U盘等)。

软件系统分为系统软件和应用软件。

其中,系统软件又包括操作系统(DOS,windows,OS/2,UNIX,)语言处理程序(C,C++)实用程序(诊断程序,排错程序),应用软件又包括通用应用软件(办公软件包,数据库管理系统,计算机辅助设计软件)和专业应用软件(如各企业的信息管理系统等)二.计算机硬件包括哪些部分,分别说明个部分的作用。

硬件是指计算机装置,即物理设备主要包括以下几部分:1,运算器,又称算术逻辑单元,它的主要功能是进行算术运算和逻辑运算。

2,控制器,是指挥计算机的各个部件按照指令的功能要求协调工作的部件。

3,存储器,基本功能是能够按照指定位置存入或取出二进制信息。

4,输入设备,用来接收用户输入的原始数据和程序,并将它们转变为计算机可以识别的形式放到内存中。

5,输出设备,用于将存放在内存中由计算机处理的结果转变为人们所能接受的形式。

三.指令和程序有什么区别?试述计算机执行指令的过程。

指令,即能被计算机识别并执行的二进制代码,它代表了计算机能完成的某一项操作。

程序,即指令的集合。

执行过程分为下列三步;①取指令:按照程序计数器中的地址从内存储器中取出指令并送往指令计数器。

②分析指令:对指令寄存器中存放的指令进行分析,由指令译码器对操作码进行译码,将指令的操作码转换成相应的控制电位信号;由地址码确定操作数地址。

微处理器与系统结构PPT详细讲解

•29 •HLDA* •28 •WR*

有效,三态)

•27 •M/IO* 测试信号(输入、低电

•26 •DT/R* •25 •DEN*

平有效)

•24 •23 •22

•ALE* •INTA* •TEST

READY 准备就绪(输入 、高电平有效)

•21 •READY

•RESET

状态信号指示当前使用段

一、8086通用引脚信号

•1

•40 •VCC

•2

•39 •AD15 INTR可屏蔽中断请求

•3 •4

•38 •A16/S3 •37 •A17/S4

信号(输入、高有效)

•5 •6

•36 •35

•A18/S5 •A19/S6

NMI非屏蔽中断请求(

•7 •8

•34 •BHE/S7 •33 •MN/M

输入,上升沿触发)

•GND •AD14 •AD13 •AD12 •AD11 •AD10 •AD9 •AD8 •AD7 •AD6 •AD5 •AD4 •AD3 •AD2 •AD1 •AD0 •NMI •INTR •CLK •GND

二、8086最小模式引脚信号

M/ 存储器/IO控制信号

•1 •2 •3

•40 •39 •38

微处理器与系统结构PPT详 细讲解

第二章学习要点

重点掌握内容: 1.微处理器的基本结构。 2.Intel 8086微处理器的基本结构,包括: 功能结构、寄存器结构和总线结构。 3.Intel 8086微处理器系统的组成: 控制核心单元+存储器组织+I/O端口组织 4.Intel 8086微处理器在最小模式下的典型总线 操作和时序。 5.几个重要概念:时钟周期,总线周期,指令周期。

cortex-m3体系结构

5、XPSR----程序状态寄存器

应用状态寄存器(APSR) 中断状态寄存器(IPSR) 执行状态寄存器(EPSR)

程序状态寄存器----应用状态寄存器(APSR)

APSR的位分配

31 30 29 28 27 26

0

NZCVQ

保留

饱和(sticky saturation)标志

溢出标志: 1:溢出 0:没有溢出

7、控制寄存器CONTROL

CONTROL[1:0] 由两个状态位组成:

CONTROL[1] CONTROL[0]

0

主堆栈

特权级

1

进程堆栈

用户级

寄存器总结

寄存器名称 APSR IAPSR EAPSR XPSR

功能 应用状态寄存器 APSR和IPSR的组合 APSR和EPSR的组合 APSR、EPSR和IPSR的组合

STEP4

EPSR使用的是[26:24]和[15:10]位

6、异常中断寄存器

6-1中断屏蔽寄存器( PRIMASK )

PRIMASK 1

0

只有最低位有效

屏蔽所有中断

响应中断

相当于中断总开关, 为1,所有中断被屏蔽; 为0,中断能正常响应。

6-2 中断屏蔽寄存器BASEPRI

BASEPRI 2

优先级0 优先级1

IPSR EPSR IEPSR MSP PSP PRIMASK BASEPRI BASEPRI_MAX FAULTMASK CONTROL

中断状态寄存器 执行状态寄存器 IPSR和EPSR的组合 主堆栈指针 进程堆栈指针 中断屏蔽寄存器 可屏蔽等于和低于某个优先级的中断 BASEPRI允许设置的最大值 错误屏蔽寄存器 控制寄存器

DSP课件第2章硬件结构

5、电源

采用高性能静态CMOS技术,供电电压为3.3V。 可用IDLE指令进入低功耗模式。

6、在片仿真接口

具有符合IEEEll49.1标准的在片仿真接口(JTAG)。

7、速度

单周期定点指令的执行时间为50ns、35ns或25ns(20MIPS,28.5MIPS, 或40MIPS)。

2.2 TMS320LF240x的总线结构

INTM:中断模式位

用来允许(INTM=0)或禁止(INTM=1)所有的可屏蔽中断。用 SETC OVM或CLRC OVM可将该位置1或清0。LST指令不影响OVM位。

DP:数据页面指针

当使用直接寻址方式时,DP存放存储器的数据页,DP与指令代 码的最低7位构成16位存储器地址。

数据存储器地址

SARAM的地址可以用于数据存储器和程序存储器。可通过软件配置 为外部存储器或内部SARAM。

SARAM在一个机器周期内只能访问一次。当CPU要求多次访问时, SARAM会向CPU提供一个未准备好的信号,然后在每个周期内执行一次 访问。

闪速存储器(Flash) 是电可擦除的、可编程的、可长期保存数据的存储器。

CPU的基本组成包括: 32位中央算术逻辑运算单元(CALU); 32位累加器(ACC);输入与输出数据比例移位器; 16位×16位的乘 法器(MUL)以及乘积比例移位器。

CPU功能结构图

2、输入比例部分

功能:将来自存储器的16位数据左移0~16位送往中央算术逻辑单元 (CALU)。

移位方法:左移后有使用的低位LSB填0,高位MSB填0或用符号 扩展,取决于状态寄存器ST1的符号扩展模式位SXM(D10)。 SXM=0 填0 SXM=1 符号扩展

中央算术逻辑单元

第二章PIC单片机系统结构

13

PICmicro® 架构

指令实例 PIC MCU 指令编码为操作码和参数 编码用一个字完成

操作码 OP CODE

操作数 k k k k k k k k

PIC微控制器实验室 大学生创新实验室

14

精简指令RISC

• PIC16F877指令集只有35条指令 学习、程序设计便利 • 全部采用单字节指令 (除4条条件跳转指令外)均为单周期指 令 • “单字节”:专指指令字节

Fetch 1 Execute 1 1. MOVLW 55h Fetch 2 Execute 2 2. MOVWF PORTB Fetch 3 Execute 3 3. CALL SUB_1 Fetch 4 4. BSF PORTA, BIT3

Flush Fetch 4 Fetch SUB_1

PIC微控制器实验室 大学生创新实验室

PIC微控制器实验室 大学生创新实验室

20

上电复位 上电延时:72ms 起振延时:1024个时钟周期 看门狗定时器:监视程序运行状态 欠压复位:当电源电压低于4V,单片机保持在 复位状态 在线调试:对芯片程序直接调试 低压编程:允许工作电压VDD作为编程电 压

PIC微控制器实验室 大学生创新实验室

Bank 1

PIC微控制器实验室 大学生创新实验室

31

PIC单片机架构 程序存储器组织

复位矢量入口地址

0000H 0000H

0001H 0001H 0002H 0002H 0003H 0003H

中断服务程序入口地址 片内程序 存储器

0004H 0004H

页面1 页面2 页面3

07FFH 07FFH

分页的程序存储器 分页的程序存储器

(14位内核)

第2章_微型计算机系统基础(2)

2.2.3 存储器

计算机的存储器用来存放程序和数据,其容量的大 小、存取数据速度的快慢将直接影响到微机系统的性能。

随机存储器 RAM

主存储器 (内 存) 只读存储器 ROM 可编程只读存储器 PROM 可改写只读存储器 EPROM

存 储 器

外存储器 (辅助存储 器)

磁盘存储器:软磁盘、硬磁盘 光盘存储器

(3)控制总线(CB):用于传送控制信 息和时序信息。控制信息中,有的是 CPU向内存或CPU向I/O接口电路发出的 信号,如读/写信息、片选信号、中断 响应信号等。控制总线上的信息传送方 向由具体控制信号而定,一般是双向的, 控制总线的位数要根据系统的实际需要 确定。

3.外部总线 外部总线是微型计算机和外部设备 之间的总线,微型计算机作为一种设备, 通过该总线和其他设备进行信息与数据 交换。

内存地址

RAM在实际存储的时候被分成 为许多等长的存储单元,在微机 中一般按照字节存储,即按字节 来分存储单元。比如,如果有内 存1kB,则被分为1024个存储单 元。每个存储单元将被赋予一个 编号即内存地址。 注意区分内存地址和内存 地址中的内容。

FFFFH

0002H

0001H

0000H

2、外存

2.2.7 微型计算机的主要性能指标

性能指标

(分32位、64位等几种字长)

重点

字长:计算机一次可并行处理的二进制数码的位数

运算速度(或时钟频率)——MIPS(每秒百万条指令) 主频,即主时钟频率。 80486:33MHZ~66MHZ之间 Pentium 4:2.4GHZ 频率越高,速度越快。 主(内)存贮器的容量:128MB/256MB/512MB/1GB等 外部设备配置 此外,还有功能指标、可靠性指标、兼容性指标等。

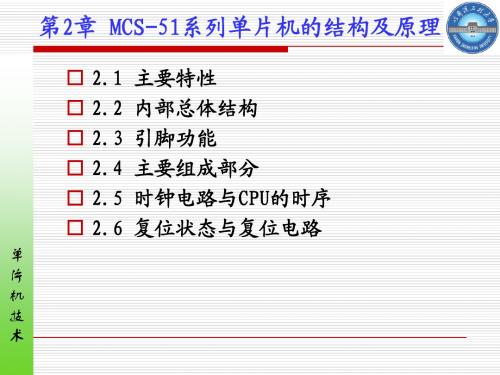

第2章 MCS-51系列单片机的结构及原理

2.3 引脚功能——封装形式

40P6-PDIP

单 片 机 技 术

2.3 引脚功能——引脚含义

P1. 0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST RXD/ P3. 0 TXD/ P3.1 INT0/ P3.2 INT1/ P3.3 T0/ P3.4 T1/ P3.5 WR/ P3.6 RD/ P3.7 XTAL2 XTAL1 VSS 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 24 22 21 VCC P0. 0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 EA ALE PSEN P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2. 0

2mcs51系列单片机的内部总体结构88微处理器运算部件b数据存储器ramp0口p2口程序存储器特殊功特殊功能寄存器sfrromepromvccvss图21mcs51单片机的基本结构控制部件p1口p3口串行口定时计数器中断系统88xtal1xtal2psenaleeareset端口0驱动器端口2驱动器ram地址锁存器ram1288端口0锁存器端口2锁存器rom4k8b寄存器程序地址寄存器缓冲器寄存器vcc5vvss堆栈指针spacctmp2tmp1p00p07p20p27图22mcs51片内总体结构框图rstpc1寄存器pcdptr指针p10p17psw端口3锁存器端口1锁存器端口1驱动器端口3驱动器scontl0tmodth1iepconth0sbuftxrx中断串行口和定时器逻辑tcontl1iposcp30p37alepsenxtal2xtal1alu指令寄存器定时与控制指令译码器返回本节2

第2章Nios II的体系结构 SOPC技术与应用

第1节Nios II处理器结构与Nios II的寄存器文件3.1 Nios II处理器结构Nios II是一种软核(Soft-Core)处理器。

所谓软核,是指未被固化在硅片上,使用时需要借助EDA软件对其进行配置并下载到可编程芯片(比如FPGA)中的IP核。

软核最大的特点就是可由用户按需要进行配置。

Nios II软核处理器简介Nios II 处理器系列包括三种内核Nios II 处理器结构框图Nios II采用哈佛结构,数据总线和指令总线分开。

为了调试方便,Nios II处理器集成了一个JTAG调试模块。

为了提高系统的整体性能,Nios II内核不仅可以集成数据Cache和指令Cache,还带有紧耦合存储器TCM 接口。

TCM可以使Nios II处理器既能提高性能,又能获得可预测的实时响应。

Nios II把外部硬件的中断事件交由中断控制器管理,内核异常事件交由异常控制器管理。

Nios II的寄存器文件包括32个通用寄存器和6个控制寄存器,Nios II结构允许将来添加浮点寄存器。

3.2 Nios II的寄存器文件Nios II的控制寄存器Nios II的控制寄存器共有6个,它们的读/写访问只能在超级用户模式(Supervisor Model)下由专用的控制寄存器读/写指令(rdctl和wrctl)实现。

通过控制寄存器一览表,来了解控制寄存器各位的意义。

通用寄存器一览Nios II的控制寄存器共有6个,它们的读/写访问只能在超级用户模式(Supervisor Model)下由专用的控制寄存器读/写指令(rdctl和wrctl)实现。

通过控制寄存器一览表,来了解控制寄存器各位的意义控制寄存器一览(3)算术逻辑单元(ALU)Nios II ALU支持的操作未实现的指令用户指令浮点指令(4)复位信号Nios II处理器支持两个复位信号:reset和cpu_resetrequestreset:是一个强制处理器核立即进入复位状态的全局硬件复位信号。

微机原理及应用课件第2章

四、内部寄存器

内部寄存器的类型

含14个16位寄存器,按功能可分为三类

8个通用寄存器 4个段寄存器 2个控制寄存器

深入理解:每个寄存器中数据的含义

28

1. 通用寄存器

数据寄存器(AX,BX,CX,DX) 地址指针寄存器(SP,BP) 变址寄存器(SI,DI)

29

数据寄存器

8088/8086含4个16位数据寄存器,它们又可分为8个 8位寄存器,即:

DX:

数据寄存器。在间接寻址的I/O指令中存放I/O端口地址;在 32位乘除法运算时,存放高16位数。

地址指针寄存器

SP:堆栈指针寄存器,其内容为栈顶的偏移地址; BP:基址指针寄存器,常用于在访问内存时存放内存单

元的偏移地址。

BP与BX的区别:

作为通用寄存器,二者均可用于存放数据; 作为基址寄存器,用BX表示所寻找的数据在数据段;用

┇

操作数

35

状态标志位(1)

CF(Carry Flag)

进位标志位。加(减)法运算时,若最高位有进(借)位则CF=1

OF(Overflow Flag)

溢出标志位。当算术运算的结果超出了有符号数的可表达范 围时,OF=l

ZF(Zero Flag)

零标志位。当运算结果为零时ZF=1

SF(Sign Flag)

欲实现对1MB内存空间的正确访问,每个内

存单元在整个内存空间中必须具备20位字长

的惟一地址

物理地址

XXXXXH

12H

00H

内存地址变换:

…

如何将直接产生的16位编码变换

…

为20位物理地址?

┇

内存单元的编址(1)

内存每个单元的地址在逻辑上都由两部分组成:

AT89S51单片机原理及应用技术第2章

双功能引脚,ALE功能是输出端,PROG功能是输入端。 ALE功能:是为CPU访问外部程序存储器或外部数据存储器时提供低 8位地址锁存信号输出,将低8位地址信号锁存在外部的低8位地址锁存器中 。ALE信号是下降沿有效。当单片机正常运行时,不包括访问外部数据存 储器操作,ALE引脚一直有周期性正脉冲信号输出,信号频率固定为单片 机时钟振荡器频率fosc的1/6,此信号可用作外部定时或触发信号;每当单片

AT89S51单片机的主要特性参数如下: 与MCS-51系列产品完全兼容。 4K字节在系统编程(ISP) Flash存储器,承受10000次擦写周期。 4.0-6.0V的工作电压范围。 全静态工作方式:0MHz-33 MHz。 3级程序加密位。 128×8位内部RAM。 32个可编程I/O端口线。 2个16位定时/计数器。 5个中断源。 全双工UART串行口。 低功耗空闲和掉电方式。 掉电方式的中断唤醒功能。

2.1 AT89S51的内部结构及外部引脚特性

通用I/O端口:没有第三态,为准双向I/O端口。P1口作为通用I/O端口 输入时,应先向端口锁存器写入1(FFH),然后再输入(读引脚);作为 通用I/O端口输出时,P1口可驱动4个LS型TTL负载。

串行编程接口:引脚P1.5/MOSI、P1.6/MISO和P1.7/SCK(Serial Clock)可用于对片内Flash存储器串行编程和校验,分别是串行数据输入 、串行数据输出和串行移位脉冲(串行时钟)引脚。

另外,该引脚可接上备用电源,当主电源发生故障,降低到低电平 规定值或掉电时,该备用电源为片内RAM供电,以保证RAM中的数据不 会丢失。

第2章 AT89系列单片机的硬件体系结构(结构、引脚、存储器配置、专用寄存器、时钟与时序、工作方式)

2021/8/1

3

2.1 AT89系列单片机概述

2.1.1 AT89系列单片机简介

AT89系列单片机是与MCS—51系列单片机兼容 的低功耗高性能8位Flash单片机。它是在MCS-51 的技术内核为主导的基础上倾注了ATMEL公司优良 技术进行新的设计和开发,使之功能更强、更具特色, 尤其是AT89S系列单片机具有在系统可程序设计功能, 使生产维护更加方便灵活。

当CPU访问64KB的外部数据存储器时,就用

DPTR作地址指针,存放外部内存的地址;

当CPU访问64KB的程序存储器时,DPTR用作基

址寄存器。

CPU也可单独对DPH、DFra bibliotekL操作,即将DPTR分成

两个寄存器使用。

2021/8/1

21

2.3 AT89系列单片机的存储器

结构AT89系列单片机采用哈佛结构,有单独的程序存储器和

(2) 堆栈指针SP 堆栈指针SP(stack pointer)是一个8位特殊功能寄存器。

它指示出堆栈顶部在内部RAM中的位置。系统复位后,SP初 始化为07H,使得堆栈事实上由08H单元开始。考虑到08H ~1FH单元分属于工作寄存器区1~3,若程序设计中要用到 这些区,则最好把SP值改置为1FH或更大的值如60H。

处理情况。

例如:有一个单片机型号为“AT89C51—12PI”,

则表示意义为该单片机是 ATMEL公司的Flash单片

机,内部是CMOS结构,速度为12 MHz,封装为塑

封DIP,是工业用产品,按标准处理工艺生产。

2021/8/1

9

2.2 AT89系列单片机的结构原

2.2理.1 AT89系列单片机的基本组成

2021/8/1

第2章_总线及习题-

例1:执行两个数的加法,分析对标志位的影响。

0 + 0 0 0 1 1 0 1 0 0 0 0 1 1 1 0 0 0 1 0 0 0 0 1 0 1 1 0 0 0 1 1

0

1

0

1

0

1

0

1

0

1

0

1

1

1

1

0

标志: 运算结果最高位为0 运算结果本身≠0 低8位中1的个数为奇数个 最高位没有进位 第三位向第四位无进位 ∴SF=0; ∴ZF=0 ∴PF=0; ∴CF=0 ∴AF=0;

运算结果最高位为1, SF=1 ; 运算结果本身不为0, ZF=0 ; 最高位向前无进位, CF=0 次高位向最高位产生进位,而最高位向前没有进位, OF=1 ; 结果低8位含偶数个1, PF=1 ; 第三位向第四位有进位, AF=1 。 在绝大多数情况下,一次运算后并不影响所有标志, 程序也并不需要对所有的标志作全面的关注。 一般只是在某些操作后,对其中某个标志进行检测。 22

总之,“Host-PCI”桥实现了PCI 总线 的全部驱动控制,它实际上是一个高速 I/O 协处理器,主要解决I/O 设备同处理 器的连接问题。 3)另一类“桥”用于生成“多级总线” 结构,例如“PCI-ISA/EISA”、“PCIUSB”、“PCI-PCI”等。多级总线把 不同传输速度、不同传输方式的设备分 门别类地连接到各自“合适”的总线上, 使得不同类型的设备共存于一个系统中, 合理地分配资源,协调地运转。

总线的结构

1. 单总线结构: CPU与主存、CPU与I/O设备、I/O设备与主存,以 及各设备之间都通过单一的系统总线交换信息。 2. 双总线结构: A)面向CPU的双总线结构: a)CPU与主存储器之间信息交换--存储器总线; b)CPU与I/O设备之间信息交换--输入输出总线; B)面向存储器的双总线结构:高档微机 3. 多总线结构

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

保留

SPI1 TIM1时钟 ADC2 ADC1 保留 GPIO端口E APB1

0x4001 1400 - 0x4001 17FF

0x4001 1000 - 0x4001 13FF 0X4001 0C00 - 0x4001 0FFF

GPIO端口D

GPIO端口C GPIO端口B

0x4001 0800 - 0x4001 0BFF

APB总线间提供同步连接。APB1操作速度限于 36MHz,APB2工作在全速状态(最高72MHz)。

二、存储器组织

1、存储器的组织方法

程序存储器、数据存储器、寄存器和输入输出端

口被组织在同一个4GB的线性地址空间内。

数据字节以小端格式存放在存储器中。一个字中

最低地址字节被认为是该字的最低位字节,而最 高地址字节是最高位字节。

第2章 存储器与总线构架

一、系统构架

1、STM32系统包含的基本单元

四个驱动单元:

Cortex-M3内核ICode总线(I-bus)、DCode 总线 (D-bus)和系统总线(S-bus),GP-DMA(通用DMA)

三个被动单元:

内部SRAM,内部闪存FLASH存储器,AHB到APB的 桥(AHB2APBx),它连接所有的APB设备

0x4002 0400 - 0x4002 0FFF 0x4002 0000 - 0x4002 03FF

闪存存储器接口 保留 复位和时钟控制

保留 DMA AHB

0x4001 3C00 - 0x4001 3FFF 0x4001 3800 - 0x4001 3BFF

保留 USART1

0x4001 3400 - 0x4001 37FF

保留

独立看门狗 (IWDG) 窗口看门狗 (WWDG) RTC 保留 TIM4定时器 TIM3定时器 TIM2定时器

APB1

4、STM32F10X中各接口部件中的寄存器

STM32F103系列微控制器嵌入的各种接口部件 都有三大类寄存器:控制寄存器、数据寄存器和状 态寄存器,每一类寄存器都包含了多个寄存器,它 们在相同的基地址下具有不同的偏移地址。

例:TIM2定时器的基地址是:0x4000 0000

控制寄存器1的偏移地址是:00H

控制寄存器2的偏移地址是:04H 从模式控制寄存器的偏移地址是:08H DMA/中断使能寄存器的偏移地址是:0CH等

由上表述可得到它们的物理地址是:

控制寄存器1的物理地址是: 0x4000 0000 控制寄存器2的物理地址是: 0x4000 0004 从模式控制寄存器的物理地址是: 0x4000 0008

2、系统结构如下图所示

ICode总线:该总线将Cortex-M3内核的指令总线

与Flash指令接口相连接,指令预取在此总线上 完成。 DCode总线:该总线将Cortex-M3内核的DCode总 线与闪存存储器的数据接口相连接(常量加载和 调试访问)。 系统总线:此总线连接Cortex-M3内核的系统总 线(外设总线)到总线矩阵,总线矩阵协调着内核 和DMA间的访问。 DMA总线:此总线将DMA的AHB主控接口与总线矩 阵相联,总线矩阵协调着CPU的DCode和DMA到 SRAM、闪存和外设的访问。

电源控制 后备寄存器 (BKP)

保留 bxCAN USB的SRAM 256x16 位 USB寄存器 APB1

0x4000 5800 - 0x4000 5BFF

000 5400 - 0x4000 57FF

I2C2

I2C1

0x4000 5000 - 0x4000 4FFF 0x4000 4800 - 0x4000 4BFF

总线矩阵:此总线矩阵协调内核系统总线和DMA

主控总线之间的访问仲裁。此总线矩阵由3个驱 动部件(CPU的DCode、系统总线和DMA总线)和3 个被动部件(闪存存储器接口、SRAM和AHB2APB 桥)构成。

AHB外设通过总线矩阵与系统总线相连,允 许DMA访问。

AHB/APB桥(APB):两个AHB/APB 桥在AHB和2个

可访问的存储器空间被分成8个512MB的主要块,

其他所有没有分配给片上存储器和外设的存储器 空间都是保留的地址空间

2、存储器映像

(续图)

3、外设存储器映像

起始地址 0x4002 2400 - 0x4002 3FFF 外设 保留 总线 寄存器映像

0x4002 2000 - 0x4002 23FF 0x4002 1400 - 0x4002 1FFF 0x4002 1000 - 0x4002 13FF

GPIO端口A

0x4001 0400 - 0x4001 07FF

0x4001 0000 - 0x4001 03FF 0x4000 8000 - 0x4000 77FF

EXTI

AFIO 保留

0x4000 7000 - 0x4000 73FF

0x4000 6C00 - 0x4000 6FFF 0x4000 6800 - 0x4000 6BFF 0x4000 6400 - 0x4000 67FF 0x4000 6000 - 0x4000 63FF 0x4000 5C00 - 0x4000 5FFF

保留 USART3

0x4000 4400 - 0x4000 47FF

0x4000 4000 - 0x4000 3FFF 0x4000 3800 - 0x4000 3BFF

USART2

保留 SPI2

0x4000 3400 - 0x4000 37FF

0x4000 3000 - 0x4000 33FF 0x4000 2C00 - 0x4000 2FFF 0x4000 2800 - 0x4000 2BFF 0x4000 2400 - 0x4000 0FFF 0x4000 0800 - 0x4000 0BFF 0x4000 0400 - 0x4000 07FF 0x4000 0000 - 0x4000 03FF