单键触发8位二进制累加计数器

EDA实验六8位二进制全加法器的设计说明

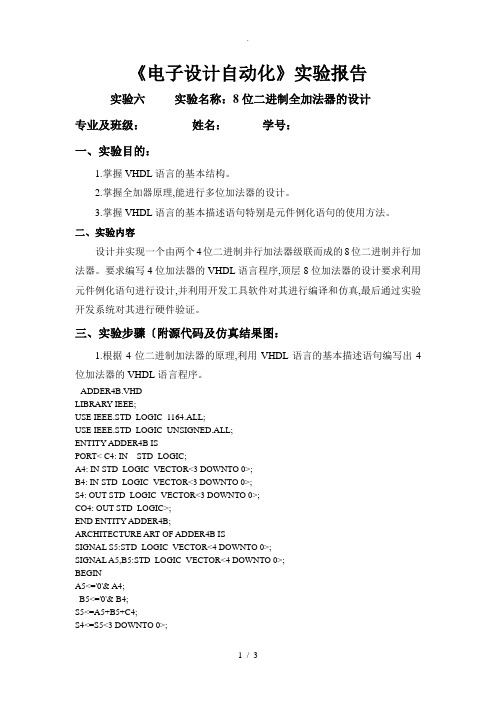

《电子设计自动化》实验报告实验六实验名称:8位二进制全加法器的设计专业及班级:姓名:学号:一、实验目的:1.掌握VHDL语言的基本结构。

2.掌握全加器原理,能进行多位加法器的设计。

3.掌握VHDL语言的基本描述语句特别是元件例化语句的使用方法。

二、实验内容设计并实现一个由两个4位二进制并行加法器级联而成的8位二进制并行加法器。

要求编写4位加法器的VHDL语言程序,顶层8位加法器的设计要求利用元件例化语句进行设计,并利用开发工具软件对其进行编译和仿真,最后通过实验开发系统对其进行硬件验证。

三、实验步骤〔附源代码及仿真结果图:1.根据4位二进制加法器的原理,利用VHDL语言的基本描述语句编写出4位加法器的VHDL语言程序。

--ADDER4B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER4B ISPORT< C4: IN STD_LOGIC;A4: IN STD_LOGIC_VECTOR<3 DOWNTO 0>;B4: IN STD_LOGIC_VECTOR<3 DOWNTO 0>;S4: OUT STD_LOGIC_VECTOR<3 DOWNTO 0>;CO4: OUT STD_LOGIC>;END ENTITY ADDER4B;ARCHITECTURE ART OF ADDER4B ISSIGNAL S5:STD_LOGIC_VECTOR<4 DOWNTO 0>;SIGNAL A5,B5:STD_LOGIC_VECTOR<4 DOWNTO 0>;BEGINA5<='0'& A4;B5<='0'& B4;S5<=A5+B5+C4;S4<=S5<3 DOWNTO 0>;CO4<=S5<4>;END ARCHITECTURE ART;2.对所设计的4位二进制加法器的VHDL程序进行编译,然后对其进行仿真,初步验证程序设计的正确性。

数电课程设计报告Quartusll软件设计环境中利用一位全加D锁存器或者D触发器实现8位二进制加法器

数学逻辑课程设计报告一、课程设计题目和要求在Quartus ll软件设计环境中利用一位全加D锁存器或者D触发器实现8位二进制加法器,将其进行功能仿真。

二、课程设计目的课程设计是培养我们学生综合运用所学知识,发现,提出,分析和解决实际问题,锻炼实践能力的重要环节,是对学生实际工作能力的具体训练和考察过程.随着科学技术发展的日新日异,数字电子技术已经成为当今计算机应用中重要的基础领域,在生活中可以说得是无处不在。

因此作为二十一世纪的大学来说掌握运用数字电子技术与逻辑电路的开发技术是十分重要的。

课程设计的目的与要求:1、了解基本的逻辑门电路。

2、在实际应用中学会实验元件的作用和工作方式。

3、提高自己的动手动脑能力,将在课堂上学到的知识应用到实际当中。

三、实验条件QUARTUS II 9.0软件、计算机四、实验设计思路1、打开QUARTUS II 9.0软件新建工程并打开作图界面。

2、按照实验要求搭好电路3、我们采用了一个74283的四位全加器,又根据题目的要求用一位的全加器因此只利用其中一位,输出输入端如图所示:4、之后我们又考虑到8位数据的存储与输出,因此我们重复使用了8次D触发器来得到八位的数据存储。

五、仿真和仿真结果1、在软件中绘制好电路图后,建立工程文件,经过编译后建立波形文件。

在波形文件中设置参数,时间为区域设为10ns。

下图为该电路实验在RTL viewer下的电路示意图。

2、功能仿真结果图:六、实验的不足在实验设计的过程中,由于对软件的使用和操作不是太熟练由此而导致一些问题的不断产生,电路的输入也不是规则有序的输入信号,因此只能实现以上的试验结果,初步的达到了本次课程设计的实验要求。

七、心得体会通过这次课程设计,加强了我们动手、思考和解决问题的能力。

在整个设计过程中,我们通过这个方案包括设计了一套电路原理和了解芯片的选择。

回顾起此次数字电子技术课程设计,至今我仍感慨颇多,的确,从查资料到定稿,从理论到实践,在设计过程中,经常会遇到这样那样的情况,就是心里想老着这样的接法可以行得通,但实际接上电路,总是实现不了,因此耗费在这上面的时间用去很多。

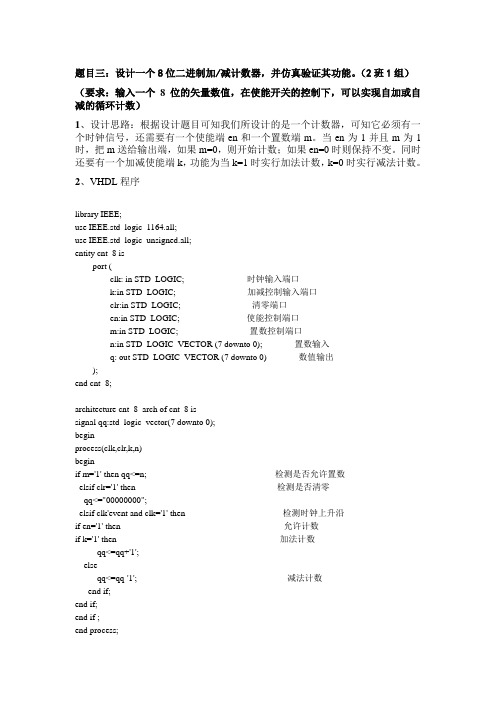

实验二8位二进制加减可控计数器设计

实验二8进制加减可控计数器设计一、实验目的1.学习时序电路的设计,仿真和硬件测试,进一步熟悉VHDL设计技术。

2.学习使用SignalTap的使用方法。

3.学习用AS模式下对配置器件的编程。

二、实验内容1.参考书中4-22,设计一个异步清零和同步时钟使能的十进制加法计数器,在QuartusⅡ上进行编辑、编译、综合、适配、仿真。

给出其所有信号的时序仿真波形。

引脚锁定后进行编译、下载和硬件测试实验。

2.使用SignalTap II对此计数器进行实时测试,保存波形。

3.从设计中去除SignalTap II,要求全程编译后生成用于配置器件EPCS1编程的压缩POF文件,并使用ByteBlasterII,通过AS模式对实验板上的EPCS1进行编程,最后进行验证。

4.设计含有异步清零和同步时钟使能的8进制加减可控计数器。

并完成硬件测试。

一般加法计数器的设计参照书本例4-22。

异步清零表示只要清零信号有效,计数器输出为某个特定的值(比如00H),计数器使能表示只有该信号有效时,才开始计数,其他时候停止计数。

另外加减控制线来控制计数器是加还是减。

三、实验报告将实验原理、设计过程、编译仿真波形和分析结果写进实验报告。

四、实验步骤1.创建工程在D盘中新建一个文件夹D:\ cnt10,此文件夹用于存放整个工程。

打开Quartus II 7.2,在菜单中选择File—〉New Project Wizard 将会出现一个信息框,这个对话框介绍创建工程步骤,可以直接选Next,这时会出现如图1所示的对话框。

这里需输入的是欲创建工程的基本信息,三个输入栏中分别输入的是工程将被保存的路径及工程文件夹、工程的名称和顶层实体的名称。

建议工程名与顶层实体名称保持一致。

输入完毕我们就可以点击Next。

图1 新建工程基本信息对话框然后出现图2所示的添加工程文件对话框。

在这里需要做的是将已经写好的VHDL文件加入到工程中。

本次实验,可以直接点击Next,以后再添加VHDL 文件的工作。

八位二进制累加器

摘要随着社会的发展,在生活和生产中,我们经常要用到二进制累加问题,为了提高运算速度,更大的节约时间,所以我做了这个八位二进制累加器来进行二进制的累加,主要内容为加法器和寄存器及一些简易的电容电阻等器件,来实现八位二进制的累加问题,这样就可以把复杂的问题具体化,从而提高生产与学习效率,极大地节约时间。

关键词:二进制累加器目录一.课题名称……………………………………………………………二.主要功能(简要说明) ………………………………………………三.电路原理图…………………………………………………………四. 工作原理分析………………………………………………………1.电路组成…………………………………………………………2.单个元器件性能…………………………………………………五. 整体电路工作原理及EDA仿真和结果分析:……………………六. 元器件选择(元器件明细表和参考价格,电路成本估算)……七.电路的制作与实验测试……………………………………………1.电路排布…………………………………………………………2.电路焊接…………………………………………………………3.电路的检查及测试………………………………………………4.调试结果…………………………………………………………八.线路的改进意见:……………………………………………………九.思考题………………………………………………………………十.课程设计的收获和体会………………………………………………十一.参考文献……………………………………………………………一.课题名称:8位二进制累加器二.主要功能(简要说明):该电路将K3,K4设定的8位二进制数与74LS273中锁存的数相累加,并将结果通过发光二极管D1~D8显示出来。

K1为累加键,每按以此累加一次。

K2为清零键,用于将累加和清零。

三.电路原理图:V四. 工作原理分析1、电路组成:如图1所示,整个电路由一个8位高速寄存器、两个4位二进制全加器及一些电阻、电容、发光二极管组成,实现8位二进制累加器的功能。

8位二进制加法计算器

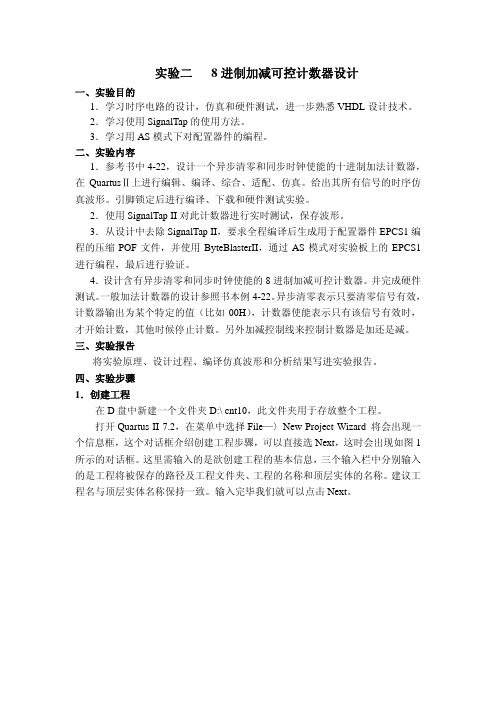

一:本实验设计的是一个8为二进制加法计算器,其功能就是对两个八位的二进制数执行加法运算,并可以异步清零。

二:电路可划分为三部分:半加器、全加器和复位电路。

1、半加器:真值表a b so co0 0 0 00 1 1 01 0 1 01 1 0 1电路图2全加器:由半加器和或门组成电路图3复位电路:复位电路通过en控制,当en为‘1’时,执行加法运算,输出正确的值,当en为‘0’时,输输出及结果为全0.三:实验波形仿真和VHDL1、仿真图:2、VHDL代码1)半加器h_adder:library ieee;use ieee.std_logic_1164.all;entity h_adder isport (a,b :in std_logic;co,so :out std_logic);end entity h_adder;architecture fh1 of h_adder isbeginso <= not(a xor (not b));co <= a and b ; end architecture fh1;2)或门or2a:library ieee;use ieee.std_logic_1164.all;entity or2a isport (a,b :in std_logic;c: out std_logic);end entity or2a;architecture one of or2a isbeginc <= a or b ;end architecture one;3)全加器f_adder:library ieee;use ieee.std_logic_1164.all;entity f_adder isport (ain,bin,cin:in std_logic;cout,sum:out std_logic);end entity f_adder;architecture fd1 of f_adder iscomponent h_adderport (a,b :in std_logic;co,so :out std_logic);end component;component or2aport (a,b :in std_logic;c: out std_logic);end component;signal d,e,f: std_logic;beginu1:h_adder port map(a=>ain,b=>bin,co=>d,so=>e);u2:h_adder port map(a=>e,b=>cin,co=>f,so=>sum);u3: or2a port map(a=>d,b=>f,c=>cout);end architecture fd1;4)与门and2a:library ieee;use ieee.std_logic_1164.all;entity and2a isport (a,b :in std_logic;c: out std_logic);end entity and2a;architecture one of and2a isbeginc <= a and b ;end architecture one;5)顶层设计文件library ieee;use ieee.std_logic_1164.all;entity zong isport (a1,a2,a3,a4,a5,a6,a7,a8,b1,b2,b3,b4,b5,b6,b7,b8,en :in std_logic;solution1,solution2,solution3,solution4,solution5,solution6,solution7,solution8,solution9 :out std_logic );end entity zong;architecture fh1 of zong iscomponent h_adderport (a,b :in std_logic;co,so :out std_logic);end component;component f_adderport (ain,bin,cin:in std_logic;cout,sum:out std_logic);end component;component and2aport (a,b :in std_logic;c: out std_logic);end component;signale2,e3,e4,e5,e6,e7,e8,e9,e10,e11,e12,e13,e14,e15,e16,e17,e18,e19,e20,e21,e22,e23,e24 :std_logi c;beginu1:and2a port map(a=>en,b=>a1,c=>e2);u2:and2a port map(a=>en,b=>a2,c=>e3);u3:and2a port map(a=>en,b=>a3,c=>e4);u4:and2a port map(a=>en,b=>a4,c=>e5);u5:and2a port map(a=>en,b=>a5,c=>e6);u6:and2a port map(a=>en,b=>a6,c=>e7);u7:and2a port map(a=>en,b=>a7,c=>e8);u8:and2a port map(a=>en,b=>a8,c=>e9);u9:and2a port map(a=>en,b=>b1,c=>e10);u10:and2a port map(a=>en,b=>b2,c=>e11);u11:and2a port map(a=>en,b=>b3,c=>e12);u12:and2a port map(a=>en,b=>b4,c=>e13);u13:and2a port map(a=>en,b=>b5,c=>e14);u14:and2a port map(a=>en,b=>b6,c=>e15);u15:and2a port map(a=>en,b=>b7,c=>e16);u16:and2a port map(a=>en,b=>b8,c=>e17);u17:h_adder port map(a=>e2,b=>e10,co=>e18,so=>solution1);u18:f_adder port map(ain=>e3,bin=>e11,cin=>e18,cout=>e19,sum=>solution2);u19:f_adder port map(ain=>e4,bin=>e12,cin=>e19,cout=>e20,sum=>solution3);u20:f_adder port map(ain=>e5,bin=>e13,cin=>e20,cout=>e21,sum=>solution4);u21:f_adder port map(ain=>e6,bin=>e14,cin=>e21,cout=>e22,sum=>solution5);u22:f_adder port map(ain=>e7,bin=>e15,cin=>e22,cout=>e23,sum=>solution6);u23:f_adder port map(ain=>e8,bin=>e16,cin=>e23,cout=>e24,sum=>solution7);u24:f_adder port map(ain=>e9,bin=>e17,cin=>e24,cout=>solution9,sum=>solution8);end architecture fh1;。

8位二进制加减计数器

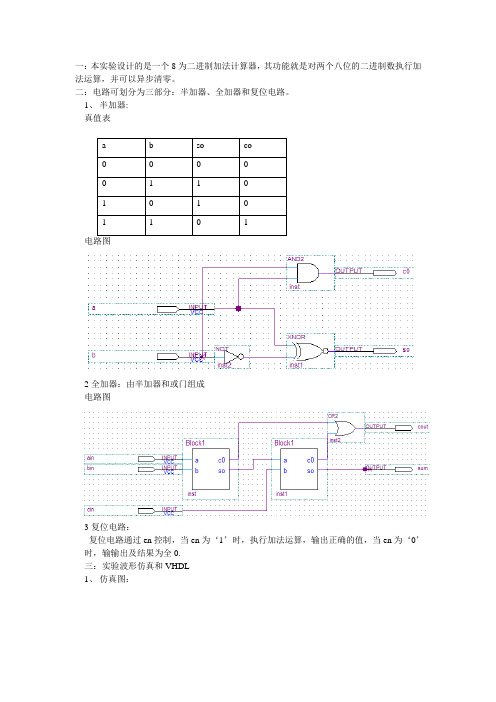

题目三:设计一个8位二进制加/减计数器,并仿真验证其功能。

(2班1组)(要求:输入一个8位的矢量数值,在使能开关的控制下,可以实现自加或自减的循环计数)1、设计思路:根据设计题目可知我们所设计的是一个计数器,可知它必须有一个时钟信号,还需要有一个使能端en和一个置数端m。

当en为1并且m为1时,把m送给输出端,如果m=0,则开始计数;如果en=0时则保持不变。

同时还要有一个加减使能端k,功能为当k=1时实行加法计数,k=0时实行减法计数。

2、VHDL程序library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;entity cnt_8 isport (clk: in STD_LOGIC; --时钟输入端口k:in STD_LOGIC; --加减控制输入端口clr:in STD_LOGIC; --清零端口en:in STD_LOGIC; --使能控制端口m:in STD_LOGIC; --置数控制端口n:in STD_LOGIC_VECTOR (7 downto 0); --置数输入q: out STD_LOGIC_VECTOR (7 downto 0) --数值输出);end cnt_8;architecture cnt_8_arch of cnt_8 issignal qq:std_logic_vector(7 downto 0);beginprocess(clk,clr,k,n)beginif m='1' then qq<=n; --检测是否允许置数elsif clr='1' then --检测是否清零qq<="00000000";elsif clk'event and clk='1' then --检测时钟上升沿if en='1' then --允许计数if k='1' then --加法计数qq<=qq+'1';elseqq<=qq-'1'; --减法计数end if;end if;end if ;end process;process(qq)beginq<=qq; --将计数值向端口输出end process;end cnt_8_arch;3、仿真波形(图片)4、程序分析:在程序设计中,当置数控制端口fr为高电平时,允许为该计数器置初值,把置数端口yz的值附给计数器,即高电平时有效。

第十三章 1 8位并行预置加法计数器设计 VHDL语言 教学课件 ppt

四位二进制并行加法器的设计思想:

(1)将加数A、被加数B、和S扩展成5位, 即将加数、被加数、和与0相并置,运算之后分 别为AA,BB,SINT;

(2)按照全加器的方法将并置运算后的加数、 被加数和接收低位进位相加赋值给并置运算后的 和,即SINT<=AA+BB+CIN,其中CIN为接收低位 进位输入端;

THEN—ELSE语句结构,使得很容易地实 现了nmi、float、int和peripheral 4个中断 请求信号的能按优先顺序分别进行处理, 程序中使用了类属语句,使此中断处理器 可根据实际情况容易地改变地址位宽;程 序中还使用了数据类型转换函数 CONV_STD_LOGIC_VECTOR(X,Y)。

例13-4:文件名:stack.vhd LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity stack is generic(n:INTEGER:=8;

——堆栈元素的字长 k:INTEGER:=8);

程序中有两个进程,一个是数据写入进程 WRITE,该进程设置条件为wr=’0’的 IF_THEN不完整的条件语句,锁存器阵列, wr作为锁存控制信号,当wr=’0’时,在满足 条件(cs=’0’ and rd=’1’)时将外部8位数据din 锁进指定地址adr的RAM单元中;而当满足

条件(rd=’0’ and cs=’0’ and wr=’1’)时, 此SRAM将指定地址adr的RAM单元中的数 据向dout端口输出,否则该端口呈高阻态。

数据的重要器件,它由锁存器阵列构成,它的 界面端口由地址线、数据输入线、数据输出线、 片选线、写入允许线和读出允许线组成。

8位二进制加法器

《电子技术》课程设计报告题目学院(部)专业班级学生姓名学号月日至月日共周指导教师(签字)前言8位二进制加法器,它的功能主要是实现两个8位二进制数的相加,其结果的范围应该在00000000到111111110之间,即000到510之间。

加法器在实际应用中占据着十分重大的地位,从我们呱呱坠地起,到小学,到初中,到高中,到大学,到工作,等等。

我们能离开加法吗,不能!加法可以说是一切运算的基础,因此8位二进制加法器的设计是很有必要的。

那么我们如何设计一个8位二进制加法器呢?在实际应用中,我们通常输入的是十进制数,一个八位二进制数所对应的最大的十进制数是255,于是输入两个范围在000到255之间的数,首先通过二-十进制编码器将输入的三位十进制数的个位、十位、百位分别转换为8421BCD码,得到两个十二位字码,再通过加法器将它们相加,逢10进1,得到一个新的十二位字码,再用7447数字显示译码器将这个十二位字码还原到原来的三位十进制数。

最后输出的就是一个三位十进制数,其范围在000到510之间。

通过上述方法我们实现了八位二进制数的相加,从而达到了题目的要求。

为实现上述目的,我们需要查阅相关资料。

通过查阅,理解以及加以运用,我们认识到了收集资料的不易性,但同时也得到了不少收获,可以说是有苦有甜。

同时,虽然我们基本设计出了这个八位二进制加法器,但是不必可避免地会产生一些问题,比如说在连线上可能有更简便的途径,在元件的选用上可能还有其它更简便的方法,在控制上可能还不够精简,等等。

我们希望在以后的实践中能找出更好的方法,也希望能吸取这次设计中的不足,逐渐改善。

另外,在电子设计的过程中,与同组同学之间的合作配和是十分重要的。

我在此次设计中也充分认识到这一点的重要性,我相信这次的电子设计能够为我们将来的工作奠定一定的基础。

目录1.摘要 (1)2.关键字 (1)3.设计要求 (1)4.正文 (1)第一章.系统概述 (1)第二章.单元电路设计与分析 (4)①.控制电路 (4)②.编码电路 (5)③.加法电路 (6)④.译码电路 (10)⑤.输出电路 (11)第三章.系统综述、总体电路图 (11)第四章.结束语 (14)5.鸣谢 (15)6.元器件明细表,附图 (15)7.参考文献 (16)8.收获与体会,存在的问题等 (17)9.评语 (18)8位二进制加法器1.摘要:本次设计主要是如何实现8位二进制数的相加,即两个000到255之间的数相加,由于在实际中输入的往往是三位十进制数,因此,被加数和加数是两个三位十进制数,范围在000到255之间,通过六个二-十进制编码器(即74LS147)分别将加数和被加数的个位、十位、百位转换为8421BCD码,于是得到了两个12位字码,将它们接入三个四位超前进位并行加法器(即74LS283),其中原加数三位十进制数的个位转换得到的四位BCD码与被加数三位十进制数的个位转换得到的四位BCD码相加,串入到第一个74LS283的接线端,得到一个四位8421BCD码。

8bit 符号数加法器

8bit符号数加法器一、概述8bit符号数加法器是一种用于实现两个8位二进制数相加的硬件或软件设备。

在数字电路和计算机编程中,这种加法器对于各种应用和计算任务非常有用。

二、设计原理符号数加法器基于二进制数的加法原理进行设计。

当两个二进制数相加时,我们需要考虑的是每一位上的数值相加的结果,以及最高位的进位问题。

对于负数,我们还需要考虑到符号位的问题。

为了处理这些情况,符号数加法器设计为可以识别输入数字的符号,并根据不同的符号采取不同的加法策略。

三、硬件实现8bit符号数加法器的硬件实现方法多种多样,具体实现方式取决于所使用的硬件平台和设计要求。

常见的实现方式包括微处理器、FPGA(现场可编程门阵列)以及其他数字逻辑设备。

微处理器通常具有专门的硬件模块或软件算法来实现加法运算,而FPGA则允许根据需要进行自定义设计。

在FPGA实现中,可以使用计数器或寄存器来存储输入数字的数值位,以及查找表来存储输入数字的符号位。

此外,可能需要使用额外的逻辑和寄存器来处理溢出和下溢情况。

四、软件实现8bit符号数加法器的软件实现方法也很多样化,具体实现方式取决于所使用的编程语言和设计要求。

常见的编程语言如Python、C++、Java等都可以方便地实现这个功能。

在软件实现中,可以通过编写程序代码来实现8bit符号数加法器的功能,并进行相应的测试和验证。

五、应用场景8bit符号数加法器可以应用于各种数字系统和计算机编程模型中,例如数字信号处理、嵌入式系统、游戏开发、人工智能等。

它提供了高效、可靠的数字运算功能,对于这些应用中的计算任务至关重要。

除此之外,它还可以用于数据校验、加密解密、科学计算等领域。

六、总结8bit符号数加法器是一种重要的数字电路组件,它能够将两个8位的二进制数相加,并对负数的符号进行特殊处理。

通过不同的硬件和软件实现方法,我们可以方便地设计和使用这个加法器。

它的应用范围广泛,为各种数字系统和计算任务提供了有力的支持。

八位二进制累加器的设计

输入电压V=5V时,当Cin=1,A=1,B由0->1变化时,用计算器中的delay函数测得此最坏下降延时(对于Sum来说,此时相当于最坏的上升延时)如图所示。由图可知,Sum最坏的上升延时为484.14ps;而Sum_layout最坏的上升延时。所以,版图仿真的最坏上升延时比原理图仿真的最坏延时小79.1ps。

图七Cin=1,A=1,B由0->1时功耗的波形

(2)最坏的下降延时分析

下面利用瞬态分析,测量Cin=0,A=0,B由1->0变化时的延时情况。如下图所示,是该情况下的输入输出波形。

图八Cin=0,A=0,B由1->0时,输入输出波形

用计算器中的delay函数测得此时的最坏上升延时(对于Sum来说,此时相当于最坏的下降延时)如图九所示。由图可知,最坏的下降延时为528.98ps

aபைடு நூலகம்组内并行,组间串行的进位链

b)组内并行,组间并行的进位链

它们的目的就是要进位信号的产生尽可能的快,因此产生了二重进位链或更高重进位链,显然进位速度的提高是以硬件设计的复杂化为代价来实现的。

(3)串行加法进位

串行加法进位从最低位进到最高位,即整个进位是分若干步骤进行的。

优点:具有器件少、成本低、电路结构简单的优点。缺点:运算速度慢。

正电平触发式触发器的状态在CP=1期间翻转,在CP=0期间保持不变。电平触发式触发器的缺点是存在空翻现象,通常只能用于数据锁存。

(2)主从触发器:

主从触发器由分别工作在时钟脉冲CP不同时段的主触发器和从触发器构成,通常只能在CP下降沿时刻状态发生翻转,而在CP其他时刻保持状态不变。它虽然克服了空翻,但对输入信号仍有限制。

八位二进制加法计数器设计

八位二进制加法计数器设计目录一、设计目的和要求 (1)1.课程设计目的 (1)2.课程设计的基本要求 (1)3.课程设计类型 (1)二、仪器和设备 (1)三、设计过程 (1)1.设计内容和要求 (1)2.设计方法和开发步骤 (2)3.设计思路 (2)4.设计难点 (4)四、设计结果与分析 (4)1.思路问题以及测试结果失败分析 (4)2.程序简要说明 (5)五、心得体会 (11)六、参考文献 (12)一、设计目的和要求1.课程设计目的设计一个带进位的八位二进制加法计数器:要求在MAX+plusⅡ10.2软件的工作平台上用VHDL语言层次设计出一个带进位的八位二进制加法器,并通过编译及时序仿真检查设计结果。

2.课程设计的基本要求全加器与带进位输入8位加法器设计要求我们通过8位全加器的设计掌握层次化设计的方法,充分理解全加器的设计过程,掌握一位全加器的程序,熟悉MAX+plusⅡ10.2软件的文本和原理图输入方法设计简单组合电路。

课程设计过程中要求能实现同步和异步的八位二进制全加器的设计。

3.课程设计类型EDA课程设计二、仪器和设备PC机、MAX+plusⅡ10.2软件三、设计过程1.设计内容和要求方法一:1.原理图输入完成半加器和1位全加器的设计,并封装入库2.层次化设计,建立顶层文件,由8个1位全加器串联构成8位全加器3.每一层次均需进行编译、综合、适配及仿真方法二:1. 原理图输入完成一个四位全加器的设计2.层次化设计,建立顶层文件,由2个4位全加器串联构成8位全加器3.每一层次均需进行编译、综合、适配及仿真2.设计方法和开发步骤加法器是数字系统中的基本逻辑器件。

例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。

但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

单片机八位二进制

编号:单片机应用实训说明书2011年12月30日摘要单片机已被广泛地应用在工业自动化控制、自动检测、智能仪表、家用电器等各个方面。

在现代工业控制和一些广告设计领域中,越来越多的场所需要用到LED点阵显示系统设计。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

关键词:单片机;计数器AbstractSCM has been widely applied in industrial automation control, automatic detection of intelligent instruments, home appliances and other aspects. In the modern industrial control and some advertising design field, more and more places need to use of LED dot matrix display system design. The counter in digital system is used widely, such as in the electronic computer controller for instructions address in the count, in order to take out the next instruction sequence, the unit in multiplication, division operation down when the addition, subtraction, times, and as in digital instrument to the count of the pulse, etc.Keywords: SCM; counter引言20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

用GAL设计八位二进制可逆同步计数器

第20卷第4期西安工业学院学报V ol120No14 2000年12月JOU RN AL OF XI p AN IN ST IT U T E OF T ECHN OL OGY Dec12000用GAL设计八位二进制可逆同步计数器X田军委,李少康,王建华,李平(西安工业学院机械工程系,陕西西安710032)摘要:介绍了可编程逻辑器件P LD的主要器件)通用阵列逻辑G AL的结构特点和主要性能特点,并阐述了用GA L设计八位二进制可逆同步计数器的方法.同时介绍一种通用逻辑设计软件)CU PL语言.文中着重介绍了八位二进制可逆同步计数器的功能特点及其用GAL设计的方法.这对于经常使用GAL进行数字系统设计的同行,具有较大的借鉴意义.关键词:可编程逻辑器件;八位二进制可逆同步计数器;CU PL语言;宏定义中图号:T P27412文献标识码:A文章编号:1000-5714(2000)04-0322-05The design of eigh-t bit binary reversible synchronouscounter with GAL deviceTIAN Jun-w ei,L I Shao-kang,WANG Jian-hua,L I p ing(Dept of M ech Engr,Xi p an Inst of T ech,Xi p an710032,China)Abstract:T he characteristics of the structur e and the performance of major dev ices of the programmable log ic device)))the generic array log ic(GAL)device are introduced.T hen the method of using GAL to desig n the eig ht-bit binar y reversible synchronous counter and a kind of logic design softw are)))CU PL language ar e also intro duced.It can be used as a r eference fo r the people w ho often use PL D to improve their dig ital system design.Key Words:programmable log ic device;eight-bit binary r eversible synchronous counter;CU PL languag e;macro definition引言CNC齿轮测量中心是80年代发展起来的机电结合的新型齿轮量仪,其位移传感器一般选用光栅尺,齿轮测量中心的精度主要取决于光栅尺的刻线密度和光栅读数头输出信号的后继处理.本文主要介绍西安工业学院测量与控制技术研究所研制的CNC齿轮测量中心光栅计X收稿日期:2000-06-16作者简介:田军委(1973-),男(汉族),西安工业学院助教,从事计算机辅助测试研究.数卡的构成及用GAL 器件设计八位二进制可逆同步计数器的方法.1 光栅计数卡的构成光栅计数卡主要由预处理电路、计数电路、锁存器和CAMAC 总线组成.预处理电路主要对相差90b 的方波进行四倍频处理和鉴向处理.光栅读数头输出的信号经EXE110倍频器倍频,输出两路相差90b 的方波,预处理电路将这两路信号转化为四倍频单波和方向信号输入计数电路,计数电路对四倍频方波进行可逆计数,计数方式由方向信号控制.计数电路计数值经锁存器通过CAMAC 总线送入计算机处理.计数电路还具备同步置数和异步清零功能,所置数值经过由计算机通过CAMAC 总线经锁存器置入,清零功能根据清零信号由计数电路异步清零.其结构框图如图1.图1 光栅计数卡结构图光栅计数卡预处理电路采用C5194来实现四倍频和鉴向,计数电路主要由八位二进制可逆同步计数器74AS867组成,但目前国内市场上74系列集成电路最高编号仅到688,购买74AS867必须从美国德州仪器等公司进口,订购周期长,价格昂贵,不符和电路设计经济性原则.近年来,PLD 器件以其设计灵活性受到广大用户的欢迎,因此作者用PLD 的一种)))GAL (Generic Array Logic)器件来设计八位二进制可逆同步计数器.2 GAL22V 10管脚定义74AS867为可预置数的八位二进制可逆同步计数器,对单脉冲同步加减计数,有同步并行置数和异步清零功能,其计数功能由计数使能控制端ENT 、ENP 控制,当二者均为底电平时允许计数,否则保持上一次计数值,867置数、输出均采用并行方式.图2 引脚定义本文设计的八位二进制可逆同步计数器,除并行输入输出引脚外,还需要脉冲输入、计数使能、进位位、功能选择五个端口,总计12个输入端口,9个输出端口,因此选择GAL22V10来实现本设计.GAL22V10是常用的GAL 器件之一,它共有10个输入输出宏单元,可实现组合逻辑输出或寄存器输出,最多可提供10路输入输出和12路输入,可满足本设计对输入输出的要求.本设计所选的GAL22V10各引脚定义如图2.D 0~D 7 并行数据输入Q 0~Q 7并行数据输出EN记数使能,为0时允许记数CP时钟输入RC 0进位输出323第4期 田军委等:用GA L 设计八位二进制可逆同步计数器324西安工业学院学报第20卷S0、S1功能选择,其功能如表1所示下面根据此定义采用CUPL语言实现上述功能.3CU PL语言源程序设计CUPL通用开发软件出现于80年代中期,属于编译类软件,其语言结构类似于C语言,可读性好,与其他语言相比,CU PL语言通用性更强,并且有很强的模拟功能,便于用户通过软件来检验设计逻辑是否合理.目前流行的电子设计软件Protel98、Protel99、Protel2000中,PLD 设计部分均采用CUPL语言,这些软件把程序格式模板化,加强了CU PL语言宏定义功能,使输出形式灵活多变,便于用户根据自己的需求选取,本文使用的CU PL语言即在Protel98环境下运行.3.1设计思想该八位二进制可逆同步计数器由时钟脉冲触发来计数、置数,对数据有保持功能,计数器的下一状态和当前状态有关,故采用寄存器输出形式,使输出由时钟脉冲触发而变化.在各种寄存器中,D触发器输入输出关系最为简单,因而输出宏定义为D触发器输出.74AS867通过ENT、ENP两个引脚来控制计数功能,实际应用中这两个管脚常常短接,因此,本设计用一位计数使能端EN控制计数器计数或保持.清零和置数功能与EN状态无关.控制引脚具体功能如表1.表1GAL计数器功能表功能S0S1EN=0EN=100清零清零01置数置数10减计数保持11加计数保持此前有些工程人员用GAL器件设计出四位可逆同步计数器,其实现方法为:每一位的状态由前边各位状态决定,逻辑式中列出所有可能情况.这种设计下,各逻辑式组成无太大差别.但对本次设计而言,由于所设计计数器为八位,若采用逐位加减设计,高几位的/或0项会超过八项,超过GAL器件对/或0项的最大要求.用这种方法设计的八位计数器的第六位计数逻辑式为D6.D=!EN&(S0&S1&D0&D1&D2&D3&D4&D5&!D6 #S0&!S1&!D0&!D1&!D2&!D3&!D4&!D5&!D6) CUPL语言在编译此式时将/与非0项当作/或0项来处理,这样,上式就有九个/或0项,若加上其他功能,/或0项就远超过八项.但低位逻辑式相对要简单的多,如最低位表达式为D0.D=!S0&am p;S1&Q0#EN&(S0&!D0)#!EN&D0&!(!S0&S1)逻辑式中仅含三个/或0项,资源远未用尽.在这种情况下,如果选用新一代GAL器件GAL39V18,该方法就可完成设计,但低位资源将会大量浪费.本文提出分块设计方案.分块设计思想在软件设计和大型硬件系统设计中应用较为广泛,其设计思想是把复杂的工作分解为若干个相对简单的工作来完成,这主要从分工角度来考虑,作者对其赋以新的思想)))从资源分配角度来对系统进行分解.基于这一思想,作者模仿硬件设计,用两个低位计数器设计一个高位计数器.经过反复试验,用低五位可逆同步计数器和高三位可逆同步计数器组合成八位可逆同步计数器,低五位计数器进位值赋给中间节点Z0,Z0将资源/转借0给高三位,高三位根据Z0来确定翻转或保持,从而使逻辑式得以化简,满足GAL 对/或0项的要求.以往用GAL 设计的可逆计数器中,清零功能由清零端和各位直接相/与0来实现,八位二进制可逆同步计数器的清零也可用!(S 0#S 1)项和各位/与0来实现,这种方法不但增加/或0项,使逻辑式复杂,而且仅能实现同步清零,不符和设计要求,因此作者没有采用这种设计方法,而采用了CUPL 语言的.AR 宏,计数器每一位在.AR 宏作用下,即时响应清零信号,无须等待时钟脉冲的到来,这样,无论计数器有无CP 信号输入,只要有清零信号,计数器即可马上清零.同样,对于保持功能,作者没有采用传统方法直接在每一位后/与0上控制信号,而是在每位逻辑式后加一/或0项(!EN&Di&am p;!(!S0&S1)),当EN=0且非置数功能时,计数器保持最后计数结果.将上述逻辑功能有机结合起来,对逻辑式进行简单化简就可得出各位逻辑表达式,据此可以编写CUPL 语言源程序.3.2 CU PL 语言源程序源程序由程序首部、引脚定义、逻辑表达式、程序说明等四部分组成.程序首部按固定格式编写,包含设计者、设计日期、所用器件、版本号等设计信息;引脚定义部分根据设计要求定义GAL 器件各引脚的功能和符号;逻辑表达式部分用CUPL 语法描述各输出脚逻辑赋值条件;说明部分主要说明各部分功能、实现条件以及注释语句.这几部分中,逻辑表达式部分是设计的核心,由于篇幅限制,本文仅给出逻辑表达式部分的描述.首先是低五位可逆计数器的设计.低五位采用传统的可逆计数器设计方法,每一位表达式包含所有赋值条件,包括计数、置数等全部功能,其逻辑表达通式如下Di.D=!S0&S1&Q i#EN&(S0&S1&D0&,&D (i-1)&!Di#S0&S1&!(D0&,&D(i-1))&Di#S0&!S1&(D0#,#D(i-1))&Di #S0&!S1&!(D0#,#D(i-1))&!Di)#!EN &Di&!(!S0&S1) (0<i<5)D0.D =!S0&S1&Q 0#EN &(S0&!D0)#!EN &D0&!(!S0&S1) (i=0)设计完低五位可逆计数器并给出Z0逻辑式后就可以设计高三位可逆计数器.高三位根据Z0的值及其下各位状态以及控制位、功能位状态来变化.加计数时,如果其下相邻一位至第六位均为1,当Z0=1时,该位发生跳变,否则保持;减计数时,如果其下相邻一位至第六位均为0,当Z0=1时,该位发生跳变,否则保持.其逻辑表达通式如下:Di.D=!S0&S1&Q i #EN &(S0&S1&Di&!(D5&,&D(i-1)&Z0)#S0&325第4期 田军委等:用GA L 设计八位二进制可逆同步计数器326西安工业学院学报第20卷S1&!Di&D5&,&Di(i-1)&Z0#S0&!S1&Di&(D5#,#D(i-1)#!Z0)#S0&!S1&! Di&!(D5#,#D(i-1)#!Z0))#!EN&Di&!(!S0&S1)(8>i&g t;5)D5.D=!S0&S1&Q5#EN&(S0&S1&D5&!(zo)#S0&S1&!D5&Z0#S0&!S1&D5&(!Z0)#S0&!S1&!D5&!(!Z0))#!EN&D5&!(!S0&S1)(i=5)根据以上描述写出各位逻辑表达式,加上其他部分就得出完整源程序,该程序编译后就产生GAL器件的熔丝图.逻辑表达式在编译时由系统自动化简,编译后产生标准JEDEC文件,此文件写入GAL22V10即可实现所要求的功能.CUPL语言也支持基于逻辑图的PLD设计,作者曾试着用两个四位可逆计数器来搭接八位计数器,结果同样遇到了GAL资源不足的情况,最后,作者选择了5+3的结构模式,这种模式使GAL22V10的资源分配比较合理.4结束语作者在设计时选用响应为15ns的GAL器件,实现了上述全部功能,并将所设计器件成功的应用于CNC齿轮测量中心光栅计数卡中,该计数卡在应用中性能稳定,其响应甚至高于原使用74AS867的计数卡.参考文献:[1]周永钊.通用逻辑阵列(GAL)[M].合肥:中国科学技术大学出版社,1989[2]艾明晶.用可编程器件取代BCD-二进制转换器的设计[J].测控技术,2000,19(3):54[3]宋俊德,新德禄.可编程逻辑器件(PLD)原理与应用[M].北京:电子工业出版社,1994[4]居悌.可编程逻辑器件的开发与应用[M].北京:人民邮电出版社,1995[5]李平.CN C测量中心光栅数据输入通道设计[J].西安工业学院学报,1996,16(3):221。

8位二进制数加法

《8 位二进制数加法》

小朋友们,今天咱们来一起了解一个有点神奇的东西,叫做8 位二进制数加法。

你们可能会想,这是个啥呀?其实呀,它就像是一个特别的数学游戏。

咱们平常做加法,比如1+1=2,这很简单对吧。

那在二进制的世界里呢,也有加法。

先来说说什么是二进制。

咱们平常数数是0、1、2、3、4……在二进制里,就只有0 和 1 这两个数字。

那8 位二进制数呢,就是一共有8 个位置,每个位置上要么是0,要么是1。

比如说00000001 就是一个8 位二进制数。

咱们来做个加法。

比如00000001 加上00000001 。

从右边开始加,1+1 等于10,这里的10 可不是咱们平常说的十哦,在二进制里,就要往左边进位,右边写0 ,左边进位变成00000010 。

再举个例子,00001010 加上00000101 。

同样从右边开始,0 + 1 = 1 , 1 + 0 = 1 ,1 + 1 = 10 ,进位,继续这样加下去,最后就得到结果啦。

二进制数加法在计算机的世界里可重要啦。

计算机可不认识咱们平常的数字,它就靠二进制来工作。

就好像计算机是一个特别聪明的小机器人,它只能看懂0 和 1 ,通过这些

8 位二进制数加法,它就能帮我们做很多很多事情。

比如说,我们在手机上玩游戏、听音乐,背后都有计算机在快速地做着这样的加法呢。

小朋友们,虽然8 位二进制数加法有点复杂,但只要我们多练习,多想想,就能慢慢明白啦。

好啦,关于8 位二进制数加法就跟大家说到这儿,希望你们能越来越聪明,学会更多有趣的知识!。

8位二进制计数器

“数字逻辑设计及应用”课程设计

题目

8位二进制计数器设计

要求

加减控制信号为1时,加计数;0时,减计数。

使能控制信号为1时,停止计数,并将当前计数值设置为输入值;使能控制信号为0时,计数器按照加减控制信号工作。

写出Verilog代码,给出仿真波形。

思路方法

1、根据要求可知输入信号有一位使能信号,一位加减控制信

号,八位计数初值和时钟信号;而输出则是八位输出计数值。

2、设计过程:采用时钟上升沿有效。

首先判断使能控制信号

(enable),若enable=1,则停止计数并装载输入值;若enable=0,则判断加减控制信号(up_down),若为1则计数值加1,若为0则计数值减1。

3、完成Verilog代码后,设计测试平台进行仿真实验。

仿真中

要尽量检测所有可能的结果,并对仿真结果进行分析。

4、最后进行综合优化,以综合成逻辑电路。

仿真结果及分析

1、仿真波形说明自上而下依次是:时钟信号(clk),使能信

号(enable),上下计数信号(up_down),输入信号(x_in),输出信号(y_out)

2、首先测试使能信号enable是否满足要求,即当enable=1

时应停止计数并装入初值,其测试波形如下

由上图可发现当enable=1时,无论up_down取何值输出计数值始终装载的是输入值0xfc

3、接着测试up_down信号

由上图可知当enable=0时开始计数。

并且当up_down=1时,增计数模式;up_down=0时减计数模式。

4、完整波形如下

5、综合所得电路如下。

8位二进制加法器

《电子技术》课程设计报告题目学院(部)专业班级学生姓名学号月日至月日共周指导教师(签字)前言8位二进制加法器,它的功能主要是实现两个8位二进制数的相加,其结果的范围应该在00000000到111111110之间,即000到510之间。

加法器在实际应用中占据着十分重大的地位,从我们呱呱坠地起,到小学,到初中,到高中,到大学,到工作,等等。

我们能离开加法吗,不能!加法可以说是一切运算的基础,因此8位二进制加法器的设计是很有必要的。

那么我们如何设计一个8位二进制加法器呢?在实际应用中,我们通常输入的是十进制数,一个八位二进制数所对应的最大的十进制数是255,于是输入两个范围在000到255之间的数,首先通过二-十进制编码器将输入的三位十进制数的个位、十位、百位分别转换为8421BCD码,得到两个十二位字码,再通过加法器将它们相加,逢10进1,得到一个新的十二位字码,再用7447数字显示译码器将这个十二位字码还原到原来的三位十进制数。

最后输出的就是一个三位十进制数,其范围在000到510之间。

通过上述方法我们实现了八位二进制数的相加,从而达到了题目的要求。

为实现上述目的,我们需要查阅相关资料。

通过查阅,理解以及加以运用,我们认识到了收集资料的不易性,但同时也得到了不少收获,可以说是有苦有甜。

同时,虽然我们基本设计出了这个八位二进制加法器,但是不必可避免地会产生一些问题,比如说在连线上可能有更简便的途径,在元件的选用上可能还有其它更简便的方法,在控制上可能还不够精简,等等。

我们希望在以后的实践中能找出更好的方法,也希望能吸取这次设计中的不足,逐渐改善。

另外,在电子设计的过程中,与同组同学之间的合作配和是十分重要的。

我在此次设计中也充分认识到这一点的重要性,我相信这次的电子设计能够为我们将来的工作奠定一定的基础。

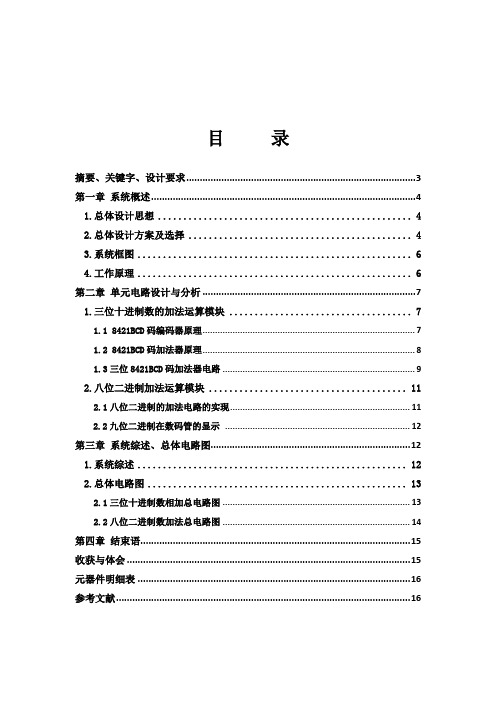

目录1.摘要 (1)2.关键字 (1)3.设计要求 (1)4.正文 (1)第一章.系统概述 (1)第二章.单元电路设计与分析 (4)①.控制电路 (4)②.编码电路 (5)③.加法电路 (6)④.译码电路 (10)⑤.输出电路 (11)第三章.系统综述、总体电路图 (11)第四章.结束语 (14)5.鸣谢 (15)6.元器件明细表,附图 (15)7.参考文献 (16)8.收获与体会,存在的问题等 (17)9.评语 (18)8位二进制加法器1.摘要:本次设计主要是如何实现8位二进制数的相加,即两个000到255之间的数相加,由于在实际中输入的往往是三位十进制数,因此,被加数和加数是两个三位十进制数,范围在000到255之间,通过六个二-十进制编码器(即74LS147)分别将加数和被加数的个位、十位、百位转换为8421BCD码,于是得到了两个12位字码,将它们接入三个四位超前进位并行加法器(即74LS283),其中原加数三位十进制数的个位转换得到的四位BCD码与被加数三位十进制数的个位转换得到的四位BCD码相加,串入到第一个74LS283的接线端,得到一个四位8421BCD码。

八位二进制加法器

2.2九位二进制在数码管的显示12

第三章系统综述、总体电路图12

1.系统综述12

2.总体电路图13

2.1三位十进制数相加总电路图13

2.2八位二进制数加法总电路图14

第四章结束语15

收获与体会15

元器件明细表16

参考文献16

《数字电子技术基础》课程设计报告

题目八位二进制加法器

运用74185实现九位二进制数BCD码的转化原理图:

第三章系统综述、总体电路图

1、系统综述:

加法电路是计算机电路中最基本的电路部分,在本次设计中,我们设计的是八位二进制相加和三位十进制相加并在数码管显示,我们采用74LS283来实现最基本的加法电路模块,再经过补充和修改加法电路,最终能实现本课题所要求

8421BCD码编码器电路

1.2 8421BCD码加法器原理

这部分是使用四位加法器构成的一位8421BCD码的加法器,8421BCD码是用4位二进制数表示1位十进制数,4位二进制数内部为二进制,8421BCD码之间是十进制,即逢十进一。而四位二进制加法器是按四位二进制数进行运算,即逢十六进一。二者进位关系不同。当四位二进制数加法器74LS283完成这个加法运算时,要用两片74LS283。第一片完成加法运算,第二片完成修正运算。

设计要求:

1.八位二进制加数与被加数的输入

2.三位数码管显示

3.三位十进制加数与被加数的输入

第一章系统概述

1、ቤተ መጻሕፍቲ ባይዱ体设计思想

选择两个74LS283超前进位并行加法器的串接可以计算八位二进制数的加法运算

选择合适的器件将输出的八位二进制数转换成三位十进制数,通过数码管显示

通过8421BCD码编码器可以将十进制数转化成四位二进制数

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

data2 equ 21h ;定义另一个廷时变量寄存器

n1 equ d'13' ;定义一个外层循环廷时常数

n2 equ 0ffh ;定义一个内层廷时常数

rp0 equ 5h ;定义状态寄存器的页选位RP0

goto check ;否!则循环检测

call delay ;调用廷时子程序,消除按钮抖动的影响

btfsc portb,0 ;再次测试S3按下否?是!跳过下条指令

goto check ;否!则循不检测

;*************************************************

org 000h ;定义程序存放区域的起始地址

nop ;放置一条ICD必须的空操作指令

bsf status,rp0 ;设置文件寄存器体1

;**************************************************

__CONFIG 3F39H;设置配置位中振荡方式为XT,其它全部禁止或关闭

;*************************************************

status equ 3h ;定义状态寄存器地址

portb equ 6h ;定义端口B的数据寄存器地址

trisb equ 86h ;定义端口B的方向控制寄存器地址

portc equ 7h ;定义端口C的数据寄存器地址

trisc equ 87h ;定义端口C的方向控制寄存器地址

incf portc,1 ;端口C的数据寄存器加1,并送LED显示

check1 btfss portb,0 ;测试S3断开否?是!跳过下条指令

goto check1 ;否!则循不检测

call delay ;调用廷时子程序,消除按钮抖动的影响

goto lp0 ;跳转到LP0

return ;返回主程序

end ;源程序结束

btfss portb,0 ;再次测试S3断开否?是!跳过下条指令

goto check1 ;否!则循不检测

goto check ;返回

;*************10MS廷时子程序************************

movlw 00h ;将端口C的方向控制码00H先送W

movwf trisc ;再转到方向寄存器,将其设置为输出

movlw 0ffh ;同理,将端口B设置为输入

movwf trisb ;

delay ;子程序名,也是子程序入口地址

movlw n1 ;将外层循环参数值送到DATA1

movwf data1 ;

lp0 movlw n2 ;将内层循环参数值送到DATA2

movwf data2 ;

lp1 decfsz data2,1 ;变量DATA2内容递减,若为0则跳跃

gห้องสมุดไป่ตู้to lp1 ;跳转到LP1

decfsz data1,1 ;变量DATA1内容递减,若为0则跳跃

bcf status,rp0 ;恢复到文件寄存器体0

movlw 00h ;送计器初值00H到RC口显示

movwf portc ;

check btfsc portb,0 ;测试S3按下否?是!跳过下条指令