FPGA基础试验之流水灯

基于FPGA的LED流水灯与按键消抖实验

基于FPGA的LED流水灯与按键消抖实验1.实验目的(1)通过实验进一步学习Quartus II软件的使用方法。

(2)通过实验学习流水灯的设计原理。

(3)通过实验学习按键消抖(边沿检测法)的基本原理。

2.实验仪器设备(1)FPGA开发实验箱。

(2)数字万用表。

(3)电脑。

3.预习(1)复习FPGA开发有关的流程。

(2)复习Verilog HDL语言语法。

(3)复习实验所用的相关原理。

(4)按要求编写实验中要求的硬件描述语言程序。

4.实验原理(1)LED流水灯。

流水灯是一个典型的FPGA程序设计,通过控制8位led向左依次循环点亮,达到对硬件语言、软件开发平台等的初步认识。

①if语句的使用。

Verilog HDL语言中的if语句与C语言中的十分相似,其使用方法有以下三种:a.if(条件1)语句块1;b.if(条件1)语句块1;else 语句块2;c.if(条件1)语句块1;else if(条件2)语句块2;……else if(条件n)语句块n;else 语句块n+1。

在上述三种方式中,“条件”一般为逻辑表达式或关系表达式,也可以是一位的变量。

如果表达式的值出现0(假),x(未知),z(高阻),则全部按“假”来处理;若为“1”,则按“真”来处理。

语句块若为单句,直接书写即可;若为多句,则需要用“begin end”块括起来。

建议无论多句还是单句都用“begin end”括起来。

②case语句的使用。

case语句是一个多路条件分支语句,常用于多路译码、状态机和微处理机的指令译码等场合。

case语句的语法格式为:case(条件表达式)分支1:语句块1;分支2:语句块2;……default:语句块nendcase其中,“分支n”通常都是一些常量表达式。

case语句先对“条件表达式”求值,然后同时并行对各分支项求值并进行比较,这是与if语句最大不同。

比较完成后,与条件表达式值相匹配的分支中的语句被执行。

分支项需要互斥,否则会出现逻辑矛盾。

基于FPGA的流水灯

基于FPGA的流水灯概述流水灯是一种常见的电子实验项目,也是学习数字电路和FPGA编程的入门项目之一。

本文介绍了如何使用FPGA实现一个基于流水灯的电子项目。

需求流水灯项目的主要需求是将一组LED灯以一定的速率顺序点亮,然后逐个熄灭,再以同样的速率顺序点亮下一个LED 灯,如此循环。

硬件设计FPGA板在本项目中,我们使用一块支持FPGA编程的开发板。

可选的FPGA开发板包括Xilinx的Nexys 4或Digilent的Basys 3等。

LED灯流水灯需要一组LED灯来显示效果。

我们将使用FPGA开发板上的LED灯作为显示单元。

连接将LED灯的阳极连接到FPGA开发板的GPIO引脚上,并将其地连接到电路板上的公共地线。

软件设计硬件描述语言(HDL)HDL是一种用于描述数字电路和FPGA的语言。

常用的HDL包括VHDL和Verilog。

我们将使用Verilog作为本项目的HDL语言。

Verilog代码下面是一个基于FPGA的流水灯的Verilog代码示例:module led_shifter(input clk,output reg [7:0] leds);reg [25:0] counter;always @(posedge clk) begincounter <= counter + 1;if (counter == 26'd255) begincounter <= 0;leds <= leds << 1;endendendmodule上述Verilog代码中,我们定义了一个led_shifter模块,该模块接受一条时钟信号(clk)和一个用于控制LED灯的8位寄存器(leds)。

leds寄存器表示LED灯的状态,其中每个位代表一个LED灯。

在always块中,我们使用一个计数器counter来计算时钟脉冲的数量。

当计数器的值达到255时,即过了一定的时钟周期,我们将计数器重置为0,并将leds寄存器向左移动一位,即将下一个LED灯点亮。

FPGA基础试验之流水灯

综合实验报告第四组组长:韩欢02081535陈洁钰02081536侯旭涛02081514高耀02081510李欣昊02081508李昊02081506FPGA基础试验之流水灯一、实验目的通过此实验进一步了解、熟悉和掌握Quartus II开发软件的使用方法及Verilog 语言的编程方法。

学习简单时序电路的设计分析和硬件测试。

二、实验内容1.熟悉信号产生板中的FPGA的普通I/O的连接;2.根据实际的流水灯分析时序,体会用Verilog语言的编程产生相应时序;3.熟悉集成开发工具Quartus II,学会使用Quartus II对Cyclone系列FPGA的程序开发、编译与调试;4.掌握Cyclone系列FPGA的程序加载,熟练掌握将.sof文件加载到实验板的FPGA中,实现流水灯的效果。

三、实验原理流水灯,顾名思义就是让LED像水一样的点亮。

如果把流水做慢动作播放,可以想象到其实就是移动,即:把水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水。

同样,如果使得最左边的灯先亮,然后通过移位,在其右侧的灯,从左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯。

初始状态时,四个灯都不亮,每来一个时钟脉冲,CLK,计数器就加1.这样通过移位依次点亮所有的灯,就形成了流水灯。

而当四个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态。

然后,再一次流水即可。

如果是右移位,就出现向右流水的现象;反之,向左流水。

四、实验要求控制4个LED进行花式显示,根据硬件设施设计两种模式:S0:从全亮到全灭,再到全亮,依次循环;S1:从LED0开始依次点亮,为LED1亮,LED2亮,LED3亮,后再LED2亮,LED1亮,LED0亮,不停循环。

即输出为:S0时,从0000到1111不停循环转换;S1时,0111,1011,1101,1110,1101,1011,0111不断循环。

五、实验步骤(1)建立工程(2)建立Verilog文件,编写相关程序(3)将verilog文件编译为可视化电路图文件(4)将可视化电路图文件添加输入输出组合成电路图文件(5)编译语法及验证原理图(6)根据需要分配管脚并进行编译(7)下载编译后得到的文件.sof(在线方式),.pof(离线方式)。

verilog实验报告流水灯数码管秒表交通灯

流水灯实验目的:在basys2开发板上实现LED灯的花样流水的显示,如隔位显示,依次向左移位显示,依次向右移位显示,两边同时靠中间显示。

实验仪器:FPGA开发板一块,计算机一台。

实验原理:当一个正向的电流通过LED时,LED就会发光。

当阳极的电压高于阴极的电压时,LED就会有电流通过。

当在LED上增添一个典型值为1.5V—2.0V之间的电压时,LED就会有电流通过并发光。

实验内容:顶层模块:输入信号:clk_50MHz(主时钟信号),rst(重置信号),输出信号:[7:0] led(LED灯控制信号)。

module led_top(clkin,rst,led_out);input clkin, rst;output [7:0] led_out;wire clk_1hz;divider_1hz d0(clkin, rst, clk_1hz);led l0(clk_1hz, rst, led_out);endmodule分频模块:module divider_1hz(clkin,rst,clkout);input clkin,rst;output reg clkout;reg [24:0] cnt;always@(posedge clkin, posedge rst)beginif(rst) begincnt<=0;clkout<=0; endelse if(cnt==24999999) begincnt<=0;clkout=!clkout; endelse cnt<=cnt+1;endendmodule亮灯信号模块:module led(clkin,rst,led_out);input clkin,rst;output [7:0] led_out;reg [2:0] state;always@(posedge clkin, posedge rst)if(rst) state<=0;else state<=state+1;always@(state)case(state)3'b000:ledout<=8'b0000_0001;3'b001:ledout<=8'b0000_0010;3'b010:ledout<=8'b0000_0100;3'b011:ledout<=8'b0000_1000;3'b100:ledout<=8'b0001_0000;3'b101:ledout<=8'b0010_0000;3'b110:ledout<=8'b0100_0000;3'b111:ledout<=8'b1000_0000;endcaseendmodule实验中存在的问题:1 芯片选择问题automotive spartan3EXA3S100E XA3S250E CPG132spartan3EXC3S100E XC3S250E CP1322 时序逻辑部分,阻塞赋值和非阻塞赋值混用always@(posedge clk)begina=b+c;d<=e+f;end3 UCF文件格式错误NET “CLK” LOC = “B8”;NET “a” LOC = “N11”;NET “b” LOC = “G13”;NET “c[0]”LOC =“K11;数码管实验目的:设计一个数码管动态扫描程序,实现在四位数码管上动态循环显示“1”、“2”“3”“4”;实验仪器:FPGA开发板一块,计算机一台。

fpga流水灯实验报告

竭诚为您提供优质文档/双击可除fpga流水灯实验报告篇一:vhdl流水灯课程设计报告院系:姓名:学号:课程设计名称:指导老师:时间:摘要VhDL的特点应用VhDL进行系统设计,有以下几方面的特点。

(一)功能强大VhDL具有功能强大的语言结构。

它可以用明确的代码描述复杂的控制逻辑设计。

并且具有多层次的设计描述功能,支持设计库和可重复使用的元件生成。

VhDL是一种设计、仿真和综合的标准硬件描述语言。

(二)可移植性VhDL语言是一个标准语言,其设计描述可以为不同的eDA工具支持。

它可以从一个仿真工具移植到另一个仿真工具,从一个综合工具移植到另一个综合工具,从一个工作平台移植到另一个工作平台。

此外,通过更换库再重新综合很容易移植为AsIc设计。

(三)独立性VhDL的硬件描述与具体的工艺技术和硬件结构无关。

设计者可以不懂硬件的结构,也不必管最终设计实现的目标器件是什么,而进行独立的设计。

程序设计的硬件目标器件有广阔的选择范围,可以是各系列的cpLD、FpgA及各种门阵列器件。

(四)可操作性由于VhDL具有类属描述语句和子程序调用等功能,对于已完成的设计,在不改变源程序的条件下,只需改变端口类属参量或函数,就能轻易地改变设计的规模和结构。

(五)灵活性VhDL最初是作为一种仿真标准格式出现的,有着丰富的仿真语句和库函数。

使其在任何大系统的设计中,随时可对设计进行仿真模拟。

所以,即使在远离门级的高层次(即使设计尚未完成时),设计者就能够对整个工程设计的结构和功能的可行性进行查验,并做出决策。

VhDL的设计结构VhDL描述数字电路系统设计的行为、功能、输入和输出。

它在语法上与现代编程语言相似,但包含了许多与硬件有特殊关系的结构。

VhDL将一个设计称为一个实体entity(元件、电路或者系统),并且将它分成外部的可见部分(实体名、连接)和内部的隐藏部分(实体算法、实现)。

当定义了一个设计的实体之后,其他实体可以利用该实体,也可以开发一个实体库。

基于FPGA的流水灯

基于FPGA的流水灯介绍流水灯(Traffic Light)是一种常见的电子实验项目,通过一组灯的亮灭变化来模拟交通信号灯的工作原理。

在本文档中,我们将介绍如何使用FPGA(Field-Programmable Gate Array)来实现流水灯功能。

背景知识FPGA概述FPGA是一种重新可编程的集成电路芯片,可以通过修改内部逻辑电路来实现不同的功能。

相比于传统的固定功能芯片,FPGA具有更高的灵活性和可重构能力。

流水灯原理流水灯由多个灯泡组成,每个灯泡在不同的时间点亮。

通过逐个点亮和熄灭灯泡,可以模拟交通信号灯的变化效果。

硬件设计硬件平台选择在本项目中,我们选择使用一块FPGA开发板作为硬件平台。

开发板上集成了FPGA芯片以及所需的外围器件,方便我们进行流水灯的实验。

硬件连接将FPGA开发板上的LED灯连接到FPGA芯片的GPIO(通用输入输出)引脚上。

通过配置FPGA芯片的GPIO引脚为输出模式,我们可以控制LED灯的亮灭状态。

软件设计硬件描述语言(HDL)为了描述FPGA中的逻辑电路,我们需要使用一种称为硬件描述语言(Hardware Description Language)的工具。

常用的硬件描述语言有Verilog和VHDL两种。

Verilog代码示例以下是一个使用Verilog描述的简单流水灯控制器的例子:module led_controller (input wire clk, // 时钟输入output wire [7:0] led // LED灯控制输出);reg [25:0] counter; // 计数器always @(posedge clk) beginif (counter == 0)led <= 8'h01; // 第一个灯亮else if (counter == 500000)led <= 8'h02; // 第二个灯亮else if (counter == 1000000)led <= 8'h04; // 第三个灯亮else if (counter == 1500000)led <= 8'h08; // 第四个灯亮else if (counter == 2000000)led <= 8'h10; // 第五个灯亮else if (counter == 2500000)led <= 8'h20; // 第六个灯亮else if (counter == 3000000)led <= 8'h40; // 第七个灯亮else if (counter == 3500000)led <= 8'h80; // 第八个灯亮counter <= counter + 1'b1;endendmodule在该代码中,我们定义了一个8位宽的led输出端口和一个26位宽的计数器。

FPGA入门系列实验教程——流水灯

FPGA入门系列实验教程——LED流水灯1.实验任务让实验板上的8个LED实现流水灯的功能。

通过这个实验,进一步掌握采用计数与判断的方式来实现分频的Verilog HDL的编程方法以及移位运算符的使用。

2.实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208C8增强版开发套件。

软件实验环境为Quartus II8.1开发软件。

3.实验原理流水灯,顾名思义就是让LED象水一样的点亮。

如果把流水做慢动作播放,可以想象到其实就是移动,即:把水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水。

同样,如果使得最左边的灯先亮;然后,通过移位,在其右侧的灯,由左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯。

初始状态时,8个灯都不亮。

每来一个时钟脉冲CLK,计数器就加1。

每当判断出计数器中的数值达到25000000时,就会点亮一个灯,并进行移位。

FPGA输出的数据就应该首先是10000000,隔1秒钟变成11000000……一直变化到11111111,这样,依次点亮所有的灯,就形成了流水灯。

而当8个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态,即:灯都不亮。

然后,再一次流水即可。

如果是右移位,就出现向右流水的现象;反之,向左流水。

4.实验程序module ledwater(clk,led);//模块名及端口参数output[7:0]led;//输出端口定义input clk;//输入端口定义,50M时钟reg[8:0]led_out;//变量led_out定义为寄存器型reg[8:0]led_out1;//变量led_out1定义为寄存器型reg[25:0]buffer;//中间变量buffer定义为寄存器型always@(posedge clk)beginbuffer=buffer+1;if(buffer==26'd2*******)//判别buffer数值为25000000时,做输出处理beginled_out=led_out<<1;//led向左移位,空闲位自动添0补位if(led_out==9'b000000000)led_out=9'b111111111;led_out1=~led_out;//取反输出endendassign led=led_out1[7:0];endmodule5.实验步骤(1)建立新工程项目:打开Quartus II软件,进入集成开发环境,点击File→New project wizard建立一个工程项目ledwater。

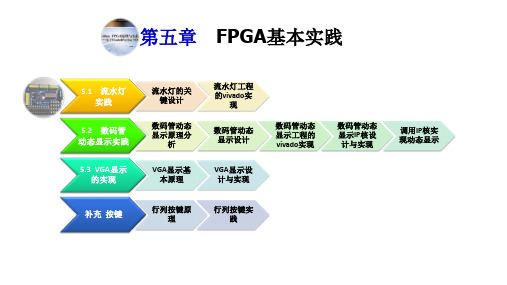

5.1流水灯实践

第五章FPGA基本实践5.1流水灯实践流水灯的关键设计流水灯工程的vivado 实现5.2数码管动态显示实践数码管动态显示原理分析数码管动态显示设计数码管动态显示工程的vivado 实现数码管动态显示IP 核设计与实现调用IP 核实现动态显示5.3 VGA 显示的实现VGA 显示基本原理VGA 显示设计与实现补充按键行列按键原理行列按键实践5.1 流水灯实践一组发光LED,在控制系统的控制下按照设定的顺序和时间来发亮和熄灭,这样就能形成一定的视觉效果。

如果通过设计,实现LED灯依次点亮,那么就形成流水灯。

本节的内容就是设计这样的控制系统,实现12位流水灯,并进行仿真及下载到电路板验证。

5.1.1 流水灯的关键设计1.状态及其变化(1)状态需要存储当前的状态,12个灯中有一个是亮的,定义12个触发器构成的12位寄存器ledtemp保存当前的状态。

(2)时钟流水灯的流转时间设置为半秒钟(500ms/2Hz)比较合适,系统的唯一时钟来源是由电路板上的有源晶振所产生的时钟连接到FPGA,是50MHz的时钟clk,因此需做25,000,000分频。

(3)状态变化将寄存器ledtemp的初始值设置为12'b0000_0000_0001,divclk的每个上升边沿,对ledtemp进行向左移位,当移到12'b1000_0000_0000之后,再次移位应移为12'b0000_0000_0001。

5.1.1 流水灯的关键设计2.分频设计要进行25,000,000分频,采用计数器的方式。

当计数值达到12,500,000时令divclk翻转,这样divclk的一个周期就是25,000,000个clk时钟周期。

需要一个寄存器变量存储计数值,12,500,000的十六进制是BEBC20为24位,因此需要设计24位以上的寄存器保存计数值。

0->12,500,000->0-> 12,500,000->0-> 12,500,0004.约束设计一个时钟输入12个数码管输出⏹module v1(⏹input clk, //时钟输入⏹output [11:0] led //LED输出⏹);⏹reg[11:0] ledtemp= 12'b0000_0000_0001; //led初始值⏹reg[31:0] divclk_cnt= 0; //32位计数器⏹reg divclk= 0; //低频时钟⏹assign led=ledtemp; //实现将寄存器变量值赋给LED输出⏹parameter halfduty_cntvalue= 12500000;⏹always@(posedge clk) //把系统时钟分频50/2500 0000= 2HZ ⏹begin⏹if(divclk_cnt==halfduty_cntvalue) //计数满后翻转⏹begin⏹divclk=~ divclk;⏹divclk_cnt= 0;⏹end⏹else⏹begin⏹divclk_cnt= divclk_cnt+1'b1;⏹end⏹end⏹仿真⏹仿真文件编写⏹仿真的目的,修改分频值以缩短仿真时间⏹执行仿真⏹编写约束文件代码⏹保存工程⏹综合⏹实现⏹生成比特流文件⏹下载到实验板测试⏹set_property PACKAGE_PIN D4 [get_ports clk]⏹set_property PACKAGE_PIN P9 [get_ports{led[0]}]⏹set_property PACKAGE_PIN R8 [get_ports{led[1]}]⏹set_property PACKAGE_PIN R7 [get_ports{led[2]}]⏹set_property PACKAGE_PIN T5 [get_ports{led[3]}]⏹set_property PACKAGE_PIN N6 [get_ports{led[4]}]⏹set_property PACKAGE_PIN T4 [get_ports{led[5]}]⏹set_property PACKAGE_PIN T3 [get_ports{led[6]}]⏹set_property PACKAGE_PIN T2 [get_ports{led[7]}]⏹set_property PACKAGE_PIN R1 [get_ports{led[8]}]⏹set_property PACKAGE_PIN G5 [get_ports{led[9]}]⏹set_property PACKAGE_PIN H3 [get_ports{led[10]}]⏹set_property PACKAGE_PIN E3 [get_ports{led[11]}]⏹set_property IOSTANDARD LVCMOS33 [get_ports clk]⏹……5.1.2流程灯工程的VIVADO实现有缘学习更多+谓ygd3076或关注桃报:奉献教育(店铺)示实践。

时序流水灯实验报告

一、实验目的1. 熟悉时序电路的基本原理和设计方法。

2. 掌握FPGA开发软件的使用方法,包括原理图设计、Verilog HDL编程、仿真调试等。

3. 学会使用FPGA实现时序流水灯的功能,并观察其工作效果。

二、实验原理时序流水灯是一种常见的电子电路,通过控制LED灯的亮灭顺序,实现流水灯效果。

本实验采用FPGA实现时序流水灯,主要原理如下:1. 使用FPGA内部寄存器作为计数器,对时钟信号进行计数。

2. 根据计数器的值,通过查找表(LUT)控制LED灯的亮灭顺序。

3. 使用时钟分频器产生定时器时钟,用于更新计数器的值。

三、实验内容1. 使用FPGA开发软件,建立时序流水灯的原理图。

2. 使用Verilog HDL编写时序流水灯的代码。

3. 对代码进行仿真调试,验证其正确性。

4. 将程序烧录到FPGA开发板上,观察时序流水灯的工作效果。

四、实验步骤1. 建立原理图(1)打开FPGA开发软件,创建一个新项目。

(2)添加FPGA芯片,并配置其引脚。

(3)添加时钟信号源,设置时钟频率。

(4)添加计数器模块,设置计数器的位宽和初始值。

(5)添加查找表(LUT)模块,用于控制LED灯的亮灭顺序。

(6)添加时钟分频器模块,产生定时器时钟。

2. 编写Verilog HDL代码(1)创建一个名为`seq_led`的模块,包含以下端口:- `clk`:时钟信号输入- `rst`:复位信号输入- `led`:LED灯输出(2)在模块内部,定义以下信号:- `count`:计数器信号- `led_pattern`:查找表输出信号(3)编写代码实现以下功能:- 初始化计数器和查找表输出信号。

- 在每个时钟周期,对计数器进行加1操作。

- 根据计数器的值,通过查找表输出对应的LED灯亮灭顺序。

3. 仿真调试(1)将编写好的代码添加到原理图中。

(2)设置仿真参数,包括时钟频率、仿真时间等。

(3)启动仿真,观察LED灯的亮灭顺序是否符合预期。

关于FPGA应用软件VIVADO的使用心得体会与操作流程流水灯

6、确认相关信息与设计所用的的 FPGA 器件信息是否一致,一致请点击 Finish,不一致,请返

依元素科技有限公司

3

Xilinx 全球合作伙伴

回上一步修改。

方案标准

7、得到如下的空白 Vivado 工程界面,完成空白工程新建。

二、设计文件输入 1、如下图所示,点击 Flow Navigator 下的 Project Manager->Add Sources 或中间 Sources 中的 对话框打开设计文件导入添加对话框。

方案标准

6、在弹出的 Define Module 中的 I/O Port Definition,输入设计模块所需的端口,并设置端口方 向,如果端口为总线型,勾选 Bus 选项,并通过 MSB 和 LSB 确定总线宽度。完成后点 OK。

注:led 实际宽度与代码中一致,也可在代码中修改。

7、新建的设计文件(此处为 flowing_light.v)即存在于 Sources 中的 Design Sources 中。双击 打开该文件,输入相应的设计代码。

4、选择 RTL Project 一项,并勾选 Do not specify sources at this time,勾选该选项是为了跳过

依元素科技有限公司

2

Xilinx 全球合作伙伴

在新建工程的过程中添加设计源文件。点击 Next。

方案标准

5、根据使用的 FPGA 开发平台,选择对应的 FPGA 目标器件。 在本手册中,以 Xilinx 数模混 合口袋实验室 为例,FPGA 采用 Artix-7 XC7A35T-1CSG324-C 的器件,即 Family 和 Subfamily 均 为 Artix-7,封装形式(Package)为 CSG324,速度等级(Speed grade)为-1,温度等级(Temp Grade) 为 C)。点击 Next。

fpga流水灯实验报告

竭诚为您提供优质文档/双击可除fpga流水灯实验报告篇一:vhdl流水灯课程设计报告院系:姓名:学号:课程设计名称:指导老师:时间:摘要VhDL的特点应用VhDL进行系统设计,有以下几方面的特点。

(一)功能强大VhDL具有功能强大的语言结构。

它可以用明确的代码描述复杂的控制逻辑设计。

并且具有多层次的设计描述功能,支持设计库和可重复使用的元件生成。

VhDL是一种设计、仿真和综合的标准硬件描述语言。

(二)可移植性VhDL语言是一个标准语言,其设计描述可以为不同的eDA工具支持。

它可以从一个仿真工具移植到另一个仿真工具,从一个综合工具移植到另一个综合工具,从一个工作平台移植到另一个工作平台。

此外,通过更换库再重新综合很容易移植为AsIc设计。

(三)独立性VhDL的硬件描述与具体的工艺技术和硬件结构无关。

设计者可以不懂硬件的结构,也不必管最终设计实现的目标器件是什么,而进行独立的设计。

程序设计的硬件目标器件有广阔的选择范围,可以是各系列的cpLD、FpgA及各种门阵列器件。

(四)可操作性由于VhDL具有类属描述语句和子程序调用等功能,对于已完成的设计,在不改变源程序的条件下,只需改变端口类属参量或函数,就能轻易地改变设计的规模和结构。

(五)灵活性VhDL最初是作为一种仿真标准格式出现的,有着丰富的仿真语句和库函数。

使其在任何大系统的设计中,随时可对设计进行仿真模拟。

所以,即使在远离门级的高层次(即使设计尚未完成时),设计者就能够对整个工程设计的结构和功能的可行性进行查验,并做出决策。

VhDL的设计结构VhDL描述数字电路系统设计的行为、功能、输入和输出。

它在语法上与现代编程语言相似,但包含了许多与硬件有特殊关系的结构。

VhDL将一个设计称为一个实体entity(元件、电路或者系统),并且将它分成外部的可见部分(实体名、连接)和内部的隐藏部分(实体算法、实现)。

当定义了一个设计的实体之后,其他实体可以利用该实体,也可以开发一个实体库。

基础项目(1)流水灯项目讲解

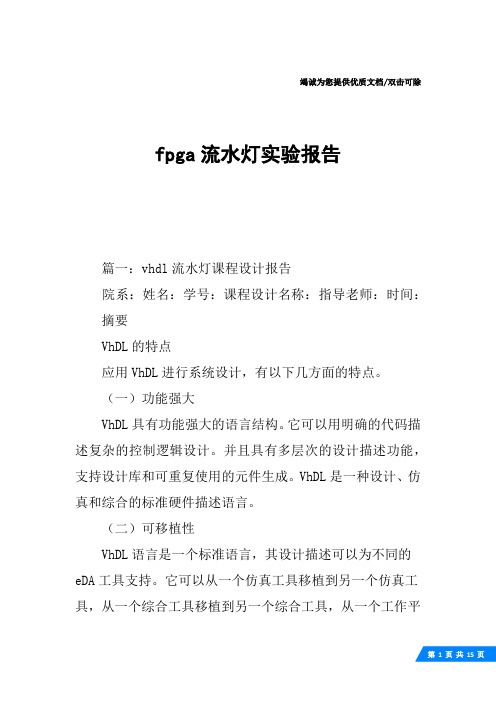

基础项⽬(1)流⽔灯项⽬讲解写在前⾯的话这⼀节呢,我们来实现⼀个流⽔灯驱动程序的编写,当然啦,点灯不是⽬的,最重要的是我们通过这个流⽔灯代码的实现可以掌握⼀些重要的规范。

项⽬需求我们要求流⽔灯模式如下:当复位键按下时,灯全部熄灭,当复位键放开以后,⾸先,点亮第⼀个灯,然后第⼀个灯熄灭,同时点亮第⼆个灯,接着,第⼆个灯熄灭,同时点亮第三个灯,然后,第三个灯熄灭,同时点亮第四个灯,最后第四个灯熄灭,同时点亮第⼀个灯,如此循环往复,实现流⽔。

相关技术介绍项⽬需求,我相信⼤家已经看清楚了,那么,接下来我们该怎么做呢?写代码?NO 我们来仔细的看看项⽬需求,这⾥⾯涉及到了按键,LED灯,还需要我们⽤按键控制流⽔灯的启动或停⽌。

那么,在写代码之前,我们⾸先应该明确按键按下和放开有什么区别、LED是低电平点亮还是⾼电平点亮。

只有清楚外设的性能,我们才可能编写代码正确地驱动这些外设。

代码体现的是我们的思路,所以在写代码之前我们必须⾸先理顺⾃⼰的思路,否则盲⽬的编写代码,⼀定是徒劳的。

硬件设计下图所⽰为轻触按键与FPGA的连接关系⽰意图由上述电路图可知,当按键放开时,FPGA端⼝等于接到了上拉电阻,所以检测到的为⾼电平。

当按键按下时,FPGA端⼦通过按键接到了地平⾯,检测到的为低电平。

下图所⽰为LED与FPGA的连接关系⽰意图由上述电路图可知,LED正极全部接到了3.3V电源。

那么,只有当FPGA端⼝给出低电平的时候,LED才会点亮。

当FPGA端给⾼电平时,LED熄灭。

顶层架构设计项⽬需求以及项⽬需求中所涉及到的所有外设都已经分析清楚了,那么接下来是不是可以开始编写代码了呢?答案还是—NO!哈哈,别着急,其实对于⼯程师⽽⾔,编写代码真的是⼩菜⼀碟,闭着眼睛都能敲⼏⾏哦。

⼀个项⽬最重要的、最终决定成败的⼀般来说不是代码的具体实现,⽽是前期的架构设计,好的架构可以化简为易,将⼀个很复杂的⼯程逐步的拆分成很多简单的⼦模块,不但提⾼了设计效率和成功率,同时也⽐较适合团队作战,分⼯合作。

fpga流水灯设计实验报告

fpga流水灯设计实验报告一、实验目的通过此实验进一步了解,熟悉FPGA开发软件的使用方法及,的编程方法:学习简单时序电路的设计。

二、实验原理和内容实验内容:在实验板上实现LED1~LED8发光二极管流水灯显示实验原理:在LED1~LED8引脚上周期性地输出流水数据,如原来输出的数据是则表示点亮LED1,LED2流水一次后,输出数据应该为,而此时则应点亮LED1-LED3三个LED发光二极管,这样就可以实现LED流水灯,为了观察方便,流水速率最好在2Hz左右。

在QuickSOPC核心板上有48MHz的标准时钟源,该时钟脉冲CLOCK与芯片的28脚相连,为了产生2Hz的时钟脉冲,在此调用了一个分频模块intdiv模块,通过修改分频系数来改变输出频率,int-div模块是一个占空比为50%的任意整数分频器。

三、实验步骤1、启动QuartusⅡ建立一个空白工程,然后命名为。

2、新建VerilogHDL源程序文件,输入程序代码并保存,然后进行综合编译。

若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

3、从设计文件创建模块,由生成名为的模块符号文件。

4、将光盘中EDA-Component目录下的和拷贝到工程目录。

5、新建图形设计文件命名为并保存。

在空白处双击鼠标左键,在Symbol对话框左上角的中,分别将project下的ledwater和int-div模块放在图形文件中,加入输入,输出引脚,双击各引脚符号进行引脚命名。

将与ledwater模块led[7.0]连接的引脚命名为led[7..0],与int-div模块clock连接的引脚命名为clock,int-div模块的clk-out与ledwater模块的clk相连接。

6、选择目标器件并对相应的引脚进行锁定,在这里所选择的器件为Altera公司Cyclone系列的EPIC12Q240C8芯片,引脚锁定方法见下表,将未使用的引脚设置为三态输入。

基于FPGA的数字电路实验7:流水灯的实现

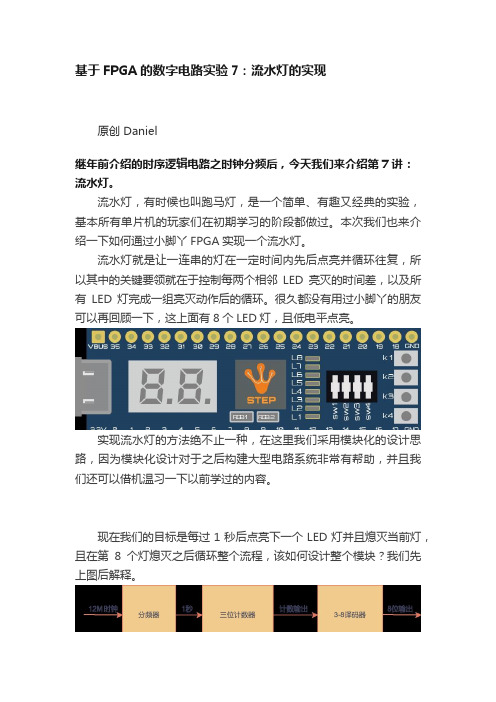

基于FPGA的数字电路实验7:流水灯的实现原创 Daniel继年前介绍的时序逻辑电路之时钟分频后,今天我们来介绍第7讲:流水灯。

流水灯,有时候也叫跑马灯,是一个简单、有趣又经典的实验,基本所有单片机的玩家们在初期学习的阶段都做过。

本次我们也来介绍一下如何通过小脚丫FPGA实现一个流水灯。

流水灯就是让一连串的灯在一定时间内先后点亮并循环往复,所以其中的关键要领就在于控制每两个相邻LED亮灭的时间差,以及所有LED灯完成一组亮灭动作后的循环。

很久都没有用过小脚丫的朋友可以再回顾一下,这上面有8个LED灯,且低电平点亮。

实现流水灯的方法绝不止一种,在这里我们采用模块化的设计思路,因为模块化设计对于之后构建大型电路系统非常有帮助,并且我们还可以借机温习一下以前学过的内容。

现在我们的目标是每过1秒后点亮下一个LED灯并且熄灭当前灯,且在第8个灯熄灭之后循环整个流程,该如何设计整个模块?我们先上图后解释。

毫无疑问,第一步需要做的就是通过分频来生成一个周期为1秒的时钟信号,不了解时钟分频童鞋可以读一下本系列的第6篇内容。

有了一个1秒钟嘀嗒一次的时钟后,我们还要考虑到循环问题,因为在第8个LED灯熄灭之后还需要再返回到第1个。

那么这个时候我们就需要一个计数器,它的作用就是数羊,一只,两只…...数到第八只后重头再来。

数8只羊需要一个3位宽的变量(23=8)。

最后,由于我们是要依次点亮,也就是说8位的输出中每次只有1位是低电平,其余均为高电平(小脚丫LED灯为低电平点亮)。

这个特性正好对应了我们之前学过的3-8译码器。

现在我们再来捋一遍。

首先,通过分频在小脚丫上生成一个周期为1秒的慢速时钟信号,这个时钟信号传送到计数器之中;这个计数器是3位宽的,因此最多可以计八次慢速时钟的嘀嗒,并且计数每增加1时,都对应着3-8译码器的下一种输出,也就对应着流水灯的下一个状态。

现在我们上代码:•••••••••••••••••••••••module runningled (clk,led); input clk,rst; output[7:0] le d; reg [2:0] cnt ; / /定义了一个3位的计数器,输出可以作为3-8译码器的输入 wire clk1hz; //定义一个中间变量,表示分频得到的时钟,用作计数器的触发 //例化分频模块,产生一个1Hz时钟信号 divide #(.WIDTH(24),.N(12000000)) u2 ( //除数为12,000,000,因此频率为1Hz .clk(clk), .rst_n(rst), .clkout(clk1hz) ); //生成计数器,上沿触发并循环计数 always@(posedge clk1hz) cnt <=< span=""> cnt +1; // 达到位宽上限后可自动溢出清零 //例化3-8译码器模块 decode38 u1 ( .X(cnt), //例化的输入端口连接到cnt,输出端口连接到led .D(led) );endmodule在第四篇讲译码器的文章里,我们介绍过,如果需要调用/例化子模块时,需要将各子模块与大模块放入同一个工程文件下进行编译。

FPGA流水灯实验报告

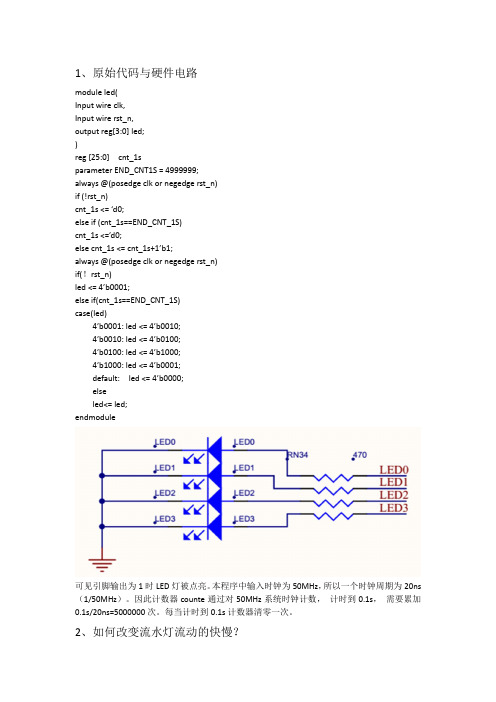

1、原始代码与硬件电路module led(Input wire clk,Input wire rst_n,output reg[3:0] led;)reg [25:0] cnt_1sparameter END_CNT1S = 4999999;always @(posedge clk or negedge rst_n)if (!rst_n)cnt_1s <= ‘d0;else if (cnt_1s==END_CNT_1S)cnt_1s <=’d0;else cnt_1s <= cnt_1s+1’b1;always @(posedge clk or negedge rst_n)if(!rst_n)led <= 4’b0001;else if(cnt_1s==END_CNT_1S)case(led)4’b0001: led <= 4’b0010;4’b0010: led <= 4’b0100;4’b0100: led <= 4’b1000;4’b1000: led <= 4’b0001;default: led <= 4’b0000;elseled<= led;endmodule可见引脚输出为1时LED灯被点亮。

本程序中输入时钟为50MHz,所以一个时钟周期为20ns (1/50MHz)。

因此计数器counte通过对50MHz系统时钟计数,计时到0.1s,需要累加0.1s/20ns=5000000次。

每当计时到0.1s计数器清零一次。

2、如何改变流水灯流动的快慢?要改变流水灯的快慢只需改变计数器的计数上限即可,要加快流水灯的速度就把计数器的计数上限降低一些,反之,要减慢流水灯的速度就把计数器的计数上限提高一些,改第七行的数值即可。

原始:parameter END_CNT1S = 4999999;加快速度:parameter END_CNT1S = 3999999;降低速度:parameter END_CNT1S = 9999999;3、如何改变流水灯移动的方向?要改变流水灯的方向,更改第18行到第21行的引脚赋值语句的数值即可原始方向代码:4’b0001: led <= 4’b0010;4’b0010: led <= 4’b0100;4’b0100: led <= 4’b1000;4’b1000: led <= 4’b0001;更改方向后的代码:4’b0001: led <= 4’b1000;4’b0010: led <= 4’b0100;4’b0100: led <= 4’b0010;4’b1000: led <= 4’b0001;。

实验4 基于FPGA的流水灯设计

实验四基于FPGA的流水灯设计

一、实验的目的

学习运用VHDL语言实现LED灯的控制方法。

二、实验内容

1.用VHDL语言编程,实现用8个发光二极管从左至右循环显示。

要求:(1) 用模式5中PI08-PI15接灯;

(2) 流水灯输入时钟为1Hz,即每秒钟变化一次;

(3) 流水灯输出为8位显示,每次仅一个灯亮;

(4) 用至少两种方法来设计流水灯的各部分功能模块(如:可以用元件例化的方法,或者用多进程的设计方法等等)。

(5)用VHDL语言编程,实现其功能

三、实验仪器

计算机、QuartusII软件和康芯EDA实验箱

四、实验报告要求

根据以上的实验内容写出实验预习报告(没写预习报告的不准进入实验室)和实验报告,包括程序设计、硬件连接图。

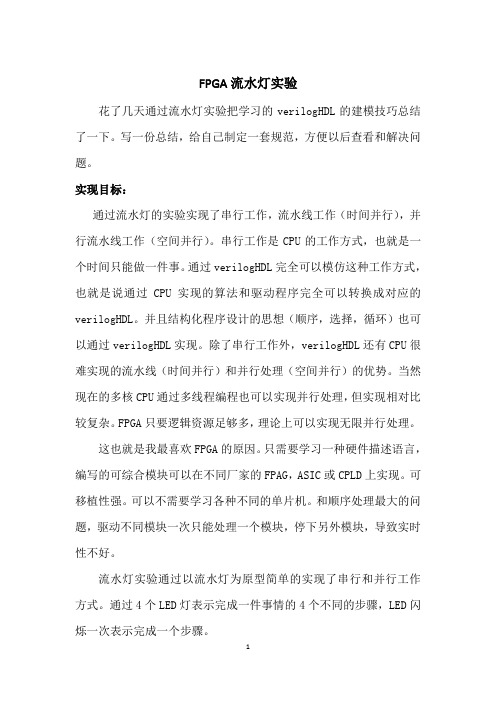

FPGA流水灯实验

编写代码的首要任务是管理复杂度,研究表明人能同时关注的智 力模型为 7+2,而嵌套关注通常不超过 5 层。编写一段代码的同时关 注点很容易会超过 9 个。通过智力训练提供关注智力模型数的效果微 乎其微。所以为了能编写任意大规模的代码,把同一时间关注的智力 模型数降低的方法是很有效的。而且软件工程也是在制定相关的编程 规范,对编程限制的基础上发展起来的。VerilogHDL 虽然是硬件描述 语言,但它已经摆脱了原始的电路图输入的方式,具有更高的抽象性, 所以它应该可以应该软件开发中的类似的结论来提高开发效率。就像 高级语言相对于 01 机器码编程一样。我觉得在 verilogHDL 在模仿顺 序操作上更像汇编语言,因为它没有实现顺序,选择,循环结构的相

10

了对 Led_Driver 更高层次的操作,使得操作每个 LED 站在了抽象层, 而不是是底层。

在底层你需要考虑定时器翻转多少次才能到这个时间,然后还要 用这个时间打开或关闭 LED,这样需要考虑的问题很复杂也容易出错。 在抽象层你只需要给什么时候打开或关闭 LED 就够了,它就会自动的 完成翻转工作。抽象性也是人脑处理信息的方式,例如自己的家你甚 至说不清门是什么颜色的,门的把手是什么样式的。人脑对门的处理 是抽象的,它是一个可以开和关的门。你只需要知道这个就可以进入 家中,根本不需要记得门的颜色是什么。

用FPGA实现的流水灯VHDL代码

双击图标选择 bit 文件。右键图标选 择

可编辑

-------------精选文档-----------------

Program

可编辑

-------------精选文档-----------------

设计目的:

在 8 盏 LED 灯每隔一秒钟顺序循环提供高电平使 LED 亮,复位键使 LED 全部置低电平使 LED 灭,重新进行流ED(1) LED(2) LED(3) LED(4) LED(5) LED(6) LED(7)

entity LED_FLASH_VHD is Port ( clk : in STD_LOGIC;

可编辑

-------------精选文档-----------------

rst : in STD_LOGIC; LED_RUN : out STD_LOGIC_VECTOR (7 downto 0)); end LED_FLASH_VHD;

其中 cnt 实现记数功能,对时钟进行分频。 Step 实现让具体哪一盏灯亮。 使用引脚: 复位 rst(Y18)、时钟 clk(D11)、LED 灯(N19、 N15、 R20、R18、U20、

T18、U18、W20);

具体设计:

1、 打开设计软件 Xilinx ISE 11,新建工程 2、 新建 VHDL Module 设置代码,对时钟进行分频: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

可编辑

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

综合实验报告第四组组长:韩欢02081535陈洁钰02081536侯旭涛02081514高耀02081510李欣昊02081508李昊02081506FPGA基础试验之流水灯一、实验目的通过此实验进一步了解、熟悉和掌握Quartus II开发软件的使用方法及Verilog 语言的编程方法。

学习简单时序电路的设计分析和硬件测试。

二、实验内容1.熟悉信号产生板中的FPGA的普通I/O的连接;2.根据实际的流水灯分析时序,体会用Verilog语言的编程产生相应时序;3.熟悉集成开发工具Quartus II,学会使用Quartus II对Cyclone系列FPGA的程序开发、编译与调试;4.掌握Cyclone系列FPGA的程序加载,熟练掌握将.sof文件加载到实验板的FPGA中,实现流水灯的效果。

三、实验原理流水灯,顾名思义就是让LED像水一样的点亮。

如果把流水做慢动作播放,可以想象到其实就是移动,即:把水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水。

同样,如果使得最左边的灯先亮,然后通过移位,在其右侧的灯,从左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯。

初始状态时,四个灯都不亮,每来一个时钟脉冲,CLK,计数器就加1.这样通过移位依次点亮所有的灯,就形成了流水灯。

而当四个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态。

然后,再一次流水即可。

如果是右移位,就出现向右流水的现象;反之,向左流水。

四、实验要求控制4个LED进行花式显示,根据硬件设施设计两种模式:S0:从全亮到全灭,再到全亮,依次循环;S1:从LED0开始依次点亮,为LED1亮,LED2亮,LED3亮,后再LED2亮,LED1亮,LED0亮,不停循环。

即输出为:S0时,从0000到1111不停循环转换;S1时,0111,1011,1101,1110,1101,1011,0111不断循环。

五、实验步骤(1)建立工程(2)建立Verilog文件,编写相关程序(3)将verilog文件编译为可视化电路图文件(4)将可视化电路图文件添加输入输出组合成电路图文件(5)编译语法及验证原理图(6)根据需要分配管脚并进行编译(7)下载编译后得到的文件.sof(在线方式),.pof(离线方式)。

一般考虑用在线方式。

(8)显示实验结果六、电路符号:流水灯的电路符号如下图所示。

sw1为模式选择输入。

rst_n为复位信号,接高电平,sys_clk为时钟信号输入,led[3..0]为LED显示信号输出端。

七:设计方法:采用文本编辑法,即利用verilogHDL语言描述流水灯,代码如下:module liushuideng(sw1,sys_clk,rst_n,led); //接口定义input sys_clk,rst_n,sw1; //输入:系统时钟50MHz,复位输入output [3:0] led; //输出:3个led产生流水现象,轮流点亮+reg [25:0] count; //系统时钟频率过高,需要计数的方式来产生延时,使led保持状态一段时间reg [3:0] led; //led低电平点亮reg [2:0] flag; //状态转换的入口,发生变化的时候,点亮另外一个ledalways @(posedge sys_clk)beginif(!rst_n) //复位,给寄存器赋初值beginflag <= 3'b0;count <= 26'b0;end//else //sys_clk上升沿到来//beginif( count == 26'd20)begincount <= 26'd0; //count归零,便于下次重新开始计数if(flag == 3'b111) //当flag等于2’b10时,flag归零(实际上,当flag==2’b10时,要在下一次归零,即在flag==2’b11时,马上就变成2’b00,而并非当flag==2’b10时马上变为2’b00;)flag <= 3'b000;else //否则flag加一flag <= flag+3'b001;endelsecount <= count + 26'd1; //当count没计数到指定值是,count执行加一操作endalways @(posedge sys_clk)if(sw1==1'b1)begincase(flag) //由于flag会不断变化,并且flag在从一个值变成另一个值的时候,会保持一段很长的时间,我们利用它来产生流水灯现象3'b000: led <= 4'b0000; //点亮所有灯,都为低电平3'b001: led <= 4'b1111; //没有点亮灯,都为高电平3'b010: led <= 4'b0000; //点亮所有灯,都为低电平3'b011: led <= 4'b1111; //没有点亮灯,都为高电平3'b100: led <= 4'b0000; //点亮所有灯,都为低电平3'b101: led <= 4'b1111; //没有点亮灯,都为高电平3'b110: led <= 4'b0000; //点亮所有灯,都为低电平3'b111: led <= 4'b1111; //没有点亮灯,都为高电平default:led <= 4'b1111; //一般要设置一个缺省状态,三个led全部灭endcaseendelsebegincase(flag) //由于flag会不断变化,并且flag在从一个值变成另一个值的时候,会保持一段很长的时间,我们利用它来产生流水灯现象3'b000: led <= 4'b0111; //点亮第一个灯低电平点亮3'b001: led <= 4'b1011; 点亮第二个灯低电平点亮//++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++ +++++++++++++3'b010: led <= 4'b1101; //点亮第三个灯低电平点亮3'b011: led <= 4'b1110; //点亮第四个灯低电平点亮3'b100: led <= 4'b1101; //点亮第三个灯低电平点亮3'b101: led <= 4'b1011; //点亮第二个灯低电平点亮3'b110: led <= 4'b0111; //点亮第一个灯低电平点亮3'b111: led <= 4'b1111;default:led <= 4'b1111; //一般要设置一个缺省状态,三个led全部灭endcaseendendmodule七:仿真结果:1:当swl=1时,(1)时序仿真结果如图所示(2)功能仿真结果为:功能仿真没有时延。

2:当swl=0时,(1)时序仿真结果为:(2)功能仿真结果为:FPGA基础实验之正弦波形产生一、实验目的通过此实验进一步了解、熟悉和掌握Quartus II开发软件的使用方法及Verilog语言的编程方法。

学习简单时序电路的设计分析和硬件测试。

二、实验内容1.熟悉信号产生板中的FPGA的普通I/O的连接;2.根据实际的正弦波形产生时序,体会用Verilog语言的编程产生相应时序;3.熟悉集成开发工具Quartus II,学会使用Quartus II对Cyclone系列FPGA的程序开发、编译与调试;4.掌握Cyclone系列FPGA的程序加载,熟练掌握将.sof文件加载到实验板的FPGA中,实现正弦波形产生。

三、实验原理DDS(Direct Digital Synthesis)是一种应用直接数字合成技术来产生信号波形的方法。

DDS技术建立在采样定理的基础上,它首先对需要的信号波形进行采样、量化,然后存入存储器作为待产生信号的数据查询表。

在输出信号波形时,从数据表依次读出数据,产生数字信号。

四、实验步骤1、通过matlab产生一组正弦信号:a=1:1:1023;b=127*cos((1/512)*pi*a)+128;b=round(b’);将生成的1024个在1~255之间的数存入ROM之中。

2、将产生的数据保存为sin.hex文件;IP核的产生。

3、选中单口rom添加文件名。

4、将q output port 勾选去掉。

5、添加产生的sin.hex文件到rom中。

6、根据需要分配管脚并进行编译。

7、完成rom的设置,添加输入输出端口。

8、验证结果:利用波形仿真看结果,新建波形文件。

9、双击Name下面的空白处,点击NewFolder。

10、点击list。

11、点击”>>”。

12、将输入及输出添加到仿真文件中。

13、给相应的输入进行赋值;对时钟进行赋值。

14、点击工具栏中的时钟标志。

15、对a进行赋值,选出一段然后点击工具栏中的“?”选择以16进制显示。

16、赋值完毕后,开始时序仿真。

17、选择相应的仿真文件,开始仿真,完毕后查看report18、点击按幅度为5的显示,得到相应的波形,a和b的值决定了显示波形的频率及相位。

五、电路符号六、设计程序Rom1module rom1 (address,clock,q);input [9:0] address;input clock;output [7:0] q;wire [7:0] sub_wire0;wire [7:0] q = sub_wire0[7:0];altsyncram altsyncram_component (.clock0 (clock),.address_a (address),.q_a (sub_wire0),.aclr0 (1'b0),.aclr1 (1'b0),.address_b (1'b1),.addressstall_a (1'b0),.addressstall_b (1'b0),.byteena_a (1'b1),.byteena_b (1'b1),.clock1 (1'b1),.clocken0 (1'b1),.clocken1 (1'b1),.clocken2 (1'b1),.clocken3 (1'b1),.data_a ({8{1'b1}}),.data_b (1'b1),.eccstatus (),.q_b (),.rden_a (1'b1),.rden_b (1'b1),.wren_a (1'b0),.wren_b (1'b0));defparamaltsyncram_component.address_aclr_a = "NONE",`ifdef NO_PLIaltsyncram_component.init_file = "boxing.rif"`elsealtsyncram_component.init_file = "boxing.hex"`endif,altsyncram_component.intended_device_family = "Cyclone",altsyncram_component.lpm_hint = "ENABLE_RUNTIME_MOD=NO",altsyncram_component.lpm_type = "altsyncram",altsyncram_component.numwords_a = 1024,altsyncram_component.operation_mode = "ROM",altsyncram_component.outdata_aclr_a = "NONE",altsyncram_component.outdata_reg_a = "UNREGISTERED",altsyncram_component.widthad_a = 10,altsyncram_component.width_a = 8,altsyncram_component.width_byteena_a = 1;endmodulemodule my_add (clock,dataa,datab,result);input clock;input [31:0] dataa;input [31:0] datab;output [31:0] result;wire [31:0] sub_wire0;wire [31:0] result = sub_wire0[31:0];lpm_add_sub lpm_add_sub_component (.dataa (dataa),.datab (datab),.clock (clock),.result (sub_wire0)// synopsys translate_off,.aclr (),.add_sub (),.cin (),.clken (),.cout (),.overflow ()// synopsys translate_on);defparamlpm_add_sub_component.lpm_direction = "ADD",lpm_add_sub_component.lpm_hint = "ONE_INPUT_IS_CONSTANT=NO,CIN_USED=NO",lpm_add_sub_component.lpm_pipeline = 1,lpm_add_sub_component.lpm_representation = "UNSIGNED",lpm_add_sub_component.lpm_type = "LPM_ADD_SUB",lpm_add_sub_component.lpm_width = 32;endmodulemodule add(clk,a,b,c);input clk;input[31:0] a;input[31:0] b;output[31:0] c;reg[31:0] c;reg[31:0] d;initialbegind<=b;endalways @(posedge clk)beginc<=a+d;d<=c;endendmodules translate_off`timescale 1 ps / 1 ps// synopsys translate_onmodule rom (address,clock,q);input [9:0] address;input clock;output [7:0] q;wire [7:0] sub_wire0;wire [7:0] q = sub_wire0[7:0];altsyncram altsyncram_component (.clock0 (clock),.address_a (address),.q_a (sub_wire0),.aclr0 (1'b0),.aclr1 (1'b0),.address_b (1'b1),.addressstall_a (1'b0),.addressstall_b (1'b0),.byteena_a (1'b1),.byteena_b (1'b1),.clock1 (1'b1),.clocken0 (1'b1),.clocken1 (1'b1),.clocken2 (1'b1),.clocken3 (1'b1),.data_a ({8{1'b1}}),.data_b (1'b1),.eccstatus (),.q_b (),.rden_a (1'b1),.rden_b (1'b1),.wren_a (1'b0),.wren_b (1'b0));defparamaltsyncram_component.address_aclr_a = "NONE",`ifdef NO_PLIaltsyncram_component.init_file = "boxing.rif"`elsealtsyncram_component.init_file = "boxing.hex"`endif,altsyncram_component.intended_device_family = "Cyclone",altsyncram_component.lpm_hint = "ENABLE_RUNTIME_MOD=NO",altsyncram_component.lpm_type = "altsyncram",altsyncram_component.numwords_a = 1024,altsyncram_component.operation_mode = "ROM",altsyncram_component.outdata_aclr_a = "NONE",altsyncram_component.outdata_reg_a = "UNREGISTERED",altsyncram_component.widthad_a = 10,altsyncram_component.width_a = 8,altsyncram_component.width_byteena_a = 1;endmodule七、实验结果八、实验总结经过不断的实验,最终完成了该实验的基本要求,通过该信号发生器的设计,学习和掌握了DA转换,更加熟练地使用Verilog语言描述硬件电路和信号的输出,也更加熟练的掌握语言编程过程中的数据的控制,运用quartusII仿真和调用modelsim仿真。