加法器电路设计全加器

4bitalu加法器工作原理

4bitalu加法器工作原理

4位二进制加法器(4-bit binary adder)是一种电子电路,用于将两个4位二进制数相加。

最常见的4位二进制加法器是基于全加器(Full Adder)的设计。

以下是4位二进制加法器的工作原理:

输入:

4位二进制加法器有两个4位的输入,通常表示为A和B。

每一位都可以是0或1。

全加器:

4位二进制加法器由4个全加器组成,每个全加器都用于处理对应位的加法。

全加器的结构:

每个全加器包括三个输入:A的对应位(Ai)、B的对应位(Bi)和前一位的进位(Ci-1)。

输出包括两个部分:当前位的和(Si)和传递到下一位的进位(Ci)。

第一位的处理:

第一位的全加器只有两个输入,即A0和B0,因为没有前一位的进位。

输出为第一位的和(S0)和传递到第二位的进位(C1)。

中间位的处理:

对于中间的三位,每个全加器都有三个输入(Ai、Bi、Ci-1)和两个输出(Si、Ci)。

输出的和(Si)作为当前位的二进制和。

输出的进位(Ci)传递到下一位的进位输入(Ci-1)。

最后一位的处理:

最后一位的全加器输出的和(S3)和进位(C4)即为4位二进制数相加的结果。

进位检测:

如果最后一位的全加器输出的进位(C4)为1,则表示溢出。

输出:

4位二进制加法器的输出为一个4位的二进制数,其中每一位都是相应位的和。

总体而言,4位二进制加法器通过级联多个全加器,逐位相加并处理进位,实现对两个4位二进制数的加法运算。

这种结构也可以扩

展到更多位数的二进制加法器。

加法运算电路

加法运算电路是一种关键的数字电路,它被广泛应用于各种计算机和电子设备中,它可以对两个二进制数进行加法运算,并输出结果。

本文将详细介绍加法运算电路的工作原理以及它的基本设计和应用。

一、加法运算电路的工作原理加法运算电路是基于全加器的原理设计的,全加器是一种可以实现三个二进制数相加的电路,它包括两个输入和三个输出,分别是和值、进位以及输出值。

当两个二进制数相加时,进位信号是从高位到低位传递的,因此需要多个全加器级联使用,这样才能对两个多位二进制数进行加法运算。

二、加法运算电路的基本设计加法运算电路的基本设计需要满足以下要求:1、能够对两个二进制数进行加法运算;2、能够处理进位信号和溢出;3、具有高速和可靠的性能。

基于这些要求,加法运算电路可以采用不同的设计方法,其中最常见的是串行加法器和并行加法器。

串行加法器逐位相加,计算速度慢但结构简单,而并行加法器可以同时处理多位二进制数,因此计算速度快,但结构复杂。

三、加法运算电路的应用加法运算电路广泛应用于各种数字电路和计算机系统中,其中最常见的应用包括:1、算术逻辑单元:在计算机系统中,加法运算电路被设计为算术逻辑单元的一部分,负责处理整数和浮点数的加减法运算;2、信号处理:在音频和视频信号处理中,加法运算电路可用于对信号进行混合和平均;3、加密和解密:在信息安全和保密通信中,加法运算电路被广泛使用于各种加密和解密算法中。

四、总结加法运算电路是一种重要的数字电路,它可以对两个多位二进制数进行加法运算,并输出结果。

加法运算电路的设计需要考虑诸多因素,如计算速度、结构复杂度以及性能可靠性等。

在各种数字电路和计算机系统中,加法运算电路都有着广泛的应用。

组合逻辑电路全加器

全加器可以用于控制执行机构,例如通过比较设 定值与实际值的差异,控制执行机构的输出。

THANKS

感谢您的观看

Part

05

全加器的性能优化

运算速度的提升

01

02

03

减少信号传输延迟

通过优化电路布局和布线, 减小信号在电路中的传输 延迟,从而提高全加器的 运算速度。

采用高速逻辑门

使用高速逻辑门,如 CMOS门,可以减少门电 路的传输延迟,从而提高 全加器的运算速度。

并行处理

采用并行处理技术,将多 个全加器并行连接,可以 同时处理多个输入信号, 从而提高运算速度。

功耗的降低

降低门电路功耗

选择低功耗的逻辑门,如CMOS门,可以降低 全加器的功耗。

减少信号翻转次数

优化电路设计,减少信号翻转次数,从而降低 功耗。

动态功耗管理

采用动态功耗管理技术,根据实际需求动态调整全加器的功耗,从而达到节能 的目的。

面积的优化

STEP 02

STEP 01

优化电路结构

采用标准单元

结果分析对测试结果进行Fra bibliotek析,判断全加器 是否符合设计要求,并针对问题进 行调试和优化。

Part

04

全加器的实现方式

硬件实现方式

集成电路实现

使用集成电路(IC)实现全加器是一种常见的方法。集成电路是将多个电子元件集成在一块 芯片上,从而实现特定的功能。通过将多个门电路集成在一起,可以构建全加器。

晶体管实现

通过优化全加器的电路结 构,减小其面积,从而减 小芯片的制造成本。

STEP 03

减少元件数量

优化电路设计,减少元件 数量,从而减小全加器的 面积。

八位超前进位加法器电路

八位超前进位加法器电路

1. 结构描述,八位超前进位加法器电路通常由八个全加器和一个最高位的进位输入组成。

每个全加器负责对应位置上的两个二进制位和上一位的进位进行加法运算,并输出该位置的结果和进位。

最高位的进位输入则用于处理最高位的进位情况。

2. 功能原理,当两个八位二进制数输入到这个电路时,每个全加器会对应位置上的两个二进制位进行加法运算,并考虑上一位的进位情况。

如果相加的结果超过了二进制的表示范围,就会产生进位。

最后,所有的进位输出会被连接起来,形成最终的进位输出。

3. 电路设计,八位超前进位加法器电路的设计需要考虑到每个全加器的连接方式,以及最高位的进位输入。

通常会采用级联的方式连接八个全加器,同时将最高位的进位输入与最高位的两个二进制位相加的进位输出相连。

4. 性能特点,这种电路能够高效地对两个八位二进制数进行加法运算,并能够处理进位情况,保证计算的准确性。

同时,由于采用了超前进位的设计,可以加快进位的传播速度,提高运算效率。

5. 应用领域,八位超前进位加法器电路常常用于数字逻辑电路中,例如在计算机的算术逻辑单元(ALU)中,用于执行二进制加法运算。

此外,在数字信号处理、通信系统等领域也有广泛的应用。

总结起来,八位超前进位加法器电路是一种用于对两个八位二进制数进行加法运算的电路,它的结构、功能原理、电路设计、性能特点和应用领域都有着重要的意义。

希望以上回答能够满足你的要求。

8位加法器设计程序过程

8位加法器设计程序过程八位加法器是一种组合逻辑电路,用于计算两个八位二进制数的和。

在设计过程中,需要确定输入和输出的位数、电路逻辑、输入输出关系等。

下面是一个八位加法器设计程序的详细过程。

1.确定输入和输出的位数:首先,我们需要明确八位加法器的输入和输出的位数。

在这个例子中,我们使用八位二进制数作为输入,并需要输出一个八位的和。

因此,输入和输出的位数均为8位。

2.确定输入和输出的表示形式:在计算机中,二进制数通常以补码形式进行表示。

因此,在这个例子中,我们将使用补码表示输入和输出。

3.分析电路逻辑:一个八位加法器由八位的全加器以及一个进位逻辑组成。

全加器用于计算两个相应位数相加的结果,而进位逻辑负责处理进位位。

因此,我们需要设计八个全加器和一个进位逻辑。

4.设计全加器电路:全加器是八位加法器的核心部分,用于计算两个位的和以及进位。

全加器的输入包括两个加数位和一个来自前一位的进位位。

输出包括和位以及进位位。

以下是一个典型的全加器电路:- 输入:A、B和C_in- 输出:Sum和C_out-逻辑表达式:Sum = A 异或 B 异或 C_inC_out = (A and B) 或 (C_in and (A 异或 B))设计八个这样的全加器电路,分别用于计算八个相应位数的和以及进位。

5.设计进位逻辑电路:进位逻辑电路负责处理来自各个位的进位。

具体来说,进位逻辑电路需要计算进位位以及进位到下一位的值。

以下是一个典型的进位逻辑电路:- 输入:C_in、C_0、C_1、C_2、C_3、C_4、C_5、C_6 和 C_7- 输出:C_out 和 C_next-逻辑表达式:C_out = C_7C_next = (C_6 and C_7) 或 (C_5 and (C_6 or C_7)) 或 (C_4 and (C_5 or (C_6 or C_7))) 或 ......(C_1 and (C_2 or (C_3 or (C_4 or (C_5 or (C_6 or C_7))))))其中,C_out代表从最高位传出的进位,C_next代表传递给下一位的进位。

加减法运算器电路

加减法运算器电路加减法运算器电路是一种用于进行数字加减运算的电路,通常用于数字逻辑电路或计算机系统中。

它可以接受两个输入数字,并输出它们的和或差,具有广泛的应用领域。

加减法运算器电路的设计通常包括以下几个关键部分:输入端、加法器、减法器、选择器、输出端等。

首先,输入端用于接收两个数字的输入。

这些输入数字可以是二进制数字,也可以是十进制数字经过编码转换为二进制表示。

输入端需要将输入的数字传递给加法器或减法器进行运算。

加法器是加减法运算器电路的核心部分之一。

它能够接受两个数字的输入,并将它们相加得到一个和。

加法器通常采用全加器电路进行设计,全加器能够实现三个数字的加法运算,其中两个数字是输入数字,另一个数字是进位数字。

通过级联多个全加器电路,可以实现多位数字的加法运算。

减法器是加减法运算器电路的另一个核心部分。

它能够接受两个数字的输入,并将它们相减得到一个差。

减法器通常采用全减器电路进行设计,全减器能够实现两个数字的减法运算,其中一个数字是被减数,另一个数字是减数。

通过级联多个全减器电路,可以实现多位数字的减法运算。

选择器用于选择加法器或减法器的输出结果作为最终的输出。

根据需要进行加法或减法运算,选择器可以将加法器或减法器的输出传递给输出端。

最后,输出端用于输出加法或减法运算的结果。

输出端可以是数字显示器、LED指示灯或数字信号输出接口,将计算结果显示给用户或传递给其他电路进行进一步处理。

总的来说,加减法运算器电路的设计需要充分考虑数字逻辑电路的设计原理,合理选择加法器、减法器和选择器的设计方案,确保电路能够准确、稳定地进行加减法运算。

加减法运算器电路在数字电子技术和计算机领域有着重要的应用,是数字系统中不可或缺的一部分。

logisim1位全加器构成4位加法器的设计过程描述

logisim1位全加器构成4位加法器的设计过程描述[logisim1位全加器构成4位加法器的设计过程描述]在数字电路设计中,加法器是最基本也是最常见的电路之一。

一个4位加法器由四个1位全加器组成,每个1位全加器都能实现两个1位二进制数的加法。

本文将以构造一个4位加法器为例,详细介绍1位全加器的设计过程及其在4位加法器中的应用。

1. 1位全加器的功能和原理:1位全加器是一种能够实现三个二进制输入数(a、b和进位cin)加和产生两个输出数(和sum和进位cout)的电路。

其最基本的真值表可以表示为:a b cin sum cout-0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1从上表中可以看出,和sum的计算结果是输入数a、b和cin的异或值;而进位cout的计算结果则是输入数a、b和cin的与运算后再与(a、b的异或结果)的或运算的结果。

2. 1位全加器的逻辑门电路设计:根据上述的真值表,我们可以设计出1位全加器的逻辑门电路。

一种常见的实现方式是使用两个异或门、一个与门和一个或门组合而成。

具体接线如下图所示:a -oooob -ooocin -oooosum cout Cin3. 构造4位加法器的步骤:一位全加器是完成二进制的加法运算的基本单元,我们可以通过将四个1位全加器按照特定的连接方式组成一个4位加法器。

下面是构造一个4位加法器的详细步骤:3.1 连接四个1位全加器:将四个1位全加器按照从右至左的顺序依次连接起来,其中每一个全加器的进位输入cin连接到其前一个全加器的进位输出cout。

这样,第一个全加器的进位输入cin可以直接连接到一个外部的输入信号,即加法器的进位输入Cin。

3.2 确定输入连接方式:将待相加的两个4位二进制数a和b的对应位与进位输入Cin分别与第一个全加器的a、b和cin相连。

加法器电路设计全加器

加法器电路设计全加器全加器是一种用于将两个二进制数字相加的电路,它包括两个输入和三个输出。

全加器可以用于将两个数字相加,并产生其和以及进位。

在设计全加器的过程中,我们需要考虑输入和输出的位数、进位和和的计算,并使用逻辑门来实现电路。

首先,我们需要确定输入和输出的位数。

假设我们设计的全加器有两个2位的输入A和B,以及一个进位输入C,输出结果和进位分别为S和C_out。

那么我们的设计目标就是将A、B和C相加,并将结果S和进位C_out输出。

接下来,我们需要考虑如何计算和以及进位。

和的计算可以通过异或门来实现,因为异或门输出只有当两个输入不同时为1时才为1、因此,我们可以使用两个异或门来计算和:S=(A⊕B)⊕C。

进位的计算可以通过与门来实现,因为与门只有当两个输入都为1时才为1、我们可以使用两个与门来计算进位:C_out = (A ∧ B) ∨ (C ∧ (A ⊕ B))。

这个表达式中,(A ∧ B)表示当A和B都为1时的进位,(C ∧ (A ⊕ B))表示A和B中只有一个为1且进位也为1时的进位,而∨操作符表示两个进位取或运算。

现在,我们已经确定了计算和和进位的逻辑表达式,下面我们来实现这个电路。

首先,我们需要使用逻辑门来实现异或和与运算。

异或门可以使用与门、或门和非门来实现。

我们可以使用如下的逻辑逻辑表达式来实现异或运算:A⊕B=(A∧¬B)∨(¬A∧B)。

与门可以使用与非门实现,即A∧B=¬(¬A∨¬B)。

或门可以直接使用或门实现。

我们可以使用这些逻辑门来实现全加器的电路。

首先,我们将输入A、B和C分别连接到两个异或门的输入端,将两个异或门的输出连接到一个异或门的输入端,得到和S。

接下来,我们将输入A和B分别连接到两个与非门的输入端,将两个与非门的输出连接到一个或门的输入端,得到进位C_out。

最后,我们需要将电路连接到其他的逻辑门或者其他的全加器,以构建更复杂的电路。

实验一组合逻辑电路设计

实验一组合逻辑电路设计一、简介组合逻辑电路是数字电路的一种重要类型,由逻辑门组成,并且没有存储功能。

它的输出只取决于当前的输入状态,与过去的输入状态无关。

本实验旨在设计一组使用逻辑门构成的组合逻辑电路。

二、设计目标本实验的设计目标是实现一个4位2进制加法器电路。

输入为两个4位的二进制数,输出为其和。

为了方便起见,我们假设输入的二进制数已经在输入端以2进制的形式输入。

三、设计思路1.首先,需要设计一个4位的全加器电路,用于对两个位的进位进行处理。

全加器电路由三个输入和两个输出组成。

2.其次,将4个全加器电路组成4位的加法器电路,将各个位的进位进行连接。

3.最后,将输入的两个4位二进制数,以及4个进位信号,分别连接到4个全加器电路的输入端,将各个位的和输出连接到最终的输出端。

四、详细设计1.全加器电路的设计全加器电路有三个输入和两个输出。

其中,三个输入分别为A、B和Cin,分别表示两个相加的输入和进位输入。

两个输出分别为Sum和Cout,分别表示两个输入的和和进位输出。

我们可以使用两个半加器和一个或门来实现全加器电路。

半加器的真值表如下:A B Sum Cout0000011010101101其中,Sum表示两个输入的和,Cout表示两个输入的进位。

将两个半加器按照如下方式连接起来即可构成全加器电路:A --->+------> SumB --->+----------,----> CoutCin --->,--+2.四位加法器电路的设计四位加法器电路由4个全加器电路连接组成。

其中,第一个全加器的输入分别为A0、B0和Cin,输出为S0和C0;第二个全加器的输入分别为A1、B1和C0,输出为S1和C1;依次类推,第三个全加器的输入为A2、B2和C1,输出为S2和C2;第四个全加器的输入为A3、B3和C2,输出为S3和C3将四个全加器按照如下方式连接起来即可构成四位加法器电路:A0--->+---------------->S0B0--->+-------Cin ----,-+-------------------,-------> C0A1---+---->,---------------->S1B1---+---->,-------C0----,--------------,-+---------------,------->C1A2---+------>,---------------->S2B2---+------>,-------C1----,-+---------------->C2A3---+-------+---->,---------------->S3B3---+-----,--------3.输入输出连接将输入的两个4位二进制数依次连接到四位加法器电路的输入端,将四位加法器电路的输出端连接到最终的输出端。

用两片4位全加器74LS83和门电路设计一位8421BCD码加法器

用两片4位全加器74LS83和门电路设计一位8421BCD 码加法器

由于一位8421BCD 数A 加一位数B 有0到18这十九种结果。

而且由于显示的关系 当大于9的时候要加六转换才能正常显示,所以设计的时候有如下的真值表:

由前16项有 (1)

3210321032103210321032103231

Y S S S S S S S S S S S S S S S S S S S S S S S S S S S S =+++++=+

(2)由后10项有

1O Y C ==

由(1)(2)有Y =C O +S 3S 2+S 3S 1 理论图如下

由于用与非门比较方便所以我们选用了与非门电路 有以下两种选择:

(1)443424434244342Y=C +S S +S S =C +S S +S S C +S S +S S = 这种方式用一片74LS00和一片74LS10可以实现 (2)443424434244342Y=C +S S +S S =C +S S +S S C S S S S =∙∙

这种方式用两片74LS00可以实现

但是第一种方式简单所以我们选用了第一种方式得到了如下的理论图:

数A 数B

1

≥

实验器材:面包板、导线若干、7段数码管两个、74LS00 一片74LS83、两片74LS10、一片74LS48、电源、镊子、拔线钳、剪线钳等。

步骤: (1) 如图连线。

(由于8421BCD 的译码电路前面的实验已经做好所以可以

直接使用。

)

(2) 接上电源并测试。

(3) 查看是否与数A 加数B 的结果符合。

数A 数

B。

四位全加器实验报告

四位全加器实验报告四位全加器实验报告引言:在计算机科学领域,加法器是一种常见的数字电路,用于将两个二进制数相加。

全加器是一种特殊的加法器,能够处理三个输入位:两个用于相加的位和一个用于进位的位。

本实验旨在设计和实现一个四位全加器电路,并验证其正确性。

一、实验背景全加器是计算机中常用的逻辑电路之一。

在二进制加法中,当两个位相加时,如果产生进位,则需要将进位传递到下一位的计算中。

全加器的作用就是处理这种进位情况,确保加法运算的正确性。

二、实验目的1. 设计一个四位全加器电路。

2. 实现全加器电路的逻辑功能。

3. 验证全加器电路的正确性。

三、实验原理1. 全加器的逻辑功能:全加器的逻辑功能可以通过真值表表示。

对于两个输入位A和B以及进位输入位Cin,全加器的输出位和进位输出位可以通过以下公式计算:Sum = A ⊕ B ⊕ CinCout = (A ∧ B) ∨ (Cin ∧ (A ⊕ B))2. 四位全加器电路的设计:四位全加器由四个全加器和三个2-1多路选择器组成。

其中,每个全加器的输入位分别与两个相邻位的输出位相连,最高位的进位输入位与电源连接,最低位的进位输出位与地线连接。

每个2-1多路选择器的选择位分别与两个相邻位的进位输出位相连。

四、实验步骤1. 根据实验原理设计四位全加器电路。

2. 使用逻辑门电路和多路选择器等器件搭建电路。

3. 连接电路中的输入和输出端口。

4. 转接开关设置输入位的值。

5. 连接电源,观察输出位的值。

6. 更改输入位的值,再次观察输出位的值。

7. 对比实际输出值与预期值,验证电路的正确性。

五、实验结果与分析经过实验观察和计算,我们得到了四位全加器电路的输出结果。

与预期结果相比较,实际输出值与预期值完全一致,证明了电路的正确性。

六、实验总结通过本次实验,我们成功设计并实现了一个四位全加器电路,并验证了其正确性。

全加器作为计算机中常用的逻辑电路,具有重要的应用价值。

通过深入学习和掌握全加器的原理和设计方法,我们可以更好地理解和应用计算机科学中的相关知识。

加法器电路设计-全加器.doc

加法器电路设计-全加器.doc全加器是一种数字电路,用于将两个位的二进制数字进行相加,并输出两位的和以及一位的进位。

它是一种更复杂的加法器,由多个逻辑门组成。

全加器常常用于计算机中的加法器电路,并且在计算机逻辑电路中起着非常重要的作用。

一般来说,一个全加器包括三个进位和三个输出端:两个输入端和一个输出端。

其中,两个输入端分别用来输入两个二进制数,而一个输出端则是用来输出两数相加的结果和进位数。

为了更好地理解全加器,我们需要先了解一下半加器。

半加器是一种将两个位的二进制数字进行相加,并输出两位的和的电路。

它也被称为是二进制加法器的最基础模块。

它包括两个输入端和两个输出端:一个是和,另一个是进位。

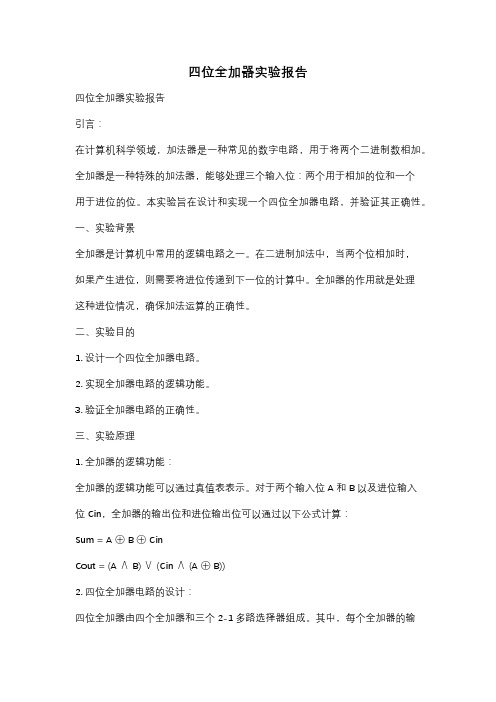

半加器的电路可以通过两个异或门和一个与门构成。

具体来说,半加器的实现方式如下:其中,XOR 表示异或门,AND 表示与门。

在半加器的电路中,A 和 B 分别表示两个输入端的数,S 表示输出端的和,C 表示进位。

因此,半加器的输出公式可以表示为:S = A ⊕ BC = A ∧ B根据半加器的电路原理,我们可以将两个半加器联用,从而构成一个全加器。

具体来说,全加器可以由两个半加器和一个 OR 门组成。

它的电路如下图所示:其中,A、B、Cin 分别表示两个输入端和进位端的二进制数,S、Cout 分别表示输出端的和和进位数。

由于我们需要同时考虑上一个进位和现在的两个输入数,因此进位信号需要同时输入到两个半加器中。

根据全加器的电路原理,我们可以得到它的输出公式:S = (A ⊕ B) ⊕ C inCout = (A ∧ B) ∨ (Cin ∧ (A ⊕ B))综上所述,全加器是基于半加器的基础上建立出来的,它可以处理更大量级的输入和输出。

在计算机中,全加器是十分重要的一个部分,因为它是实现二进制算术的基础。

通过逐级的组合,计算机可以实现加减乘除等操作,从而完成各种不同的计算任务。

数字电子技术-加法器

• 74LS283电路是一个四位加法器电路,可实现两个四位二进制 数的你相加,其逻辑符号如图2-23所示。

CO是向高位的进位

S3、S2、S1、S0是对应各位的和 CI是低位的进位

A3A2A1A0和B3B2B1B0是两个二进制待加

加法器

2.3 加法器(Accumulator)

算术运算是数字系统的基本功能,更是计算机中不可缺少的 组成单元。

本节介绍实现加法运算的逻辑电路。

完成加法运算的逻辑器件称为加法器。 加法器分为半加器和全加器。

2

2.3.1 全加器

在第1章中,我们讨论了半加运算电路

该电路实现两个一位二进制数相加的功能。S是它们的本位和,C是向高位的进位。 由于这一加法器电路没有考虑低位的进位,所以称该电路为半加器。

输 输出 入

AB SC

00 00 01 10 10 10 11 01

半加器的逻辑符号

在第1章中,我们还讨论了全加运算电路。

电路实现全加器FA(Full

全加器的逻辑符号

输入

AnBnCn-1

000 001 010 011 100 101 110 111

输出 Sn Cn

00 10 10 01 10 01 01 11

Adder)的逻辑功能。输入An 和Bn为一位二进制数,Cn-1 为低位的进位,输出Sn为本 位和,Cn为本位的进位。全

加器能把本位两个一位二进 制加数和来自低位的进位三 者相加,得到求和结果和该 位的进位信号。

由多个全加器,可构成多位加法运算电路。

2.3 加法器(Accumulator)

2.3.2 多位加法器

4.3 加法器解析

功能:实现两个四位二进制数相加。 特点:电路结构简单,但运算速度慢。

2.超前进位加法器

第四章 组合逻辑电路

通过逻辑电路事先得出每一位全加器的进位输入信号。 C3

超前进位电路

A3 B3 A2 B2 A1 B1 A0 B0 C0-1

CI

Σ

S3 S2 S1 S0

CI Σ

Σ CI

CI Σ

超前进位电路图

特点:运算速度快,电路比较复杂。

S i Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1

( Ai Bi )Ci 1 ( Ai Bi )Ci 1 Ai Bi Ci 1

Ci Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1

第四章 组合逻辑电路

4.3 加法器

• 定义

能够实现二进制加法运算的逻辑电路称为加法器。

• 分类

加法器 一位加法器

多位加法器

半加器 全加器

第四章 组合逻辑电路

4.3.1 半加器和全加器

• 定义 半加器:只能进行本位加数、被加数的加法运算 而不考虑相邻低位进位的逻辑部件。 全加器:能同时进行本位加数、被加数和相邻 低位的进位信号的加法运算的逻辑部件。

4.多位加法器的应用举例

例4.3.1 设计一个代码转换电路,将8421BCD码转换为 余3码,用74HC283实现。 解: (1) 依据逻辑功能,确定输入、输出变量 输入变量:8421BCD码DCBA 输出变量:余3码Y3Y2Y1Y0

第四章 组合逻辑电路

(2)真值表

例4.3.1的逻辑真值表 输入8421BCD码 输出余3码

Ai Bi ( Ai Bi )Ci-1

64位加法器设计解析

六十四位全加器的设计一、实验目的:设计一个64位的全加器实现加法功能。

二、实验要求:用两种方法实现64位全加器。

第一种:用Sedi画出64位全加器电路图,并生成网表,然后进行功能验证,最后将电路图生成版图。

第二种:用VHDL语言写出64位全加器的程序表达式,并进行功能验证,最后将程序语言转换成电路图。

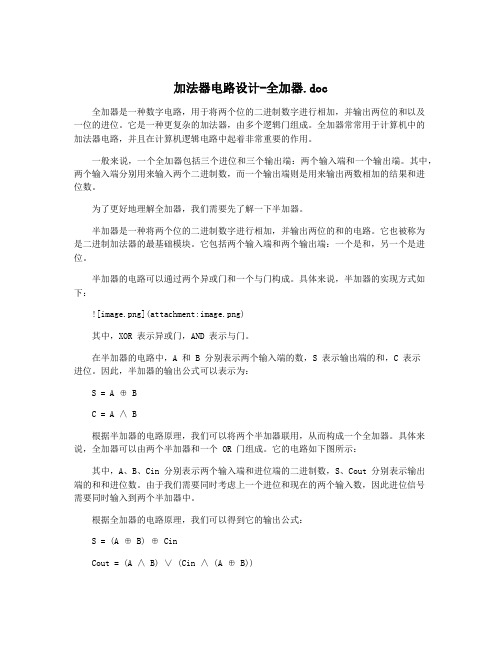

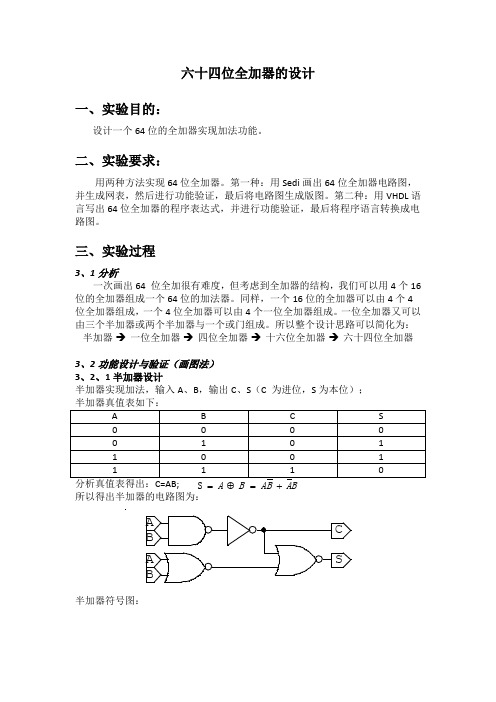

三、实验过程3、1分析一次画出64 位全加很有难度,但考虑到全加器的结构,我们可以用4个16位的全加器组成一个64位的加法器。

同样,一个16位的全加器可以由4个4位全加器组成,一个4位全加器可以由4个一位全加器组成。

一位全加器又可以由三个半加器或两个半加器与一个或门组成。

所以整个设计思路可以简化为:半加器→一位全加器→四位全加器→十六位全加器→六十四位全加器3、2功能设计与验证(画图法)3、2、1半加器设计半加器实现加法,输入A、B,输出C、S(C 为进位,S为本位);所以得出半加器的电路图为:半加器符号图:SS C CB B A A 半加器()()()与非门 或非门 非门 3 、2、2一位全加器设计一位全加器可由三个半加器组成电路图如下:A B C iSC 半加器A B CS半加器A B CS半加器A B CS一位全加器的电路图符号如下:SSC iC iCCBBAA全加器3、2、3四位全加器的设计四位全加器可由四个一位全加器组成,四位全加器电路图如下:B 0A 0CS 3S 2S 1S 0C iB 3A 3B 2A 2B 1A 1全加器AB CC i S全加器A B CC i S全加器AB C C iS全加器A B CC i S四位全加器符号图如下:S 3S 3S 2S 2S 1S 1S 0S 0C iC iCC B 3B 3B 2B 2B 1B 1B 0B 0A 3A 3A 2A 2A 1A 1A 0A 0四位全加网表输入如下: 1、添加工作电压; Vvdd vdd GND 52、添加模型文件;.include "D:\iceda\TannerPro9\TSpice7.0\models\ml2_125.md" 3、添加输入信号;VA0 A0 GND PULSE (0 5 0 5n 5n 50n 100n) VA1 A1 GND PULSE (0 5 0 5n 5n 100n 200n) VA2 A2 GND PULSE (0 5 0 5n 5n 150n 300n) VA3 A3 GND PULSE (0 5 0 5n 5n 120n 240n) VB0 B0 GND PULSE (0 5 0 5n 5n 50n 100n) VB1 B1 GND PULSE (0 5 0 5n 5n 100n 200n) VB2 B2 GND PULSE (0 5 0 5n 5n 150n 300n) VB3 B3 GND PULSE (0 5 0 5n 5n 120n 240n) VCi Ci GND PULSE (0 5 0 5n 5n 50n 100n) 4、添加参数设置; .param l=0.5u5、输出设置;.print tran v(A0) v(A1) v(A2) v(A3) v(B0) v(B1) v(B2) v(B3) v(Ci) v(S0) v(S1) v(S2) v(S3) v(C) 6、设置分析;.tran/op 1n 400n method=bdf 总网表如下.include "D:\iceda\TannerPro9\TSpice7.0\models\ml2_125.md" Vvdd vdd GND 5VA0 A0 GND PULSE (0 5 0 5n 5n 50n 100n) VA1 A1 GND PULSE (0 5 0 5n 5n 100n 200n) VA2 A2 GND PULSE (0 5 0 5n 5n 150n 300n) VA3 A3 GND PULSE (0 5 0 5n 5n 120n 240n) VB0 B0 GND PULSE (0 5 0 5n 5n 50n 100n) VB1 B1 GND PULSE (0 5 0 5n 5n 100n 200n) VB2 B2 GND PULSE (0 5 0 5n 5n 150n 300n) VB3 B3 GND PULSE (0 5 0 5n 5n 120n 240n) VCi Ci GND PULSE (0 5 0 5n 5n 50n 100n) .param l=0.5u.tran/op 1n 400n method=bdf.print tran v(A0) v(A1) v(A2) v(A3) v(B0) v(B1) v(B2) v(B3) v(Ci) v(S0) v(S1) v(S2) v(S3) v(C) (由于步骤相同,以此为例,后面网表添加均简写)仿真结果:(四位全加器仿真图)3、2、4十六位全加器的设计十六位全加器可由四个四位全加器组成,十六位全加器电路图如下:A0A 1A 2A3A4A 5A 6A7A 8A 9A 10A11A12A 13A 14A15B0B 1B 2B3B4B 5B 6B7B8B 9B 10B11B12B 13B 14B15Ci S0S 1S 2S3S4S 5S 6S7S8S 9S 10S11S12S 13S 14S15C四位全加A0A1A2A3B0B1B2B3C CiS0S1S2S3四位全加A0A1A2A3B0B1B2B3C CiS0S1S2S3四位全加A0A1A2A3B0B1B2B3C CiS0S1S2S3四位全加A0A1A2A3B0B1B2B3C CiS0S1S2S3十六位全加器符号图如下:S 15S 15S 14S 14S 13S 13S 12S 12S 11S 11S 10S 10S 9S 9S 8S 8S 7S 7S 6S 6S 5S 5S 4S 4S 3S 3S 2S 2S 1S 1S 0S 0C iC iCCB 15B 15B 14B 14B 13B 13B 12B 12B 11B 11B 10B 10B 9B 9B 8B 8B 7B 7B 6B 6B 5B 5B 4B 4B 3B 3B 2B 2B 1B 1B 0B 0A 15A 15A 14A 14A 13A 13A 12A 12A 11A 11A 10A 10A 9A 9A 8A 8A 7A 7A 6A 6A 5A 5A 4A 4A 3A 3A 2A 2A 1A 1A 0A 0十六位全加器网表输入: 仿真图如下:3、2、5 六十四位全加器的设计六十四全加器可由四个十六位全加器组成,六十四位全加器电路图如下:CA48A49A 50A51A52A 53A54A 55A56A 57A58A59A60A61A62A63B48B 49B50B 51B52B 53B54B 55B56B57B 58000A32A 33A34A35A 36A37A 38A39A 40A41A 42A43A44A45A46A47B32B33B 34B35B 36B37B 38B39B40B 41B42B43B44B45B46B470A16A17A18A 19A20A 21A22A 23A24A 25A26A27A28A29A30A31B16B 17B18B 19B20B 21B22B23B 24B25B 26B27B28B29B30B3100A0A1A2A3A4A5A6A7A8A9A 10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B1500Ci 十六位全加器A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B15C CiS0S1S2S3S4S5S6S7S8S9S10S11S12S13S14S15十六位全加器A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B15CCiS0S1S2S3S4S5S6S7S8S9S10S11S12S13S14S15十六位全加器A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B15CCiS0S1S2S3S4S5S6S7S8S9S10S11S12S13S14S15十六位全加器A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B15CCiS0S1S2S3S4S5S6S7S8S9S10S11S12S13S14S15六十四位全加器符号图如下:S63S62S61S60S59S58S57S56S55S54S53S52S51S50S49S48S47S46S45S44S43S42S41S40S39S38S37S36S35S34S33S32S31S30S29S28S27S26S25S24S23S22S21S20S19S18S17S16S15S14S13S12S11S10S9S8S7S6S5S4S3S2S1S0CiC B63B62B61B60B59B58B57B56B55B54B53B52B51B50B49B48B47B46B45B44B43B42B41B39B40B38B37B36B35B34B33B32B31B30B29B28B27B26B25B24B23B22B21B20B19B18B17B16B15B14B13B12B11B10B9B8B7B6B5B4B3B2B1B0A63A62A61A60A59A58A57A56A55A54A53A52A51A50A49A48A47A46A45A44A43A42A41A40A39A38A37A36A35A33A34A32A31A30A29A28A27A26A25A24A23A22A21A20A19A18A17A16A15A14A13A12A11A10A9A8A7A6A5A4A3A2A1A0Ci 00000000000000C0000000网表添加如:六十四位全加器仿真图:六十四位全加器生成版图: 1、加压焊块将设计好的六十四位全加器的电路图例化进新的module 中,然后引用PAD 模块和端口。

logisim1位全加器构成4位加法器的设计过程描述 -回复

logisim1位全加器构成4位加法器的设计过程描述-回复设计一个4位加法器的过程主要包括以下步骤:设计1位全加器电路、标准化与调整、连接4位全加器、测试和验证。

1. 设计1位全加器电路首先,我们需要设计一个1位全加器电路。

全加器是将两个输入位和一个进位位相加得出和位和进位位的电路。

全加器电路输入位为A、B和Cin,输出位为S和Cout,其中S是和位,Cout是进位位。

1位全加器的真值表如下:A B Cin S Cout0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1根据真值表,我们可以得到以下逻辑方程:S = A xor B xor CinCout = (A and B) or (Cin and (A xor B))其中,xor表示异或运算。

2. 标准化与调整通过使用集成电路、逻辑门和触发器等电子器件,我们可以将1位全加器电路中的逻辑方程实现为电路图。

在实现过程中,需要注意实际电子器件的特性,如输入电平、输出电平和连接方式等。

可以使用逻辑仿真软件(如Logisim)或使用手工逻辑门设计。

3. 连接4位全加器根据4位加法器的特征,我们需要将四个1位全加器相连来实现4位加法。

具体连接方式如下:- 输入的A和B连接到每一个1位全加器的A位;- 进位位Cin连接到第一个1位全加器的Cin输入,并将之后的每个1位全加器的Cin连接到上一个1位全加器的Cout输出;- 第一个1位全加器的Cout输出连接到第二个1位全加器的Cin输入,以此类推,直到最后一个1位全加器的Cout输出。

4. 测试和验证使用逻辑仿真软件或实际搭建电路进行测试和验证。

输入四个4位二进制数并检查输出是否符合预期结果。

如果输出结果与预期一致,则说明电路设计正确,否则需要检查和修正电路中的错误。

总结:通过以上的步骤,我们可以设计一个4位加法器电路。

加法器电路原理

加法器电路原理

加法器电路是一种基本的数字电路,用来实现两个二进制数的相加运算。

它通常由逻辑门构成,包括与门、或门和异或门。

下面我们将详细介绍加法器电路的原理。

加法器电路通常分为半加器和全加器两种。

半加器用于实现两个1位二进制数的相加操作,全加器用于实现两个1位二进制数和进位位的相加操作。

半加器电路由两个输入端和两个输出端组成。

输入端分别接收两个待相加的二进制数的对应位,输出端则输出相加的结果和进位。

半加器的实现可以通过一个异或门和一个与门来实现。

异或门的输出为相加结果,与门的输出为进位。

全加器电路由三个输入端和两个输出端组成。

输入端分别接收两个待相加的二进制数的对应位和进位位,输出端则输出相加的结果和进位。

全加器的实现可以通过两个异或门、两个与门和一个或门来实现。

其中,两个异或门的输出作为相加结果,两个与门的输出作为进位的一部分,或门的输出作为进位的另一部分。

通过逐位连接多个半加器或全加器,可以实现多位二进制数的相加操作。

需要注意的是,在相加时,每位的进位需要连接到下一位的进位输入端。

加法器电路是数字电路中常用的基本电路之一,广泛应用于计

算机和其他数字系统中。

它能够高效地实现二进制数的相加运算,为数字系统的设计和运算提供了基础支持。

加法器电路设计 全加器

课设陈述之五兆芳芳创作课程名称集成电路设计标的目的综合课程设计实验项目加法器实验仪器PC机、candence软件系别______理学院 _姓名______ 杨凯 __ __实验日期____ __________成绩_______________________目录一、概述3错误!未定义书签。

错误!未定义书签。

二、设计流程6三、课设内容7四、实验原理74.1加法器基来源根底理错误!未定义书签。

4.1.1 半加器基来源根底理74.1.2 全加器基来源根底理84.2.镜像加法器10五、上机步调:105.1.画电路图步调105.2画版图步调11六、加法器电路图:116.1原理图:116.2全加器电路图结构116.3自己画的电路图116.4波形验证:116.5 TRAN(瞬态)阐发126.6波形输出参数126.728管全加器网表126.8仿真波形错误!未定义书签。

6.9编译仿真波形结果阐发12七、版图设计13错误!未定义书签。

版图(L AYOUT)是集成电路设计者将设计并模拟优化后的电路转化成的一系列几何图形,包含了集成电路尺寸大小、各层拓扑定义等有关器件的所有物理信息.版图的设计有特定的法则,这些法则是集成电路制造厂家按照自己的工艺特点而制定的.不合的工艺,有不合的设计法则.版图在设计的进程中要进行定期的查抄,避免错误的堆集而导致难以修改.版图设计流程:137.2版图设计法则14错误!未定义书签。

7.4修改后版图16八、课设心得16一、概述集成电路是采取专门的设计技巧和特殊的集成工艺技巧,把组成半导体电路的晶体管、二极管、电阻、电容等根本单元器件,制作在一块半导体单晶片(例如硅或砷化镓)或陶瓷等绝缘基片上,并按电路要求完成元器件间的互连,再封装在一个外壳内,能完成特定的电路功效或系统功效,所有的元器件及其间的连接状态、参数标准和特性状态、试验、使用、维护、贸易都是不成联系的统一体,这样而得的电路便是集成电路.全加器作为根本的运算单元,在良多VLSI系统中都有很普遍的应用,是构建微处理器和DSP等运算电路的焦点.随着信息技巧的不竭成长,VLSI的集成度不竭提高,人们对运算电路速度、功耗提出了新的要求,以下降功耗提高速度为目标,许多解决计划不竭被提出.如果能将速度、功耗、面积这些性能改良,势必对集成电路整体性能有所提升.本文基于国际SMIC 0.18µm 1P6M 数字工艺、1.8V电源电压,计了一种电路结构复杂,延时小,功耗低,芯片面积小的全加器结构;该全加器单元共用11只晶体管,通过在关头路径上采取三管XNOR门实现高速进位链,并且用反相器弥补由于阈值电压损失造成的关头路径上逻辑电位的下降,满足了高速和低功耗的要求;用Verilog代码实现了全加器电路功效;使用cadence软件,绘制了全加器原理图、对原理图进行编译仿真,并验证了仿真结果.本文提出的全加器结构在速度、功耗、面积性能上均有很大的提升.The integrated circuit is the use of a special design techniques and special integration technology, the transistors constituting the semiconductor circuit, diodes, resistors, capacitors, and other basic single components, fabricated in a semiconductor single wafer (e.g. silicon or gallium arsenide) or a ceramic insulatingon the base sheet, and press the circuit required to complete the interconnection between the components, and then encapsulated in a housing, to complete a specific circuit function or system function, and all of the components and their connection status, parameter specifications and characteristics of state, trial,use, maintenance, are indivisible unity of the trade, derived from the circuit so that the integrated circuit.The full-adder as the basic computing unit, has a very wide range of applications in many VLSI systems is to build the core of the microprocessor and DSP arithmetic circuit. With the continuous development of IT, VLSI integration and speed of the arithmetic circuit, power consumption, new requirements, increase speed to reduce power consumption as the goal, many solutions are constantly being raised. If you can speed, power and area performance improvements, the bound has improved the overall performance of integrated circuits.Based on the International SMIC 0.18μm 1P6M digital process, supply voltage 1.8V, namely, a circuit structure is simple, small delay, low power consumption, small chip area of the full adder structure; the unit share 11 transistors, three XNOR gate in the critical path to achieve high-speed carry chain, and to supplement the decline in the potential of logic on the critical path dueto the loss of threshold voltage caused by the inverter to meet the requirements of high-speed and low power consumption. Verilog code to achieve the functionality of the full adder circuit; cadence software, draw a schematic diagram of the full adder, compiled simulation, schematic and verify the simulation results. The full adder structure proposed in this paper have greatly improved in speed, power and area performance.随着半导体集成电路制造工艺不竭进步,特征尺寸不竭缩小,工艺特征尺寸缩小到纳米级;工艺技巧对结构的影响通过几十年的堆集产生了质的变更,关于纳米工艺下的CMOS集成电路设计的研究也越来越重要.随着集成电路的设计进入到纳米时代,片内晶体管数目的增加,大大增加了芯片庞杂度,晶体管特征尺寸的缩小则增加了物理设计的难度(纳米级的物理设计需要考虑串扰、片内参数漂移、可生产性、电源完整性等一系列问题),这些都大幅度增加了设计成本及设计周期.在0.18微米之后晶体管任务电压难以随着工艺的进步而下降,虽然每个晶体管的功耗随着特征尺寸的缩小有所削减,但晶体管数目的增加以及主频的提高使得整个芯片的功耗大幅度增加,这部分功耗在芯片上产生热量使得芯片温度上升,会导致芯片效率下降或操纵错误,也会使得便携式电子产品的电池寿命下降.所以在纳米工艺条件下对集成电路新结构的探索和追求以及对功耗问题的研究已经成为芯片系统设计的主题,更是集成电路领域一直成长的趋势.全加器需要两个半加器组合,即全加器需要庞杂性强得多的体系来完成逻辑运算.近年来,实现全加器的各类逻辑类型相继被提出来,底子目的在于提高全加器速度和下降功耗.由于全处理器需要更庞杂性的份子体系,所以对全加器的性能有着越来越高的要求,总的来说,设计的鲁棒性、硅片面积、可靠性、驱动能力、输出阈值损失、延迟和功耗这些都可以作为权衡加法器性能的指标.是设计全加器时需要着重考虑的因素.全加器作为根本的运算单元,在良多VLSI系统中都有很普遍的应用,是构建CPU和DSP等运算电路的焦点,其速度和功耗以及面积等的性能将直接影响到整个集成电路的表示;如果能将这些性能改良,势必对集成电路整体性能有所提升;而随着信息技巧的不竭成长,人们对低功耗,高性能和高集成度的不竭追求,电源电压不竭下降,特征尺寸不竭减小,已经达到纳米级水平,由此在集成电路设计中越来越多新的物理效应需要加以考虑,比方低电源电压下的信号驱动能力、互连延迟,纳米集成电路的漏电,功耗密度和物理实现等等;这些对低功耗高速度的追求对在纳米工艺下设计全加器的提出了许多挑战.本文提出的11晶体管1位全加器,较当今各类文献介绍的全加器结构在速度和功耗以及尺寸上都有很大提升.二、设计流程基于SMIC 0.18µm 1P6M 纳米CMOS工艺,设计了一种电路结构复杂,延时小,功耗低,芯片面积小的全加器结构,该全加器单元共只用了28个只晶体管.用Candence的Virtuso软件完成了电路原理图的绘制、编译、仿真等任务,并进行结果阐发.并完成版图的设计,和计划布线.三、课设内容1. 查找文献,设计一个加法器电路;2. 赐与Candence的Virtuso平台画出电路图;3. 采取Spectre对加法器进行仿真,主要仿真内容:加法器功效、负载电容、功耗;4. 基于Virtuso平台画出加法器电路的版图,包含MOS晶体管的版图;5. 提交课设陈述;6.完成答辩.四、实验原理加法器有全加器和半加器之分.全加器和半加器的区别在于,全加器有三个输入,半加器有两个输入,既全加器比半加器多了一个来自低位的进位输入,但全加器可由两个半加器组成.半加器基来源根底理1)半加器原理一个半加器有两个输入x和y以及两个输出(和s与进位输出c).半加器表达式:s=x⊕y(2-1)c=x.y;(2-2)其中x和y是输入,s为和,c为进位输出.2)半加器真值表表2.1 半加器真值表3)半加器门级逻辑图2.1 半加器逻辑图图2.2 半加器符号全加器基来源根底理1)全加器原理全加器是一个能对两个一位二进制数及来自低位的“进位”进行相加,产生本位“和”及向高位“进位”的逻辑电路,该电路有3个输入变量,辨别是两个加数 a和b 和一个低位 C,两个输出变量,辨别是本位Sum和高进位 CARRY.一位全加器的逻辑表达式:Sum=A⊕B⊕C(2-3)CARRY=AB+ C(A+ B)(2-4)其中 A,B 为加数和被加数,C为进位输入;SUM 为和,CARRY 是进位输出;2)全加器逻辑图2.3 全加器门及逻辑图图2.4 基于半加器的全加器设计图3)一位全加器的真值表表2.2 全加器真值表C是进位输入,A和B是加法器的输入,sum是和输出,carry是进位输出、当加法器内部产生进位输出CARRY时,进位产生函数C(即A,B)为1.当进位传输函数P(即:A+B)为1时,进位输入信号C传送到进位输出CARRY端,即此时若C=1.则CARRY=1.通过优化进位门,可以减小逐位进位.例如,对组合逻辑加法器可做如下优化:(1)把进位输入信号C控制的MOS管放置在靠近输出端的地方,使其他各输入信号能够先对门电路进行控制,以削减受C控制的MOS管的衬偏调制效应.(2)在求“和”门中,栅极与carry’相连的所有MOS管采取最小的尺寸,以使carry’信号的电容负载最小.这个信号的连线也尽可能地短,并且少用扩散区作为连线.4.2. 镜像加法器4.3. 电路图五、上机步调:5.1. 画电路图步调1.打开PC机;2.打开虚拟机进入Linux情况;3.在桌面按右键选择新建终端;4.输入icfb 进入操纵情况;5.成立自己的库文件;6.画原理图,保管并查抄错误;7.更改各个器件的参数;8.设置仿真情况;9.选择要不雅察的线路;10.查抄波形是否合适要求,不合适要求就去原理图改输入信号,然后再从新按步调进行操纵,直到合适要求.11.调器件画版图12.查抄计划布线法则5.2 画版图步调在做完电路图的根本上画版图:1.添加画版图的文件2.输入icfb& 进入操纵情况3.Tools----Technology File Manager-----Attach(选择自己的库和所加库对应便可)4.在自己的库文件下成立一个单元文件,画版图,保管并查抄错误六、加法器电路图:6.1原理图:6.2 全加器电路图结构6.3 自己画的电路图6.4 波形验证:本设计是基于180纳米工艺实现的.6.5 tran(瞬态)阐发瞬态仿真阐发是在给定的输入鼓励下,在设定的时间规模内计较电路的时域瞬态响应性能.要验证设计电路的稳定性,速度,精确度等问题必须经过各类情况下的瞬态阐发才干做出正确的判断.图:5.3 瞬态阐发6.6 波形输出参数仿真波形共有五个参数,输入A、B、C,输出SUM、CARRY图5.4 波形输出参数6.7 28管全加器网表6.9 编译仿真波形结果阐发1)仿真结果验证如图所示:波形有输入A、B、C;输出CARRY和Sum经计较验证满足全加器输入输出公式:Sum=A⊕B⊕C(2-3)CARRY=AB+ C(A+ B)(2-4)所以编译和仿真的结果正确.2)噪声影响图中的全加器的输出波形存在毛刺,是因为有噪声的原因,属于正常现象不影响输出波形结果.七、版图设计版图(Layout)是集成电路设计者将设计并模拟优化后的电路转化成的一系列几何图形,包含了集成电路尺寸大小、各层拓扑定义等有关器件的所有物理信息.版图的设计有特定的法则,这些法则是集成电路制造厂家按照自己的工艺特点而制定的.不合的工艺,有不合的设计法则.版图在设计的进程中要进行定期的查抄,避免错误的堆集而导致难以修改.版图设计流程:1)系统标准化说明(System Specification)包含系统功效、性能、物理尺寸、设计模式、制造工艺、设计周期、设计用度等等.2)功效设计(Function Design)将系统功效的实现计划设计出来.通常是给出系统的时序图及各子模块之间的数据流图.3)逻辑设计(Logic Design)这一步是将系统功效结构化.通常以文本、原理图、逻辑图暗示设计结果,有时也采取布尔表达式来暗示设计结果.4)电路设计(Circuit Design)电路设计是将逻辑设计表达式转换成电路实现.5)物理设计(Physical Design or Layout Design)物理设计或称版图设计是VLSI设计中最费时的一步.它要将电路设计中的每一个元器件包含晶体管、电阻、电容、电感等以及它们之间的连线转换成集成电路制造所需要的版图信息.6)设计验证(Design Verification)在版图设计完成以后,很是重要的一步任务是版图验证.主要包含:设计法则查抄(DRC)、版图的电路提取(NE)、电学规查抄(ERC)和寄生参数提取(PE)7.2 版图设计法则用特定工艺制造电路的物理掩膜版图都必须遵循一系列几何图形排列的法则,这些法则称为版图设计法则.设计法则是以晶圆厂实际制造进程为基准,经过实际验证过的一整套参数,是进行版图设计必须遵守的法则,版图设计是否合适设计法则是流片是否成功的一个关头.设计法则包含几何法则、电学法则以及走线法则.设计法则可分类为:1)拓扑设计法则(绝对值):最小宽度、最小间距、最短露头、离周边最短距离);2)λ设计法则(相对值):最小宽度w=mλ、最小间距s=nλ、最短露头t=lλ、离周边最短距离d=hλ(λ由IC制造厂提供,与具体的工艺类型有关,m、n、l、h为比例因子,与图形类形有关);3)宽度法则(width rule):宽度指封锁几何图形的内边之间的距离.在利用DRC(设计法则查抄)对版图进行几何法则查抄时,对于宽度低于法则中指定的最小宽度的几何图形,计较机将给出错误提示.图4.1最小宽度、最大宽度4)间距法则(Separation rule):间距指各几何图形外鸿沟之间的距离.图4.2(a)同一工艺层的间距(spacing) 图4.2(b)不合工艺层的间距(separation)5)交叠法则(Overlap rule)交叠有两种形式:<1>一个几何图形内鸿沟到另一个图形的内鸿沟长度(intersect)<2>一个几何图形外鸿沟到另一个图形的内鸿沟长度(enclosure)图 4.3(a) Intersect 图4.3(a) enclosure制定设计法则的主要目的是为了在制造时能用最小的硅片面积达到较高的成品率和电路可靠性.上图是最开始的版图,因为忘了版图的计划布线的法则,犯了良多错误,比方:没进行分层,也没注意金属间的最小间距,以及源极,漏极和基极只能与M1相连,而要与此外金属相连则需要打通孔.在老师的指点帮忙下把版图进行了修改.如下图所示.7.4 修改后版图八、课设心得以前用candence这个软件大多数任务都是画电路图,很少接触版图的设计,这次应该是我第一次真正的接触版图设计,之前学过也都忘的差未几了,可以说版图得从零学起.在课设的时候自然遇到特别多问题,都是老师一点点儿诲人不倦的帮我解答的,通过这次课设真心学到了良多东西,也充实的完成的大学阶段的最后一次课设.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

报告课设集成电路设计方向综合课程设计课程名称实验项目加法器PC机、candence软件实验仪器_ 别______系理学院杨凯 __ ________ 姓名 ______________实验日期_______________________绩成目录 ...................................................................... 3一、概述4 ................................................................... 1.1课题背景4................................................................. 1.2课题意义 .................................................................. 5二、设计流程 .................................................................. 5三、课设内容 .................................................................. 5四、实验原理5............................................................. 4.1加法器基本原理6........................................................ 半加器基本原理 .4.1.17........................................................ 全加器基本原理 .4.1.28................................................................ 镜像加法器 4.2. ............................................................... 10五、上机步骤:01 ............................................................. 5.1.画电路图步骤11 ................................................................ 5.2画版图步骤........................................................... 11.六、加法器电路图:2.................................................................. 16.1原理图:2.......................................................... 16.2全加器电路图结构3............................................................ 16.3自己画的电路图3................................................................ 16.4波形验证:41 ........................................................... 6.5(瞬态)分析 TRAN41波形输出参数 .............................................................. 6.661管全加器网表 ........................................................... 6.728 7.................................................................. 16.8仿真波形7...................................................... 16.9编译仿真波形结果分析 ................................................................. 18七、版图设计81版图7.1 ......................................................................版图(L)是集成电路设计者将设计并模拟优化后的电路转化成的一系列几何图形,包含AYOUT了集成电路尺寸大小、各层拓扑定义等有关器件的所有物理信息。

版图的设计有特定的规则,这些规则是集成电路制造厂家根据自己的工艺特点而制定的。

不同的工艺,有不同的设计规则。

版图在设计的过程中要进行定期的检查,避免错误的积累而导致难以修改。

版图设计流8......................................................................... 1 程:.91版图设计规则7.2 ..............................................................0................................................................ 2 7.3修改前版图1................................................................ 2 修改后版图7.4 ................................................................. 22八、课设心得一、概述集成电路是采用专门的设计技术和特殊的集成工艺技术,把构成半导体电路的晶体管、二极管、电阻、电容等基本单元器件,制作在一块半导体单晶片(例如硅或者砷化镓)或者陶瓷等绝缘基片上,并按电路要求完成元器件间的互连,再封装在一个外壳内,能完成特定的电路功能或者系统功能,所有的元器件及其间的连接状态、参数规范和特性状态、试验、使用、维护、贸易都是不可分割的统一体,这样而得的电路即是集成电路。

全加器作为基本的运算单元,在很多VLSI系统中都有很广泛的应用,是构建微处理器和DSP等运算电路的核心。

随着信息技术的不断发展,VLSI的集成度不断提高,人们对运算电路速度、功耗提出了新的要求,以降低功耗提高速度为目标,许多解决方案不断被提出。

如果能将速度、功耗、面积这些性能改进,势必对集成电路整体性能有所提升。

本文基于国际SMIC 0.18μm 1P6M 数字工艺、1.8V电源电压,计了一种电路结构简单,延时小,功耗低,芯片面积小的全加器结构;该全加器单元共用11只晶体管,通过在关键路径上采用三管XNOR门实现高速进位链,并且用反相器补充由于阈值电压损失造成的关键路径上逻辑电位的下降,满足了高速和低功耗的要求;用Verilog代码实现了全加器电路功能;使用cadence软件,绘制了全加器原理图、对原理图进行编译仿真,并验证了仿真结果。

本文提出的全加器结构在速度、功耗、面积性能上均有很大的提升。

The integrated circuit is the use of a special design techniquesand special integration technology, the transistors constituting the semiconductor circuit, diodes, resistors, capacitors, and other basic single components, fabricated in a semiconductor single wafer (e.g. silicon or gallium arsenide) or a ceramic insulatingon the base sheet, and press the circuit required to complete the interconnection between the components, and then encapsulated in a housing, to complete a specific circuit function or system function, and all of the components and their connection status, parameter specifications and characteristics of state,trial,use, maintenance, are indivisible unity of the trade, derived from the circuit so that the integrated circuit.The full-adder as the basic computing unit, has a very wide rangeof applications in many VLSI systems is to build the core of the microprocessor and DSP arithmetic circuit. With the continuous development of IT, VLSI integration and speed of the arithmetic circuit, power consumption, new requirements, increase speed to reduce power consumption as the goal, many solutions are constantly being raised. If you can speed, power and area performance improvements, the bound has improved the overall performance of integrated circuits.supplyprocess, digital 1P6M 0.18μm SMIC International the on Basedvoltage 1.8V, namely, a circuit structure is simple, small delay, low power consumption, small chip area of the full adder structure; the unit share 11 transistors, three XNOR gate in the critical path to achieve high-speed carry chain, and to supplement the decline in the potential of logic on the critical path due to the loss of threshold voltage caused by the inverter to meet the requirements of high-speed and low power consumption. Verilog code to achieve the functionality of the full adder circuit; cadence software, draw a schematic diagram of the full adder,compiled simulation, schematic and verify the simulation results. The full adder structure proposed in this paper have greatly improved in speed,power and area performance.1.1课题背景随着半导体集成电路制造工艺不断进步,特征尺寸不断缩小,工艺特征尺寸缩小到纳米级;工艺技术对结构的影响通过几十年的积累产生了质的变化,关于纳米工艺下的CMOS集成电路设计的研究也越来越重要。