MEMORY存储芯片W25Q32JVSSIQ中文规格书

MEMORY存储芯片MT25QU256ABA1EW7-0SIT中文规格书

Serial NOR Flash Memory 1.8V , Multiple I/O, 4KB, 32KB, 64KB, Sector Erase MT25QU256ABAFeatures•SPI-compatible serial bus interface•Single and double transfer rate (STR/DTR)•Clock frequency –166 MHz (MAX) for all protocols in STR–90 MHz (MAX) for all protocols in DTR•Dual/quad I/O commands for increased through-put up to 90 MB/s•Supported protocols: Extended, Dual and Quad I/Oboth STR and DTR•Execute-in-place (XIP)•PROGRAM/ERASE SUSPEND operations•Volatile and nonvolatile configuration settings•Software reset•Additional reset pin for selected part numbers•3-byte and 4-byte address modes – enable memoryaccess beyond 128Mb•Dedicated 64-byte OTP area outside main memory–Readable and user-lockable–Permanent lock with PROGRAM OTP command•Erase capability–Bulk erase–Sector erase 64KB uniform granularity–Subsector erase 4KB, 32KB granularity•Erase performance: 400KB/sec (64KB sector)•Erase performance: 80KB/sec (4KB sub-sector)•Program performance: 2MB/sec•Security and write protection–Volatile and nonvolatile locking and softwarewrite protection for each 64KB sector–Nonvolatile configuration locking–Password protection–Hardware write protection: nonvolatile bits(BP[3:0] and TB) define protected area size–Program/erase protection during power-up–CRC detects accidental changes to raw data•Electronic signature–JEDEC-standard 3-byte signature (BB19h)–Extended device ID: two additional bytes identifydevice factory options•JESD47H-compliant–Minimum 100,000 ERASE cycles per sector–Data retention: 20 years (TYP)Options Marking •Voltage – 1.7-2.0V U •Density –256Mb 256•Device stacking –Monolithic A •Device generation B •Die revision A •Pin configuration –RESET# and HOLD#8•Sector size –64KB E •Packages – JEDEC-standard, RoHS-compliant –24-ball T-PBGA 05/6mm × 8mm (5 × 5 array)12–24-ball T-PBGA 05/6mm × 8mm (4 × 6 array)14–Wafer level chip-scale package, 23balls , 9 active balls (XFWLBGA 0.5P)55–16-pin SOP2, 300 mils (SO16W, SO16-Wide, SOIC-16)SF –W-PDFN-8 6mm × 5mm (MLP8 6mm × 5mm)W7–W-PDFN-8 8mm × 6mm (MLP8 8mm × 6mm)W9•Security features –Standard security 0•Special options –Standard S –Automotive A •Operating temperature range –From –40°C to +85°C IT –From –40°C to +105°C AT –From –40°C to +125°C UTCCMTD-1725822587-3458mt25q_qljs_U_256_ABA_xxT.pdf - Rev. K 07/18 EN 1 Technology, Inc. reserves the right to change products or specifications without notice. © 2014 Technology, Inc. All rights reserved.Products and specifications discussed herein are subject to change by without notice.Device DescriptionThe MT25Q is a high-performance multiple input/output serial Flash memory device. It features a high-speed SPI-compatible bus interface, execute-in-place (XIP) functionali-ty, advanced write protection mechanisms, and extended address access. Innovative,high-performance, dual and quad input/output commands enable double or quadru-ple the transfer bandwidth for READ and PROGRAM operations.Figure 2: Block DiagramNote: 1.Each page of memory can be individually programmed, but the device is not page-eras-able.256Mb, 1.8V Multiple I/O Serial Flash Memory Device DescriptionCCMTD-1725822587-3458mt25q_qljs_U_256_ABA_xxT.pdf - Rev. K 07/18 EN 9 Technology, Inc. reserves the right to change products or specifications without notice. © 2014 Technology, Inc. All rights reserved.Package Dimensions – Package Code: 12Figure 9: 24-Ball T -PBGA (5 x 5 ball grid array) – 6mm x 8mmNotes: 1.All dimensions are in millimeters.2.See Part Number Ordering Information for complete package names and details.256Mb, 1.8V Multiple I/O Serial Flash Memory Package Dimensions – Package Code: 12CCMTD-1725822587-3458mt25q_qljs_U_256_ABA_xxT.pdf - Rev. K 07/18 EN 18 Technology, Inc. reserves the right to change products or specifications without notice. © 2014 Technology, Inc. All rights reserved.Serial Flash Discovery Parameter DataThe serial Flash discovery parameter (SFDP) provides a standard, consistent method to describe serial Flash device functions and features using internal parameter tables. The parameter tables can be interrogated by host system software, enabling adjustments to accommodate divergent features from multiple vendors. The SFDP standard defines a common parameter table that describes important device characteristics and serial ac-cess methods used to read the parameter table data.Micron's SFDP table information aligns with JEDEC-standard JESD216 for serial Flash discoverable parameters. The latest JEDEC standard includes revision 1.6. Beginning week 42 (2014), Micron's MT25Q production parts will include SFDP data that aligns with revision 1.6.Refer to JEDEC-standard JESD216B for a complete overview of the SFDP table defini-tion.Data in the SFDP tables is read by the READ SERIAL FLASH DISCOVERY PARAMETER operation.See TN-25-06: Serial Flash Discovery Parameters for MT25Q Family for serial Flash discovery parameter data.256Mb, 1.8V Multiple I/O Serial Flash Memory Serial Flash Discovery Parameter DataCCMTD-1725822587-3458mt25q_qljs_U_256_ABA_xxT.pdf - Rev. K 07/18 EN 40 Technology, Inc. reserves the right to change products or specifications without notice. © 2014 Technology, Inc. All rights reserved.。

MEMORY存储芯片W25Q64JVSSIQ中文规格书

4.PIN DESCRIPTIONS4.1Chip Select (/CS)The SPI Chip Select (/CS) pin enables and disables device operation. When /CS is high the device is deselected and the Serial Data Output (DO, or IO0, IO1, IO2, IO3) pins are at high impedance. When deselected, the devices power consumption will be at standby levels unless an internal erase, program or write status register cycle is in progress. When /CS is brought low the device will be selected, power consumption will increase to active levels and instructions can be written to and data read from the device. After power-up, /CS must transition from high to low before a new instruction will be accepted. The /CS input must track the VCC supply level at power-up and power-down (see “Write Protection” and Figure 58). If needed a pull-up resister on the /CS pin can be used to accomplish this.4.2Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3)The W25Q64JV supports standard SPI, Dual SPI and Quad SPI operation. Standard SPI instructions use the unidirectional DI (input) pin to serially write instructions, addresses or data to the device on the rising edge of the Serial Clock (CLK) input pin. Standard SPI also uses the unidirectional DO (output) to read data or status from the device on the falling edge of CLK.Dual and Quad SPI instructions use the bidirectional IO pins to serially write instructions, addresses or data to the device on the rising edge of CLK and read data or status from the device on the falling edge of CLK. Quad SPI instructions require the non-volatile Quad Enable bit (QE) in Status Register-2 to be set. When QE=1, the /WP pin becomes IO2 and the /HOLD pin becomes IO3.4.3Write Protect (/WP)The Write Protect (/WP) pin can be used to prevent the Status Register from being written. Used in conjunction with the Status Register’s Block Protect (CMP, SEC, TB, BP2, BP1 and BP0) bits and Status Register Protect (SRP) bits, a portion as small as a 4KB sector or the entire memory array can be hardware protected. The /WP pin is active low.4.4HOLD (/HOLD)The /HOLD pin allows the device to be paused while it is actively selected. When /HOLD is brought low, while /CS is low, the DO pin will be at high impedance and signals on the DI and CLK pins will be ignored (don’t care). When /HOLD is brought high, device operation can resume. The /HOLD func tion can be useful when multiple devices are sharing the same SPI signals. The /HOLD pin is active low. When the QE bit of Status Register-2 is set for Quad I/O, the /HOLD pin function is not available since this pin is used for IO3. See Figure 1a-c for the pin configuration of Quad I/O operation.4.5Serial Clock (CLK)The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations. ("See SPI Operations")4.6Reset (/RESET)(1)A dedicated hardware /RESET pin is available on SOIC-16 and TFBGA packages. When it’s driven low for a minimum period of ~1µS, this device will terminate any external or internal operations and return to its power-on state.Note:1.H ardware /RESET pin is available on SOIC-16 or TFBGA; please contact Winbond for this package.5.BLOCK DIAGRAMFigure 2. W25Q64JV Serial Flash Memory Block Diagram6.5Write ProtectionApplications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern, the W25Q64JV provides several means to protect the data from inadvertent writes.Write Protect Features∙Device resets when VCC is below threshold∙Time delay write disable after Power-up∙Write enable/disable instructions and automatic write disable after erase or program∙Software and Hardware (/WP pin) write protection using Status Registers∙Additional Individual Block/Sector Locks for array protection∙Write Protection using Power-down instruction∙Lock Down write protection for Status Register until the next power-up∙One Time Program (OTP) write protection for array and Security Registers using Status Register* *Note:This feature is available upon special flow. Please contact Winbond for details.Upon power-up or at power-down, the W25Q64JV will maintain a reset condition while VCC is below the threshold value of V WI, (See Power-up Timing and Voltage Levels and Figure 43). While reset, all operations are disabled and no instructions are recognized. During power-up and after the VCC voltage exceeds V WI, all program and erase related instructions are further disabled for a time delay of t PUW. This includes the Write Enable, Page Program, Sector Erase, Block Erase, Chip Erase and the Write Status Register instructions. Note that the chip select pin (/CS) must track the VCC supply level at power-up until the VCC-min level and t VSL time delay is reached, and it must also track the VCC supply level at power-down to prevent adverse command sequence. If needed a pull-up resister on /CS can be used to accomplish this. After power-up the device is automatically placed in a write-disabled state with the Status Register Write Enable Latch (WEL) set to a 0. A Write Enable instruction must be issued before a Page Program, Sector Erase, Block Erase, Chip Erase or Write Status Register instruction will be accepted. After completing a program, erase or write instruction the Write Enable Latch (WEL) is automatically cleared to a write-disabled state of 0.Software controlled write protection is facilitated using the Write Status Register instruction and setting the Status Register Protect (SRP, SRL) and Block Protect (CMP, TB, BP[3:0]) bits. These settings allow a portion or the entire memory array to be configured as read only. Used in conjunction with the Write Protect (/WP) pin, changes to the Status Register can be enabled or disabled under hardware control. See Status Register section for further information. Additionally, the Power-down instruction offers an extra level of write protection as all instructions are ignored except for the Release Power-down instruction.The W25Q64JV also provides another Write Protect method using the Individual Block Locks. Each 64KB block (except the top and bottom blocks, total of 126 blocks) and each 4KB sector within the top/bottom blocks (total of 32 sectors) are equipped with an Individual Block Lock bit. When the lock bit is 0, the corresponding sector or block can be erased or programmed; when the lock bit is set to 1, Erase or Program commands issued to the corresponding sector or block will be ignored. When the device is powered on, all Individual Block Lock bits will be 1, so the entire memory array is protected from Erase/Program. An “Individual Block Unlock (39h)” instruction must be issued to unlock any specific sector or block.The WPS bit in Status Register-3 is used to decide which Write Protect scheme should be used. When WPS=0 (factory default), the device will only utilize CMP, SEC, TB, BP[2:0] bits to protect specific areas of the array; when WPS=1, the device will utilize the Individual Block Locks for write protection.7.STATUS AND CONFIGURATION REGISTERSThree Status and Configuration Registers are provided for W25Q64JV. The Read Status Register-1/2/3 instructions can be used to provide status on the availability of the flash memory array, whether the device is write enabled or disabled, the state of write protection, Quad SPI setting, Security Register lock status, Erase/Program Suspend status, output driver strength, power-up. The Write Status Register instruction can be used to configure the device write protection features, Quad SPI setting, Security Register OTP locks, and output driver strength. Write access to the Status Register is controlled by the state of the non-volatile Status Register Protect bits (SRL), the Write Enable instruction, and during Standard/Dual SPI operations7.1Status RegistersFigure 4a. Status Register-1Erase/Write In Progress (BUSY) –Status OnlyBUSY is a read only bit in the status register (S0) that is set to a 1 state when the device is executing a Page Program, Quad Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register or Erase/Program Security Register instruction. During this time the device will ignore further instructions except for the Read Status Register and Erase/Program Suspend instruction (see t W, t PP, t SE,t BE, and t CE in AC Characteristics). When the program, erase or write status/security register instruction has completed, the BUSY bit will be cleared to a 0 state indicating the device is ready for further instructions.Write Enable Latch (WEL) –Status OnlyWrite Enable Latch (WEL) is a read only bit in the status register (S1) that is set to 1 after executing a Write Enable Instruction. The WEL status bit is cleared to 0 when the device is write disabled. A write disable state occurs upon power-up or after any of the following instructions: Write Disable, Page Program, Quad Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register, Erase Security Register andProgram Security Register.Block Protect Bits (BP2, BP1, BP0) –Volatile/Non-Volatile WritableThe Block Protect Bits (BP2, BP1, BP0) are non-volatile read/write bits in the status register (S4, S3, and S2) that provide Write Protection control and status. Block Protect bits can be set using the Write Status Register Instruction (see t W in AC characteristics). All, none or a portion of the memory array can be protected from Program and Erase instructions (see Status Register Memory Protection table). The factory default setting for the Block Protection Bits is 0, none of the array protected.SRP SEC TB BP2BP1BP0WEL BUSYTOP/BOTTOM PROTECTWRITE ENABLE LATCHS7S6S5S4S3S2S1S0STATUS REGISTER PROTECTSECTOR PROTECTBLOCK PROTECT BITSWRITE IN PROGRESS(volatile/non-volatile)(volatile/non-volatile)(volatile/non-volatile)(volatile/non-volatile)。

MEMORY存储芯片N25Q256A83ESF40F中文规格书

READ VOLATILE or ENHANCED VOLATILE CONFIGURATION REGISTER CommandTo execute a READ VOLATILE CONFIGURATION REGISTER command or a READ EN-HANCED VOLATILE CONFIGURATION REGISTER command, S# is driven LOW. For ex-tended SPI protocol, the command code is input on DQ0, and output on DQ1. For dualSPI protocol, the command code is input on DQ[1:0], and output on DQ[1:0]. For quadSPI protocol, the command code is input on DQ[3:0], and is output on DQ[3:0]. The op-eration is terminated by driving S# HIGH at any time during data output.When the register is read continuously, the same byte is output repeatedly.READ EXTENDED ADDRESS REGISTER CommandTo initiate a READ EXTENDED ADDRESS REGISTER command, S# is driven LOW. Forextended SPI protocol, the command code is input on DQ0, and output on DQ1. Fordual SPI protocol, the command code is input on DQ[1:0], and output on DQ[1:0]. Forquad SPI protocol, the command code is input on DQ[3:0], and is output on DQ[3:0].The operation is terminated by driving S# HIGH at any time during data output.When the register is read continuously, the same byte is output repeatedly.WRITE STATUS REGISTER CommandTo issue a WRITE STATUS REGISTER command, the WRITE ENABLE command must beexecuted to set the write enable latch bit to 1. S# is driven LOW and held LOW until theeighth bit of the last data byte has been latched in, after which it must be driven HIGH.For extended SPI protocol, the command code is input on DQ0, followed by the databytes. For dual SPI protocol, the command code is input on DQ[1:0], followed by the da-ta bytes. For quad SPI protocol, the command code is input on DQ[3:0], followed by thedata bytes. When S# is driven HIGH, the operation, which is self-timed, is initiated; itsduration is t W.This command is used to write new values to status register bits 7:2, enabling softwaredata protection. The status register can also be combined with the W#/V PP signal toprovide hardware data protection. The WRITE STATUS REGISTER command has no ef-fect on status register bits 1:0.When the operation is in progress, the write in progress bit is set to 1. The write enablelatch bit is cleared to 0, whether the operation is successful or not. The status registerand flag status register can be polled for the operation status. When the operation com-pletes, the write in progress bit is cleared to 0, whether the operation is successful ornot. If S# is not driven HIGH, the command is not executed, flag status register errorbits are not set, and the write enable latch remains set to 1.找Memory 、FPGA 、二三极管、连接器、模块、光耦、电容电阻、单片机、处理器、晶振、传感器、 滤波器,上深圳市美光存储技术有限公司Figure 11: WRITE REGISTER CommandCDQ0CDQ[1:0]ExtendedDual QuadCDQ[3:0]Notes: 1.Supports all WRITE REGISTER commands except WRITE LOCK REGISTER.2.Waveform must be extended for each protocol, to 23 for extended, 11 for dual, and 5for quad.3. A WRITE NONVOLATILE CONFIGURATION REGISTER operation requires data being sentstarting from least significant byte.WRITE NONVOLATILE CONFIGURATION REGISTER CommandTo execute the WRITE NONVOLATILE CONFIGURATION REGISTER command, theWRITE ENABLE command must be executed to set the write enable latch bit to 1. S# isdriven LOW and held LOW until the 16th bit of the last data byte has been latched in,after which it must be driven HIGH. For extended SPI protocol, the command code isinput on DQ0, followed by two data bytes. For dual SPI protocol, the command code isinput on DQ[1:0], followed by the data bytes. For quad SPI protocol, the command codeis input on DQ[3:0], followed by the data bytes. When S# is driven HIGH, the operation,which is self-timed, is initiated; its duration is t NVCR.When the operation is in progress, the write in progress bit is set to 1. The write enablelatch bit is cleared to 0, whether the operation is successful or not. The status registerand flag status register can be polled for the operation status. When the operation com-pletes, the write in progress bit is cleared to 0, whether the operation is successful ornot. If S# is not driven HIGH, the command is not executed, flag status register errorbits are not set, and the write enable latch remains set to 1.WRITE VOLATILE or ENHANCED VOLATILE CONFIGURATION REGISTER CommandTo execute a WRITE VOLATILE CONFIGURATION REGISTER command or a WRITEENHANCED VOLATILE CONFIGURATION REGISTER command, the WRITE ENABLEcommand must be executed to set the write enable latch bit to 1. S# is driven LOW andheld LOW until the eighth bit of the last data byte has been latched in, after which itmust be driven HIGH. For extended SPI protocol, the command code is input on DQ0,followed by the data bytes. For dual SPI protocol, the command code is input onDQ[1:0], followed by the data bytes. For quad SPI protocol, the command code is inputon DQ[3:0], followed by the data bytes.3V , 256Mb: Multiple I/O Serial Flash Memory READ REGISTER and WRITE REGISTER OperationsREAD MEMORY OperationsThe device supports default reading and writing to an A[MAX:MIN] of A[23:0] (3-byteaddress).Reading and writing to an A[MAX:MIN] of A[31:0] (4-byte address) is also supported. Se-lection of the 3-byte or 4-byte address range can be enabled in two ways: setting thenonvolatile configuration register or entering the ENABLE 4-BYTE ADDRESS MODE orEXIT 4-BYTE ADDRESS MODE commands. Further details for these settings and com-mands are in the respective register and command sections of the data sheet.Note: When the device is set to the default address range of A[23:0], another method forenabling 4-byte addressing is through the extended address register. Details can befound in Nonvolatile and Volatile Registers.3-Byte AddressTo execute READ MEMORY commands, S# is driven LOW. The command code is inputon DQ n, followed by input on DQ n of three address bytes. Each address bit is latched induring the rising edge of the clock. The addressed byte can be at any location, and theaddress automatically increments to the next address after each byte of data is shiftedout; therefore, the entire memory can be read with a single command. The operation isterminated by driving S# HIGH at any time during data output.PROGRAM OperationsPROGRAM commands are initiated by first executing the WRITE ENABLE command toset the write enable latch bit to 1. S# is then driven LOW and held LOW until the eighthbit of the last data byte has been latched in, after which it must be driven HIGH. Thecommand code is input on DQ0, followed by input on DQ[n] of address bytes and atleast one data byte. Each address bit is latched in during the rising edge of the clock.When S# is driven HIGH, the operation, which is self-timed, is initiated; its duration ist PP.If the bits of the least significant address, which is the starting address, are not all zero,all data transmitted beyond the end of the current page is programmed from the start-ing address of the same page. If the number of bytes sent to the device exceed the maxi-mum page size, previously latched data is discarded and only the last maximum page-size number of data bytes are guaranteed to be programmed correctly within the samepage. If the number of bytes sent to the device is less than the maximum page size, theyare correctly programmed at the specified addresses without any effect on the otherbytes of the same page.When the operation is in progress, the write in progress bit is set to 1. The write enablelatch bit is cleared to 0, whether the operation is successful or not. The status registerand flag status register can be polled for the operation status. An operation can bepaused or resumed by the PROGRAM/ERASE SUSPEND or PROGRAM/ERASE RESUMEcommand, respectively. When the operation completes, the write in progress bit iscleared to 0.If the operation times out, the write enable latch bit is reset and the program fail bit isset to 1. If S# is not driven HIGH, the command is not executed, flag status register errorbits are not set, and the write enable latch remains set to 1. When a command is appliedto a protected sector, the command is not executed, the write enable latch bit remainsset to 1, and flag status register bits 1 and 4 are set.Table 27: Data/Address Lines for PROGRAM CommandsNote: 1.Yes in the protocol columns indicates that the command is supported and has the samefunctionality and command sequence as other commands marked Yes.。

MEMORY存储芯片N25Q032A13ESE40中文规格书

Figure 37: Tangent Line for t IH (Command and Address – Clock)V SSHold slew rate falling signal =V DDQV IH(AC)min V IH(DC)minV REF(DC)V IL(DC)max V IL(AC)maxHold slew rate rising signal =DQSDQS#CK#CK Tangent line (V REF(DC) - V IL(DC)max )Tangent line (V IH(DC)min - V REF(DC))ǻTRǻTRǻTRǻTF Note: 1.The clock and the strobe are drawn on different time scales.4Gb: x4, x8, x16 DDR3L SDRAM Command and Address Setup, Hold, and DeratingFigure 83: t RPST TimingDQS - DQS#DQSDQS#t CKCK#4Gb: x4, x8, x16 DDR3L SDRAM READ OperationWrite Leveling ProcedureA memory controller initiates the DRAM write leveling mode by setting MR1[7] to 1, as-suming the other programable features (MR0, MR1, MR2, and MR3) are first set and the DLL is fully reset and locked. The DQ balls enter the write leveling mode going from a High-Z state to an undefined driving state, so the DQ bus should not be driven. During write leveling mode, only the NOP or DES commands are allowed. The memory con-troller should attempt to level only one rank at a time; thus, the outputs of other ranks should be disabled by setting MR1[12] to 1 in the other ranks. The memory controller may assert ODT after a t MOD delay, as the DRAM will be ready to process the ODT tran-sition. ODT should be turned on prior to DQS being driven LOW by at least ODTLon delay (WL - 2 t CK), provided it does not violate the aforementioned t MOD delay require-ment.The memory controller may drive DQS LOW and DQS# HIGH after t WLDQSEN has been satisfied. The controller may begin to toggle DQS after t WLMRD (one DQS toggle is DQS transitioning from a LOW state to a HIGH state with DQS# transitioning from a HIGH state to a LOW state, then both transition back to their original states). At a mini-mum, ODTLon and t AON must be satisfied at least one clock prior to DQS toggling.After t WLMRD and a DQS LOW preamble (t WPRE) have been satisfied, the memory controller may provide either a single DQS toggle or multiple DQS toggles to sample CK for a given DQS-to-CK skew. Each DQS toggle must not violate t DQSL (MIN) and t DQSH (MIN) specifications. t DQSL (MAX) and t DQSH (MAX) specifications are not applicable during write leveling mode. The DQS must be able to distinguish the CK’s rising edge within t WLS and t WLH. The prime DQ will output the CK’s status asynchronously from the associated DQS rising edge CK capture within t WLO. The remaining DQ that always drive LOW when DQS is toggling must be LOW within t WLOE after the first t WLO is sat-isfied (the prime DQ going LOW). As previously noted, DQS is an input and not an out-put during this process. Figure 48 (page 134) depicts the basic timing parameters for the overall write leveling procedure.The memory controller will most likely sample each applicable prime DQ state and de-termine whether to increment or decrement its DQS delay setting. After the memory controller performs enough DQS toggles to detect the CK’s 0-to-1 transition, the memo-ry controller should lock the DQS delay setting for that DRAM. After locking the DQS setting is locked, leveling for the rank will have been achieved, and the write leveling mode for the rank should be disabled or reprogrammed (if write leveling of another rank follows).4Gb: x4, x8, x16 DDR3L SDRAM Write Leveling。

MEMORY存储芯片MAX232ESE中文规格书

MAX202E–MAX213E,MAX232E/MAX241E±15kV ESD-Protected, 5V RS-232 TransceiversGeneral DescriptionThe MAX202E-MAX213E, MAX232E, and MAX241E are a family of RS-232 and V.28 transceivers with high ±15kV ESD HBM protection and integrated charge pump circuit-ry for single +5V supply operation. The various combina-tions of features are outlined in the Selector Guide.The drivers and receivers for all ten devices meet all EIA/TIA-232E and CCITT V.28 specifications at data rates up to 120kbps when loaded.The MAX211E/MAX213E/MAX241E are available in 28-pin SO and SSOP packages. The MAX202E/MAX232E come in 16-pin TSSOP, narrow SO, wide SO, and DIP packages. The MAX203E comes in a 20-pin DIP/SO package, and needs no external charge-pump capaci-tors. The MAX205E comes in a 24-pin wide DIP pack-age, and also eliminates external charge-pump capacitors.Applications•Battery-Powered Equipment •Hand-Held Equipment•Portable Diagnostics EquipmentBenefits and Features•Saves Board Space•Integrated High ±15kV HBM ESD Protection •Integrated Charge Pump CircuitryEliminates the Need for a Bipolar ±12V SupplyEnables Single Supply Operation From +5V Supply •Integrated 0.1µF Capacitors (MAX203E, MAX205E)•24 pin SSOP Package Saves up to 40% Versus SO Package•Saves Power for Reduced Power Requirements •1µA Shutdown Mode•15µA Shutdown Mode for MAX213EPin Configurations and Typical Operating Circuits appear at end of data sheet.YesPARTNO. OF RS-232DRIVERSNO. OF RS-232RECEIVERSRECEIVERS ACTIVE IN SHUTDOWNNO. OF EXTERNALCAPACITORS(µF)LOW-POWER SHUTDOWNTTL TRI-STATE MAX202E 220 4 (0.1)No No MAX203E 220None No No MAX205E 550None Yes Yes MAX206E 430 4 (0.1)Yes Yes MAX207E 530 4 (0.1)No No MAX208E 440 4 (0.1)No No MAX211E 450 4 (0.1)Yes Yes MAX213E 452 4 (0.1)Yes Yes MAX232E 220 4 (1)No No MAX241E454 (1)YesAutoShutdown and UCSP are trademarks of Maxim Integrated Products, Inc.Ordering InformationOrdering Information continued at end of data sheet.Absolute Maximum RatingsV CC ..........................................................................-0.3V to +6V V+................................................................(V CC - 0.3V) to +14V V-............................................................................-14V to +0.3V Input VoltagesT_IN............................................................-0.3V to (V+ + 0.3V)R_IN...................................................................................±30V Output VoltagesT_OUT.................................................(V- - 0.3V) to (V+ + 0.3V)R_OUT......................................................-0.3V to (V CC + 0.3V)Short-Circuit Duration, T_OUT....................................Continuous Continuous Power Dissipation (T A = +70°C)16-Pin Plastic DIP (derate 10.53mW/°C above +70°C)....842mW 16-Pin Narrow SO (derate 8.70mW/°C above +70°C).....696mW 16-Pin Wide SO (derate 9.52mW/°C above +70°C)......762mW 16-Pin TSSOP (derate 9.4mW/°C above +70°C)...........755mW20-Pin Plastic DIP (derate 11.11mW/°C above +70°C)...889mW 20-Pin SO (derate 10.00mW/°C above +70°C).............800mW 24-Pin Narrow Plastic DIP(derate 13.33mW/°C above +70°C) ...............................1.07W 24-Pin Wide Plastic DIP(derate 14.29mW/°C above +70°C)................................1.14W 24-Pin SO (derate 11.76mW/°C above +70°C).............941mW 24-Pin SSOP (derate 8.00mW/°C above +70°C)..........640mW 28-Pin SO (derate 12.50mW/°C above +70°C)....................1W 28-Pin SSOP (derate 9.52mW/°C above +70°C)..........762mW Operating Temperature RangesMAX2_ _EC_ _.....................................................0°C to +70°C MAX2_ _EE_ _...................................................-40°C to +85°C Storage Temperature Range.............................-65°C to +165°C Lead Temperature (soldering, 10s).................................+300°CElectrical Characteristics(V CC = +5V ±10% for MAX202E/206E/208E/211E/213E/232E/241E; V CC = +5V ±5% for MAX203E/205E/207E; C1–C4 = 0.1µF for MAX202E/206E/207E/208E/211E/213E; C1–C4 = 1µF for MAX232E/241E; T A = T MIN to T MAX ; unless otherwise noted. Typical values are at T A = +25°C.)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Electrical Characteristics (continued)(V CC= +5V ±10% for MAX202E/206E/208E/211E/213E/232E/241E; V CC= +5V ±5% for MAX203E/205E/207E; C1–C4 = 0.1µF for MAX202E/206E/207E/208E/211E/213E; C1–C4 = 1µF for MAX232E/241E; T A= T MIN to T MAX; unless otherwise noted. Typical valuesNote 1:MAX211EE_ _ tested with V CC= +5V ±5%.Typical Operating Characteristics。

W25Q128JVSIQ规格书_W25Q128JVSIQ中文资料_W25Q128JVSIQ Datasheet

Publication Release Date: May 02, 2017Revision D3V 128M-BITSERIAL FLASH MEMORY WITH DUAL/QUAD SPI- 1 -Table of Contents1. GENERAL DESCRIPTIONS ............................................................................................................. 42. FEATURES ....................................................................................................................................... 43.PACKAGE TYPES AND PIN CONFIGURATIONS ........................................................................... 5 3.1 Pin Configuration SOIC 208-mil ........................................................................................... 5 3.2 Pad Configuration WSON 6x5-mm/ 8x6-mm ....................................................................... 5 3.3 Pin Description SOIC 208-mil, WSON 6x5-mm / 8x6-mm ................................................... 5 3.4 Pin Configuration SOIC 300-mil ........................................................................................... 6 3.5 Pin Description SOIC 300-mil ............................................................................................... 6 3.6 Ball Configuration TFBGA 8x6-mm (5x5 or 6x4 Ball Array) ................................................. 7 3.7Ball Description TFBGA 8x6-mm ......................................................................................... 7 4. PIN DESCRIPTIONS ........................................................................................................................ 8 4.1 Chip Select (/CS) .................................................................................................................. 8 4.2 Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3) ..................................... 8 4.3 Write Protect (/WP) .............................................................................................................. 8 4.4 HOLD (/HOLD) ..................................................................................................................... 8 4.5 Serial Clock (CLK) ................................................................................................................ 8 4.6Reset (/RESET) (8)5. BLOCK DIAGRAM ............................................................................................................................ 96.FUNCTIONAL DESCRIPTIONS ..................................................................................................... 10 6.1 Standard SPI Instructions ................................................................................................... 10 6.2 Dual SPI Instructions .......................................................................................................... 10 6.3 Quad SPI Instructions ......................................................................................................... 10 6.4 Software Reset & Hardware /RESET pin ........................................................................... 10 6.5Write Protection (11)6.5.1 Write Protect Features (11)7. STATUS AND CONFIGURATION REGISTERS ............................................................................ 12 7.1Status Registers (12)7.1.1 Erase/Write In Progress (BUSY) – Status Only ................................................................ 12 7.1.2 Write Enable Latch (WEL) – Status Only .......................................................................... 12 7.1.3 Block Protect Bits (BP2, BP1, BP0) – Volatile/Non-Volatile Writable ................................ 12 7.1.4 Top/Bottom Block Protect (TB) – Volatile/Non-Volatile Writable ....................................... 13 7.1.5 Sector/Block Protect Bit (SEC) – Volatile/Non-Volatile Writable ....................................... 13 7.1.6 Complement Protect (CMP) – Volatile/Non-Volatile Writable ............................................ 13 7.1.1 Status Register Protect (SRP, SRL) – Volatile/Non-Volatile Writable ............................... 14 7.1.2 Erase/Program Suspend Status (SUS) – Status Only . (15)Publication Release Date: May 02, 2017- 2 - Revision D7.1.3 Security Register Lock Bits (LB3, LB2, LB1) – Volatile/Non-Volatile OTP Writable .......... 15 7.1.4 Quad Enable (QE) – Volatile/Non-Volatile Writable .......................................................... 15 7.1.5 Write Protect Selection (WPS) – Volatile/Non-Volatile Writable ....................................... 16 7.1.6 Output Driver Strength (DRV1, DRV0) – Volatile/Non-Volatile Writable ........................... 16 7.1.7 Reserved Bits – Non Functional ........................................................................................ 16 7.1.8 W25Q128JV Status Register Memory Protection (WPS = 0, CMP = 0) ............................... 17 7.1.9 W25Q128JV Status Register Memory Protection (WPS = 0, CMP = 1) ............................... 18 7.1.10 W25Q128JV Individual Block Memory Protection (WPS=1) . (19)8. INSTRUCTIONS ............................................................................................................................. 20 8.1Device ID and Instruction Set Tables (20)8.1.1 Manufacturer and Device Identification ................................................................................ 20 8.1.2 Instruction Set Table 1 (Standard SPI Instructions)(1)........................................................... 21 8.1.3 Instruction Set Table 2 (Dual/Quad SPI Instructions) ........................................................... 22 Notes: (22)8.2 Instruction Descriptions (23)8.2.1 Write Enable (06h) ............................................................................................................... 23 8.2.2 Write Enable for Volatile Status Register (50h) .................................................................... 23 8.2.3 Write Disable (04h) ............................................................................................................... 24 8.2.4 Read Status Register-1 (05h), Status Register-2 (35h) & Status Register-3 (15h) .............. 24 8.2.5 Write Status Register-1 (01h), Status Register-2 (31h) & Status Register-3 (11h) .............. 25 8.2.6 Read Data (03h) ................................................................................................................... 27 8.2.7 Fast Read (0Bh) ................................................................................................................... 28 8.2.8 Fast Read Dual Output (3Bh) ............................................................................................... 29 8.2.9 Fast Read Quad Output (6Bh) .............................................................................................. 30 8.2.10 Fast Read Dual I/O (BBh) ................................................................................................... 31 8.2.11 Fast Read Quad I/O (EBh) ................................................................................................. 32 8.2.12 Set Burst with Wrap (77h) .................................................................................................. 34 8.2.13 Page Program (02h) ........................................................................................................... 35 8.2.14 Quad Input Page Program (32h) ........................................................................................ 36 8.2.15 Sector Erase (20h) ............................................................................................................. 37 8.2.16 32KB Block Erase (52h) ..................................................................................................... 38 8.2.17 64KB Block Erase (D8h) ..................................................................................................... 39 8.2.18 Chip Erase (C7h / 60h) ....................................................................................................... 40 8.2.19 Erase / Program Suspend (75h) ......................................................................................... 41 8.2.20 Erase / Program Resume (7Ah) ......................................................................................... 42 8.2.21 Power-down (B9h) .............................................................................................................. 43 8.2.22 Release Power-down / Device ID (ABh) ............................................................................. 44 8.2.23 Read Manufacturer / Device ID (90h) ................................................................................. 45 8.2.24 Read Manufacturer / Device ID Dual I/O (92h) ................................................................... 46 8.2.25 Read Manufacturer / Device ID Quad I/O (94h) ................................................................. 47 8.2.26 Read Unique ID Number (4Bh). (48)- 3 -8.2.27 Read JEDEC ID (9Fh) ........................................................................................................ 49 8.2.28 Read SFDP Register (5Ah) ................................................................................................ 50 8.2.29 Erase Security Registers (44h) ........................................................................................... 51 8.2.30 Program Security Registers (42h) ...................................................................................... 52 8.2.31 Read Security Registers (48h) ........................................................................................... 53 8.2.32 Individual Block/Sector Lock (36h) ..................................................................................... 54 8.2.33 Individual Block/Sector Unlock (39h) .................................................................................. 55 8.2.34 Read Block/Sector Lock (3Dh) ........................................................................................... 56 8.2.35 Global Block/Sector Lock (7Eh) .......................................................................................... 57 8.2.36 Global Block/Sector Unlock (98h) ....................................................................................... 57 8.2.37 Enable Reset (66h) and Reset Device (99h) . (58)9.ELECTRICAL CHARACTERISTICS (59)9.1 Absolute Maximum Ratings (1) ............................................................................................ 59 9.2 Operating Ranges............................................................................................................... 59 9.3 Power-Up Power-Down Timing and Requirements ............................................................ 60 9.4 DC Electrical Characteristics- ............................................................................................. 61 9.5 AC Measurement Conditions .............................................................................................. 62 9.6 AC Electrical Characteristics (6) ........................................................................................... 63 9.7 Serial Output Timing ........................................................................................................... 65 9.8 Serial Input Timing .............................................................................................................. 65 9.9/WP Timing ......................................................................................................................... 65 10. PACKAGE SPECIFICATIONS ........................................................................................................ 66 10.1 8-Pin SOIC 208-mil (Package Code S) .............................................................................. 66 10.2 16-Pin SOIC 300-mil (Package Code F) ............................................................................ 67 10.3 8-Pad WSON 6x5-mm (Package Code P) ......................................................................... 68 10.4 8-Pad WSON 8x6-mm (Package Code E) ......................................................................... 69 10.5 24-Ball TFBGA 8x6-mm (Package Code B, 5x5-1 ball array) ............................................ 70 10.624-Ball TFBGA 8x6-mm (Package Code C, 6x4 ball array) ............................................... 71 11. ORDERING INFORMATION .......................................................................................................... 72 11.1Valid Part Numbers and Top Side Marking (73)12. REVISION HISTORY (74)Publication Release Date: May 02, 2017- 4 - Revision D1. GENERAL DESCRIPTIONSThe W25Q128JV (128M-bit) Serial Flash memory provides a storage solution for systems with limited space, pins and power. The 25Q series offers flexibility and performance well beyond ordinary Serial Flash devices. They are ideal for code shadowing to RAM, executing code directly from Dual/Quad SPI (XIP) and storing voice, text and data. The device operates on a single 2.7V to 3.6V power supply with current consumption as low as 1µA for power-down. All devices are offered in space-saving packages.The W25Q128JV array is organized into 65,536 programmable pages of 256-bytes each. Up to 256 bytes can be programmed at a time. Pages can be erased in groups of 16 (4KB sector erase), groups of 128 (32KB block erase), groups of 256 (64KB block erase) or the entire chip (chip erase). The W25Q128JV has 4,096 erasable sectors and 256 erasable blocks respectively. The small 4KB sectors allow for greater flexibility in applications that require data and parameter storage. (See Figure 2.)The W25Q128JV supports the standard Serial Peripheral Interface (SPI), Dual/Quad I/O SPI: Serial Clock, Chip Select, Serial Data I/O0 (DI), I/O1 (DO), I/O2 and I/O3. SPI clock frequencies of W25Q128JV of up to 133MHz are supported allowing equivalent clock rates of 266MHz (133MHz x 2) for Dual I/O and 532MHz (133MHz x 4) for Quad I/O when using the Fast Read Dual/Quad I/O. These transfer rates can outperform standard Asynchronous 8 and 16-bit Parallel Flash memories.Additionally, the device supports JEDEC standard manufacturer and device ID and SFDP, and a 64-bit Unique Serial Number and three 256-bytes Security Registers.2. FEATURES∙ New Family of SpiFlash Memories – W25Q128JV: 128M-bit / 16M-byte – Standard SPI: CLK, /CS, DI, DO – Dual SPI: CLK, /CS, IO 0, IO 1 – Quad SPI: CLK, /CS, IO 0, IO 1, IO 2, IO 3 – Software & Hardware Reset (1) ∙ Highest Performance Serial Flash – 133MHz Single, Dual/Quad SPI clocks – 266/532MHz equivalent Dual/Quad SPI – 66MB/S continuous data transfer rate – Min. 100K Program-Erase cycles per sector – More than 20-year data retention ∙ Efficient “Continuous Read”– Continuous Read with 8/16/32/64-Byte Wrap– As few as 8 clocks to address memory– Allows true XIP (execute in place) operation ∙ Low Power, Wide Temperature Range– Single 2.7 to 3.6V supply– <1µA Power-down (typ.)– -40°C to +85°C operating range∙ Flexible Architecture with 4KB sectors – Uniform Sector/Block Erase (4K/32K/64K-Byte) – Program 1 to 256 byte per programmable page – Erase/Program Suspend & Resume ∙ Advanced Security Features – Software and Hardware Write-Protect – Power Supply Lock-Down – Special OTP protection – Top/Bottom, Complement array protection – Individual Block/Sector array protection – 64-Bit Unique ID for each device – Discoverable Parameters (SFDP) Register– 3X256-Bytes Security Registers with OTP locks – Volatile & Non-volatile Status Register Bits ∙ Space Efficient Packaging – 8-pin SOIC 208-mil– 16-pin SOIC 300-mil (additional /RESET pin) – 8-pad WSON 6x5-mm / 8x6-mm – 24-ball TFBGA 8x6-mm (6x4/5x5 ball array) – Contact Winbond for KGD and other options Note: 1. Hardware /RESET pin is only available on TFBGA or SOIC16 packages- 5 -3. PACKAGE TYPES AND PIN CONFIGURATIONS3.1 Pin Configuration SOIC 208-milFigure 1a. W25Q128JV Pin Assignments, 8-pin SOIC 208-mil (Package Code S)3.2 Pad Configuration WSON 6x5-mm/ 8x6-mmFigure 1b. W25Q128JV Pad Assignments, 8-pad WSON 6x5-mm/ 8x6-mm (Package Code P/E)3.3 Pin Description SOIC 208-mil, WSON 6x5-mm / 8x6-mmNotes:1. IO0 and IO1 are used for Standard and Dual SPI instructions2.IO0 – IO3 are used for Quad SPI instructions, /HOLD (or /RESET) function is only available for Standard/Dual SPI.Publication Release Date: May 02, 2017- 6 - Revision D3.4 Pin Configuration SOIC 300-milFigure 1c. W25Q128JV Pin Assignments, 16-pin SOIC 300-mil (Package Code F)3.5 Pin Description SOIC 300-milNotes:1. IO0 and IO1 are used for Standard and Dual SPI instructions.2. IO0 – IO3 are used for Quad SPI instructions, /HOLD (or /RESET) function is only available for Standard/Dual SPI.3. The /RESET pin is a dedicated hardware reset pin regardless of device settings or operation states. If the hardware reset function is not used, this pin can be left floating or connected to VCC in the system.3.6Ball Configuration TFBGA 8x6-mm (5x5 or 6x4 Ball Array)Figure 1d. W25Q128JV Ball Assignments, 24-ball TFBGA 8x6-mm (Package Code B/C)3.7Ball Description TFBGA 8x6-mmNotes:1.IO0 and IO1 are used for Standard and Dual SPI instructions2.IO0 – IO3 are used for Quad SPI instructions, /HOLD (or /RESET) function is only available for Standard/Dual SPI.3. The /RESET pin is a dedicated hardware reset pin regardless of device settings or operation states.If the hardware reset function is not used, this pin can be left floating or connected to VCC in the system- 7 -Publication Release Date: May 02, 2017- 8 - Revision D4. PIN DESCRIPTIONS4.1 Chip Select (/CS)The SPI Chip Select (/CS) pin enables and disables device operation. When /CS is high the device is deselected and the Serial Data Output (DO, or IO0, IO1, IO2, IO3) pins are at high impedance. When deselected, the devices power consumption will be at standby levels unless an internal erase, program or write status register cycle is in progress. When /CS is brought low the device will be selected, power consumption will increase to active levels and instructions can be written to and data read from the device. After power-up, /CS must transition from high to low before a new instruction will be accepted. The /CS input must track the VCC supply level at power-up and power-down (see “Write Protection” and Figure 58). If needed a pull-up resister on the /CS pin can be used to accomplish this.4.2 Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3)The W25Q128JV supports standard SPI, Dual SPI and Quad SPI operation. Standard SPI instructions use the unidirectional DI (input) pin to serially write instructions, addresses or data to the device on the rising edge of the Serial Clock (CLK) input pin. Standard SPI also uses the unidirectional DO (output) to read data or status from the device on the falling edge of CLK.Dual and Quad SPI instructions use the bidirectional IO pins to serially write instructions, addresses or data to the device on the rising edge of CLK and read data or status from the device on the falling edge of CLK. Quad SPI instructions require the non-volatile Quad Enable bit (QE) in Status Register-2 to be set. When QE=1, the /WP pin becomes IO2 and the /HOLD pin becomes IO3.4.3 Write Protect (/WP)The Write Protect (/WP) pin can be used to prevent the Status Register from being written. Used in conjunction with the Status Register’s Block Protect (CMP, SEC, TB, BP2, BP1 and BP0) bits and Status Register Protect (SRP) bits, a portion as small as a 4KB sector or the entire memory array can be hardware protected. The /WP pin is active low.4.4 HOLD (/HOLD)The /HOLD pin allows the device to be paused while it is actively selected. When /HOLD is brought low, while /CS is low, the DO pin will be at high impedance and signals on the DI and CLK pins will be ignored (don’t care). When /HOLD is brought high, device operation can resume. The /HOLD function can be useful when multiple devices are sharing the same SPI signals. The /HOLD pin is active low. When the QE bit of Status Register-2 is set for Quad I/O, the /HOLD pin function is not available since this pin is used for IO3. See Figure 1a-c for the pin configuration of Quad I/O operation.4.5 Serial Clock (CLK)The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations. ("See SPI Operations")4.6 Reset (/RESET)A dedicated hardware /RESET pin is available on SOIC-16 and TFBGA packages. When it’s driven low for a minimum period of ~1µS, this device will terminate any external or internal operations and return to its power-on state.Note: Hardware /RESET pin is available on SOIC-16 or TFBGA; please contact Winbond for this package.- 9 -5. BLOCK DIAGRAMFigure 2. W25Q128JV Serial Flash Memory Block Diagram6.FUNCTIONAL DESCRIPTIONS6.1Standard SPI InstructionsThe W25Q128JV is accessed through an SPI compatible bus consisting of four signals: Serial Clock (CLK), Chip Select (/CS), Serial Data Input (DI) and Serial Data Output (DO). Standard SPI instructions use the DI input pin to serially write instructions, addresses or data to the device on the rising edge of CLK. The DO output pin is used to read data or status from the device on the falling edge of CLK.SPI bus operation Mode 0 (0,0) and 3 (1,1) are supported. The primary difference between Mode 0 and Mode 3 concerns the normal state of the CLK signal when the SPI bus master is in standby and data is not being transferred to the Serial Flash. For Mode 0, the CLK signal is normally low on the falling and rising edges of /CS. For Mode 3, the CLK signal is normally high on the falling and rising edges of /CS.6.2Dual SPI InstructionsThe W25Q128JV supports Dual SPI operation when using instructions such as “Fast Read Dual Output (3Bh)” and “Fast Read Dual I/O (BBh)”. These instructions allow data to be transferred to or from the device at two to three times the rate of ordinary Serial Flash devices. The Dual SPI Read instructions are ideal for quickly downloading code to RAM upon power-up (code-shadowing) or for executing non-speed-critical code directly from the SPI bus (XIP). When using Dual SPI instructions, the DI and DO pins become bidirectional I/O pins: IO0 and IO1.6.3Quad SPI InstructionsThe W25Q128JV supports Quad SPI operation when using instructions such as “Fast Read Quad Output (6Bh)”,and “Fast Read Quad I/O (EBh). These instructions allow data to be transferred to or from the device four to six times the rate of ordinary Serial Flash. When using Quad SPI instructions, the DI and DO pins become bidirectional IO0 and IO1, with the additional I/O pins: IO2, IO3.6.4Software Reset & Hardware /RESET pinThe W25Q128JV can be reset to the initial power-on state by a software Reset sequence. This sequence must include two consecutive instructions: Enable Reset (66h) & Reset (99h). If the instruction sequence is successfully accepted, the device will take approximately 30µS (t RST)to reset. No instruction will be accepted during the reset period. For the SOIC-16 and TFBGA packages, W25Q128JV provides a dedicated hardware /RESET pin. Drive the /RESET pin low for a minimum period of ~1µS (tRESET*) will interrupt any on-going external/internal operations and reset the device to its initial power-on state. Hardware /RESET pin has higher priority than other SPI input signals (/CS, CLK, IOs).Note:1.Hardware /RESET pin is available on SOIC-16 or TFBGA; please contact Winbond for his package.2.While a faster /RESET pulse (as short as a few hundred nanoseconds) will often reset the device, a 1us minimum isrecommended to ensure reliable operation.3.There is an internal pull-up resistor for the dedicated /RESET pin on the SOIC-16 and TFBGA-24 package. If the reset functionis not needed, this pin can be left floating in the system.6.5Write ProtectionApplications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern, the W25Q128JV provides several means to protect the data from inadvertent writes.6.5.1Write Protect Features∙Device resets when VCC is below threshold∙Time delay write disable after Power-up∙Write enable/disable instructions and automatic write disable after erase or program∙Software and Hardware (/WP pin) write protection using Status Registers∙Additional Individual Block/Sector Locks for array protection∙Write Protection using Power-down instruction∙Lock Down write protection for Status Register until the next power-up∙One Time Program (OTP) write protection for array and Security Registers using Status Register** Note:This feature is available upon special order. Please contact Winbond for details.Upon power-up or at power-down, the W25Q128JV will maintain a reset condition while VCC is below the threshold value of V WI, (See Power-up Timing and Voltage Levels and Figure 43). While reset, all operations are disabled and no instructions are recognized. During power-up and after the VCC voltage exceeds V WI, all program and erase related instructions are further disabled for a time delay of t PUW. This includes the Write Enable, Page Program, Sector Erase, Block Erase, Chip Erase and the Write Status Register instructions. Note that the chip select pin (/CS) must track the VCC supply level at power-up until the VCC-min level and t VSL time delay is reached, and it must also track the VCC supply level at power-down to prevent adverse command sequence. If needed a pull-up resister on /CS can be used to accomplish this.After power-up the device is automatically placed in a write-disabled state with the Status Register Write Enable Latch (WEL) set to a 0. A Write Enable instruction must be issued before a Page Program, Sector Erase, Block Erase, Chip Erase or Write Status Register instruction will be accepted. After completing a program, erase or write instruction the Write Enable Latch (WEL) is automatically cleared to a write-disabled state of 0.Software controlled write protection is facilitated using the Write Status Register instruction and setting the Status Register Protect (SRP, SRL) and Block Protect (CMP, TB, BP[3:0]) bits. These settings allow a portion or the entire memory array to be configured as read only. Used in conjunction with the Write Protect (/WP) pin, changes to the Status Register can be enabled or disabled under hardware control. See Status Register section for further information. Additionally, the Power-down instruction offers an extra level of write protection as all instructions are ignored except for the Release Power-down instruction.The W25Q128JV also provides another Write Protect method using the Individual Block Locks. Each 64KB block (except the top and bottom blocks, total of 126 blocks) and each 4KB sector within the top/bottom blocks (total of 32 sectors) are equipped with an Individual Block Lock bit. When the lock bit is 0, the corresponding sector or block can be erased or programmed; when the lock bit is set to 1, Erase or Program commands issued to the corresponding sector or block will be ignored. When the device is powered on, all Individual Block Lock bits will be 1, so the entire memory array is protected from Erase/Program. An “Individual Block Unlock (39h)” instruction must be issued to unlock any specific sector or block.The WPS bit in Status Register-3 is used to decide which Write Protect scheme should be used. When WPS=0 (factory default), the device will only utilize CMP, SEC, TB, BP[2:0] bits to protect specific areas of the array; when WPS=1, the device will utilize the Individual Block Locks for write protection.。

MEMORY存储芯片N25Q032A13ESC40F中文规格书

Table 11: DDR2 I DD Specifications and Conditions (Die Revision M) (Continued)Notes: 1.I DD specifications are tested after the device is properly initialized. 0°C ≤ T C ≤ +85°C.2.V DD = +1.8V ±0.1V, V DDQ = +1.8V ±0.1V, V DDL = +1.8V ±0.1V, V REF = V DDQ/2.3.I DD parameters are specified with ODT disabled.4.Data bus consists of DQ, DM, DQS, DQS#, RDQS, RDQS#, LDQS, LDQS#, UDQS, andUDQS#. I DD values must be met with all combinations of EMR bits 10 and 11.5.Definitions for I DD conditions:LOW V IN≤ V IL(AC)maxHIGH V IN≥ V IH(AC)minStable Inputs stable at a HIGH or LOW levelFloating Inputs at V REF = V DDQ/2Switching Inputs changing between HIGH and LOW every other clock cycle (once pertwo clocks) for address and control signalsSwitching Inputs changing between HIGH and LOW every other data transfer (onceper clock) for DQ signals, not including masks or strobes6.I DD1, I DD4R, and I DD7 require A12 in EMR to be enabled during testing.7.The following I DD values must be derated (I DD limits increase) on IT-option and AT-optiondevices when operated outside of the range 0°C ≤ T C ≤ 85°C:WhenT C≤ 0°C (IT)I DD2P and I DD3P(SLOW) must be derated by 4%; I DD4R and I DD5W must be de-rated by 2%; and I DD6 and I DD7 must be derated by 7%AC and DC Operating ConditionsTable 13: Recommended DC Operating Conditions (SSTL_18)Input Electrical Characteristics and Operating ConditionsTable 15: Input DC Logic LevelsNote:1.V DDQ + 300mV allowed provided 1.9V is not exceeded.Table 16: Input AC Logic LevelsNote:1.Refer to AC Overshoot/Undershoot Specification (page 58).Figure 13: Single-Ended Input Signal Levels650mV775mV864mV882mV 900mV 918mV 936mV 1,025mV1,150mVNote: 1.Numbers in diagram reflect nominal DDR2-400/DDR2-533 values.Preliminary1Gb: x4, x8, x16 DDR2 SDRAMInput Electrical Characteristics and Operating Conditions。

MEMORY存储芯片NAND225AQA9PZC5E中文规格书

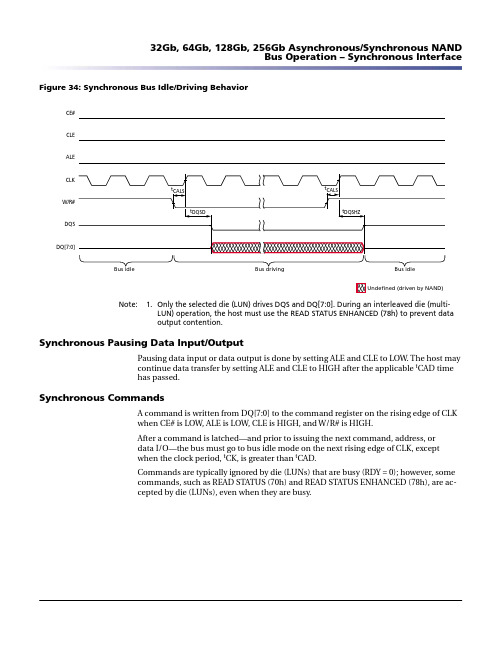

Figure 34: Synchronous Bus Idle/Driving BehaviorCE#CLEALECLKW/R#DQS DQ[7:0]Note: 1.Only the selected die (LUN) drives DQS and DQ[7:0]. During an interleaved die (multi-LUN) operation, the host must use the READ STATUS ENHANCED (78h) to prevent data output contention.Synchronous Pausing Data Input/OutputPausing data input or data output is done by setting ALE and CLE to LOW. The host may continue data transfer by setting ALE and CLE to HIGH after the applicable t CAD time has passed.Synchronous CommandsA command is written from DQ[7:0] to the command register on the rising edge of CLK when CE# is LOW, ALE is LOW, CLE is HIGH, and W/R# is HIGH.After a command is latched—and prior to issuing the next command, address, or data I/O—the bus must go to bus idle mode on the next rising edge of CLK, except when the clock period, t CK, is greater than t CAD.Commands are typically ignored by die (LUNs) that are busy (RDY = 0); however, some commands, such as READ STATUS (70h) and READ STATUS ENHANCED (78h), are ac-cepted by die (LUNs), even when they are busy.32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Bus Operation – Synchronous InterfaceREAD ID Parameter TablesTable 6: Read ID Parameters for Address 00hNote: 1.h = hexadecimal.Table 7: Read ID Parameters for Address 20hNotes: 1.h = hexadecimal.2.XXh = Undefined.32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Identification OperationsTable 11: Feature Addresses 10h and 80h: Programmable Output Drive StrengthNote: 1.See Output Drive Impedance section for details.Table 12: Feature Addresses 81h: Programmable R/B# Pull-Down StrengthNote: 1.This feature address is used to change the default R/B# pull-down strength. Its strengthshould be selected based on the expected loading of R/B#. Full strength is the default,power-on value.32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Configuration Operations。

MEMORY存储芯片MAX3232ESE中文规格书

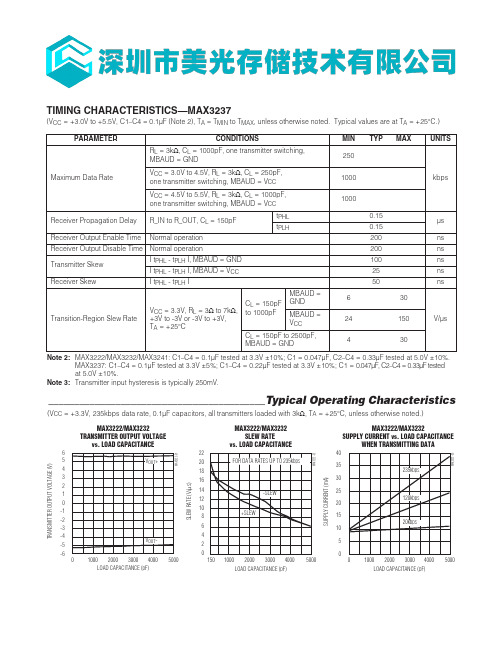

__________________________________________Typical Operating Characteristics(V CC = +3.3V, 235kbps data rate, 0.1µF capacitors, all transmitters loaded with 3k Ω, T A = +25°C, unless otherwise noted.)TIMING CHARACTERISTICS—MAX3237(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)Note 2:MAX3222/MAX3232/MAX3241: C1–C4 = 0.1µF tested at 3.3V ±10%; C1 = 0.047µF, C2–C4 = 0.33µF tested at 5.0V ±10%.MAX3237: C1–C4 = 0.1µF tested at 3.3V ±5%; C1–C4 = 0.22µF tested at 3.3V ±10%; C1 = 0.047µF, C2–C4 = 0.33µF tested at 5.0V ±10%.Note 3:Transmitter input hysteresis is typically 250mV.-6-5-4-3-2-101234560MAX3222/MAX3232TRANSMITTER OUTPUT VOLTAGEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )20003000100040005000246810121416182022150MAX3222/MAX3232SLEW RATEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)S L E W R A T E (V /μs )20003000100040005000510152025303540MAX3222/MAX3232SUPPLY CURRENT vs. LOAD CAPACITANCEWHEN TRANSMITTING DATALOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )20003000100040005000MAX3222/MAX3232/MAX3237/MAX32413.0V to 5.5V, Low-Power, up to 1Mbps, True RS-232 Transceivers Using Four 0.1µF External CapacitorsFigure 4a. MAX3241 Transmitter Output Voltage vs. Load Current per Transmitter3.0V to 5.5V , Low-Power, up to 1Mbps, True RS-232Transceivers Using Four 0.1µF External CapacitorsMAX3222/MAX3232/MAX3237/MAX3241CC = 3.3V5μs/divFigure 5. Loopback Test CircuitHigh Data RatesThe MAX3222/MAX3232/MAX3241 maintain the RS-232±5.0V minimum transmitter output voltage even at high data rates. Figure 5 shows a transmitter loopb ack test circuit. Figure 6 shows a loopb ack test result at 120kbps, and Figure 7 shows the same test at 235kbps. For Figure 6, all transmitters were driven simultaneously at 120kb ps into RS-232 loads in parallel with 1000pF. For Figure 7, a single transmitter was driven at 235kbps, and all transmitters were loaded with an RS-232 receiver in parallel with 1000pF.The MAX3237 maintains the RS-232 ±5.0V minimum transmitter output voltage at data rates up to 1Mb ps. Figure 8 shows a loopb ack test result at 1Mb ps with MBAUD = V CC . For Figure 8, all transmitters were loaded with an RS-232 receiver in parallel with 250pF.fdzfdfbbFigure 6. MAX3241 Loopback Test Result at 120kbpsCC = 3.3V2μs/divFigure 7. MAX3241 Loopback Test Result at 235kbps0V +5V 0V -5V +5V 0VT_INT_OUT = R_IN 5k R_OUT 150pF200ns/divCC = 3.3VFigure 8. MAX3237 Loopback Test Result at 1000kbps (MBAUD = V CC )___________________Chip Topography___________________Chip InformationT1INT2IN 0.087"(2.209mm)R2OUTR2IN T2OUT R1OUTR1INT1OUTV CCV+C1+ENC1-C2+C2-V-GNDTRANSISTOR COUNT: 339SUBSTRATE CONNECTED TO GNDMAX3222/MAX3232/MAX3237/MAX3241 3.0V to 5.5V, Low-Power, up to 1Mbps, True RS-232Transceivers Using Four 0.1µF External Capacitors。

MEMORY存储芯片N25Q032A13EF640F中文规格书

Micron Serial NOR Flash Memory 3V, Multiple I/O, 4KB Sector EraseN25Q032AFeatures•SPI-compatible serial bus interface•108 MHz (MAX) clock frequency•2.7–3.6V single supply voltage•Dual/quad I/O instruction provides increased throughput up to 432 MHz•Supported protocols–Extended SPI, dual I/O, and quad I/O •Execute-in-place (XIP) mode for all three protocols –Configurable via volatile or nonvolatile registers –Enables memory to work in XIP mode directly af-ter power-on•PROGRAM/ERASE SUSPEND operations •Continuous read of entire memory via a single com-mand–FAST READ–QUAD or DUAL OUTPUT FAST READ–QUAD or DUAL I/O FAST READ•Flexible to fit application–Configurable number of dummy cycles–Configurable output buffer–RESET function available upon customer request •64-byte, user-lockable, one-time programmable (OTP) dedicated area•Erase capability–Subsector erase 4KB uniform granularity blocks –Sector erase 64KB uniform granularity blocks–Full-chip erase •Write protection–Software write protection applicable to every 64KB sector via volatile lock bit–Hardware write protection: protected area size defined by four nonvolatile bits (BP0, BP1, BP2,and TB)–Additional smart protections, available upon re-quest•Electronic signature–JEDEC-standard, 2-byte signature (BA16h)–Unique ID code: 17 read-only bytes, including:•Two additional extended device ID bytes toidentify device factory options•Customized factory data (14 bytes)•Minimum 100,000 ERASE cycles per sector •More than 20 years data retention•Packages (JEDEC-standard, RoHS compliant)–F4 = U-PDFN-8 4mm x 3mm (MLP8)–F6 = V-PDFN-8 6mm x 5mm (MLP8)–F8 = V-PDFN-8 8mm x 6mm (MLP8)–12 = T-PBGA-24b05 6mm x 8mm–SC = SOP2-8 150 mils body width (SO8N)–SF = SOP2-16 300 mils body width (SO16W)–SE = SOP2-8 208 mils body width (SO8W)CCMTD-1725822587-8448n25q_32mb_3v_65nm.pdf - Rev. K 05/18 EN 1Micron Technology, Inc. reserves the right to change products or specifications without notice.© 2011 Micron Technology, Inc. All rights reserved.Products and specifications discussed herein are subject to change by Micron without notice.Signal AssignmentsFigure 2: 8-Pin, VDFPN8 – MLP8 and SOP2 – SO8W (Top View)12348765S#DQ1W#/V PP /DQ2V SSV CC HOLD#/DQ3C DQ0Notes: 1.On the underside of the MLP8 package, there is an exposed central pad that is pulledinternally to V SS and must not be connected to any other voltage or signal line on the PCB.2.Reset functionality is available in devices with a dedicated part number. See Part Num-ber Ordering Information for complete package names and details.Figure 3: 16-Pin, Plastic Small Outline – SO16 (Top View)12345678161514131211109C DQ0DNU DNU DNU DNU V SS W#/V PP /DQ2HOLD#/DQ3V CCDNUDNUDNUDNUS#DQ1Note: 1.Reset functionality is available in devices with a dedicated part number. See Part Num-ber Ordering Information for complete package names and details.32Mb, 3V , Multiple I/O Serial Flash Memory Signal AssignmentsCCMTD-1725822587-8448n25q_32mb_3v_65nm.pdf - Rev. K 05/18 EN 9Micron Technology, Inc. reserves the right to change products or specifications without notice.© 2011 Micron Technology, Inc. All rights reserved.Memory OrganizationMemory Configuration and Block DiagramEach page of memory can be individually programmed. Bits are programmed from one through zero. The device is subsector, sector, or bulk-erasable, but not page-erasable.Bits are erased from zero through one. The memory is configured as 4,194,304 bytes (8bits each); 64 sectors (64KB each); 1024 subsectors (4KB each); and 16,384 pages (256bytes each); and 64 OTP bytes are located outside the main memory array.Figure 5: Block DiagramHOLD#S#W#/VCDQ0DQ132Mb, 3V , Multiple I/O Serial Flash Memory Memory OrganizationCCMTD-1725822587-8448n25q_32mb_3v_65nm.pdf - Rev. K 05/18 EN 13Micron Technology, Inc. reserves the right to change products or specifications without notice.© 2011 Micron Technology, Inc. All rights reserved.Table 15: Flag Status Register Bit Definitions (Continued)Notes: 1.Register bits are read by READ FLAG STATUS REGISTER command. All bits are volatile.2.These program/erase controller settings apply only to PROGRAM or ERASE command cy-cles in progress, or to the specific WRITE command cycles in progress as shown here.3.Status bits are reset automatically.4.Error bits must be reset by CLEAR FLAG STATUS REGISTER command.5.Typical errors include operation failures and protection errors caused by issuing a com-mand before the error bit has been reset to 0.32Mb, 3V , Multiple I/O Serial Flash Memory Nonvolatile and Volatile RegistersCCMTD-1725822587-8448n25q_32mb_3v_65nm.pdf - Rev. K 05/18 EN 26Micron Technology, Inc. reserves the right to change products or specifications without notice.© 2011 Micron Technology, Inc. All rights reserved.。

MEMORY存储芯片W25Q32JVSSIQ中文规格书

6.5Write ProtectionApplications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern, the W25Q32JV provides several means to protect the data from inadvertent writes.Write Protect Features∙Device resets when VCC is below threshold∙Time delay write disable after Power-up∙Write enable/disable instructions and automatic write disable after erase or program∙Software and Hardware (/WP pin) write protection using Status Registers∙Additional Individual Block/Sector Locks for array protection∙Write Protection using Power-down instruction∙Lock Down write protection for Status Register until the next power-up∙One Time Program (OTP) write protection for array and Security Registers using Status Register* *Note:This feature is available upon special order. Please contact Winbond for details.Upon power-up or at power-down, the W25Q32JV will maintain a reset condition while VCC is below the threshold value of V WI, (See Power-up Timing and Voltage Levels and Figure 43). While reset, all operations are disabled and no instructions are recognized. During power-up and after the VCC voltage exceeds V WI, all program and erase related instructions are further disabled for a time delay of t PUW. This includes the Write Enable, Page Program, Sector Erase, Block Erase, Chip Erase and the Write Status Register instructions. Note that the chip select pin (/CS) must track the VCC supply level at power-up until the VCC-min level and t VSL time delay is reached, and it must also track the VCC supply level at power-down to prevent adverse command sequence. If needed a pull-up resister on /CS can be used to accomplish this.After power-up the device is automatically placed in a write-disabled state with the Status Register Write Enable Latch (WEL) set to a 0. A Write Enable instruction must be issued before a Page Program, Sector Erase, Block Erase, Chip Erase or Write Status Register instruction will be accepted. After completing a program, erase or write instruction the Write Enable Latch (WEL) is automatically cleared to a write-disabled state of 0.Software controlled write protection is facilitated using the Write Status Register instruction and setting the Status Register Protect (SRP, SRL) and Block Protect (CMP, TB, BP[2:0]) bits. These settings allow a portion or the entire memory array to be configured as read only. Used in conjunction with the Write Protect (/WP) pin, changes to the Status Register can be enabled or disabled under hardware control. See Status Register section for further information. Additionally, the Power-down instruction offers an extra level of write protection as all instructions are ignored except for the Release Power-down instruction.The W25Q32JV also provides another Write Protect method using the Individual Block Locks. Each 64KB block (except the top and bottom blocks, total of 62 blocks) and each 4KB sector within the top/bottom blocks (total of 32 sectors) are equipped with an Individual Block Lock bit. When the lock bit is 0, the corresponding sector or block can be erased or programmed; when the lock bit is set to 1, Erase or Program commands issued to the corresponding sector or block will be ignored. When the device is powered on, all Individual Block Lock bits will be 1, so the entire memory array is protected from Erase/Program. An “Individual Block Unlock (39h)” instruction must be issued to unlock any specific sector or block.The WPS bit in Status Register-3 is used to decide which Write Protect scheme should be used. When WPS=0 (factory default), the device will only utilize CMP, SEC, TB, BP[2:0] bits to protect specific areas of the array; when WPS=1, the device will utilize the Individual Block Locks for write protection.Figure 4c. Status Register-3Write Protect Selection (WPS) –Volatile/Non-Volatile WritableThe WPS bit is used to select which Write Protect scheme should be used. When WPS=0, the device will use the combination of CMP, SEC, TB, BP[2:0] bits to protect a specific area of the memory array. When WPS=1, the device will utilize the Individual Block Locks to protect any individual sector or blocks. Thedefault value for all Individual Block Lock bits is 1 upon device power on or after reset.Output Driver Strength (DRV1, DRV0) –Volatile/Non-Volatile WritableThe DRV1 & DRV0 bits are used to determine the output driver strength for the Read operations.Reserved Bits –Non FunctionalThere are a few reserved Status Register bits that may be read out as a “0” or “1”. It is recommended to ignore the values of those bits. During a “Write Status Register” instruction, the Reserved Bits can be written as “0”, but there will not be any effects.Status Register Memory Protection (WPS = 0, CMP = 0)Notes:1.X = don’t care2.L = Lower; U = Upper3.If any Erase or Program command specifies a memory region that contains protected data portion, this commandwill be ignored.Write Status Register-1 (01h), Status Register-2 (31h) & Status Register-3 (11h)The Write Status Register instruction allows the Status Registers to be written. The writable Status Register bits include: SEC, TB, BP[2:0] in Status Register-1; CMP, LB[3:1], QE, SRL in Status Register-2; DRV1, DRV0, WPS in Status Register-3. All other Status Register bit locations are read-only and will not be affected by the Write Status Register instruction. LB[3:1] are non-volatile OTP bits, once it is set to 1, it cannot be cleared to 0.To write non-volatile Status Register bits, a standard Write Enable (06h) instruction must previously have been executed for the device to accept the Write Status Register instruction (Status Register bit WEL must equal 1). Once write enabled, the instruction is entered by driving /CS low, sending the instruction code “01h/31h/11h”, and then writing the status register data byte as illustrated in Figure 9a.To write volatile Status Register bits, a Write Enable for Volatile Status Register (50h) instruction must have been executed prior to the Write Status Register instruction (Status Register bit WEL remains 0). However, SRL and LB[3:1] cannot be changed from “1” to “0” because of the OTP protection for these bits. Upon power off or the execution of a Software/Hardware Reset, the volatile Status Register bit values will be lost, and the non-volatile Status Register bit values will be restored.During non-volatile Status Register write operation (06h combined with 01h/31h/11h), after /CS is driven high, the self-timed Write Status Register cycle will commence for a time duration of t W(See AC Characteristics). While the Write Status Register cycle is in progress, the Read Status Register instruction may still be accessed to check the status of the BUSY bit. The BUSY bit is a 1 during the Write Status Register cycle and a 0 when the cycle is finished and ready to accept other instructions again. After the Write Status Register cycle has finished, the Write Enable Latch (WEL) bit in the Status Register will be cleared to 0.During volatile Status Register write operation (50h combined with 01h/31h/11h), after /CS is driven high, the Status Register bits will be refreshed to the new values within the time period of t SHSL2(See AC Characteristics). BUSY bit will remain 0 during the Status Register bit refresh period.Refer to section 7.1 for Status Register descriptions.Figure 9a. Write Status Register-1/2/3 Instruction。

MEMORY存储芯片N25W032A11EF640F中文规格书