Jtag的各种引脚定义

JTAG接口总结

并口与连接1.并行口基地址:0x0378 新系统通用,通常是LPT1,也可以是LPT2,通常使用中断IRQ70x0278 通常是LPT2,也可以是LPT1,LPT3(只能用此基地址),通常使用中断IRQ5 2.寄存器定义3.状态寄存器(379)和控制寄存器(37A)的定义:5.连接方式a)hybus255与并口的连接是通过74CH541与并口连接LPT D0 Pin 2 and TCK J10 Pin 4LPT D1 Pin 3 and TDI J10 Pin 11LPT D2 Pin 4 and TMS J10 Pin 9LPT Busy Pin 11 and TDO J10 Pin 13b)2410以及44b0连接图TCK---------------->DATA0TDI---------------->DATA1TMS---------------->DATA2TDO---------------->STATUS76.寄存器的读写a)先对控制寄存器(Control)初始化如果禁止中断用out(37A,0x80),如果使用中断用out(37A,0x90)b)写一个寄存器的两条基本指令:out(37B,addr);// 将addr写入用户设备地址寄存器写:out(37C,data);// 将数据data写入addr指向的用户设备空间单元读:in(37C);// 从addr指向的用户设备空间单元中读取数据JTAG接口信息1.TCK:输入移位时钟TMS和TDI的数据在TCK的上升沿被采样数据在时钟的下降沿输出到TDO2.TMS:输入方式选择TMS用于控制TAP状态机3.TDI:输入。

输入到指令寄存器IR或数据寄存器DR的数据出现在TDI输入端在TCK的上升沿被采样4.TDO:TDO输出来自指令寄存器或数据寄存器的数据在时钟的下降沿被移出到TDOTAP状态机*状态机框图中位于箭头旁边的数字表示TCK变高时TMS的逻辑状态JTAG时序1.TAP复位时序在hybus255-Jflash中void test_logic_reset(void){putp(1,1,IGNORE_PORT); // keep TMS set to 1 force a test logic resetputp(1,1,IGNORE_PORT); // no matter where you are in the TAP controller putp(1,1,IGNORE_PORT);putp(1,1,IGNORE_PORT);putp(1,1,IGNORE_PORT);putp(1,1,IGNORE_PORT);}2.IR,DR扫描时序。

JTAG各类接口针脚定义及含义

JTAG各类接口针脚定义及含义JTAG(Joint Test Action Group;联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

接口JTAG最初是用来对芯片进行接口编辑JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对内部节点进行测试。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG 链,能实现对各个器件分别测试。

如今,JTAG接口还常用于实现ISP(In-System Programmer,在系统编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程然后再装到板上,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。

JTAG接口可对DSP芯片内部的所有部件进行编程。

JTAG引脚定义具有JTAG口的芯片都有如下JTAG引脚定义:TCK——测试时钟输入;TDI——测试数据输入,数据通过TDI输入JTAG口;TDO——测试数据输出,数据通过TDO从JTAG口输出;TMS——测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。

可选引脚TRST——测试复位,输入引脚,低电平有效。

含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。

JTAG内部有一个状态机,称为TAP控制器。

TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。

JTAG芯片的边界扫描寄存器JTAG标准定义了一个串行的移位寄存器。

寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。

JTAG接口

JTAG接口

JTAG口(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行调试和仿真。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

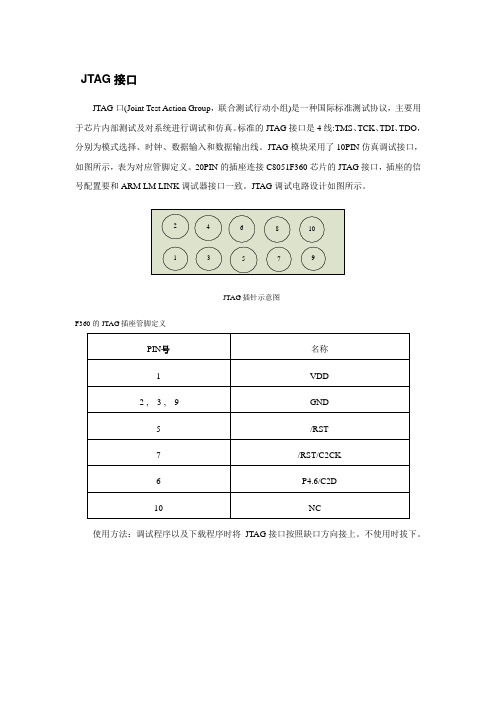

JTAG模块采用了10PIN仿真调试接口,如图所示,表为对应管脚定义。

20PIN的插座连接C8051F360芯片的JTAG接口,插座的信号配置要和ARM LM LINK调试器接口一致。

JTAG调试电路设计如图所示。

136

79

248

5

10

JTAG插针示意图

F360的JTAG插座管脚定义

PIN号名称

1 VDD

2 ,

3 , 9 GND

5 /RST

7 /RST/C2CK

6 P4.6/C2D

10 NC

使用方法:调试程序以及下载程序时将JTAG接口按照缺口方向接上。

不使用时拔下。

14针与20针jtag接口介绍

JTAG接口定义JTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, JTAG 技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路 TAP ( Test Access Port ,测试访问口),通过专用的 J TAG 测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持 JTAG 协议,如 ARM 、 DSP 、 FPGA 器件等。

标准的JTAG 接口是 4 线: TMS 、 TCK 、 TDI 、 TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

JTAG 测试允许多个器件通过 JTAG 接口串联在一起,形成一个 JTAG 链,能实现对各个器件分别测试。

JTAG 接口还常用于实现 ISP ( In-System Programmable 在系统编程)功能,如对 FLASH器件进行编程等。

通过 JTAG 接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。

目前 JTAG 接口的连接有两种标准,即 14 针接口和 20 针接口,其定义分别如下所示。

14 针JTAG 接口定义:14 针 JTAG 接口定义引脚名称描述1 、 13 VCC 接电源2 、 4 、 6 、 8 、 10 、 14 GND 接地3 nTRST 测试系统复位信号5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 TDO 测试数据串行输出12 NC 未连接20 针 JTAG 接口定义引脚名称描述VTref 目标板参考电压,接电源2 VCC 接电源3 nTRST 测试系统复位信号4、6、8、10、12、14、16、18、20 GND 接地5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 RTCK 测试时钟返回信号13 TDO 测试数据串行输出15 nRESET 目标系统复位信号17 、 19 NC 未连接。

jtag标准 引脚定义

jtag标准引脚定义

JTAG标准的引脚定义

JTAG(Joint Test Action Group)是一种用于测试和调试电子设备的标准接口。

它能够通过几根线路实现对设备内部的观察和控制,用于芯片的生产和维护。

在JTAG标准中,定义了一系列的引脚,用于实现与设备的通信和控制。

根据JTAG标准的定义,JTAG接口包括四根信号线(TMS、TCK、TDO和TDI)和一个共享引脚(TRST)。

这些引脚的定义如下:

1. TMS(Test Mode Select):此引脚用于选择设备的测试模式。

在测试过程中,通过改变TMS引脚的状态,可以控制设备进入不同的测试状态。

2. TCK(Test Clock):此引脚用于提供时钟信号,控制测试数据的传输速率。

TCK信号是通过在TCK引脚上周期性地切换高和低电平来控制的。

3. TDO(Test Data Out):此引脚用于从设备读取测试数据。

在测试过程中,

设备通过TDO引脚将测试数据输出。

4. TDI(Test Data In):此引脚用于向设备输入测试数据。

在测试过程中,通

过TDO引脚将测试数据输入给设备。

5. TRST(Test Reset):此引脚用于将设备重置为初始状态,以便开始测试过程。

TRST引脚是一个共享引脚,可以在需要的情况下选择使用或不使用。

以上就是JTAG标准中定义的引脚及其功能的简要介绍。

这些引脚的正确使用

可以帮助测试人员有效地测试和调试电子设备。

JTAG接口已经成为现代电子设备

测试和调试的关键部分,并广泛应用于各个领域。

Jtag的各种引脚定义

使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。

所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。

以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。

Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。

由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。

正版的Jlink是卖的很贵的。

大概是1000到2000RMB吧。

不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。

所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。

除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。

还有人制作了开源版本的JTAG仿真器——OpenJTAG。

而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。

比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。

还有飞思卡尔公司的USBDM和OSJTAG。

他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。

这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。

5pin jtag标准

5pin jtag标准

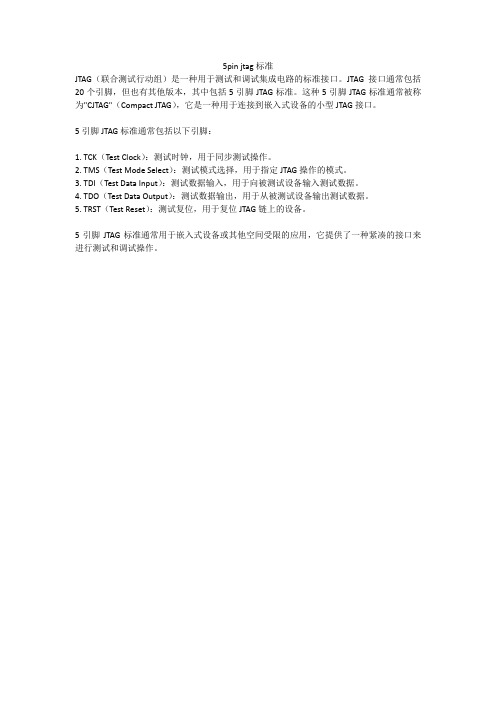

JTAG(联合测试行动组)是一种用于测试和调试集成电路的标准接口。

JTAG接口通常包括20个引脚,但也有其他版本,其中包括5引脚JTAG标准。

这种5引脚JTAG标准通常被称为"CJTAG"(Compact JTAG),它是一种用于连接到嵌入式设备的小型JTAG接口。

5引脚JTAG标准通常包括以下引脚:

1. TCK(Test Clock):测试时钟,用于同步测试操作。

2. TMS(Test Mode Select):测试模式选择,用于指定JTAG操作的模式。

3. TDI(Test Data Input):测试数据输入,用于向被测试设备输入测试数据。

4. TDO(Test Data Output):测试数据输出,用于从被测试设备输出测试数据。

5. TRST(Test Reset):测试复位,用于复位JTAG链上的设备。

5引脚JTAG标准通常用于嵌入式设备或其他空间受限的应用,它提供了一种紧凑的接口来进行测试和调试操作。

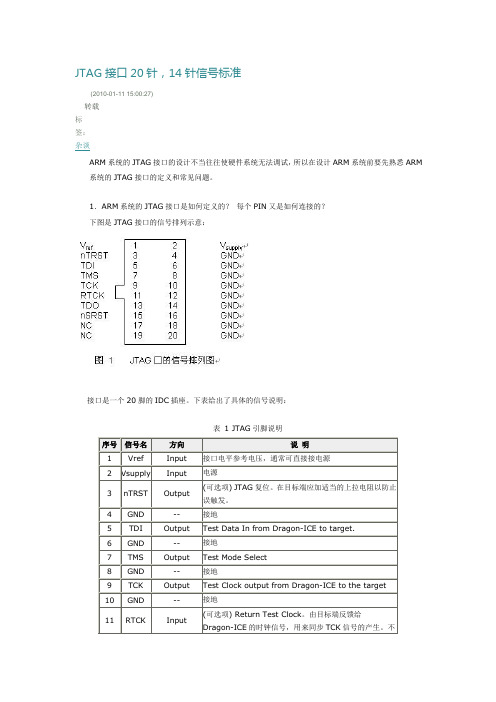

ARM系统的JTAG接口

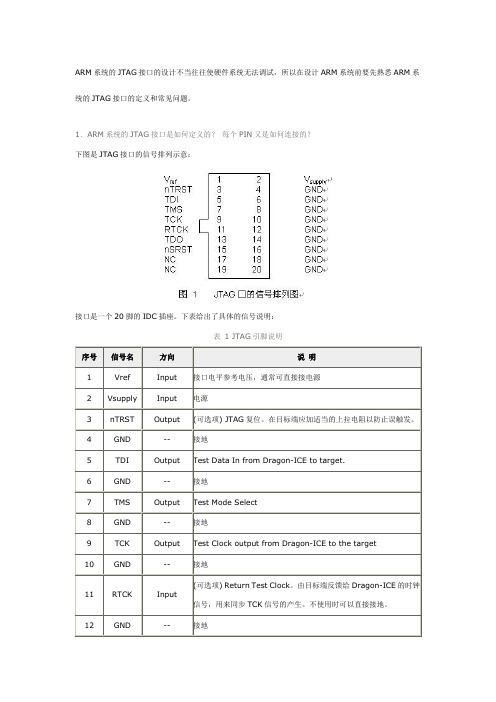

ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

下表给出了具体的信号说明:表1 JTAG引脚说明2.目标系统如何设计?目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。

RTCK和nTRST这两个信号根据目标ASIC有否提供对应的引脚来选用。

nSRST则根据目标系统的设计考虑来选择使用。

下面是一个典型的连接关系图:复位电路中可以根据不同的需要包含上电复位、手动复位等等功能。

如果用户希望系统复位信号nSRST能同时触发JTAG口的复位信号nTRST,则可以使用一些简单的组合逻辑电路来达到要求。

后面给出了一种电路方案的效果图。

图3 一个复位电路结构的例子在目标系统的PCB设计中,最好把JTAG接口放置得离目标ASIC近一些,如果这两者之间的连线过长,会影响JTAG口的通信速率。

另外电源的连线也需要加以额外考虑,因为Dragon-ICE要从目标板上吸取超过100mA的大电流。

最好能有专门的敷铜层来供电,假如只能使用连线供电的话,最小线宽不应小于10mil (0.254mm)。

3. 14脚JTAG如何与20JTAG连接?Dragon-ICE使用工业标准的20脚JTAG插头,但是有些老的系统采用一种14脚的插座。

这两类接口的信号排列如下:这两类接口之间的信号电气特性都是一样的,因此可以把对应的信号直接连起来进行转接。

Dragon-ICE配备这种转接卡,随机配备。

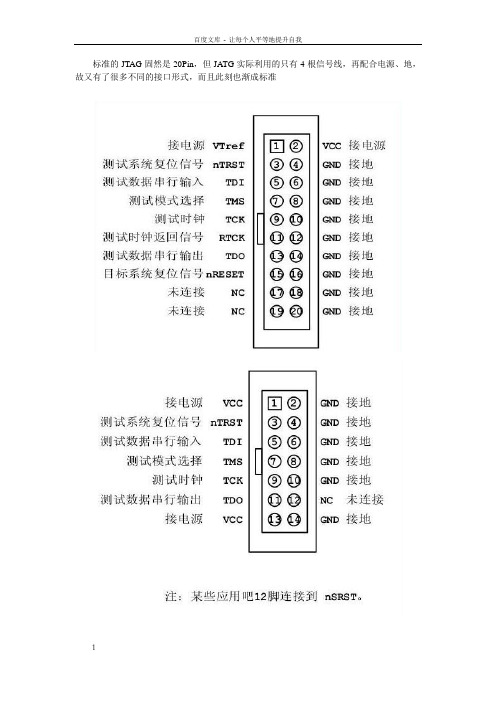

JTAG接口引脚概念

标准的JTAG固然是20Pin,但JATG实际利用的只有4根信号线,再配合电源、地,故又有了很多不同的接口形式,而且此刻也渐成标准1.TCK Programmer JTAG Clock(JTAG管脚中的输入时钟信号,对编程和边界扫描都需要)2.GND1 Signal Reference(信号地)3.TDO Target Board Test Data Output(JTAG管脚中串行的输出数据信号,对编程和边界扫描都需要)4.VTref 接开发板电源5.TMS Programmer Test Mode Select(JTAG管脚中的测试选通信号,对编程和边界扫描都需要)6.VJTAG Target Board JTAG Supply V oltage(目标板JTAG电源)7.VPUMP2 Programmer/Target Board Programming Supply Voltage(目标板JTAG电源)8.nTRST Programmer JTAG Test Reset (Hi-Z with 10 kΩ pull-down, HIGH, LOW,ortoggling)(JTAG管脚中异步复位信号,对编程和边界扫描都需要,用10K电阻上拉到Vddp)9.TDI Programmer Test Data Input(JTAG管脚中串行的输入数据信号,对编程和边界扫描都需要)10.GND1 Signal Reference(信号地)Notes:1. Both GND pins must be connected.(所有的地引脚都要连接)2. FlashPro3 can provide VPUMP if there is only one device on the target board.(若是目标板只有一个芯片,则VPUMP能够由FlashPro3提供。

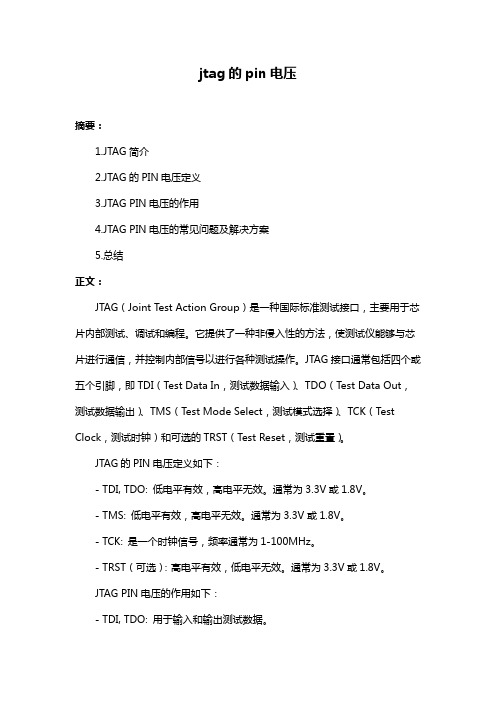

jtag的pin电压

jtag的pin电压摘要:1.JTAG简介2.JTAG的PIN电压定义3.JTAG PIN电压的作用4.JTAG PIN电压的常见问题及解决方案5.总结正文:JTAG(Joint Test Action Group)是一种国际标准测试接口,主要用于芯片内部测试、调试和编程。

它提供了一种非侵入性的方法,使测试仪能够与芯片进行通信,并控制内部信号以进行各种测试操作。

JTAG接口通常包括四个或五个引脚,即TDI(Test Data In,测试数据输入)、TDO(Test Data Out,测试数据输出)、TMS(Test Mode Select,测试模式选择)、TCK(Test Clock,测试时钟)和可选的TRST(Test Reset,测试重置)。

JTAG的PIN电压定义如下:- TDI, TDO: 低电平有效,高电平无效。

通常为3.3V或1.8V。

- TMS: 低电平有效,高电平无效。

通常为3.3V或1.8V。

- TCK: 是一个时钟信号,频率通常为1-100MHz。

- TRST(可选):高电平有效,低电平无效。

通常为3.3V或1.8V。

JTAG PIN电压的作用如下:- TDI, TDO: 用于输入和输出测试数据。

- TMS: 用于选择和控制测试模式。

- TCK: 用于产生测试时钟,驱动JTAG操作。

- TRST(可选):用于重置测试状态,以便在测试过程中进行复位操作。

在实际应用中,JTAG PIN电压可能遇到一些常见问题,例如:1.不同电压等级的PIN连接在一起,可能导致信号干扰或损坏。

2.PIN电压与实际电路中的其他电压等级不匹配,可能影响JTAG功能的正常工作。

3.JTAG接口的ESD保护不足,可能导致静电放电损坏。

针对以上问题,可以采取以下解决方案:1.确保使用相同电压等级的PIN连接,避免不同电压等级的PIN直接相连。

2.在设计电路时,确保JTAG PIN电压与其他电路电压等级匹配。

JTAG使用说明

JTAG使用说明遵循JTAG的器件包含以下几个管脚TCK 测试时钟输入,它和系统时钟不同TDI测试数据输入,通过它数据移位进入器件TDO测试数据输出,通过它数据从器件移出TMS测试模式选择,在JTAG规范中TMS命令选择测试模式TRST测试复位输入,它为TAP控制器提供异步初始化器件的测试支持功能是通过TAP控制器来实现的。

TAP是一个状态机,它控制控制所有相关操作,每种遵循JTAG的器件都有自己的TAP控制器,通过TCK和TMS可以使状态机内部的状态发生变化,从而支持诸如断点、单步、内部观察等调试工作。

本章针对ARM7TDMI介绍调试结构。

ARM的调试体系采用协议转换器来使调试器通过JTAG与ARM核直接通信。

前面JTAG标准中提到的扫描链功能是测试用,这里把它作为调试用:捕获数据总线上的信号并向内核或存储器插入新的信息。

ARM7TDMI-S核内具有EmbeddedICE逻辑,EmbeddedICE逻辑提供对片内调试的支持。

调试指令直接通过扫描链插入ARM内核并执行。

根据插入调试指令的不同,内核可以处于观察、保存或改变状态。

ARM的调试体系可以使程序指令执行速度处于调试速度或全速运行。

在ARM中采用JTAG的特点是:通过JTAG接口可以观察ARM内核状态和系统状态(注意:系统状态包括片内外设,不同于内核状态);不占用额外的目标系统资源;提供传统的断点访问和观察点访问;不再需要另外的UART端口来和监控程序通信。

围绕ARM内核有两个扫描链:围绕整个内核外围的一个扫描链以及仅仅覆盖数据总线和断点的扫描链。

由于后者的链比较短,从而使调试指令和数据可以快速插入内核,避免了额外的时间ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

ti jtag14pin管脚定义

ti jtag14pin管脚定义TI JTAG 14pin是Texas Instruments(德州仪器)公司定义的一种用于联接微处理器和其他电子设备进行调试和编程的接口标准。

JTAG(Joint Test Action Group)是一个开放性标准,得到了许多公司的支持和采用。

TI JTAG 14pin是一种比较常见的JTAG接口类型,它具有14pin的针脚数量。

TI JTAG 14pin接口的管脚定义如下:1. GND(地线):引脚用于接地,提供电路的电流回路。

2. VTREF(电源电压引脚):引脚用于提供外部引脚电平的参考电压。

3. TMS(测试模式选择引脚):引脚用于控制JTAG控制器和被测设备之间的模式转换。

4. TDI(测试数据输入引脚):引脚用于向被测设备传输数据。

5. TCK(测试时钟引脚):引脚用于提供给JTAG控制器和被测设备的时钟信号。

6. TDO(测试数据输出引脚):引脚用于从被测设备读取数据。

7. RST(复位引脚):引脚用于复位被测设备。

8. N/C(无连接引脚):引脚没有连接,不用于任何功能。

9. SRST(系统复位引脚):引脚用于系统级别的复位。

10. TRST(测试复位引脚):引脚用于测试级别的复位。

11. GND(地线):引脚用于接地。

12. VCC(供电引脚):引脚用于为JTAG接口提供电源。

13. N/C(无连接引脚):引脚没有连接,不用于任何功能。

14. N/C(无连接引脚):引脚没有连接,不用于任何功能。

TI JTAG 14pin接口的使用方法:1.接线:将JTAG接口的各个管脚按照定义连接到目标设备上,一般使用排针或插座进行连接。

2.供电:将VCC引脚连接到适当电源上,确保设备具有所需的供电电压。

3.控制信号:使用JTAG控制器通过TMS和TCK引脚来控制设备和数据流的转换。

4.数据传输:通过TDI引脚将测试数据输入到目标设备,通过TDO 引脚将被测设备返回的数据读取出来。

JTAG各类接口针脚定义及含义

JTAG各类接口针脚定义及含义JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。

一、引脚定义Test Clock Input (TCK) -----强制要求1TCK在IEEE1149.1标准里是强制要求的。

TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode Selection Input (TMS) -----强制要求2TMS信号在TCK的上升沿有效。

TMS在IEEE1149.1标准里是强制要求的。

TMS信号用来控制TAP状态机的转换。

通过TMS信号,可以控制TAP在不同的状态间相互转换。

Test Data Input (TDI) -----强制要求3TDI在IEEE1149.1标准里是强制要求的。

TDI是数据输入的接口。

所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

Test Data Output (TDO) -----强制要求4TDO在IEEE1149.1标准里是强制要求的。

TDO是数据输出的接口。

所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

Test Reset Input (TRST) ----可选项1这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。

TRST可以用来对TAPController进行复位(初始化)。

因为通过TMS 也可以对TAP Controll进行复位(初始化)。

所以有四线JTAG与五线JTAG之分。

(VTREF) -----强制要求5接口信号电平参考电压一般直接连接Vsupply。

这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)Return Test Clock ( RTCK) ----可选项2可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。

JLink和JTAG接口详细及接线

接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定

ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)

Return Test Clock(RTCK)----可选项2

可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的

产生,不使用时直接接地。

System Reset(nSRST)----可选项3

Test Reset Input(TRST)----可选项1

这个信号接口在IEEE1149.1标准里是可选的,并不是强制要求的。

TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以

对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。

(VTREF)-----强制要求5

可选项,与目标板上的系统复位信号相连,可以直接对目标系统复

位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适

当的上拉电阻。

说明:

1脚:通常连接到目标板的vdd,用来检测目标系统是否供电;检测

原理上图中有简单的说明。

2脚:原版的JLink这个引脚没有使用,不提供Vsupply输出,而很

TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制

要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制

TAP在不同的状态间相互转换。

Test Data Input(TDI)-----强制要求3

TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口。

多改造版的JLink通过跳线选择从该引脚输出3.3V的电压给外边,我的就是

JTAG接口20针,14针信号标准

JTAG接口20针,14针信号标准(2010-01-11 15:00:27)转载标签:杂谈ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM 系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

下表给出了具体的信号说明:表1 JTAG引脚说明序号信号名方向说明1 Vref Input 接口电平参考电压,通常可直接接电源2 Vsupply Input 电源3 nTRST Output (可选项) JTAG复位。

在目标端应加适当的上拉电阻以防止误触发。

4 GND -- 接地5 TDI Output Test Data In from Dragon-ICE to target.6 GND -- 接地7 TMS Output Test Mode Select8 GND -- 接地9 TCK Output Test Clock output from Dragon-ICE to the target10 GND -- 接地11 RTCK Input (可选项) Return Test Clock。

由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。

不使用时可以直接接地。

12GND -- 接地 13TDO Input Test Data Out from target to Dragon-ICE. 14 GND -- 接地15 nSRST Input/Output (可选项) System Reset ,与目标板上的系统复位信号相连。

可以直接对目标系统复位,同时可以检测目标系统的复位情况。

为了防止误触发,应在目标端加上适当的上拉电阻。

16GND -- 接地 17NC 保留 18GND -- 接地 19NC -- 保留 20 GND -- 接地。

jtag各类接口针脚定义含义以及swd接线方式

JTAG各类接口针脚定义、含义以及SWD接线方式JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。

一、引脚定义Test Clock Input (TCK) -----强制要求1TCK在IEEE1149.1标准里是强制要求的。

TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode Selection Input (TMS) -----强制要求2TMS信号在TCK的上升沿有效。

TMS在IEEE1149.1标准里是强制要求的。

TMS信号用来控制TAP状态机的转换。

通过TMS信号,可以控制TAP在不同的状态间相互转换。

Test Data Input (TDI) -----强制要求3TDI在IEEE1149.1标准里是强制要求的。

TDI是数据输入的接口。

所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

Test Data Output (TDO) -----强制要求4TDO在IEEE1149.1标准里是强制要求的。

TDO是数据输出的接口。

所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

Test Reset Input (TRST) ----可选项1这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。

TRST可以用来对TAPController进行复位(初始化)。

因为通过TMS也可以对TAP Controll进行复位(初始化)。

所以有四线JTAG与五线JTAG之分。

(VTREF) -----强制要求5接口信号电平参考电压一般直接连接Vsupply。

这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)Return Test Clock ( RTCK) ----可选项2可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK 信号的产生,不使用时直接接地。

JLink和JTAG接口详细及接线

JLink 和JTAG 接口详细及接线JTAG 各类接口针脚定义、含义一、引脚定义Test Clock Input (TCK)-----强制要求1TCK 在IEEE1149.1 标准里是强制要求的。

TCK 为TAP 的操作提供了一个独立的、基本的时钟信号,TAP 的所有操作都是通过这个时钟信号来驱动的。

Test Mode SelecTIon Input (TMS)-----强制要求2TMS 信号在TCK 的上升沿有效。

TMS 在IEEE1149.1 标准里是强制要求的。

TMS 信号用来控制TAP 状态机的转换。

通过TMS 信号,可以控制TAP 在不同的状态间相互转换。

Test Data Input (TDI)-----强制要求3TDI 在IEEE1149.1 标准里是强制要求的。

TDI 是数据输入的接口。

所有要输入到特定寄存器的数据都是通过TDI 接口一位一位串行输入的(由TCK 驱动)。

Test Data Output (TDO)-----强制要求4TDO 在IEEE1149.1 标准里是强制要求的。

TDO 是数据输出的接口。

所有要从特定的寄存器中输出的数据都是通过TDO 接口一位一位串行输出的(由TCK 驱动)。

Test Reset Input (TRST)----可选项1这个信号接口在IEEE 1149.1 标准里是可选的,并不是强制要求的。

TRST 可以用来对TAPController 进行复位(初始化)。

因为通过TMS 也可以对TAP Controll 进行复位(初始化)。

所以有四线JTAG 与五线JTAG 之分。

(VTREF)-----强制要求5接口信号电平参考电压一般直接连接Vsupply。

这个可以用来确定ARM 的JTAG 接口使用的逻辑电平(比如3.3V 还是5.0V?)Return Test Clock (RTCK)----可选项2可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK 信号的产生,不使用时直接接地。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Jtag的各种引脚定义

使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。

所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。

以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。

Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。

由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。

正版的Jlink是卖的很贵的。

大概是1000到2000RMB吧。

不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。

所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。

除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。

还有人制作了开源版本的JTAG仿真器——OpenJTAG。

而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。

比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。

还有飞思卡尔公司的USBDM和OSJTAG。

他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。

这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。

今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

上面的图中已经有了20Pin和10Pin对应的关系了,实际上JTAG的下载和调试至少需要四根线就行了—— TDI、TCK、TDO、TMS。

从20Pin的引脚图中我们也发现右边有九个脚全是GND,这些脚完全可以舍去,所以就有了右边的10Pin的JTAG引脚图。

不过10Pin的引脚图里面引脚也比较多,所以又有人根据JTAG的协议改进产生了新的引脚定义——SWD协议。

SWD协议比JTAG使用的脚更少,至少三根线就可以了——SWCLK、SWDIO、GND。

而且现在的Jlink基本上都支持JTAG和SWD两种协议,你只要使用转接板,或者是直接使用杜邦线连接即可。

最近,我接触到了Freescale的K60芯片,FSL官方有提供了一款开源的JTAG调试工具——OSJTAG。

不知FSL是否是故意与别人不同,它的JTAG引脚与Jlink的引脚又有所不同,如下图所示:

好吧,我做过试验,直接用杜邦线将OSJTAG的引脚与Jlink定义的下载接口相连接,也是可以下载进去程序的,那么干嘛定义那么多的不同的引脚定义呢?统一一点不好么?。