第13章 阵列处理机

自考《计算机系统结构》问答题总结(6)

第六章 1、试分析阵列处理机特点 (1)阵列处理机提⾼速度是利⽤资源重复,利⽤并⾏性中的同时性; (2)处理单元同等地担负起各种运算,其设备利⽤率可能不那么⾼; (3)速度提⾼在硬件价格⼤幅度下降情况下,潜⼒巨⼤; (4)互连络对系统性能影响显著; (5)互连络使阵列处理机⽐固定结构的单功能流⽔线灵活; (6)阵列处理机结构和所采⽤并⾏算法紧密联系; (7)阵列处理机还必须提⾼标量处理速度。

总之,阵列处理机实质上是专门对付数组运算的处理单元阵列组成的处理机、专门从事处理单元阵列控制及标量处理的处理机和专门从事输⼊输出及操作系统管理的处理机组成的⼀个异构型多处理机系统。

2、试⽐较阵列机的两种基本形式 (1)分布式存储器阵列机。

a、各处理单元PE有局部存储器,被分布数据只能被本处理单元直接访问。

b、在控制部件CU内有主存储器。

运⾏时所有指令都在CU中,只把适合并⾏处理的“向量类”指令播给各PE,并控制各PE并⾏执⾏。

c、各PE可通过互连ICN交换数据。

d、PE通过CU连到管理处理机SC上,⽤于管理系统资源。

(2)集中式共享存储器阵列机。

a、K个存储体集中组成,经互连络为全部N个处理单元共享。

其中K等于数据处理单元数。

b、互连⽤于处理单元与存储分体之间进⾏转接构成数据通路。

3、试⽐较多级互连的⼏种络 ATRAN——拓扑结构:第I级交换单元处于交换⽅式时,实现Cubei;控制⽅式:级控制分级控制;交换单元:⼆功能交换单元。

间接⼆进制N⽅体——拓扑结构:第I级交换单元处于交换⽅式时,实现Cubei;控制⽅式:单元控制;交换单元:⼆功能交换单元。

多级混洗omega——拓扑结构:每⼀级有⼀个全混拓扑和⼀列四功能交换单元;控制⽅式:单元控制;交换单元:四功能交换单元。

多级PM2I——拓扑结构:每级按PM2I连接;控制⽅式:级控制或单元控制;交换单元:⼆功能交换单元。

全排列Benes——拓扑结构:三维⽴⽅体多级络与它的逆络连在⼀起,省去中间重复⼀级;控制⽅式:单元控制;交换单元:⼆功能交换单元。

并行处理机获奖课件

111 111

111

Cube0

Cube1

Cube2

扩展成超立方体:

有n=log2N个互连函数; Cubei=(bn-1…bi…b0); 最大连接度=log2N; 结点最大间距=log2N。 应用:几种互连函数反复调用,任意结点间可连接。

2.PM2I单级网络(循环移数网络)

出端编码与连接旳入端结点编码相差2i。

2 2[log2(N+1)-1]

3 log2N

1

动态:没有源开关,借助控制信号重新组合。

单级循环网、多种多级互连网络。

4.设计思绪

根据应用需要(互连网络属性),选择合 理旳特征方式,考虑互连网络旳性能原因, 综合加以合理组合。

目的:低成本、高灵活性、高连接度、低延时、适 合VLSI。

5.互连网络表达

以STARAN网络为例简介。

互换开关:二功能(直通和互换)

拓扑构造:第i级为Cubei; 为何只有三级?

(1)互换功能

入端

控制:级控制(开关为1时互换功能,不然为直通)

0 1 2 3 4 5 6 7

功 能

级控制信号(k2k1k0)

000 001 010 011 100 101 110 111

0

1

2

应用: 屡次调用混洗互换互连函数,可实现任意结点间

旳连接。

4.总结 (1)单级互连网络特征

任一单级互连网络均可表达成N入

N出旳过程。

任一单级互连网络可实现部分结点(一对或几对) 间旳连接,不能实现任意多对结点间旳同步连接。

单级互连网络含义:某些连接措施或拓扑构造。 (2)单级互连网络应用

利用单级互连网络旳特征作为实际IN旳拓扑构造; 经过互换开关作为IN旳可变原因; 经过互换开关屡次控制实现IN旳结点间任意互连。

02325计算机系统结构真题及答案202110

2021年10月高等教育自学考试全国统一命题考试计算机系统结构注意事项:1.本试卷分为两部分,第一部分为选择题,第二部分为非选择題。

2.应考者必须按试题順序在答题卡(纸)指定位置上作答,答在试卷上无效。

3.涂写部分、画图部分必须使用2B钳笔,书写部分必须使用黑色字迹签字笔。

第一部分选择题―、单项选择题:本大題共10小题,每小题1分,共10分。

在毎小题列出的备选项中只有一项是最符合题目要求的,请将其选出。

1.汇编语言源程序变换成机器语言目标程序是经()A.汇编程序翻译B.编译程序翻译C.汇编程序解释D.编译程序解释参考答案:A2.在计算机系统设计中,设计方法最好的是()A.由上往下设计B.由下往上设计C.从两边向中间设计D.从中间开始向两边设计参考答案:D3.浮点数尾数基值rm =8,尾数数值部分於6位,可表示的规格化最小正数尾数为()A.0.015625B.0.125C.0.25D.0.5参考答案:B4.总线控制釆用集中式定时査询需另外增加控制线根数为()A.3B.N+2C.2+[log2N]D.2N+1参考答案:C5.不属于堆栈型替换算法的是()A.先进先出法B.近期最少使用法C.近期最久未用法D.页面失效频率法参考答案:A6.流水机器IBM 360/91对指令中断的处理方法是()A.指令复执法B.猜测法C.不精确断点法D.对流水线重调度法参考答案:C7.标量处理机的重登方式中二次相关是()A.指令k与指令k+1存在先读后写相关B.指令k与指令k+2存在先写后读相关C.指令k与指令k+1存在先写后读相关D.指令k+1与指令k+2存在写写相关参考答案:B8.ILLLAC IV阵列处理机中,PE之间所用的互连函数是()A.Cube0和 Cube1B.PM2±2C.ShuffleD.PM2±0 和 PM±3参考答案:D9.混洗交换单级网络,最远的两个单元建立连接需要()A.n-1次混洗和n-1次交换B.n-1次混洗和n次交换C.n次混洗和n-1次交换D.n次混洗和n次交换参考答案:B10.有关多处理机任务粒度说法正确的是()A.任务粒度小,辅助开销大B.任务粒度大,并行度高C.任务粒度小,并行度低D.任务粗度小,效率高参考答案:A第二部分非选择题二、填空题:本大题共10小题,毎小题2分,共20分。

22春“计算机科学与技术”专业《计算机系统结构》离线作业-满分答案7

22春“计算机科学与技术”专业《计算机系统结构》离线作业-满分答案1. 在需求驱动模型中,计算的进行时由对该计算结果的需求而被驱动的。

( )A.正确B.错误参考答案:A2. 浮点数尾数下溢处理采用舍入法还是恒置“1”法,对计算机系统结构是不透明的。

( )A.正确B.错误参考答案:B3. 下列关于阵列处理机与流水线处理机特点的描述,不正确的是( )。

A.阵列处理机提高速度主要靠缩短时钟周期,流水线处理机主要靠增大处理单元数B.阵列处理机利用并行性中的同时性,而流水线处理机利用的是时间重叠C.阵列处理机使用互连网络来确定处理单元间的连接,而流水线处理机则不是D.与流水线处理机不同,阵列处理机的结构是和所采用的并行算法紧密联系的参考答案:A4. Cache存储器应用最广泛的地址映像方式是( )。

A.组相联映像B.直接映像C.段页表映像D.全相联映像参考答案:A5. 计算机系统接地包括直流地;交流工作地;安全保护地;电源零线和防雷保护地。

( )A.错误B.正确参考答案:A6. RISC采用重叠寄存器窗口技术,可以减少( )A.绝大多数指令的执行时间B.目标程序的指令条数C.程序调用引起的访存次数D.CPU访存的访问周期参考答案:C7. “启动I/O”指令是主要的输入输出指令,是属于( )。

A.编译程序只能用的指令B.管态指令C.目态、管态都能用的指令D.目态指令参考答案:B8. 利用时间重叠概念实现并行处理的是( )。

A.相联处理机B.流水处理机C.并行(阵列)处理机D.多处理机参考答案:B9. 磁盘外部设备适合连接于( )A.数组多路通道或选择通道B.字节多路通道或选择通道C.数组多路通道或字节多路通道D.字节多路、数组多路通道或选择通道参考答案:A10. 对机器语言程序员透明的是( )。

A.通用寄存器B.条件码C.主存地址寄存器D.中断字参考答案:C11. EMC测试和约束用户关心的信息信号的电磁发射。

雷达组成及原理

雷达的组成及其原理课程名称:现代阵列并行信号处理技术姓名:杜凯洋教师:王文钦教授示器、(1(2(3(4(5雷达等。

(一)概述1、天线:辐射能量和接收回波(单基地脉冲雷达),(天线形状,波束形状,扫描方式)。

2、收发开关:收发隔离。

3、发射机:直接振荡式(如磁控管振荡器),功率放大式(如主振放大式),(稳定,产生复杂波形,可相参处理)。

4、接收机:超外差,高频放大,混频,中频放大,检波,视频放大等。

(接收机部分也进行一些信号处理,如匹配滤波等),接收机中的检波器通常是包络检波,对于多普勒处理则采用相位检波器。

5、信号处理:消除不需要的信号及干扰而通过或加强由目标产生的回波信号,通常在检测判决之前完成(MTI,多普勒滤波器组,脉冲压缩),许多现代雷达也在检测判决之后完成。

6、显示器(终端):原始视频,或经过处理的信息。

7、同步设备(视频综合器):是雷达机的频率和时间标准(只有功率放大式(主振放大式)才有)。

(二)雷达发射机1、单级振荡式:大功率电磁振荡产生与调制同时完成(一个器件)(1(2)(32(1(2(3(4(三)雷达接收机一、超外差雷达接收机的组成优点:灵敏度高、增益高、选择性好、适应性广。

图3-1 超外差式雷达接收机简化框图1、高频部分:(1)T/R 及保护器:发射机工作时,使接收机输入端短路,并对大信号限幅保护。

(2)低噪声高放:提高灵敏度,降低接收机噪声系数,热噪声增益。

(3)Mixer ,LD ,AFC :保证本振频率与发射频率差频为中频,实现变频。

2、中频部分及 AGC :(1)匹配滤波:max (/)o S N(2)AGC :auto gain control.3(1(21、灵敏度d P 时的输完成。

23。

4、中频的选择与滤波特性:02R f f ≥∆ ,中频选择通常选择 30M ~500M ,抑制镜频.实际与发射波形特性,接收机工作带宽有关。

5、工作稳定性和频率稳定度:指当环境变化时,接收机性能参数受到影响的程度,频率稳定度,信号处理,采取频率稳定度、相位稳定度提高的本振,“稳定本振” 。

计算机系统的基础知识

计算机系统的基础知识有关计算机系统的基础知识本章主要内容计算机系统结构基础计算机操作系统基础1.计算机系统结构的基础计算机系统结构的基础概念主要研究软件、硬件功能分配,确定软件、硬件界面,即从机器语言程序员或编译程序设计者的角度所看到的物理系统的抽象。

计算机系统的分类Fly分类SISDSIMDMISDMIMD2.CPU结构及分类CPU的结构运算器控制器寄存器输入输出总线分类16位32位64位3.指令系统及其分类指令系统的基础概念指令系统是计算机所有指令的集合。

程序员用各种语言编写的程序都有翻译成以指令形式表示的机器语言后才能运行,所以指令系统反映了计算机的基本功能,是硬件设计人员和程序员都能看到的机器的主要属性。

分类复杂指令系统(CISC):随着硬件成本的不断下降,软件成本的不断提高,使得人们热衷于在指令系统中增加更多的指令和复杂的指令,来提高操作系统的效率,并尽量缩短指令系统与高级语言的语义差别,以便高级语言的编译和降低软件成本,同时为了保证程序兼容,新的计算机的指令系统只能增加而不能减少,所以就使得指令系统越来越来复杂精简指令系统(RISC):通过简化指令使计算机的结构更加简单合理,从而提高运算速度!RISC的特点及其优缺点4.存储系统的基础知识基本概念存储器主要用于存放计算机的程序和数据,存储器系统指的是存储器硬件设备以及管理该存储器的'软、硬件设备。

对存储器的基本要求是增大容量、提高速度、降低价格。

单一的存储器硬件(主存储器)难以满足要求。

所以就提出了多层次的存储体系结构(即:寄存器---Cache--主存—外存)在计算机中存放当前正在执行的程序以及被程序所使用的数据(包括运算结果)原存储器称为主存储器。

也就是我们所说的内存5.主存储器的种类按读写功能来分:是否需要定期刷新:静态:不停电情况下能长时间保留不变,速度快,但容量小,成本高动态:不停电的情况下也要定期刷新,容量大,成本低,常用在计算机系统中,常见的有:SDRAM、DDR等可读写(RAM)可擦写只读:EPRM(可擦写,用紫外线擦写)EERM(可用电擦写)FLASH(电读写,但只能以块为单位,速度快,成本低,现在最常用)可编程:ERM(通过编程一次性写入)只读:RM(制造时一次性写入)6.存储器容量的扩展位扩展:位扩展是对存储器的位数进行扩充字扩展:是对存储器的容量进行扩展位、字扩展:对位数和容量都进行扩展7.多体交叉存储为了协调存储器与CPU速度的,其工作原理是:将存储器分成几个独立的个体,这样第一次就能进行多个字的数据读写!影响多体交叉效率的因素:多体存储的模值M数据的分布情况较移指令8.Cache的基础知识基本概念在多级存储体系中,Cache处于CPU与存储器之间,其目的是使程序员能使作一个速度与CACHE相当而容量与主存相当的存储器。

阵列处理机

阵列处理机的特点

背景----科学计算

有限差分、矩阵、信号处理、线性规划 数组、向量处理

资源重复,利用并行性中的同时性 简单而规整的互联网络---设计重点 专用机 与并行算法紧密相联

阵列处理机

阵列处理机实质上是由

专门对付数组运算的处理单元阵列组成的处 理机 专门从事处理单元阵列的控制及标量处理的 处理机 专门从事系统输入输出及操作系统管理的处 理机

65536 个 PE 排 成 10 维超立方体, 每个 Thinking PE 可 有 1M 位 存 储 Machines公 器 , 32 个 PE 共 享 司CM-2 FPU 选 件 , 峰 值 速 度28 Gflops和持续 速度5.6 Gflops 1K位/PE方形网格 Active 互连成4096PE的细 Memory 粒 、 位 片 SIMD 阵 Technology 列,正交4-邻位链 DAP600 接 , 20GIPS 和 系列 560Mflops 峰 值 性 能

阵列处理机的构形与特点

分布式存储器的阵列处理机构形 集中式共享存储器的阵列处理机构形 一台阵列处理机由五个部分组成

多个处理单元PE 多个存储器模块M 一个控制器CU 一个互连网络ICN 一台输入输出处理机IOP

分布式存储器的阵列处理机

各处理单元设有局部存储器PEM(Processing Element Memory),存放被分布的数据;只能 被本处理单元直接访问 控制部件CU设有存放程序和数据的主存储器 整个系统在CU控制下运行用户程序和部分系统 程序 处理单元之间可通过互联网络ICN (Interconnection Network) 目前的大部分阵列处理机是基于分布式存储器 模型的系统

CU …… ……

IOP

脉动阵列处理机

Two Communication Styles

Systolic communication

CPU

CPU

CPU

Local Memory

Local Memory

Local Memory

Memory communication

CPU

CPU

CPU

Local Memory

Local Memory

Local Memory

Different from pipelining

Nonlinear array structure, multidirection data flow, each PE may have (small) local instruction and data memory

Different from SIMD

Each PE may do something different

Initial motivation

VLSI enables inexpensive special-purpose chips Represent algorithms directly by chips connected in regular

Systolic Method

This will run in O(n) time! To run in N time we need N x N processing units, in this case we need 9.

P1 P2 P3

P4 P5 P6

P7 P8 P9

We need to modify the input data, like so:

342

342

23 36 28

处理机

功能分类

处理机又可根据在计算机系统中的功能来分类。一般情况下,处理机的指令系统可以反映出处理机功能的强 弱和它的适用范围。通用中央处理器具有很强的指令功能,适用于科学计算、数据处理、商业应用、事务管理各 个领域或某一个和某几个领域。某些处理机的指令系统只有局部的功能,往往以其用途来命名。①输入-输出处理 机:解释和执行输入-输出指令,具有一定的字符处理能力,它完成输入-输出操作和设备控制操作。②通信控制处 理机:在计算机网中实现各个处理机之间的通信并协调它们的操作。③支持和维护处理机:具有系统控制台功能, 能实现系统维护和故障诊断。④数组处理机:结构上适合于数组和矩阵运算尤其是信号处理算法运算,与前置处 理机或主机配接后可大大增强系统的向量处理能力。此外还有:具有数据库管理功能的数据库处理机;实现虚拟 存储器页面调度的处理机等。

操作

处理机的操作是首先将用户程序和数据通过输入-输出设备输入到主存储器(主存)或辅助存储器。中央处 理器从主存取出指令,完成对指令的解释,执行控制操作;若是运算型指令,还须从主存取出数据,由运算器完 成运算。结果通常暂存在运算器或送回主存。

执行程序

处理机执行程序过程涉及输入-输出操作、主存-辅存的信息交换,这些都要经过输入、输出接口部件。处理 机与外界的这种信息交换有三种方式。①中断方式:即程序I/O。每传送一个位组(如一个字或字节)产生一次 中断,由CPU执行相应的中断程序完成。这种方式主要用于慢速输入-输出设备。②直接存储器存取(DMA)方式:在 硬件线路控制下直接在快速输入-输出设备和主存之间完成一条输入-输出指令规定的信息量交换。③通道控制方 式:各通道各有自己的通道程序,实现输入-输出指令规定的主存和输入-输出设备之间的信息交换。

分类

从系统结构角度,按处理机执行的指令流和与指令流相关的数据流的关系,有单指令流单数据流(SISD)处 理机、单指令流多数据流(SIMD)处理机和多指令流多数据流(MIMD)处理机。SISD处理机的程序是按单一指令 序列执行的,操作数据亦按对应的指令确定的单一顺序逐个处理。大多数处理机都属于这一类。SIMD和MIMD处理 机又称并行处理机。并行处理机的目的在于提高处理机的数据处理能力。SIMD处理机以处理向量数据为主,故又 称向量处理机。其中以单个指令执行部件和多个相同的运算处理器构成的处理机称为阵列(式)处理机,如美国的 伊利阿克ILLIAC-Ⅳ。以生产流水线方式组织指令部件(称先行控制)和运算功能部件的SIMD处理机,称为流水线 处理机,如中国1983年研制成功的“银河”计算机的处理机。联想处理机则是采用按内容检索的联想存储器为主 要特征的SIMD处理机。至于MIMD处理机,实际上是多处理机系统,它是多个相同的处理机通过公共主存储器相互 耦合构成有多重处理能力的系统。

全国自考(计算机系统结构)模拟试卷9(题后含答案及解析)

全国自考(计算机系统结构)模拟试卷9(题后含答案及解析)题型有:1. 单项选择题 2. 填空题 3. 简答题 4. 简单应用题 5. 综合应用题单项选择题1.虚拟存储器是因何而提出来的( )A.主存速度满足不了要求B.外存速度满足不了要求C.主存容量满足不了要求D.外存容量满足不了要求正确答案:C解析:虚拟存储器是因主存容量满足不了要求而提出来的。

在主存和辅存之间,增设辅助的软、硬件设备,让它们构成一个整体,所以也称为主存一辅存存储层次。

2.根据存储映像算法的不同,可有多种不同的存储管理方式的虚拟存储器,其中不属于其主要管理方式的是( )A.段式B.页式C.段页式D.页段式正确答案:D解析:根据存储映像算法的不同,可有多种不同存储管理方式的虚拟存储器,其中主要管理方式是段式、页式、段页式。

3.下列哪个算法是选择最早装入内存的页作为被替换的页( )A.FIFOB.LRUC.OPTD.FILO正确答案:A解析:FIFO指的是先进先出算法,是选择最早装入内存的页作为被替换的页。

4.Cache存储器的性能主要取决于命中率的高低,下列与命中率无关的是( )A.主存容量B.替换算法C.块的大小D.采用组相联时组的大小正确答案:A解析:评价Cache存储器的性能主要是看命中率的高低,而命中率与块的大小、块的总数(即Cache的总容量)、采用组相联时组的大小(组内块数)、替换算法和地址流的簇聚性等有关。

5.虚拟存储器中段式管理虚地址不包含的部分是( )A.基号B.段号C.页号D.段内位移正确答案:C解析:虚拟存储器中段式管理虚地址包含的部分是基号、段号、段内位移。

6.下列不属于堆栈型替换算法的是( )A.近期最少使用算法B.先进先出替换算法C.优化替换算法D.近期最久未使用算法正确答案:B解析:先进先出替换算法不属于堆栈型替换算法,而近期最少使用算法和优化替换法是堆栈型替换算法。

7.最易出现块冲突的Cache地址映像方式是( )A.段相联B.直接相联C.全相联D.组相联正确答案:B解析:直接相联是把主存空间按Cache大小等分成区,每区内的各块只能按位置一一对应到Cache的相应块位置上。

并行处理技术

并行处理技术摘要:并行处理计算机是计算机设计的未来。

当代面临着的重大科学技术问题要依赖于计算技术协助解决,一方面要作大型计算以得到更精确的解,另一方面要作计算机模拟,以便进一步了解所探讨问题的结构与运动规律。

这两个方面都离不开并行处理技术。

虽然许多人都认识到并行处理技术的重要性,但并行处理技术的发展道路并不平坦。

从70年代到90年代中期,中间几起几落,究其原因,就是并行计算技术仍然遇到若干困难,使其无法推广应用。

这其中既有软件方面的(并行程序设计)问题,也有硬件方面(并行处理机)的原因。

本文主要从并行程序设计和并行处理机两方面对并行处理技术进行了简要的介绍。

关键词:并行处理技术、并行处理机、并行程序引言人类对计算能力的需求是永无止境的,而在各种类型的计算系统中,超级计算机的性能最高。

90年代以来,超级计算机在工业、商业和设计等民用领域的重要性越来越明显了。

因此,超级计算机的发展,不仅会深刻地改变产品和材料的设计方法,改变研究和实验的方式,而且将逐步影响人们的生活方式。

超级计算机已经成为体现一个国家经济和国防力量的重要标志。

20多年来,超级计算机的工作频率只提高了将近10倍,而峰值速度却提高了1万倍。

这说明,主要的性能改善来自结构的进步,尤其是来自各种形式的并行处理技术。

但是,超级计算机的用户们关心的并不是系统在理论上的最高速度,而是实际解题所需要的时间和程序设计及移植的工作量。

并行处理是提高计算机系统性能的重要途径。

目前几乎所有的高性能计算机系统,都或多或少地采用了并行处理技术。

本文将就并行处理技术做简要的介绍。

何为并行并行性主要是指同时性或并发性,并行处理是指对一种相对于串行处理的处理方式,它着重开发计算过程中存在的并发事件。

并行性通常划分为作业级、任务级、例行程序或子程序级、循环和迭代级以及语句和指令级。

作业级的层次高,并行处理粒度粗。

粗粒度开并行性开发主要采用MIMD方式,而细粒度并行性开发则主要采用SIMD方式。

数据库课程

王珊,萨师煊.数据库系统概论(第四版).高等教育出版社 王珊,萨师煊.数据库系统概论(第四版).高等教育出版社 ).

主 讲:任荣

计算机科学与工程学院 2009-2010春季学期 2009-2010春季学期

课 程 简 介

数据库管理系统( DBMS) 数据库管理系统 ( DBMS ) 是现代计算机环境中 的核心基础软件, 的核心基础软件 , 信息系统以及许多新的应用 领域采用数据库技术存储和处理信息( 数据) 领域采用数据库技术存储和处理信息 ( 数据 ) 资源。 资源。 当 前 广 泛 使 用 的 小 型 数 据 库 系 统 Acess 、 FoxPro,大型数据库系统Oracle Oracle、 DB2 Visual FoxPro, 大型数据库系统 Oracle 、 DB2 、 Server、 Informix、 Sybase等关系数据库 SQL Server 、 Informix 、 Sybase 等关系数据库 管理系统。 管理系统。 本课程主要讲述数据库系统的基本概念及原理, 本课程主要讲述数据库系统的基本概念及原理 , 包括数据库系统结构、 数据库语言、 包括数据库系统结构 、 数据库语言 、 数据库安 全保护、数据库设计、数据库编程等。 全保护、数据库设计、数据库编程等。

4本课程的知识体系结构基础知识基础知识设计应用设计应用系统原理系统原理第一章绪论第二章关系数据库第三章关系数据库语言sql第四章数据库安全性第五章数据库完整性第一章绪论第二章关系数据库第三章关系数据库语言sql第四章数据库安全性第五章数据库完整性第六章关系数据理论第七章数据库设计第八章数据库编程第十三章数据库的新发展及新技术第六章关系数据理论第七章数据库设计第八章数据库编程第十三章数据库的新发展及新技术第九章关系查询处理和查询优化第十章数据库恢复技术第十一章并发控制第十二章数据库管理系统运行机制第九章关系查询处理和查询优化第十章数据库恢复技术第十一章并发控制第十二章数据库管理系统运行机制实验内容?建立数据库er模型?sql语言的数据定义Байду номын сангаасsql语言的数据查询?sql语言的数据更新和视图?数据的安全性控制?数据库完整性控制?数据库编程?本课程是考试课考试方式为笔试期末笔试成绩占70平时成绩包括作业实验报告成绩和考勤成绩占30

并行处理技术

SIMD

(2)SIMD计算机的操作模型

SIMD是细粒度并行,在一个指令周期内,每一个PE可处于活动或不活动状态 ,用一个屏蔽向量来控制所有PE的状态。 SIMD计算机的操作系统可用五元组表示:

M=<N,C,I,M,R>

• • • • • N-机器的处理单元(PE)数。 C-为由控制部件(CU)直接执行的指令集,包括标量和程序流控制指令。 I-为由CU广播至所有PE进行并行执行的指令集。 M-屏蔽方案集,其中每种屏蔽将PE集划分为允许操作和禁止操作两种子集。 R-数据寻径功能集,说明互联网络中PE间通信所需要的各种设置模式。

Pn-1 Mn-1

控 制

IN 分布存储阵列机

Mm-1

I/O接口 接口

共享存储阵列机

SIMD

分布存储阵列机中,只要数据分配得当,各PEi将从各自的本地存 储器Mi中获得所需要的数据;CU中除了存放系统程序和用户程序 外,也可存放各个PEi所需共享的数据。 共享存储阵列机中,存储模块以集中形式为所有的PE共享,当两 个需要交换数据的PE之间无共享存储单元时,就需要经过多次传 输,方可实现交换。 不管哪种结构,对于标量型指令,CU中的运算部件可直接执行; 对于向量型指令,它就将此指令播送给各个PE同步执行。 SC是通用机,管理系统资源,系统维护,输入/出,用户程序汇 编,作业调度,存储分配;设备、文件管理。

结束语

面向图像处理的SIMD计算机是一台专用的SIMD型计算 机,主要用于图像处理等细粒度的并行计算。 文中介绍的存储系统是整个系统中的一个关键部分,可 以有效解决阵列存储器、SRF、LRF之间的存储带宽平衡 的问题,使面向图像处理的SIMD计算机系统的性能得到 有效提高。

谢

谢观看!

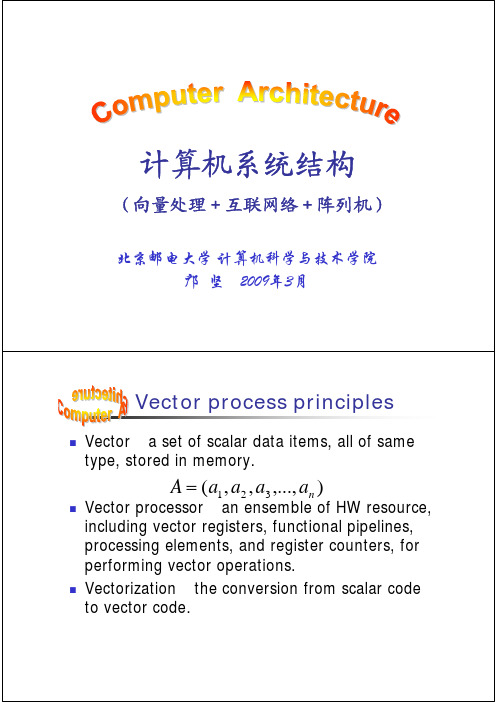

计算机系统结构03(向量处理_互联网络_阵列机)(北邮课件)

Vector process principlesVectorization VectorizationVector instruction types1V V ×Vector instruction types01V1Vector processor architecture采用多个存储体交叉和并行访问来提高存储器速度操作数缓冲栈和写结果缓冲栈主要用于解决访问存储器个存储体,每个处理机访问4个存储体。

个存储体交叉访问,每个存储体,每个周期并Memory-to-memoryMemory-to-memoryRegister-to-Register Register-to-RegisterVector/Scalar Ratio Balanced Vector/Scalar RatioBalanced Vector/Scalar Ratio Multiple function unit (Cray-1)功能部件并行条件:•无功能部件冲突•无向量寄存器冲突Vector parallelStrip-mining (Vector loop)Pipeline chainingPipeline chainingPipeline chaining Cray-1 只有一个访存部件;Cray X-MP有三个访存部件,两个用于向量load,一个用于向量store,并且三个部件可同时使用。

Y=s*X+YVector Processor Terminologynetworksnetworks互连网络的性能参数总时延=发送方开销+飞行时间+消息长度/带宽+接收方开销x(蝶式函数(Butterfly)x(PM2Network structure Static NetworksStatic NetworksStatic Networks维立方体由N=2n个结点构成,分布在n维上,每维有两个结点;超立方体网采用交换函数,结点度为Static NetworksDynamic networks总线系统Dynamic networks多级互连网络MIN (multistage interconnection network)多级互连网络采用的关键技术:交换开关;交换开关之间的拓扑连接;对交换开关的不同控制方式。

自考计算机系统结构复习资料大全

1计算机系统的多级层次结构, , 1:M0微程序(微指令)机器、2:M1传统(机器指令)机器、3:M2操作系统(作业控制)机器、4:M3汇编语言机器、5:M4高级语言机器、6:M5应用语言机器;1-2为实际机器,3-6为虚拟机器2, 各个机器级的实现的依靠, , 翻译和解释3, 翻译, translation, 是先用转换程序将高一级机器级上实现的程序整个地变换成低一级机器级上等效的程序,然后再在低一级机器上实现的技术。

4, 解释, interpretation, 在低级机器级上用它的一串语句或指令来仿真高级机器级上的一条语句或指令的功能,通过高级机器语言程序中的每条语句或指令逐条解释来实现的技术。

5, M0-M5各级的实现方式, , M0用硬件实现,M1用微程序(固件实现),M2到M5大多采用软件实现。

6, 虚拟机器的定义, , 以软件为主实现的机器7, 实际机器的定义, , 以硬件或固件实现的实际机器8 透明的定义, , 客观存在的事物或属性从某个角度看不到,称之为透明9 计算机系统结构的定义,, 是系统结构的一部分,指的是传统机器级的系统结构,其界面之上包括操作系统、汇编语言、高级语言和应用语言级中所有的软件功能,界面之下包括所有硬件和固件的功能。

它是软件和硬件/固件的交界面,是机器语言、汇编语言、程序设计者,或者编译程序设计者看到的机器物理系统的抽象。

是研究软、硬件之间的功能分配以及对传统机器级界面的确定,提供机器语言、汇编语言设计者或编译程序生成系统为使其设计或生成的程序能在机器上正确运行应看到或遵循的计算机属性。

10计算机系统结构的属性(需了解一部分), , 1、数据表示;2、寻址方式;3、寄存器组织;4、指令系统;5、存储系统组织;6、中断机构;7、系统机器级的管态和用户态的定义与切换;8、I/O结构;9、信息保护方式和保护机构等等。

11计算机系统结构不包含的内容,, 不包含“机器级内部”的数据流和控制流的组成,逻辑设计和器件设计等。

计算机体系结构L6_CA并行处理机与互联网络

计算机体系结构

北理工计算机学院

19

3. 阵列处理机特点

(6)从处理单元来看,由于结构都相同, 因而可将阵列机看成是一个同构型并行 机。但其控制器实质上是一个标量处理 机,而为了完成I/O操作及操作系统管 理,尚需一个前端机,因此,实际的阵 列机系统是由上述三部分构成的一个异 构型多处理机系统。

计算机体系结构

北理工计算机学院

6

6.1.1 并行处理机定义及特点

从CU看,指令是串行执行的。 从PE看,数据是并行处理的。

PE

不带指令控制部件的算术运算部件 使用按地址访问的随机存贮器 按照佛林分类法,它属于SIMD计算机。

计算机体系结构

北理工计算机学院

7

6.1.1 并行处理机定义及特点

特点:

北理工计算机学院

24

1. ILLIAC IV系统组成

计算机体系结构

北理工计算机学院

25

ILLIAC IV阵列

由 88=64 个PU组成。每个PU由处理部件 PE和它的局部存储器PEM组成。

每一个PUi 只和它的东、西、南、北四个近邻 直接连接。{PUi+1 mod 64、PUi-1 mod 64 、PUi+8 mod 64、PU i-8mod 64}

60年代研制、1972年生产的ILLIAC Ⅳ 1979年研制成功的巨型并行处理机MPP 1980年生产的分布式阵列处理机DAP等

计算机体系结构

北理工计算机学院

14

2. 集中式共享存贮器的阵列处理机

控制

控制

CU

SC

PE0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例如:Illiac Ⅳ计算机有64个PE MP-1计算机有16384个PE

➢ C:控制部件CU直接执行的指令集,包括标量指 令和程序流控制指令。

➢ I:由CU广播至所有PE进行并行执行的指令集。

包括算术运算、逻辑运算、数据寻径、屏蔽以及其 他由每个PE对它的数据所执行的局部操作。

述字送至CDC、处理中断、提供操作系统所具备的 其他服务等。

13.3.2 实例2:BSP计算机

➢ 美国宝来公司和伊利诺依大学 1979年 ➢ 共享存储器结构的SIMD计算机的典型代表 ➢ 最高处理性能:每秒5千万次浮点运算 ➢ 依靠并行性来提高性能

▲

26/50

程序和数据 250K 字/s

文件存储器系统

5. PE的同步是在控制部件的控制下由硬件实现。 ➢ 可以让所有PE在同一个周期执行同一条指令

▲

12/50

13.2 阵列处理机的基本结构

➢ 也可以通过采用屏蔽逻辑来控制某些PE在指定的 指令周期是否参与执行

6. 各种阵列处理机的主要差别 在于数据寻径网络的不同。

➢ Illiac Ⅳ: 4-邻连接网络结构

➢ 阵列机的控制器实质上是一台标量处理机,而为 了完成I/O操作以及操作系统的管理,尚需一个前 端机。 实际的阵列机系统是由3部分构成的一个异构型

多处理机系统。

▲

9/50

13.2 阵列处理机的基本结构

13.2.1 分布式存储器的阵列机

1. 分布式存储器的阵列机结构 ➢ 含有多个相同的处理单元PE,每个PE有各自的本 地存储器LM。 ➢ PE之间通过数据寻径网络以一定方式互相连接。 它们在阵列控制部件的统一指挥下,实现并行操 作。 ➢ 指令的执行顺序基本上是串行进行的。 ➢ 程序和数据是通过主机装入控制存储器。

2. 阵列处理机的特点 ➢ 以单指令流多数据流方式工作。 ➢ 通过设置多个相同的处理单元来开发并行性。

利用并行性中的同时性,而不是并发性。所有处理 单元必须同时进行相同的操作。

➢ 以某一类算法为背景的专用计算机。

▲

8/50

13.1 阵列处理机的操作模型和特点

➢ 阵列机的研究必须与并行算法的研究密切结合, 以便能充分发挥它的处理能力。

➢ 运算部件

加/乘算术单元 逻辑单元 移位单元 地址加法器等

➢ 操作数来源

PE本身的寄存器 PEM CU的公共数据总线 PE的4个近邻

▲

21/50

13.3 阵列处理机实例

➢ 并行的加法速度

每秒1010次8位定点加法或150×106次64位浮点加法

➢ 每一个处理单元有一个自己的本地存储器PEM ➢ PE和PEM之间经过存储器逻辑部件MLU相连 2. 阵列控制器CU ➢ 一台小型计算机

对阵列的处理单元进行控制 利用本身的内部资源执行一整套指令,用以完成标

量操作。

➢ 功能

▲

22/50

13.3 阵列处理机实例

对指令流进行控制和译码,包括执行一整套标量指令; 向各处理单元发出执行数组操作指令所需的控制信号; 产生并向所有处理单元广播公共的地址部分; 产生并向所有处理单元广播公共的数据; 接收和处理由各PE计算出错、系统I/O操作以及B6700

16 个算术单元

BSP计算机系统的框图

13.3 阵列处理机实例

➢ BSP处理机由3部分构成:控制处理机,并行处理 机,文件存储器。

1. BSP处理机

➢ 并行处理机

包含16个算术单元AE、由17个存储体组成的一个无 冲突访问的并行存储器和两套对准网络(分别为入 口和出口对准网络)

一条5级的数据流水线 从17个存储器输出端口并行读出16个操作数; 经对准网络NW1将16个操作数重新排列,形成 16个算术单元所需要的顺序;

存储模块的数目等于或略大于处理单元的数目。

➢ 必须减少存储器访问冲突

(将数据合理地分配到各存储器模块中 )

➢ 在处理单元数目不太多的情况下是很理想的 ➢ 所有阵列指令都必须使用长度为n的向量操作数

(n为PE的个数)

▲

14/50

13.2 阵列处理机的基本结构

大容量 存储器

主机 I/O(用户)

网络控制

…

… …

i-1

i

i+1

PU55

PU56

PU57

……

PU63

PU0

i+8

PU0

PU1

PU7

(a)

(b)

例如:从PU10到PU46 的距离以下列路径为最短

PU10 →PU9 →PU8 →PU0 →PU63 →PU62 →PU54 →PU46

13.3 阵列处理机实例

一般情况,n×n个单元组成的阵列中,任意两个处 理单元之间的最短距离不会超过(n-1)步。

▲

4/50

13.1 阵列处理机的操作模型和特点

PE1

处理 单元 1

控制部件(CU)

PE2

处理 单元 2

PE3

处理

单元 3

…

PEn

处理 单元 n

互连网络

阵列处理机的操作模型

▲

5/50

13.1 阵列处理机的操作模型和特点

2. 阵列处理机的操作模型可用五元组表示 阵列处理机=(N,C,I,M,R)

其中:

数据进行相同的运算和操作。

又称为SIMD计算机。

➢ 有时还被称为并行处理机。

▲

3/50

13.1 阵列处理机的操作模型和特点

1. 阵列处理机的操作模型 ➢ 用一个控制部件CU同时管理多个处理单元PE。 ➢ CU对指令进行译码,并把指令播送到各处理单 元。 ➢ 所有处理单元均被动地接收并执行从控制部件广 播来的同一条指令,但它们所操作的对象却是不 同的数据。

据宽度为256位,最大传输率为502×106b/s;平均等 待时间为19.6ms; 如果两个通道同时发送或接收数据,则数据宽度为 5113.3 阵列处理机实例

➢ I/O系统 包括3部分:

输入/输出开关IOS 作为一个开关,把DFS或可能连上的实时装置转 接到阵列存储器,进行大批数据的I/O传送; 作为DFS和PEM之间的缓冲,以平衡两边不同的 数据宽度。

标准浮点运算。PE从CU接收指令。

▲

7/50

13.1 阵列处理机的操作模型和特点

(4)屏蔽方案设在每个PE中,并由CU连续监控,它能在运行 时动态地使每个PE处于工作或禁止状态。

(5)MP-1有一个X-Net网格网络和一个全局多级交叉开关寻径 器,以实现CU-PE之间、X-Net的8个近邻和全局寻径器的通信。

▲

11/50

13.2 阵列处理机的基本结构

2. 指令送到控制部件进行译码。 ➢ 标量指令:直接由标量处理机执行。 ➢ 向量指令:阵列控制部件通过广播总线将它广播 到所有PE中去并行地执行。

3. 执行程序所需的数据集经划分后通过数据总线分布存 放到各PE的本地存储器LM。

4. 各PE之间通过数据寻径网络互连,实现PE间的通信, 控制部件通过执行程序来控制数据寻径网络。

▲

28/50

13.3 阵列处理机实例

17 个存储体 存储器

NW1 对准网络

指令译码 控制部件

NW2 对准网络

处理器 16 个处理单元

BSP的5级数据流水线结构示意图

▲

29/50

13.3 阵列处理机实例

将排列好的16个操作数送到16个算术单元进行处理; 所得的16个结果经对准网络NW2重新排列成在17个存

48 CDC

控制线

PE0

PE0

PE1

……

PE63

B6700 计算机

48 BIOM I/O 缓冲存储器

128

DFS 磁盘文件系统

PEM0

PEM1

PEM63

256

256

CU 总线

I/O 总线 1024

Illiac Ⅳ系统总框图

IOS 1024 I/O 开关

实时 装置

▲

17/50

13.3 阵列处理机实例

控制存储器 阵列控制部件

标量指令 标量处理机

广播总线(向量指令)

PE1

PE2

……

PEn

对准网络

数据总线

SM1

SM2

……

SMm

共享存储器的阵列处理机结构

互连网络是共享存储器SM和处理单元PE之间的必由之路。

▲

15/50

13.3 阵列处理机实例

13.3.1 实例1:Illiac Ⅳ阵列处理机

➢ 美国宝来公司和伊利诺大学合作研制 1972年 ➢ 最早的阵列处理机 ➢ 一个由3种类型处理机联合组成的多机系统

▲

10/50

13.2 阵列处理机的基本结构

标量处理机

大容量存储器

标量指令

网络控制

阵列控制 部件

控制存储器 指令 (程序和数据)

向量指令

广播总线

PE1

PE2

PE3

……

LM1

LM2

LM3

主机 PEn LMn

I/O(用户)

数据总线 PE:处理单元 LM:本地存储器

数据寻径网络

分布式存储器的阵列处理机结构

➢ 每个处理单元有6个可编程序寄存器

64位字长的累加器RGA 64位字长的操作数寄存器RGB 64位字长的数据路由寄存器RGR 64位字长的通用寄存器RGS

(可被程序用来暂存中间结果) 16位的变址寄存器 8位的模式寄存器

(存放PE屏蔽信息以及状态位)

▲

20/50

13.3 阵列处理机实例

▲

6/50

13.1 阵列处理机的操作模型和特点

➢ M:屏蔽方案集

每种屏蔽将所有PE划分成允许操作和禁止操作两种 工作模式。