chapterpart集成电路物理结构

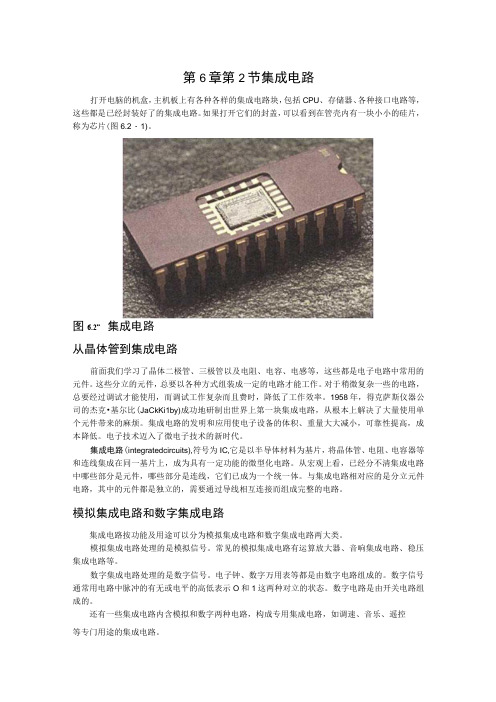

第6章第2节集成电路

一、选择题(每题2分,共20分)1. 以下哪位是中国古代著名的文学家?()A. 王之涣B. 王维C. 杜甫D. 苏轼2. 下列哪个成语出自《战国策》?()A. 破釜沉舟B. 画龙点睛C. 一鼓作气D. 胸有成竹3. 下列哪个词语是表示时间的?()A. 阳春白雪B. 风花雪月C. 桃红柳绿D. 日月如梭4. 下列哪个词语是表示颜色的?()A. 风花雪月B. 桃红柳绿C. 日月如梭D. 阳春白雪5. 下列哪个成语是形容人很有智慧的?()A. 眼光如炬B. 精卫填海C. 拔苗助长D. 班门弄斧6. 下列哪个词语是表示方向的?()A. 南腔北调B. 东施效颦C. 倒行逆施D. 南辕北辙7. 下列哪个词语是表示数量的?()A. 千里之行B. 一日千里C. 百尺竿头D. 千里马8. 下列哪个成语是形容人很有耐心的?()A. 持之以恒B. 一鼓作气C. 亡羊补牢D. 胸有成竹9. 下列哪个词语是表示心情的?()A. 风花雪月B. 桃红柳绿C. 日月如梭D. 心旷神怡10. 下列哪个成语是表示时间的流逝?()A. 日月如梭B. 千里之行C. 一日千里D. 百尺竿头二、填空题(每题2分,共20分)11. 《孟子》中提到:“______,则不远人。

”12. “______,人不知而不愠,不亦君子乎?”出自《论语》。

13. “______,沉舟侧畔千帆过。

”出自唐代刘禹锡的《陋室铭》。

14. “______,有铁一般的胳膊和腰脚,领着我们向前走。

”出自《少年中国说》。

15. “______,春暖花开。

”出自唐代白居易的《赋得古原草送别》。

三、简答题(每题5分,共20分)16. 简述《三国演义》中诸葛亮的主要事迹。

17. 简述《红楼梦》中贾宝玉和林黛玉的性格特点。

18. 简述《西游记》中孙悟空的主要特点。

19. 简述《水浒传》中宋江的主要事迹。

20. 简述《童年》中阿廖沙的性格特点。

四、作文(40分)21. 请以“我的读书生活”为题,写一篇不少于300字的作文。

半导体 第十八讲 集成电路物理器件

VDS +

漏

VGS + 源 GND

N

VDS +

漏

载止区:VGS<VT,无电流 通过

VT为引起沟通区表面反型 的最小栅电压,也称阀值 电压。

VGS + 源 GND

N

饱和区:0<(VGS-VT)<VDS, 电流与VDS 无关

VDS +

漏

线性区:(VGS-VT)>VDS>0, 电流与VDS ,VGS有关

MOS 晶体管

PN结的基本应用

❖ 整流:使一个正弦波流经二极管,则只有大于零的正向

部分会到达后面的电路,这种滤除负向信号的过程称为整 流

❖ 电流隔离:电流单向流动

结型二极管

金属与N型材料接触

金属与P型材料接触

内建电场E

E0 EFm

E0

Ec

qVD

EFn

Ev

EF

Ec qVD

Ev

内建电场E

E0 EFm

E0 Ec

qVD

另一种方法,轻掺杂漏极(lightly doped drain,LDD) MOSFET器件的漏极和源极,掺杂浓度比原来你n+型源 极与n+型漏极浓度低的n_型区。如图2-37

图 2-38 , 所 示 为 增 强 型 N 型 MOSFET有LDD以及无LDD 存在时,沟道接近漏极附近 的电场大小与分布情形。

❖ 这种限制第一次由,约翰冯诺依曼 提出,利用公式

正向偏压下的PN结

电压表

0

--

+

p

n

随着正向偏压的增加,PN结的耗尽区变窄。ຫໍສະໝຸດ EipqVD Ec

EF

Ein

集成电路材料与器件物理基础综述(ppt 25页)

q(Vbi –VDq)(Vbi –VD) Ec EFn EinEEcF EvEn in Ev

PN结符号

理想PN结半导体二极管电流方程

IDIS(eqD V/kT1)

PN结的基本应用

• 整流:使一个正弦波流经二极管,则只有大于零的正向

部分会到达后面的电路,这种滤除负向信号的过程称为整 流

10-9 ~102

SiO2、Si3N4

10-22 ~10-14

§2.4 PN结 了解pn结的意义

pn结---多数半导体器件的核心单元 电子器件:

整流器 (rectifier) 检波器 (radiodetector) 双极晶体管 (BJT)

光电器件:

太阳能电池 (solar cell) 发光二极管(LED) 半导体激光器 (LD) 光电二极管(PD)

扩散

饱和区:0<(VGS-VT)<VDS,电流与VDS 无关

根据杂质浓度的分布,可以划分为:

欧姆接触的金属与P型材料的选择 半导体激光器 (LD)

空穴

电流隔离:电流单向流动

发射结反偏,集电结也反偏时,为载断工作状态。

铝、金、钨、铜等,镍铬等合金,重掺多晶硅

理想PN结半导体二极管电流方程

随着正向偏压的增加,PN结的耗尽区变窄。

顶部的N型半导体收集另一个N型半导体提供的电子,叫集电极(Collector)

势垒的存在才导致了大的界面电阻。

正向偏压下理想PN结的能带图

JFET(junction gate field-effect transistor )

电子

eVbi

平衡态的pn结

• 扩散电 流 • 空间电荷区

• 内建电场 E

集成电路原理第四章ppt课件

4.1 MOS器件的基本电学特性

4.1.1 MOSFET的结构与工作原理

MOSFET——Metal-Oxide-Semiconductor

Field Effected Transistor

增强型〔常关闭型)

金属PM氧OS 化物半导体场效应晶体管

耗尽型〔常开启型)

MOSFET

iDSCOXLWvGSVthvDSvD 2S2

3.4

51

085 L

801

0030.43922220.62(m 5 )A

4.1.4 MOSFET小信号参数 (1〕跨导gm

——表示交流小信号时vGS对ids的控制能力〔vDS恒定)

饱和区:

gm

iDS vGS

vDSc onst

C OX LW vG SV th 1vDS

足电路设计的要求,此工序称为“调沟”。即向沟道区进行离

子注入〔Ion Implantation),以改变沟道区表面附近载流子浓

度,与此相关的项用

Qi C OX

表示。一般调沟用浅注入,注入能量

在60 80KeV左右;若异型注入剂量、能量较大,则可注入到

体内,形成埋沟MOS〔Buried-Channel MOS)。

例4-2 知:n+ Poly-Si栅NMOS晶体管宽长比W/L=100 m/10 m, 漏、栅、源、衬底电位分别为5V,3V,0V,0V。

n=580cm2/V s,其他参数与例4-1相同。 求:① 漏电流iDS。

② 若漏栅源衬底电位分别为2V,3V,0V,0V,则IDS=?

解:① 由已知得: vGS=3V,vDS=5V,vBS=0V 而由例4-1得Vth=0.439V vDS=5V(vGS-Vth)=3-0.439=2.561(V) 器件工作在饱和区,那么:

集成电路内部构造-概念解析以及定义

集成电路内部构造-概述说明以及解释1.引言1.1 概述集成电路是一种能够将多个电子元件和电路功能集成到一个单一芯片上的技术。

与传统电路相比,集成电路具有体积小、功耗低、速度快等显著优势。

它广泛应用于计算机、通信、嵌入式系统以及各种电子设备中。

在集成电路内部构造方面,包含了多个基本元件和互连结构。

基本元件可以是传统的电阻、电容、电感等passiv元件,也可以是能够实现逻辑功能的转换器、门电路、触发器等active 元件。

互连结构则是将这些元件连接起来,形成一个完整的电路,实现特定的功能。

随着技术的不断进步,集成电路的内部构造也在不断演进。

从早期的小规模集成电路到现在的超大规模集成电路,集成度不断提高,功能更加强大。

同时,集成电路的制造工艺也在不断改进,如光刻技术、扩散技术等,使得更多的元件能够被集成到一个芯片上。

在今后的发展中,集成电路内部构造将更加注重实现更高的集成度和更复杂的功能。

同时,随着人工智能、物联网等技术的兴起,集成电路内部构造也将面临更多的挑战和机遇。

因此,研究和探索集成电路内部构造的意义和应用,以及展望未来的发展方向,对于推动整个电子产业的发展具有重要的意义。

1.2 文章结构文章结构部分的内容主要是对整篇文章的组织和安排进行介绍,目的是帮助读者更好地了解文章的结构和内容安排。

在本篇文章中,文章结构部分可以包括以下内容:文章的结构主要分为以下几个部分:1. 引言部分:在引言部分,我们将对集成电路内部构造的重要性进行概述,并介绍本文的目的和意义。

2. 正文部分:在正文部分,我们将详细介绍集成电路的定义、分类和组成,包括介绍各类集成电路的特点和应用领域等。

- 2.1 集成电路的定义:在这一部分,我们将阐述集成电路的概念和定义,包括对集成电路内部元器件关系的描述。

- 2.2 集成电路的分类:在这一部分,我们将介绍集成电路的不同分类方法,如按工艺、按功能等分类,并详细介绍每类集成电路的特点和应用。

讲稿第二章

第2章大规模集成电路制造工艺和版图设计集成电路制造是一项非常复杂的技术,本章的目的是介绍大规模集成电路器件的工艺流程以及衍生的集成电路元件和版图设计基础。

首先介绍制造集成电路的主要材料,接着介绍一些基本的加工工艺,包括形成二氧化硅膜的热氧化工艺,将杂质掺入硅中的杂质扩散和淀积工艺,将电路图形复制到硅片表面的光刻和刻蚀工艺,最后将描述三类集成电路的基本制造工艺,重点描述COMS集成电路的制造过程。

1.1半导体材料材料按导电性能可以分为导体、个导体和绝缘体三类。

如果说电气系统主要应用导体和绝缘体两类材料的话,电子系统特别是微电子系统则应用所有的三类材料。

集成电路虽然是导体、半导体和绝缘体三种材料有机组合形成的系统,但相对于其他系统,半导体材料在集成电路的制造巾起着根本性的作用。

首先,集成电路通常是制作在半导体衬底材料之上的:同时,集成电路的基本元件是依据半导体的特性构成的。

半导体材料之所以得到广泛的应用,是因为它具有以下特性,(1)通过掺入杂质可以明显改变半日体的电导率。

例如,在室温30℃时,在纯净锗中掺入亿分之一的杂质,电导率会增加几百倍。

正是因为掺杂可控制半导体的电导率,才能利用它制造出各种不同的半导体器件。

(2)当半导体受到外界热的刺激时,其导电能力将发生显著变化。

利用这种热敏效应可制成热敏器件。

另—方面,热敏效应会使半导体的热稳定性下降,所以出半导体构成的电路中常采用温度补偿等措施。

(3)光照也可以改变半导体的电导率,通常称为半导体的光电效应。

利用光电效应可以制成光敏电阻、光电晶体管、光电精合器等*(4)多种由半导体形成的结构中,当注入电流时,会发射出光,从而r1J制造出发光—极管和激光二极管。

在这些材料中硅(Si,Sillcon)、砷化嫁(GaAs)和锗是较为常用的。

以这些材料为衬底,可以做出复杂的材料系统,不同的固态器件和集成电路。

硅是现代微电子工业的基础。

在过去的40年中,基于砖材料的多种工艺技术得以发展,并达到成熟,如双极型晶体管(BJT)、结型场效应管(J—PET)、P型场效应管(PMOS)、N型场效应管(NMoS)、互补型金属氧化物半导体场效应管(CMOS)及双极管CMOS(BiCMOS)等。

集成电路的物理工作原理

集成电路的物理工作原理

集成电路是由大量电子元器件构成,可以实现数字信号的操作、存储和传输。

集成电路的物理工作原理基于半导体物理学和微电子技术。

其主要结构包括晶片、接线和封装三部分。

晶片是集成电路最核心的部分,也叫做芯片。

晶片是一个由半导体材料组成的单片硅片,上面有各种电子元器件,例如晶体管、二极管和电容等。

这些元器件用电子束或光刻技术制造而成,非常小巧,通常仅有几微米的大小。

晶片中的这些元器件被连接成各种电路,实现不同的功能。

晶片的性能取决于元器件的材料和结构设计。

接线是将晶片中的各种元器件和电路与外部世界连接起来的桥梁。

接线使用金属线、铜箔线等材料制成,并通过微电子技术印制在晶片表面。

接线是集成电路中最繁琐的部分,因为每个元器件都需要与其他元器件连接,而且这些连接必须遵循严格的设计规则。

封装是将晶片和接线封装在塑料或陶瓷外壳中,以便集成电路可以便于安装和使用。

封装的形式有多种多样,如双列直插(DIP)、表面贴装(SMT)等。

不同的封装形式适用于不同的应用场景。

总之,集成电路的物理工作原理是在晶片、接线和封装三部分的共同作用下,实现数字信号的处理和传输。

随着科技的不断发展,集成电路的性能不断提高,应

用范围也越来越广泛。

超大规模集成电路设计基础-第三章

3.3 CMOS工艺层

CMOS工艺是有关从裸硅“圆片”到形成 最终的电子集成电路所需要的一系列步骤。 n阱工艺起始于p型衬底(圆片),nFET可 以直接在p型衬底上形成,加上n阱区是为 了包括pFET。

栅

n+ FOX P+ n阱 栅氧化层

P衬底

nFET

pFET

n+

p+

n阱

一旦定义了基本的晶体管工艺层,就可 加上用玻璃绝缘体分隔开的导电金属层以便 连线。现代工艺往往可有5个或更多的金属互 连线层以缓解复杂电路中大量布线的问题。

互连线的电阻和电容

逻辑门之间通过点与点之间的信号流路 径相互通信。在集成电路层次上,这一 任务是通过形成图形的金属线作为导线 来传导电流而完成的。电流的大小还取 决于这些金属线材料的物理性质及其尺 寸。

电导率 表示电流容易通过的程度,其值越大,材料层的

导电性就越好

线电阻的欧姆数

R line ( 1

在晶体中掺入硼原子可以增加带正电荷的空穴 数。得到的样品称为p型材料。

同样,我们用下式计算载流子密度:

p p N a cm

3

np

ni

2

cm

3

Na

一个载流子密度为n和p的半导体区域,其电导 率为: q ( n n p p )

对于一个特定的n型样品,通常可以近似其电 导率为: q n n n

L

W

3.2.1 硅的导电性

硅中只有很少量的电子由于热激发的作 用获得热能而脱离原来的硅原子,具有 导电性。 在室温下(T=27o)本征载流子密度

n i 1 . 45 10

10

cm

3

n p ni np n i

集成电路--物理

集成电路集成电路(integrated circuit)是一种微型电子器件或部件。

采用一定的工艺,把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗、智能化和和高可靠性方面迈进了一大步。

它在电路中用字母“IC”表示。

集成电路发明者为杰克·基尔比(基于锗的集成电路)和罗伯特·诺伊思(基于硅的集成电路)。

当今半导体工业大多数应用的是基于硅的集成电路。

集成电路(Integrated Circuit,简称IC)是20世纪50年代后期一60年代发展起来的一种新型半导体器件。

它是经过氧化、光刻、扩散、外延、蒸铝等半导体制造工艺,把构成具有一定功能的电路所需的半导体、电阻、电容等元件及它们之间的连接导线全部集成在一小块硅片上,然后焊接封装在一个管壳内的电子器件。

其封装外壳有圆壳式、扁平式或双列直插式等多种形式。

集成电路技术包括芯片制造技术与设计技术,主要体现在加工设备,加工工艺,封装测试,批量生产及设计创新的能力上。

集成电路或称微电路(microcircuit)、微芯片(microchip)、芯片(chip)在电子学中是一种把电路(主要包括半导体装置,也包括被动元件等)小型化的方式,并通常制造在半导体晶圆表面上。

前述将电路制造在半导体芯片表面上的集成电路又称薄膜(thin-film)集成电路。

另有一种厚膜(thick-film)混成集成电路(hybrid integrated circuit)是由独立半导体设备和被动元件,集成到衬底或线路板所构成的小型化电路。

本文是关于单片(monolithic)集成电路,即薄膜集成电路。

集成电路具有体积小,重量轻,引出线和焊接点少,寿命长,可靠性高,性能好等优点,同时成本低,便于大规模生产。

集成电路 (7)

第一节 概 述

一、集成电路简介

二、集成电路中的元件

概

述

三、模拟集成电路的结构特点

四、集成运放的组成

一、集成电路简介

第一节

集成电路是一种将“管”和“路”

紧密结合的器件,它以半导体单晶

定

硅为芯片,应用半导体制造工艺把

义

晶体管、场效应管、电阻、小容量

电容等许多元件以及它们之间的连

线都做在同一芯片上,然后封装在

集成运放的偏置电流通常较小,以降低电路 的功耗。 为了克服直接耦合电路的温漂,采用差动放 大电路。

大量采用晶体管或场效应管构成恒流源,代 替大电阻。

采用复合管的接法以改进单管的性能。

同类元件的相对误差小,匹配性好,性能比 较一致,因而特别适宜于制作采用对称式结 构的电路。

管壳里。

特 点

为集体这成积样电功制路小耗成(、的I低n重t具e、g有量ra可特t轻ed定靠C、功i性r能性cu高的it能,电. I好子C)电、路。称

集成电路的分类

第一节

集成运算放大器

集

模拟集成电路

按特 点分

集成稳压器

成 电

集成功率放大器

路 数字集成电路

其他种类

我国集成电路发展

第一节

集成运放

通用型集成运算放大器

六掩 膜

选择 要去 掉的 铝层

基区扩散

发射区、 集电极区扩散

蒸铝

2. PNP型三极管

第一节

ce

b

c eb

P

N+

P P N+

P+

P+

P+

N

N

N

N+ P

衬底PNP型管

横向PNP型管

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.3晶体管版图简介

2019/12/24

PMOS晶体管

8

西安邮电学院ASIC中心

CMOS集成电路版图

3.3晶体管版图简介

2019/12/24

9

西安邮电学院ASIC中心

CMOS集成电路版图

3.3晶体管版图简介

2019/12/24

NMOS晶体管

10

西安邮电学院ASIC中心

3.3 晶体管版图简介

CMOS集成电路版图

结合使用四种类型的层就可以创建晶体管、电阻、电 容以及互连。

2019/12/24

2

西安邮电学院ASIC中心

CMOS集成电路版图

版图器件层

FOX+Active=surface

2019/12/24

3

西安邮电学院ASIC中心

3.2.1多边形

CMOS集成电路版图

多边形主要用于覆盖无法用简单矩形覆 盖的区域,如单元边界、晶体管、n阱、 接触、扩散区及晶体管栅极。

Layout of a transmission gate with a driver

2019/12/24

23

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

2019/12/24

NAND2 layout

24

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

反相器:方案1

2019/12/24

19

西安邮电学院ASIC中心

3.3.3 FET阵列设计

CMOS集成电路版图

反相器:方案2

2019/12/24

20

西安邮电学院ASIC中心

3.3.3 FET阵列设计

CMOS集成电路版图

物理设计的目标之一:整个芯片面积最小

2019/12/24

两个独立非门相邻

共享电源、共享地

2019/12/24

27

西安邮电学院ASIC中心

3.3.3 FET阵列设计

CMOS集成电路版图

NOR3/NAND3

2019/12/24

28

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

2019/12/24

29

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

电路图

表面视图

原理图的画法最好与版图相对应

2019/12/24

17

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

方案2:n+区全部被分开,有源区面积较大,但互 连线较短

电路图

2019/12/24

表面视图

18

西安邮电学院ASIC中心

3.3.3 FET阵列设计

CMOS集成电路版图

2019/12/24

11

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.1 衬底连接

2019/12/24

反相器衬底连接的截面图

12

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.1 衬底连接

目前多数硅晶圆是P型的 衬底连接:N阱中N型;P衬上P型;

显示衬底连接的晶圆截面图

2019/12/24

2019/12/24

NOR2 gate design

25

西安邮电学院ASIC中心

NAND2-NOR2 Layout Comparison

CMOS集成电路版图

2019/12/24

26

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

ANAND2 and NOR2 layouts using vertical FETs.

主要用于连接器件,传送信号 通常采用“曼哈顿”几何形状,即所有的转角都是90o

2019/12/24

6

西安邮电学院ASIC中心

3.2.2线形

CMOS集成电路版图

线形的优势

存储数据小 屏幕刷新时间短 占用内存、cpu时间少 通过线形的merge生成多边形

2019/12/24

7

西安邮电学院ASIC中心

CMOS集成电路版图

13

西安邮电学院ASIC中心

3.3.2 导体和接触孔

CMOS集成电路版图

导体层

1PNM

接触孔和通孔

Contact Via

隔离物 层叠式通孔

2019Байду номын сангаас12/24

14

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

两个串联的nFET

有1个n+区被共享

电路图

2019/12/24

表面视图

第三章 版图设计

CMOS集成电路版图

3.1 CMOS VLSI制造工艺简介 3.2 分层和连接 3.3 晶体管版图简介 3.4 工艺设计规则 3.5 纵向连接图 3.6 通用设计步骤

2019/12/24

1

西安邮电学院ASIC中心

CMOS集成电路版图

3.2分层和连接

导体

扩散区 金属层 多晶层 阱层

隔离层:避免电气节点间产生“短路” 接触孔和通孔 注入层

2019/12/24

4

西安邮电学院ASIC中心

3.2.1多边形

CMOS集成电路版图

多边形的优势

圈起形状奇特的区域 易于绘制、增加、减少、拼接

多边形的缺点

不易修改 数据存储量大

2019/12/24

5

西安邮电学院ASIC中心

3.2.2线形

CMOS集成电路版图

由起点、终点、中间顶点及宽度值定义的一种 几何形状。

2019/12/24

30

西安邮电学院ASIC中心

3.3.3 FET阵列设计

CMOS集成电路版图

实例1和2的对比

逻辑对偶

2019/12/24

31

版图对称

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

A general 4-input AOI gate

晶体管的长度、宽度是两个最重要的参数(尺寸 参数)

长度:

版图角度,源极、漏极间的距离,通常比宽度小 性能角度:管子导通时,为了形成一个可测的电流,载流子所必须

移动的距离 制造角度:多晶能够可靠制造的最细线条的宽度

宽度:

电流流经的沟道的宽度

为了提高电路速度,总是希望晶体管的宽长比越 大越好。 但宽长比并不总是越大越好

Two NOT gates that share power supply and ground.

21

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

两个反相器串联

共享电源、地、源、漏

2019/12/24

22

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

15

侧视图

西安邮电学院ASIC中心

CMOS集成电路版图

3.3.3 FET阵列设计

三个串联的nFET(有2个n+区被共享)

电路图

2019/12/24

表面视图

16

西安邮电学院ASIC中心

3.3.3 FET阵列设计

CMOS集成电路版图

两个并联的nFET

方案1:有1个n+区被共享,有源区面积较小,但互连线较长