QFN封装的组装和PCB布局指南

QFN封装Layout指导

IntroductionLeadless Quad Flat Pack (QFN) packages are plastic-encapsulated with a copper lead frame substrate, providing a robust, low-cost solution for small form factor applications such as mobile handsets and other battery operated consumer products. Dual-row QFN packages have interstitial, staggered contacts. The inner row is offset 0.5 mm, resulting in a compact design that does not exceed the surface mount technology (SMT) capability of a typical 0.5 mm pitch surface-mount process.Because SiliconBlue iCE65 mobileFPGA devices have the ultra-low power consumption, connecting the center thermal pad is not required. Therefore, when designing a PCB for an iCE65 mobileFPGA in the QN84 package, the following primary factors can affect the successful package mounting on the board:⏹ Perimeter Land Pad and Trace Design ⏹ Stencil design ⏹ Type of vias ⏹ Board thickness⏹ Lead finish on the package ⏹ Surface finish on the board ⏹ Type of solder pasted ⏹Reflow profileThese are general guidelines and other factors may affect the successful and reliable mounting of a QN84 package. Additionally, particular applications may require specific analysis and/or considerations that are not covered here.All spacing calculations assume a standard four-layer board using one-half ounce of copper. Perimeter Land Pad and Trace DesignIn several published QFN tests, trace cracking was observed during board-level drop and bend tests. The reported trace cracking usually occurred at the edge of the solder mask opening around the metal pad. To avoid this failure mode, widen the trace under the solder mask edge so that it is wider than the remainder of the trace as shown in Figure 1. Depending on the reliability requirements, the wider part of the trace might need to be as wide as 50 to 75% of the metal pad width.Avoid if possiblePreferred, where B > 50% • ANon-solder mask defined (NSMD) pads are recommended for dual-row QFN packages, because the copper etching process has tighter control than the solder masking process and improves the reliability of the solder joints.AN016: Dual-Row QFN Package Assembly/PCB Layout GuidelinesStencil Design for Perimeter Land PadsFor reliable solder joints on dual-row QFN packages, pay extra attention because of the small land surface area and the sole reliance on printed solder paste on the PCB surface. Special considerations are needed in stencil design and paste printing for both perimeter lands. Because the surface mount process varies from company to company, careful process development is recommended. The following section provides some guidelines for stencil design based on industry experience.The optimum and reliable solder joints on the perimeter pads have about 50 to 70 µm (2 to 3 mils) standoff height. Tightly control the stencil aperture tolerance because these tolerances can effectively reduce the aperture size. Area ratios of 0.66 and aspect ratios of 1.5 were never exceeded. The land pattern on the PCB should be 1:1 to the land pads on QFN package.Stencil thickness of 0.125 mm is recommended for 0.5 mm dual-row QFN packages. A laser-cut stainless steel stencil with electro-polished trapezoidal walls is recommended to improve the paste release. SiliconBlue recommends that no-clean, Type 3 or Type 4 paste be used for mounting QFN packages. Nitrogen purge is also recommended during reflow. Reflow ProfileReflow profile and peak temperature have a strong influence on void formation. SiliconBlue strongly recommends that users follow the profile recommendation of the paste suppliers, since this is specific to the requirements of the flux formation. However, the following profile, Figure 2 serves as a general reference for SiliconBlue mobileFPGA devices.Figure 2: Typical Pb-Free Solder Flow ProfileWetting Time Time (seconds)T e m p e r a t u r e (°C )Assembly Process FlowQFN packages use the same process flow used for typical surface mount packages, without modification. Include post-print and post-reflow inspections, especially during initial process refinement. The paste volume should be approximately 80%–90% of stencil aperture volume to indicate sufficient paste release and should be measured either by 2D or 3D techniques. After reflow, inspect the mounted packages for the presence of voids, solder balling, or other defects. Cross-section analysis may be required to determine the fillet shape and size and joint standoff height.Rework GuidelinesSince solder joints are not fully exposed, retouch work for QFN packages is limited. For defects underneath the package, the entire device must be removed. In addition, rework of QFN packages after removal can be a challenge due to their small size. Also, since QFN devices are typically mounted on smaller, thinner, and denser PCBs, handling and heating can be problematic. Because of these complexities, the following guidelines provide a starting point for the development of a successful rework process for these packages.The rework process involves the following steps:1. Component removal2. Site redress3. Solder paste application4. Component placement and attachmentThe first step to remove the component is the reflow of solder joints attaching the component to the PCB board.Ideally the reflow profile for removing the component should be the same as the one used for part attachment.However, the time above liquid can be reduced as long as the reflow is completed. In the removal process, the board should be heated from the bottom side using a convective heater, and hot gas or air should be used on the top side of the component. A special nozzle should be used to direct the heating in the component area. The heating of adjacent components should be minimized. Air velocity of 15 to 20 liters per minute is a good starting point, and excessive airflow should be avoided. Once the joints have reflowed, the vacuum lift-off should be automatically engaged during the transition from reflow to cool down. Because of their small size, the vacuum pressure should be kept below 15 inches of mercury (Hg). This will ensure the component is not lifted if all joints have not been reflowed, thus avoiding pad liftoff.After the components have been removed, the site must be cleaned properly. Use a combination of a blade-style conductive tool and de-soldering braid. Match the width of the blade to the maximum width of the footprint and set the baked temperature low enough so as not to cause any damage to the circuit board. Once the residual solder is removed, clean the landing pads with solvent. The solvent is usually specific to the type of paste used in the original assembly and follow the paste manufacturer’s recommendations.Because of their small size and finer pitches, solder paste deposition for QFN packages require extra care. Use a miniature stencil specific for the component to achieve a uniform and precise deposition. Align the stencil aperture with the pads under 50X–100X magnification. Then, lower the stencil onto the PCB and deposit the paste with a small metal squeegee blade. Alternatively, use miniature stencil to print paste on the package site. Use a stencil with a thickness of 125 µm with an aperture size and shape the same as the package land. Use no-clean flux because the small standoff of QFN packages does not leave much room for cleaning.QFN packages have superior self-centering ability due to their small mass. Placing QFN packages is similar to BGA package placement. Because the land pads are on the underside of the package, use a split-beam optical system to align the component onto the motherboard. This optical system forms an image of land overlaid on the mating footprint and aid proper alignment. Again, perform the alignment at 50X–100X magnification. The placement machine should be capable of allowing fine adjustments in X, Y, and rotational axes. Use the reflow profile developed during the original component attachment or removal process to attach the new component. Since all reflow profile parameters have already been optimized, using the same profile eliminates the need for thermocouple feedback and reduces operator dependencies.Other DocumentationSee also the single-layer layout example for the QN84 package in the following application note.AN010: iCE65 Printed Circuit Board (PCB) Layout Guidelines/media/downloads/SiliconBlue_AN010.pdfAN016: Dual-Row QFN Package Assembly/PCB Layout GuidelinesAppendix I: Recommended PCB Layout DetailsFigure 3 shows the suggested board layout for the QN84 package on a top layer of a printed circuit board, assuming NSMD solder mask rules. The labeled dimensions are listed in Table 1.Figure 3: Top-layer LayoutFigure 4 shows the suggested layout if pads are connected on inner layers.Figure 4: Inner-layer LayoutLW1OTHRevision HistoryDisclaimerSILICONBLUE TECHNOLOGIES PROVIDES THIS APPLICATION NOTE TO YOU “AS-IS”. ALL WARRANTIES, REPRESENTATIONS, OR GUARANTEES OF ANY KIND (WHETHER EXPRESS, IMPLIED, OR STATUTORY) INCLUDING, WITHOUT LIMITATION, WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY DISCLAIMED.LIMITATION OF LIABILITY: SUBJECT TO APPLICABLE LAWS: (1) IN NO EVENT WILL SILICONBLUE TECHNOLOGIES OR ITS LICENSORS BE LIABLE FOR ANY LOSS OF DATA, LOST PROFITS, COST OF PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES, OR FOR ANY SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES ARISING FROM THE USE OR IMPLEMENTATION OF THE APPLICATION NOTE, IN WHOLE OR IN PART, HOWEVER CAUSED AND UNDER ANY THEORY OF LIABILITY; (2) THIS LIMITATION WILL APPLY EVEN IF SILICONBLUE TECHNOLOGIES HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES; (3) THIS LIMITATION SHALL APPLY NOTWITHSTANDING THE FAILURE OF THE ESSENTIAL PURPOSE OF ANY LIMITED REMEDIES HEREIN.Copyright © 2010 by SiliconBlue Technologies LTD. All rights reserved. SiliconBlue is a registered trademark of SiliconBlue Technologies LTD in the United States. Specific device designations, and all other words and logos that are identified as trademarks are, unless noted otherwise, the trademarks of SiliconBlue Technologies LTD. All other product or service names are the property of their respective holders. SiliconBlue products are protected under numerous United States and foreign patents and pending applications, maskwork rights, and copyrights. SiliconBlue warrants performance of its semiconductor products to current specifications in accordance with SiliconBlue's standard warranty, but reserves the right to make changes to any products and services at any time without notice. SiliconBlue assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by SiliconBlue Technologies LTD. SiliconBlue customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.。

QFN焊盘设计和工艺指南

QFN焊盘设计和工艺指南(湖州生力电子有限公司沈新海)一、基本介绍QFN(Quad Flat No Lead)是一种相对比较新的IC 封装形式,但由于其独特的优势,其应用得到了快速的增长。

QFN 是一种无引脚封装,它有利于降低引脚间的自感应系数,在高频领域的应用优势明显。

QFN 外观呈正方形或矩形,大小接近于CSP,所以很薄很轻。

元件底部具有与底面水平的焊端,在中央有一个大面积裸露焊端用来导热,围绕大焊端的外围四周有实现电气连接的I/O 焊端,I/O 焊端有两种类型:一种只裸露出元件底部的一面,其它部分被封装在元件内;另一种焊端有裸露在元件侧面的部分。

QFN 采用周边引脚方式使PCB 布线更灵活,中央裸露的铜焊端提供了良好的导热性能和电性能。

这些特点使QFN 在某些对体积、重量、热性能、电性能要求高的电子产品中得到了重用。

由于QFN 是一种较新的IC 封装形式,IPC-SM-782等PCB设计指南上都未包含相关内容,本文可以帮助指导用户进行QFN 的焊盘设计和生产工艺设计。

但需要说明的是本文只是提供一些基本知识供参考,用户需要在实际生产中不断积累经验,优化焊盘设计和生产工艺设计方案,以取得令人满意的焊接效果。

二、QFN封装描述QFN 的外形尺寸可参考其产品手册,它符合一般工业标准。

QFN 通常采用JEDECMO-220系列标准外形,在焊盘设计时可以参考这些外形尺寸(示例如图1)。

图 1 QFN元件三维剖视图和实物外观三、通用设计指南QFN的中央裸焊端和周边I/O焊端组成了平坦的铜引线结构框架,再用模铸树脂将其浇铸在树脂里固定,底面露出的中央裸焊端和周边I/O 焊端,均须焊接到PCB上。

PCB 焊盘设计应该适应工厂的实际工艺能力,以求取得最大的工艺窗口,得到良好的高可靠性焊点。

需要说明的是中央裸焊端的焊接,通过“锚”定元件,不仅可以获得良好的散热效果,还可以增强元件的机械强度,有利于提高周边I/O 焊端的焊点可靠性。

qfn封装流程

qfn封装流程QFN封装流程QFN(Quad Flat No-leads)封装是一种常见的集成电路封装技术,它具有尺寸小、焊接可靠性高等优点,在现代电子工业中得到广泛应用。

本文将介绍QFN封装的流程,并探讨其在电子封装领域的重要性。

一、QFN封装的概述QFN封装是一种无引线封装技术,其特点是焊盘位于芯片的底部,通过焊盘与印刷电路板(PCB)上的焊盘连接。

相比传统的封装技术,QFN封装具有更小的尺寸和更好的散热性能,适用于高密度集成电路的封装需求。

二、QFN封装的流程1. 芯片制备:首先,从硅片上切割出芯片,并进行测试和筛选。

然后,将芯片进行金属化处理,以便在后续的封装过程中与焊盘连接。

2. 焊盘制备:在PCB上制作焊盘,通常采用镀金或镀银的方式,以提高焊接可靠性和导电性能。

3. 芯片定位:将芯片精确地定位在PCB上的焊盘区域,通常采用自动化设备完成。

4. 焊接:使用热板或热风枪等设备,将芯片和焊盘加热至一定温度,然后利用焊料的润湿性将芯片与焊盘连接。

5. 清洗:清洗封装好的芯片,去除焊接过程中产生的杂质和污染物。

6. 芯片测试:对封装好的芯片进行功能性测试和可靠性测试,以确保其符合规定的电气性能要求。

7. 封装检验:对封装好的芯片进行外观检验和尺寸检验,以确保封装质量符合标准。

8. 封装包装:将封装好的芯片进行包装,通常采用真空包装或干燥包装,以保护芯片免受潮湿和静电等环境因素的影响。

三、QFN封装的重要性QFN封装在电子封装领域具有重要的应用价值。

首先,由于其尺寸小,QFN封装可以实现更高的元器件集成度,从而提高电路板的布局密度和系统性能。

其次,QFN封装的焊接可靠性高,能够有效减少因焊接引起的电路故障和失效。

此外,QFN封装还具有良好的散热性能,能够有效降低芯片的工作温度,提高系统的稳定性和可靠性。

四、结论QFN封装是一种常见且重要的集成电路封装技术,通过精确的制备和封装流程,能够实现小尺寸、高可靠性和良好的散热性能。

QFN焊盘设计和QFN焊盘设计和工艺指南工艺指南

QFN焊盘设计和QFN焊盘设计和工艺指南工艺指南引言:QFN(Quad Flat No-leads)封装是一种常用的表面贴装技术(SMT)封装,广泛应用于电子产品中。

QFN封装具有较小的尺寸、较高的密度和良好的散热性能,逐渐代替了传统的DIP、SOIC等封装。

本篇文章将重点介绍QFN焊盘设计和工艺指南,以帮助工程师顺利完成QFN封装的设计和制造。

一、QFN焊盘设计1.封装尺寸:QFN焊盘设计的第一步是确定封装的尺寸,根据产品的需求进行选择。

QFN封装一般有几种常见的尺寸标准,如QFN16、QFN32等。

2.焊盘定位孔:在设计QFN焊盘时,应考虑焊盘的定位。

由于QFN封装没有引脚,焊盘的定位孔起到了连接QFN封装与PCB板的作用。

因此,在焊盘的设计过程中,需要加入定位孔来确保QFN封装的精确定位。

3.焊盘布局:QFN焊盘设计的另一个重要考虑因素是焊盘的布局。

焊盘的布局应尽可能合理,避免相邻焊盘之间出现短路和焊盘间距过近导致焊接不良的问题。

4.焊盘尺寸:焊盘尺寸的选择需要根据焊接工艺的要求和焊接设备的能力来确定。

一般来说,焊盘的尺寸可以参考QFN封装的数据手册。

5.铺铜面积:为了提高焊接的可靠性和热传导性能,应在焊盘周围铺设一定面积的铜。

这可以提高焊接的稳定性,并提高QFN封装的散热效果。

二、QFN焊盘制造工艺指南1.焊盘制造:焊盘的制造过程一般包括切割、抛光、镀锡等工艺。

切割工艺主要是将QFN封装的焊盘切割到正确的尺寸。

抛光工艺是为了提高焊盘的光洁度和平整度。

镀锡工艺是为了提供焊接所需的锡层,提高焊盘和焊头之间的接触性能。

2.焊盘检测:焊盘制造完成后,需要进行焊盘的检测。

焊盘检测主要包括焊盘的外观检查、焊盘的尺寸检查、焊盘的平直度检查等。

3.焊接工艺:焊接工艺是QFN焊盘制造中至关重要的一步。

合适的焊接工艺可以确保焊接的质量和可靠性。

在焊接过程中,需要注意控制焊接温度、焊接时间和焊接压力。

4.散热处理:QFN封装的散热处理对于产品的可靠性至关重要。

功率四方扁平无引脚PQFN封装

Outside PQFN Extra PCB Pad Length ཌ䜞PQFN仓ཌPCB ❀ⴎ䮵ᓜ

PCPBCBP❀adⴎ

00..1155 mmm

PPQQFFNNᕋLe㓵ad PQPFQNFሷN 㻻Package

দ⭫䐥ᶵ Printed Circuit Board

图 2. 封装引脚和推荐 PCB 焊盘的横截面

© Freescale Semiconductor, Inc., 2007. All rights reserved.

功率四方扁平无引脚 (PQFN) 封装

3 功率四方扁平无引脚 (PQFN) 封装

3.1 封装说明

PQFN 是一种表面贴装型塑料封装,封装下表面附有引脚。根据设备要求和目标应用,所有 PQFN 封装均设计为采用单个外露式散热引脚 (标志)或多个外露式散热引脚。行业标准化委 员会 JEDEC 指定的 MO-251 注册代号用于描述单个外露式裸焊盘 PQFN 封装系列产品。

1 目的 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2 范围 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

3 功率四方扁平无引脚 (PQFN) 封装 . . . . . . . . . . 2 3.1 封装说明. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

选定外焊盘行长度后,就需要设定 PCB 内行与外行之间的间距。在本例中,切割街区保守地设 定为 0.5 mm。由于 PCB 外焊盘行长度为 0.775 mm,切割街区宽度为 0.50 mm,因此应从封装 边缘内 1.275 mm 处的位置开始安装内 PCB 焊盘。

基于QFN封装IC的印制板设计和装配

IntroductionThe need for low-cost surface mount plastic packages that operate to high frequency with low package thermal resistance has led to the development of Quad Flatpack No-Lead (QFN) packages. The industry standard description for these packages is JEDEC MO-220 or “Thermally enhanced plastic very thin and very fi ne pitch quad fl at no lead package (QFN)”. Hittite Microwave Corporation offers standard products in QFN packages operating at frequencies up to 16 GHz. To successfully integrate these new packages into a system design, proper PCB layout, handling and assembly guidelines must be followed.General Description of QFN (LPCC) PackagesHittite standard products that make use of QFN packages carry the simple suffi x “LP3” or “LP4”, representing leadless packages that are 3x3mm (fi gure 1a) or 4x4mm (fi gure 1b) in size. These packages typically contain 16 and 24 I/Os respectively and have exposed metal on the underside of the package that must be attached to both an RF groundplane and a proper thermal path.LP3 & LP4 NOTES:1. MATERIAL PACKAGE BODY:LOW STRESS INJECTION MOLDED PLASTIC SILICA AND SILICON IMPREGNATED.2. LEAD AND GROUND PADDLE MATERIAL: COPPER ALLOY 3. LEAD AND GROUND PADDLE PLATING: Sn/Pb SOLDER 4. DIMENSIONS ARE IN INCHES [MILLIMETERS].5. LEAD SPACING TOLERANCE IS NON-CUMULATIVE6. PAD BURR LENGTH SHALL BE 0.15mm MAXIMUM. PAD BURR HEIGHT SHALL BE 0.05mm MAXIMUM.7. PACKAGE WARP SHALL NOT EXCEED 0.05mm.8. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.Figure 1a – LP3 outlineFigure 1b– LP4 outlineFOR QFN PACKAGESPCB Solder Mask and Land Pattern DesignDue to the dense land pattern and exposed metal base of the QFN package, the PCB land pattern geometry is critical. The application of a solder mask is required, and must be applied to the PCB between the land pads and the ground pad. A minimum solder mask web of 0.010 inches [0.25 mm] between the land pads and the ground pad should be used in order to prevent shorting. Unless solid-fi lled vias are used, solder stop must also be applied to the backside of the PCB under the LP3/LP4 to prevent depletion (or wicking) of the solder paste from the device ground pad through the plated via holes during the reflow process.Figure 2a –LP3 solder mask and land patternFigure 2b – LP4 solder mask and land patternFOR QFN PACKAGESThe land pattern and solder mask pattern for the LP3 and LP4 packages are shown with their proper alignment in fi gure 2a and 2b respectively.Solder Paste ApplicationHand soldering of LP3 and LP4 packages is not recommended due to the fi ne pitch of the package leads and the inability to properly attach the exposed metal base to the PCB. Furthermore, the use of conductive epoxy is not recommended since these epoxies will bleed, causing shorts between lands and they do not have suffi cient thermal properties. Solder paste must be used to attach QFN packages to the PCB. For proper solder thickness and alignment, the solder paste must be applied to the PCB using a stencil printer. The volume of solder paste dispensed via screen-printing will be dependent on the stencil opening and stencil thickness. A recommended stencil pattern for the LP3 and LP4 package to be used with SN63 solder paste is shown in fi gure 3a and 3b respectively. Stencil alignment to the PCB land pattern should be to within +/-1 mil to prevent formation of solder balls between the lands during the refl ow process. A PCB with properly screened solder paste is shown in Figure 4.Component Placementdiffi cult and is not recommended. Therefore a pick-and-place machine with a microscope is recommendedfor the component placement operation. Careful device placement and minimal pressure will prevent solder paste smearing. To minimize solder paste smearing, the base of the LPCC package should be brought to a height of 3-4 mils above the surface of the PCB. This will result in the LPCC package being pressed 1-2 mils into the solder paste.Reflow Solder ProcessThe soldering process is usually accomplished in a refl ow oven but may also use a vapor phase process. Prior to refl owing the device, temperature profi les should be measured using the same mass as the actual assemblies. The thermocouple should be moved to various positions on the board to account for edge and corner effects and varying component masses. The fi nal profi le should be determined by mounting the thermocouple to the PCB at the location of the device. Follow solder paste and oven vendor’s recommendations when developing a solder refl ow profi le. A standard profi le will have a steady ramp up from room temperature to the pre-heat temperature to avoid damage due to thermal shock. Allow enough time between reaching pre-heat temperature and refl ow for the solvent in the paste to evaporate and the fl ux to completely activate. Refl ow must then occur prior to the fl ux being completely driven off. To help prevent the fl ux from being driven off, a steady ramp is preferred to the traditional soak. This profi le is also preferred for lead-free soldering. The duration of peak refl ow temperature should not exceed 15 seconds. QFN Packages have been qualifi ed to withstand a peak temperature of 235°C for 15 seconds. Verify that the profi le will not expose the device to temperatures in excess of 235°C. A typical refl ow profi le for the QFN package is shown in Figure 5.Figure 3a – LP3 solder paste stencilFigure 3b – LP4 solder paste stencilFOR QFN PACKAGESFigure 4 – PCB with properly screen solder pasteReworkingIn cases where the QFN package must be removed from the PCB and replaced, special tools and procedures are needed. In order to heat the QFN package suffi ciently to remove it without refl owing the solder of nearby components, a hot air workstation is recommended with an appropriate tool that limits the exposure of adjacent components to the hot air fl ow. If the part being removed will be reused, make sure not to exceed the 235°C maximum temperature of the QFN package.Once the package has been suffi ciently heated and the solder has melted, the QFN package should be removed with tweezers. The PCB and the bottom of the QFN package must then be thoroughly cleaned and all solder and fl ux removed. Solder wick is usually suffi cient to remove the solder from the surface of the board and bottom of the QFN package.Application of the solder paste must meet the criteria previously discussed. This can be accomplished using a solderpaste dispenser, although extreme care must be taken to apply the correct amount of paste in the proper locations. A more reliable method is to use a miniature stencil that can be applied directly onto the PCB at the location of the QFN package. Alternatively a stencil that applies the solder paste directly to the back of the QFN package can be used. Rework stencils are available from several manufacturers including the CPF (Component Print Frame) from Mini Micro Stencil Inc 1 (fi gure 6).Solder Refl ow can be accomplished using the hot-air workstation with care taken not to overheat the QFN package. Due to the small mass of the package, when the solder paste at the leads refl ows, the bottom of the package will also refl ow and the heat can then be removed.ConclusionThe PCB layout, handling and assembly processes necessary to successfully integrate QFN packages into a system design have been detailed. These processes are easily integrated into standard PCB manufacturing lines. All of the layout and stencil drawings presented are available from the factory and can be obtained by contacting Hittite Microwave Corporation by phone or by going on-line at and completing an inquiry form.1.. For the LP3 package use part number CPF-16.For the LP4 package use part number CPF-24.050100150200250012345678LPCC Reflow ProfileT e m p e r a t u r e (C )Time (Min.)Figure 5 – Typical LPCC refl ow profi leFOR QFN PACKAGESFigure 6 – ReworkCPF stencil。

QFN元器件PCB焊盘与贴片网板设计

0.28

0.6

正常 0.37

最小 0.15

最小 0.05

0.5

0.23

0.6

正常 0.28

最小 0.15

最小 0.05

0.5

0.23

0.4

正常 0.28

最小 0.15

最小 0.05

0.4

0.20

0.6

正常 0.25

最小 0.15

最小 0.05

表 1 I/O 焊盘设计指南

如果 PCB 有设计空间, I/O 焊盘的外延长度(Tout)大于 0.15mm,可以明显改善外侧 焊点形成,如果内延长度(Tin)大于 0.05mm,则必须考虑与中央散热焊盘之间保留足够的 间隙,以免引起桥连。

QFN 的外形尺寸可参考其产品手册,它符合一般工业标准。QFN 通常采用 JEDEC MO-220 系列标准外形,在焊盘设计时可以参考这些外形尺寸(示例如图 1)。

图 1 QFN 元件三维剖视图和实物外观

三、通用设计指南 QFN 的中央裸焊端和周边 I/O 焊端组成了平坦的铜引线结构框架,再用模铸树脂将其浇

图 2 典型的 QFN 元件焊端和 PCB 焊盘外观图

典型的 QFN 元件 I/O 焊端尺寸(mm)

典型的 PCB I/O 焊盘设计指南(mm)

第 4 部分:QFN(方形扁平无引脚封装)

图 16:0.65 mm 间距 QFN 过孔扇出和布线

图 17:0.5 mm 间距 QFN 过孔扇出和布线

图 18:0.4 mm 间距 QFN 过孔扇出和布线

7

QFN(方形扁平无引脚封装)元器件

结论

在创建方形扁平无引脚封装 (QFN) 元器件时,应该考虑各个设计方面,包括每个封装特性对 PCB 设计流程 所产生的影响。

图 12 QFN 包含多个散热片和“隐藏的管脚”。一些 QFN 封装包含采用不同形状和尺寸的 3-5 个散热片。

图 13 所示的 QFN 包含删除的管脚,并且管脚 1 位于左下角。在这里,管脚顺序是逆时针的,而不是传统 的顺时针管脚顺序。

图 11:具有不同引脚长度的 QFN

图 12:具有多个散热片和 删除管脚的 QFN

图 9:固晶焊焊盘上的散热垫焊膏层过大

4

QFN(方形扁平无引脚封装)元器件

不要尝试使用干膜阻焊层来遮盖过孔,因为这 会减小焊盘上的焊膏容积和面积。过孔焊盘 采用 0.5 mm 焊盘、0.7 mm 平面间距、0.25 mm 孔,并且不使用热焊盘。通过将过孔置于 1 mm 网格上,可在所有内层和相对侧采用双 0.1 mm 走线/空间布线技术。要实现 1 mm 过孔网格 捕捉,必须将 QFN 置于 0.5 mm 布局网格上。 有关散热垫中的过孔矩阵示例,请参见图 10。

图 6:QFN 元器件封装样式

3

QFN(方形扁平无引脚封装)元器件

散热片在最靠近管脚 1 的位置可能有一个倒角。“焊盘尺 寸”与散热片尺寸的最大容差相等。阻焊层尺寸与焊盘 尺寸保持 1:1 的比例关系。散热片在其他拐角上还可能包 含拐角半径。有关带有倒角和圆角拐角的散热片示例, 请参见图 7。

QFN封装的PCB焊盘和网板设计

QFN封装的PCB焊盘和网板设计

一、QFN封装的PCB焊盘设计

1、PCB焊盘的选择:QFN封装的PCB焊盘一般采用多条直线或多个圆

形焊盘,需要选择适当的焊盘形状,其尺寸应根据QFN封装的封装尺寸确定,以确保焊盘的完整性和位置精度。

2、焊盘的形状:QFN封装的PCB焊盘一般采用椭圆形、多条线状或

多个圆形焊盘,其中多条线状焊盘的通路应足够窄,以减少焊锡在焊盘通

路中的迁移。

3、焊盘尺寸:QFN封装的PCB焊盘的尺寸一般比QFN封装的封装尺

寸大,且其宽度也要大于封装宽度,尽可能的增大PCB焊盘的面积,以提

高焊接过程中焊锡的容积,确保焊接强度。

4、焊盘间距:QFN封装的PCB焊盘的间距应做到合理,且不能太近,太近容易影响焊接精度,焊接效果不理想。

二、QFN封装的PCB网板设计

1、网板选择:QFN封装的PCB网板应根据封装的尺寸、焊盘形状和

数量等参数来选定,其选择的网板应当稳定、耐高温,具有良好的焊接强度。

2、网板形状:QFN封装的PCB网板的形状可以采用标准圆形、正方形、长方形等,其尺寸应考虑外形大小、焊盘的形状和数量等参数,确保

网板的焊接质量和稳定性。

3、网板的厚度:QFN封装的PCB网板的厚度要根据使用的焊接温度和焊接深度等参数确定,以适应不同的焊接技术,保证网板的稳定性和焊接强度。

QFN(LPCC)封装PCB设计与装配指导

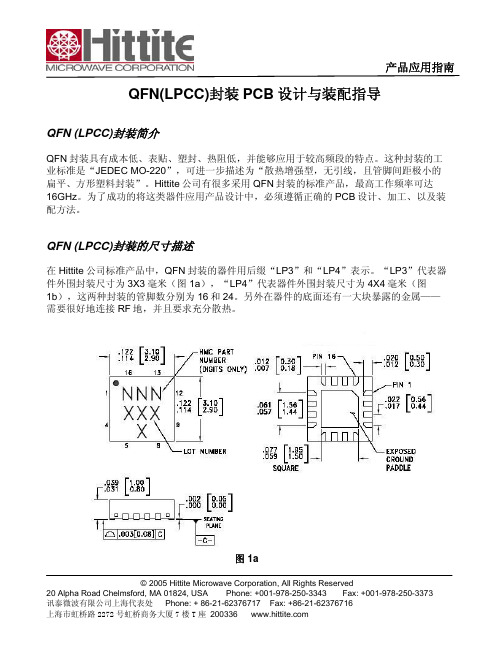

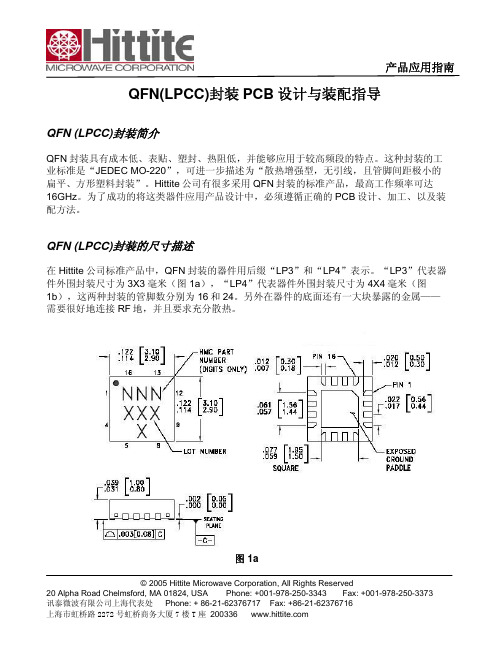

QFN(LPCC)封装PCB设计与装配指导QFN (LPCC)封装简介QFN封装具有成本低、表贴、塑封、热阻低,并能够应用于较高频段的特点。

这种封装的工业标准是“JEDEC MO-220”,可进一步描述为“散热增强型,无引线,且管脚间距极小的扁平、方形塑料封装”。

Hittite公司有很多采用QFN封装的标准产品,最高工作频率可达16GHz。

为了成功的将这类器件应用产品设计中,必须遵循正确的PCB设计、加工、以及装配方法。

QFN (LPCC)封装的尺寸描述在Hittite公司标准产品中,QFN封装的器件用后缀“LP3”和“LP4”表示。

“LP3”代表器件外围封装尺寸为3X3毫米(图 1a),“LP4”代表器件外围封装尺寸为4X4毫米(图1b),这两种封装的管脚数分别为16和24。

另外在器件的底面还有一大块暴露的金属——需要很好地连接RF地,并且要求充分散热。

图 1a© 2005 Hittite Microwave Corporation, All Rights Reserved图 1bLP3 与 LP4 封装说明:1. 封装的主体材质——通过低应力注入形成的二氧化硅与硅相互浸透的塑模。

2. 管脚引线与背面接地焊盘的材料——铜合金。

3. 管脚引线与背面接地焊盘的镀层——锡 / 铅焊料。

4. 尺寸单位标注说明——英寸 [毫米]。

5. 管脚间距的容差为非累加。

6. 焊盘长度的最大毛刺尺寸为0.15mm,焊盘厚度的最大毛刺尺寸为0.05mm。

7. 封装的外形扭曲尺寸小于0.05mm。

8. 所有接地的引线与焊盘必须与PCB上RF地可靠连接。

QFN封装的PCB阻焊层与焊盘样式设计由于QFN封装管脚密集且背面又有一块接地的大焊盘,所以在PCB设计中应该格外注意焊盘的几何尺寸。

为了防止短路,在信号线与地之间必需有阻焊剂。

阻焊剂网格的最小尺寸为© 2005 Hittite Microwave Corporation, All Rights Reserved© 2005 Hittite Microwave Corporation, All Rights Reserved0.010英寸[0.25mm]。

QFN(LPCC)封装PCB设计与装配指导

QFN(LPCC)封装PCB设计与装配指导QFN (LPCC)封装简介QFN封装具有成本低、表贴、塑封、热阻低,并能够应用于较高频段的特点。

这种封装的工业标准是“JEDEC MO-220”,可进一步描述为“散热增强型,无引线,且管脚间距极小的扁平、方形塑料封装”。

Hittite公司有很多采用QFN封装的标准产品,最高工作频率可达16GHz。

为了成功的将这类器件应用产品设计中,必须遵循正确的PCB设计、加工、以及装配方法。

QFN (LPCC)封装的尺寸描述在Hittite公司标准产品中,QFN封装的器件用后缀“LP3”和“LP4”表示。

“LP3”代表器件外围封装尺寸为3X3毫米(图 1a),“LP4”代表器件外围封装尺寸为4X4毫米(图1b),这两种封装的管脚数分别为16和24。

另外在器件的底面还有一大块暴露的金属——需要很好地连接RF地,并且要求充分散热。

图 1a© 2005 Hittite Microwave Corporation, All Rights Reserved图 1bLP3 与 LP4 封装说明:1. 封装的主体材质——通过低应力注入形成的二氧化硅与硅相互浸透的塑模。

2. 管脚引线与背面接地焊盘的材料——铜合金。

3. 管脚引线与背面接地焊盘的镀层——锡 / 铅焊料。

4. 尺寸单位标注说明——英寸 [毫米]。

5. 管脚间距的容差为非累加。

6. 焊盘长度的最大毛刺尺寸为0.15mm,焊盘厚度的最大毛刺尺寸为0.05mm。

7. 封装的外形扭曲尺寸小于0.05mm。

8. 所有接地的引线与焊盘必须与PCB上RF地可靠连接。

QFN封装的PCB阻焊层与焊盘样式设计由于QFN封装管脚密集且背面又有一块接地的大焊盘,所以在PCB设计中应该格外注意焊盘的几何尺寸。

为了防止短路,在信号线与地之间必需有阻焊剂。

阻焊剂网格的最小尺寸为© 2005 Hittite Microwave Corporation, All Rights Reserved© 2005 Hittite Microwave Corporation, All Rights Reserved0.010英寸[0.25mm]。

QFN封装的PCB焊盘和网板设计

QFN封装的PCB焊盘和网板设计近几年来,由于QFN封装(Quad Flat No-lead package,方形扁平无引脚封装)具有良好的电和热性能、体积小、重量轻,其应用正在快速增长。

采用微型引线框架的QFN封装称为MLF(Micro Lead Frame,微引线框架)封装。

QFN封装和CSP(Chip Size Package,芯片尺寸封装)有些相似,但元件底部没有焊球,与PCB的电气和机械连接是通过PCB焊盘上印刷焊膏经过回流焊形成的焊点来实现的。

QFN封装对工艺提出了新的要求,本文将对PCB焊盘和印刷网板设计进行探讨。

图1:外露散热焊盘的QFN封装QFN封装的特点QFN是一种无引脚封装,呈正方形或矩形,封装底部中央位置有一个大面积裸露焊盘用来导热,围绕大焊盘的封装四周有实现电气连接的导电焊盘。

由于QF N封装不像传统的SOIC与TSOP封装那样具有鸥翼状引线,内部引脚与焊盘之间的导电路径短,自感系数以及封装体内布线电阻很低,所以它能提供卓越的电性能。

此外,它还通过外露的引线框架焊盘提供了出色的散热性能,该焊盘具有直接散热通道,用于释放封装内的热量。

通常将散热焊盘直接焊接在电路板上,PCB中的散热过孔有助于将多余的功耗扩散到铜接地板中,从而吸收多余的热量。

图1显示了这种采用PCB焊接的外露散热焊盘的封装。

由于体积小、重量轻,以及极佳的电性能和热性能,QFN封装特别适合任何一个对尺寸、重量和性能都有要求的应用。

与传统的28引脚PLCC封装相比,32引脚QFN封装的面积(5mm×5mm)缩小了84%,厚度(0.9mm)降低了80%,重量(0.06g)减轻了95%,电子封装寄生效应也降低了50%,所以非常适合应用在手机、数码相机、PDA及其他便携电子设备的高密度PCB上。

PCB焊盘设计QFN的焊盘设计主要包含以下三个方面:周边引脚的焊盘设计、中间热焊盘及过孔的设计和对PCB阻焊层结构的考虑。

第 4 部分:QFN(方形扁平无引脚封装)

散热垫

所有端子焊盘上 1:1 比例的焊膏层

重心原点

所有焊盘上隆起的 75um 焊膏层

散热垫上划分为方形 的 40% 焊膏缩减

IPC 布局控制区 0.25 mm 外部边界

图 14:QFN 封装细节

已执行 0.25 mm 丝印层到 焊盘间距自动 DRC 检查

已执行 2 mm 散热垫到 焊盘间距 DRC 检查

有两种类型的 QFN 元器件封装样式:标准型和凸缘型。标准型封装通常称为“锯痕”封装,而凸缘型则 称为“模制实体”封装。有关这两种类型的元器件封装样式,请参见图 6。

引脚 焊盘脚趾

封装

PCB 叠层结构

焊盘脚跟

封装

PCB 端视图

引脚 焊盘

图 5:扁平无引脚边缘端子类型

标准型(锯痕)

凸缘型(模制)

底座面

图 6:QFN 元器件封装样式

3

QFN(方形扁平无引脚封装)元器件

散热片在最靠近管脚 1 的位置可能有一个倒角。“焊盘尺 寸”与散热片尺寸的最大容差相等。阻焊层尺寸与焊盘 尺寸保持 1:1 的比例关系。散热片在其他拐角上还可能包 含拐角半径。有关带有倒角和圆角拐角的散热片示例, 请参见图 7。

■ 与原理图设计和库管理环境集成的元器件管理系统。 ■ 内置的库数据一致性检查功能可确保您的库始终保持同步状态。 ■ 参照最新的元器件和库数据对原理图中布置的符号进行实时验证,从而消除代价巨大的重新设计,

图 13:具有删除管脚的 QFN。管脚 1 位于左下角并采用逆时针管脚顺序编号

5

QFN(方形扁平无引脚封装)元器件

图 14 显示了构成 QFN 封装库元件的所有元素的全景图。

丝印层管脚 1 极性

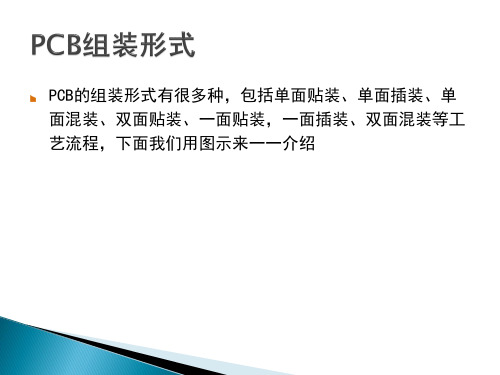

第2讲PCB安装形式及布局要点

间距要求 1.对于贴片元件,考虑到元器件制造误差、贴装误差以及检查和返修之需,相邻元器件焊盘之间间 隔不能太近,建议按照以下原则设计: a) PLCC、QFP、SOP 各自之间和相互之间间隙≥2.5mm; b) PLCC、QFP、SOP 与Chip 、SOT 之间间隙≥1.5mm; c) Chip、SOT 各自之间和相互之间间隙≥0.7mm; d) BGA 与其他元件的间隙≥5mm。 2. 贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm。 3.元器件的外侧距板边的距离为5mm。 4.波峰焊时,两个大小不同的元件或错开排列的元件,它们之间的间距必须≥2.5mm.。否则,前面 的元件可能挡住后面的元件,造成漏焊。

需要安装较重的元件时,应考虑安装位置和安装强度;应安排在靠近印制板支承点 的地方,使印制板的翘曲度减少最小。还应计算引脚单位面积所承受的力,当该值 ≥0.22 牛顿/mm2时,必须对该模块采取固定措施,不能仅仅靠引脚焊接来固定。

对于有结构尺寸要求的单板,其元器件的允许最大高度应为: a) 元器件的允许最大高度=结构允许尺寸-印制板厚度-4.5mm; b) 超高的应采用卧式安装。

单面混装

印刷锡膏

贴装元件

回流焊

插通孔元件

波峰焊

清洗

PCB组装二次加热,效率较高

* 如果通孔元件很少,可采用回流焊和手工焊的方式

双面贴装

B面 印刷锡膏

贴装元件

A面

回流焊

翻转

印刷锡膏

贴装元件

回流焊

翻转

A面布有大型IC器件,B面以片式元件为主

清洗

充分利用 PCB空间,实现安装面积最小化,效率高

一面贴装、另一面插装

间距要求 对于贴片元件,考虑到元器件制造误差、贴装误差以及检查和返修之需,相邻元器件焊 盘之间间隔不能太近,建议按照以下原则设计: a) PLCC、QFP、SOP 各自之间和相互之间间隙≥2.5mm; b) PLCC、QFP、SOP 与Chip 、SOT 之间间隙≥1.5mm; c) Chip、SOT 各自之间和相互之间间隙≥0.7mm; d) BGA 与其他元件的间隙≥5mm。

qfn封装流程

qfn封装流程

QFN封装是一种新型的表面贴装封装技术,它具有体积小、重量轻、高密度、高可靠性等优点,因此在电子产品中得到了广泛应用。

下面

将介绍QFN封装的流程。

一、基板制备

首先需要准备好基板,通常使用FR-4玻璃纤维板或者陶瓷板。

基板需要经过表面处理,包括去除氧化层、清洗、沉积金属等步骤,以保证

焊接质量。

二、印刷焊膏

将焊膏印刷在基板上,焊膏的成分和厚度需要根据具体的封装要求进

行调整。

印刷焊膏的设备通常是自动化的,可以提高生产效率和质量。

三、贴片

将芯片贴在基板上,需要注意芯片的方向和位置。

贴片设备通常是自

动化的,可以提高生产效率和质量。

四、热压焊接

将基板和芯片放入热压机中,进行热压焊接。

热压焊接的温度和时间

需要根据具体的封装要求进行调整。

热压焊接可以使焊膏熔化,将芯

片和基板焊接在一起。

五、切割

将焊接好的基板切割成单个的QFN封装。

切割设备通常是自动化的,可以提高生产效率和质量。

六、测试

对QFN封装进行测试,包括外观检查、焊接质量检查、电性能测试等。

测试设备通常是自动化的,可以提高生产效率和质量。

七、包装

将测试合格的QFN封装进行包装,通常使用盘装或者卷装的方式。

包装设备通常是自动化的,可以提高生产效率和质量。

总之,QFN封装流程需要经过基板制备、印刷焊膏、贴片、热压焊接、

切割、测试和包装等步骤。

每个步骤都需要严格控制,以保证QFN封装的质量和可靠性。

QFN封装的组装和PCB布局指南

QFN封装的组装和PCB布局指南前言双排或多排QFN封装是近似于芯片级塑封的封装,其基板上有铜引线框架。

底部上面裸露的芯片粘附焊盘会有效地将热量传递给PCB,并且通过下面的键合提供稳定的接地或通过导电芯片粘附材料形成电气连接。

双排或多排QFN封装的设计实现了柔性,并提高了在极高速操作频率下的电气性能。

双排或多排QFN封装采用有间隙的引线设计,这种设计可形成交错排列的引线布局。

内排交错0.5mm,就会使最大尺寸芯片实现紧凑致密的设计,同时,不会超过通常的0.5mm间距的SMT工艺的表面组装技术(SMT)的能力。

Actel公司提供的QFN封装有三种结构:QN180、QN132和QN108。

这些封装的印脚和外形是按照JEDEC MO-247标准:塑料四方无引线交叉排列的多排封装(增热任选)和按照JEDEC Design Guide 4.19:四方形无引线交叉排列的多排封装而实施的。

QFN封装概述图1和图2所示是通过同一平面上的芯片和线焊焊盘使这种封装的高度达到最小化。

图3说明了这种焊盘的结构。

在组装时,引线直接与板子连接,而不像塑料四方(PQ)或薄形四方(TQ)那样,在引线封装内留有一定间隙的高度以便分离。

此外,由于芯片焊盘直接与PCB连接,使得QFN封装具有极好的散热性。

由于QFN封装的有效和致密的设计,还会降低电子寄生效应。

表1所列是典型的可靠性数据。

表1 可靠性为了达到峰值性能,母板的设计必须合适,且对于封装的组装必须给予特别的构思。

就提高的温度、电气和板级性能而言,必须使用与板上热焊盘相对应的焊盘将封装上裸露的焊盘焊接到板上。

为了使板子能够实现有效的导热,PCB的热焊盘区域必须设置有导热通孔。

对内部一排引线和热焊盘之间的容差是有要求的,以便通过导通孔来布设内排信号的线路。

对容差量的要求取决于具体应用。

在设计PCB印脚时必须考虑到这一点,由于封装、PCB和板组装诸多方面的关联性,必须考虑到尺寸容差。

qfn pcb封装制作标准

qfn pcb封装制作标准

QFN(Quad Flat Non-leaded)是一种常见的PCB封装形式,以下是其制作标准:

1. 焊盘设计:焊盘是QFN封装的关键部分之一,其设计应考虑元件的引脚间距、元件大小、散热要求等因素。

焊盘的直径应略大于引脚直径,以增加焊接面积和可靠性。

焊盘之间的距离应符合元件规格书的要求,以保证元件能够正确放置和焊接。

2. 元件放置:在放置QFN封装元件时,应确保元件的标记面朝上,以便于识别和焊接。

元件的引脚应与PCB上的焊盘对齐,偏差应在允许范围内。

3. 焊接工艺:焊接QFN封装元件时,应使用合适的焊接温度和时间,以保证焊接质量和可靠性。

焊接后应检查焊点是否饱满、无气泡、无虚焊等现象。

4. 外观检查:外观检查是确保QFN封装元件质量的重要环节。

应检查元件是否正确放置、焊点是否饱满、无气泡、无虚焊等现象,以及元件的标记是否清晰可辨。

5. 可靠性测试:为确保QFN封装元件的可靠性,需要进行一系列的可靠性测试,如温度循环测试、振动测试等。

这些测试应按照元件规格书和相关标准进行。

总之,QFN封装制作标准涉及到多个方面,包括焊盘设计、元件放置、焊接工艺、外观检查和可靠性测试等。

只有符合这些标准,才能保证QFN封装元件的质量和可靠性。

QFN封装设计

QFN封装设计1. Introduction⽴理 , QFN/ DFN Package (Quad Flat No-lead, Dual Flat No-lead) 中央有⼀個⼤⾯積的散熱⽚ (SMD). QFN Package ( ⾯ )/ DFN Package (矩形⾯ ) 良導功性功能量 , (Figure 1)QFN的封装和CSP(Chip Scale Package) , QFN , 與PCB(Print Circuit Board)的電性和機械連接是通過QFN四周底部的焊盤(Pad)與PCB焊盤(Footprint or Land Pattern)上印刷錫膏、過IR回焊流来實現的, SMT(Surface Mount Technology)有關於PCB Footprint 設計, ⽬前業界參考IPC-SM-782, 但是QFN对PCB焊盤設計仍然是屬於較新的製程, 相關的QFN Footprint設計規格仍在發展中, 所以此份Application Note提供使⽤者有關於QFN General Guideline。

數, Guideline , 理,Figure 1: QFN Section View2. QFN/ DFN Outline Drawings有關於RichTek QFN/ DFN Package Outline 請參考RichTek Data Sheet Outline Dimension, 亦可在RichTekWeb-site 4.1.2 Outline Dimension Package Outline Dimension.3. SMT ProcessSMT 數良率, 數 SMT 參PointFactors ControlSolder Paste Shippment and Storeage Tempture, Paste Expiration Date, Viscosity and Texture, Dry out, Stencil Design PCB Quality Clean, Flat, Residue, Wrapage…Reflow Profile Profile Depended PCB Design, PCB Thickness, Compontent…4. Stencil Design Guideline4.1 度 Stencil Thickness Design, 列 : 雷 , ⾦ . 度 , 略 Footprint , 1:1 Footprint. IPC-7525 . 130um~150um(5~6mils) , 150um 易連度 ( 更不 ), 參數4.2 Stencil Design for Thermal Pad了 Package QFN PCB Thermal Pad, Thermal Pad , Thermal Pad 易洞Void, Splatter, Solder Balling,… , 易 (Fig2), Thermal Pad 率 50%~80% , 連 >40%Fig.2 Excess Exposed Pad Solder列 , 列65 um ( 50~65um Depend on PCB ⼒)… PCB (Fig.3)Fig. 3: Thermal Pad Stencil Design4.3 Terminal Lead Stencil DesignSolder (Lead ) 50um~75um ⽴度(Stand-off), 兩 :Area Ratio: Area of Aperture open/ Aperture Wall Area=LW/2T(L+W) ? Area Ratio > 0.66 Aspect Ratio: Aperture With/ Stencil Thickness= W/T ? Aspect Ratio > 1.5 L: Aperture Length; W: Aperture Width; T: Stencil Thickness 5. PCB Footprint Guideline 5.1 Footprint DrawingTable 1: Typical Footprint Dimension X: Pad Width+0.05mm; Y: Pad Length+0.20mm; ZD Max: D+ PKG Tolerance+2(0.2); GD Min: D-2(Lmax)-2(0.05); D2th: GDmin-2(CpL=0.2) & Thermal Pad Open, 兩 Package (mm)PCB Footprint DimensionBody Lead Pad Width Pad LengthPitchZD Max GD Min ZE Max GE Min D2th E2th X YDFN 2*2 6 0.30 0.40 0.65 2.50 1.10 0.70 1.40 0.350.60 DFN 2*2 8 0.30 0.40 0.50 2.50 1.10 0.60 1.20 0.35 0.60 DFN 3*3 6 0.45 0.525 0.95 3.50 1.85 1.45 2.30 0.50 0.725 DFN 3*3 8 0.30 0.525 0.65 3.50 1.851.452.30 0.35 0.725 DFN 3*3 10 0.30 0.45 0.503.50 2.00 1.60 2.50 0.35 0.65 QFN 3*3 16 0.30 0.45 0.50 3.50 2.00 3.50 2.00 1.60 1.60 0.35 0.65 QFN 4*4 16 0.35 0.60 0.654.50 2.70 4.50 2.70 2.25 2.25 0.40 0.80 QFN 4*4 24 0.30 0.45 0.50 4.50 3.00 4.50 3.00 2.60 2.60 0.35 0.65 QFN 5*5 16 0.35 0.60 0.805.50 3.70 5.50 3.70 3.25 3.25 0.40 0.80 QFN 5*5 24 0.35 0.45 0.65 5.50 4.00 5.50 4.00 3.25 3.25 0.40 0.65 QFN 5*5 32 0.30 0.45 0.50 5.50 4.00 5.50 4.00 3.60 3.60 0.35 0.65 QFN 6*6 28 0.375 0.45 0.656.50 5.00 6.50 5.00 4.225 4.225 0.425 0.65 QFN 6*6 40 0.30 0.45 0.506.505.006.50 5.00 4.40 4.40 0.35 0.65Fig. 4: Typical QFN/ DFN FootprintDesign with PackageQ FN P ad5.2 Solder Mask DesignPCB 了 , PCB (Solder Mask), , 若 , , (Solder Mask Define: SMD). 若 , , (Non-solder Mask Defined)(Fig.5)Lead Non-Solder Mask Defined, 來 Thermal Pad Solder Mask Defined, 來5.3 Thermal Pad Via Design了 PCB ⾦ , , Thermal Pad . 參 : 1.2mm Pitch with Via Diameter of 0.34mm( / 料 Solder Wicking, 0.25mm(0.010”) via , 例0.34mm 1 略 0.25mm 洞)(Fig. 6)Fig. 5 Comparison between Solder Mask Defined Pad and Non-solder Mask Defined PadPadSolder Mask DefinedNon-solder Mask Defined5*5 Body6*6 Body0.34 mm Via DiameterFig. 6 Suggested Thermal Via LayoutSMT 連洞 Via Solder Wicking, Thermal Pad ⾏類塞 , 塞 :PCB 爐 , 路留爐 , 路防⽌表⾯錫膏流⼊孔內造成虛焊影響黏貼列塞來 Solder Wicking: Capped Via (Copper Layer Cover Via & Plugged Material) Plugged Via (Solder Mask Cover Via & Plugged Material) Tented Via (Solder Mask Cover Via)6. Re-flow ProfileAll of RichTek’s products are requested to meet the standard of Reflow Profile in theIPC/JEDEC J-STD-020C. (Fig.8)CopperCapped ViaPlugged ViaTented Via Fig. 7 Via Type7.0 Rework ProcessPCB ? ? ? PCB ? ? IC ? IR Re-flow ? Fig.8 IR-Re-flow Profile。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

QFN封装的组装和PCB布局指南前言双排或多排QFN封装是近似于芯片级塑封的封装,其基板上有铜引线框架。

底部上面裸露的芯片粘附焊盘会有效地将热量传递给PCB,并且通过下面的键合提供稳定的接地或通过导电芯片粘附材料形成电气连接。

双排或多排QFN封装的设计实现了柔性,并提高了在极高速操作频率下的电气性能。

双排或多排QFN封装采用有间隙的引线设计,这种设计可形成交错排列的引线布局。

内排交错0.5mm,就会使最大尺寸芯片实现紧凑致密的设计,同时,不会超过通常的0.5mm间距的SMT工艺的表面组装技术(SMT)的能力。

Actel公司提供的QFN封装有三种结构:QN180、QN132和QN108。

这些封装的印脚和外形是按照JEDEC MO-247标准:塑料四方无引线交叉排列的多排封装(增热任选)和按照JEDEC Design Guide 4.19:四方形无引线交叉排列的多排封装而实施的。

QFN封装概述图1和图2所示是通过同一平面上的芯片和线焊焊盘使这种封装的高度达到最小化。

图3说明了这种焊盘的结构。

在组装时,引线直接与板子连接,而不像塑料四方(PQ)或薄形四方(TQ)那样,在引线封装内留有一定间隙的高度以便分离。

此外,由于芯片焊盘直接与PCB连接,使得QFN封装具有极好的散热性。

由于QFN封装的有效和致密的设计,还会降低电子寄生效应。

表1所列是典型的可靠性数据。

表1 可靠性为了达到峰值性能,母板的设计必须合适,且对于封装的组装必须给予特别的构思。

就提高的温度、电气和板级性能而言,必须使用与板上热焊盘相对应的焊盘将封装上裸露的焊盘焊接到板上。

为了使板子能够实现有效的导热,PCB的热焊盘区域必须设置有导热通孔。

对内部一排引线和热焊盘之间的容差是有要求的,以便通过导通孔来布设内排信号的线路。

对容差量的要求取决于具体应用。

在设计PCB印脚时必须考虑到这一点,由于封装、PCB和板组装诸多方面的关联性,必须考虑到尺寸容差。

明显影响QFN封装在板上的组装和焊点质量的一些因素列在下面:‧覆盖于热焊盘区域的焊膏量;‧热焊盘周边和热焊盘区域的模板设计;‧导通孔的类型;‧板厚度;‧封装上的引线涂层;‧板上的表面涂层;‧焊膏类型;‧再流曲线。

这种应用提示:为开发适当的板设计和表面组装工艺提供了通用指南。

为了满足一些特别用户的表面组装实践和应用要求而优化工艺,需要进一步地进行潜心研发。

PCB焊盘设计指南这部分主要论述对于推荐的焊盘图形的逻辑依据在封装级和板级布局中的局限性。

三排QFN PCB焊盘设计(QN132和QN180)通常,热焊盘的尺寸至少应与裸芯片焊盘尺寸匹配。

由于导通孔所要求的容差,可能需将热焊盘尺寸降低到小于封装焊盘尺寸。

从板组装的角度来看,在板子热焊盘小于封装焊盘尺寸时没有发现问题。

热焊盘在小到焊盘尺寸的80%时,就会实现成功的组装,不会出现任何问题。

从热效率方面来看,只要板上的热焊盘至少与封装内的芯片尺寸相同,那么,效率损耗就最小。

假设板子设计规则是使用1/2盎司铜的标准四层板。

就可以用这些假设来确定导通孔间距的要求。

图5和图6给出了分析中所用的值。

详细内容请参见“附件1:PCB具体布局”的说明。

要特别注意板上用金属焊盘连接的印制线。

在这个封装的板级跌落和弯曲试验中观察到印制线有开裂的现象。

印制线开裂通常发生在金属焊盘周边的阻焊膜开口的边缘。

为了避免产生这种模式的缺陷,Actel公司建议阻焊膜边缘下面的印制线应比其它印制线宽些儿,见图4所示。

这取决于可靠性要求,印制线较宽的部位可能宽度需达到金属焊盘宽度的50-75%。

热焊盘导通孔设计双排和三排QFN封装的设计可以提供杰出的热性能。

而热焊盘可为PCB的上面提供可焊的表面(就焊接板上的封装芯片焊盘而言),需要导热通孔为内部和PCB底层提供导热通路,以便去除热量。

为了有效地将PCB上面的金属层的热量传递到内层或底层,导热通孔必须纳入热焊盘设计中。

导热通孔的数量应取决于应用、能耗和电气要求。

虽然,较多的导热通孔可以改善热性能,值得注意的一点是其额外的导热通孔不可能使性能得到明显的改善,会减少回报率。

基于分包商提供的信息,Actel公司建议将一系列间距为1.0mm-1.2mm,直径为0.3mm-0.33mm的导热通孔应用于设计中。

必须确定每种用途的操作环境和条件下的导通孔的数量。

导通孔的一个缺点是在再流焊接过程中焊料有使导通孔向下芯吸的倾向,这样的话,就降低了周边引线的焊料分离高度。

通过采用阻焊膜堵塞或摭蔽导通孔就可以避免这种现象的产生,而且这样还会使DAP和热焊盘之间的焊料层中产生空洞(图7a导通孔)。

因此,在空洞和分离高度之间必须采取一种折衷的方法,以便确定对导热通孔采取一种适当的处理方法。

虽然,并不是那么有效,但是,还可以通过使用导通孔和热焊盘区域的微过孔的混合技术使热传导到内层(图7b导通孔和盲微过孔的组合)。

阻焊膜的构思建议双排和三排QFN封装采用非焊料掩膜定义的(NSMD)焊盘,由于对铜蚀刻工艺的管控要比阻焊膜工艺更为苛刻,而且这种工艺可以改善焊点的可靠性。

对于中心的热焊盘,推荐使用阻焊膜定义(SMD)的结构。

板组装指南由于小焊盘表面积和仅依赖于印刷到PCB表面上的焊膏,为使双排和三排QFN 封装能够形成可靠的焊点,在操作中一定要谨慎。

由于封装底部的热焊盘较大及其接近于焊盘内边缘,所以使得结构进一步复杂化。

对于周边焊盘和热焊盘的模板设计和焊膏印刷需特别考虑。

由于公司与公司间采用的表面组装工艺不同,因此,建议认真地开发工艺。

“周边焊盘和热焊盘的模板设计”这一部分是基于Actel分包商在双排和三排QFN封装的表面组装的经验和提供的信息而提供了模板设计的一些指南。

周边焊盘和热焊盘的模板设计周边焊盘上最佳的、可靠的焊点的分离高度大约为50-70μm(2-3mil)。

模板是激光切割和电镀抛光的模板。

抛光可使模板壁光滑,还会使焊膏释放顺畅。

Actel公司建议要严格控制模板孔径容差,因为容差会明显地降低孔径尺寸。

通过对双排和三排QFN封装的板组装的研究说明,分离高度主要是由热焊盘焊膏的覆盖率决定。

周边焊盘的飘浮效应是小的,而且不是决定分离高度的主要因素。

由于分离高度下降,热焊盘上的焊膏不足还会使内排桥接,这一点也是肯定的。

为了实现适当的模板设计,决不能超过0.66的面积比和1.5的孔径的数据要求。

‧PCB的焊盘图形与QFN封装的焊盘比例应是1:1。

‧PCB的热焊盘设计应是焊膏覆盖率的75%,并使用一个开口(见图8所示)。

应选择开口的数据(D2'尺寸),如像,AH和AW=1.00±0.15mm。

开口之间的网厚度保持在0.200mm,使得助焊剂挥发物就有空间逃逸,这样的话,就可以减少孔洞。

模板厚度和焊膏建议0.5mm双排和三排QFN组件采用0.125mm厚的模板。

建议使用激光切割的经电镀抛光孔壁为不规则四边形的不锈钢模板,以改善焊膏的释放。

由于在再流后组件下面没有足够的空间,为此,Actel公司建议采用免清洗,类型3和类型4焊膏用于组装QFN封装。

还建议在再流过程中采用氮气吹扫。

再流曲线再流曲线和峰值温度对孔洞的形成有很大的影响。

Actel特此提出建议,用户要按照焊膏供货商推荐的再流曲线进行操作,因为这是为助焊剂成形专门制定的要求。

不过,有两个再流曲线(图9和图10)可以作为你在实际操作中最终曲线微调的参考。

组装工艺流程图11所示是在PCB上组装表面组装封装的通用工艺流程。

组装QFN可使用相同的工艺,而不需做任何变更。

在印刷后和再流后进行检测是很重要的,特别是在开发工艺过程中。

应采用2D或3D技术来检测焊膏的印刷量。

焊膏量大约为模板开孔体积的80%-90%,就可以实现良好的焊膏释放。

再流后,应对组装后的封装通过X射线照射进行检验,以便确认是否有孔洞、焊料球或其它缺陷存在。

还需要进行横剖面,以便确定填角焊缝形状和尺寸以及焊点分离高度。

返工指南由于QFN的焊点不是完全裸露在外的,所以,再次接触焊点是很难的。

对于封装下面的缺陷,必须将整个封装拆开才能进行返修。

由于QFN封装尺寸小,所以,QFN封装的返修是一个挑战。

在多数应用中,QFN都是组装在更小、更薄和更致密的PCB上,因此,给操作和加热带来了一定的难度,使其成为又一个挑战的领域。

在返修过程中的再流中,由于相邻组件也不可避免地受热,邻近的其它组件受热可能会使工艺进一步复杂化。

因为复杂程度取决于产品,所以,下面仅给出了返修QFN封装的指南和作为成功开发返修QFN封装工艺的一个起点。

返修工艺包括如下步骤:1. 拆除组件2. 焊盘清理3. 施加焊膏4. 贴装组件和焊接拆除组件拆除组件的第一步是对焊接到PCB板上的组件的焊点进行再流。

最理想的做法是,拆除组件的再流曲线应与焊接组件使用的再流曲线相同。

不过,只要完成再流焊,就可以降低液相线以上的时间。

在拆除组件过程中,Actel建议,应使用对流加热器从板子底部进行加热,并在组件上面使用热风。

在对组件区域进行导热过程中应使用特制的吸嘴。

应尽量使相邻组件少一些受热。

还应避免过分地气流,由于气流过大会使CSP扭曲。

空气流动速率为每分钟15-20升,就是一个好的起点。

一旦焊点再流,在再流到冷却的转换过程中,就会自动实施真空抬起(lift-off)。

由于组件尺寸小,所以,真空压力应保持在每汞柱15in以下。

如果并不是所有的焊点都被再流的话,这样就可以确保组件不会抬起,从而避免了焊盘抬起。

焊盘清理拆除组件后,应对返修区域进行适当地清理。

最好是使用刀片型导热工具和编织带式除焊相结合的方法。

刀片的宽度应与印脚的最大宽度相匹配,烘烤温度应低到不会给电路板带来任意损坏为好。

一旦去除了残余焊料,就应用溶剂清理焊盘。

通常溶剂应使用专为原组装厂家提供的焊膏类型,并应按照焊膏制造厂家的建议进行操作。

焊膏印刷因为这种封装的尺寸小,且间距小,QFN的焊膏沉积要特别的小心。

如果使用专为此种组件研制的小型模板,就可以实现均匀一致、精确的焊膏沉积。

模板的孔径应与焊盘在50X-100X的放大倍率下对位。

然后,将模板降落在PCB上,使用小的金属刮板将焊膏挤压到板上。

还可使用小型模板将焊膏印刷到QFN封装的焊盘上。

应使用厚度为125μm和开口尺寸及形状与封装焊盘相同的模板。

由于QFN分离高度低没有给清洗留下足够的空间,所以,应使用免清洗助焊剂。

组件贴装和焊接由于QFN封装的质量小,所以,可望QFN封装具有极优越的自对位能力。

这种类型封装的贴装类似于BGA的贴装。

由于焊盘是在封装的下面,应用裂隙(split-beam)光系统来实施组件与母板的对位。

这样就会在与之相匹配的印脚上形成重的焊盘图像,并且有助于适当的对位。

同样,应在50X-100X放大倍率下进行对位。

贴装设备应具有对X、Y和旋转轴进行微调的能力。