数字电路设计实验-简易密码锁

数字电路课程设计(密码锁)

数字电路课程设计设计报告课题名称:密码锁设计成员1:设计成员2:设计成员3:密码锁一、目录1、设计项目综述 (2)2、设计方案及分析 (3)2.1设计方案 (3)2.2设计分析 (4)2.3方案优缺点 (4)3、电路原理分析 (5)3.1模块1:八进制优先编码器74ls148 (5)3.2模块2:4位双稳锁存器74LS75 (6)3.3模块3:4位数字比较器74LS85 (8)3.4模块4:可预置bcd计数器74LS160 (9)3.5 总图 (14)4、总结 (16)4.1设计中遇到的问题及解决方法 (17)4.2设计方案中需要改进的地方 (17)4.3这次设计中的收获和教训 (17)二、设计项目综述:1、可以预置1位十进制数密码,并保存密码。

2、开锁时,输入正确密码,按开锁键,锁打开。

3、当输入密码时,数码管显示相应的输入数字。

密码输入错误时计数一次,当输入错误密码连续达到四次,拒绝再输入密码。

需用复位键将其还原才能再次输入。

4、输入密码时,数码管8显示密码的数值。

拒绝输入密码时,只显示0。

按开锁键时,数码管5显示密码输入错误的次数;当错误次数连续少于4次以下时,则当输入密码正确时数码管5清“0”。

5、开锁指示灯亮表示锁已经打开。

三、设计方案及分析1、设计方案根据以上密码锁的设计任务,我们拟定的方案可以简略的如以下框图所示:2、方案分析(1)密码输入:由于要求通过每按一个输入键时直接显示为对应的十进制数密码,所以需要将二进制数转换为对应的十进制数。

根据前面这个要求,我们有两个选择74ls147和74ls148。

74ls147与74ls148比较,74ls148比74ls147多一个功能端。

使用74ls148可以实现输入四次错误自动锁定。

虽74ls148总的输入键只有8个,使用两块74ls148,并他们通过级联可以解决0~9输入。

当多过输入端同时出现时,只对其中优先权最高的一个进行编码,这个编码就是我们要的对应的十进制数。

数电实验报告电子密码锁设计

数电实验报告电子密码锁设计

实验报告

实验十四电子密码锁设计与实现

3.4.1 实验目的与设计要求

目的:(1)学习4位数值比较器CC14585和74LS85的功能。

(2)掌握电子密码锁的工作原理及综合实验技能。

要求:(1)电路可以由主持人预置16种不同的开锁密码,并能够更换。

(2)当输入和预置开锁密码相同时,发出开锁信号(LED 显示)。

(3)如果连续三次输入错误密码即产生报警信号。

报警信号用声光报警电路指示(蜂鸣器等)。

(4)具备能够取消报警状态的功能。

3.4.2 实验仪器与器件

直流稳压电源一台;数字实验箱一个;计算机一台。

74LS75锁存器、74LS00、74LS10、74LS20、4位数值比较器CC14585或74LS85。

3.4.3 实验原理框图

设计思路:用74LS194四位寄存器作锁存电路,74LS75四位锁密

码

预

置

输

入锁存电路密码比较电路密码锁存装置计数器确认按钮

报警电路开锁电路确认按钮

密码输入

存器作密码锁存装置,4位数值比较器4585作密码比较电路,74LS160作计数器。

当连续三次输入错误密码即产生报警信号同时锁住,此时再输入正确密码不产生开锁信号。

仿真图如下:。

简易14位数字密码锁控制电路设计实验报告

简易14位数字密码锁控制电路设计实验报告实验目的:本实验旨在掌握基本的数字锁控制电路设计方法,通过具体实验操作,使学生对数字锁的原理、控制电路以及数字电路的设计方法等有更加深入的了解和认识。

实验器材:1.数字集成电路:CD4017B、CD4069UB、CD4073B、SN74LS08N;2.10K电位器、电容、电阻器、LED灯等。

实验原理:密码锁控制电路是由数字集成电路CD4017B、CD4069UB、CD4073B及SN74LS08N组成的。

其中CD4017B为计数器,CD4069UB、CD4073B和SN74LS08N为逻辑门电路,用于实现密码锁控制功能。

CD4017B为数字集成电路,它是一个10位二进制计数器,可以用于电子时钟、计时器、频率分频器等电路中。

它具有高速、低功耗、可升级性等优点,被广泛地应用于数字电路中。

CD4069UB、CD4073B和SN74LS08N均为逻辑门电路,主要用来实现与门、或门、非门等逻辑运算。

在本实验中,CD4017B接在控制端,用于实现计数和循环控制功能;CD4069UB、CD4073B和SN74LS08N三个逻辑门电路用于实现锁定、解锁功能。

实验步骤:1. 选择合适的元器件,按照电路图连接电路。

将电路连接好后,注意检查电路连接是否正确、元器件是否插紧等。

2. 按照实验要求进行编程。

将编程程序设置为14位数字密码,具体程序如下:3. 按照要求测试实验电路。

输入正确的密码,即可实现锁定或解锁功能。

实验结果:通过实验操作,我们成功地设计出一款14位数字密码锁控制电路,其操作流程为输入密码-验证密码-锁定或解锁。

通过实验可以看出,密码锁控制电路设计简单,操作方便,具有广泛的应用前景。

实验分析:数字密码锁是一种常见的电子密码产品,可以用于保护个人财产、资料等,在家庭、宾馆等场所得到了广泛的应用。

基于数字集成电路和逻辑门电路设计数字密码锁控制电路,具有操作简单、易于维护和升级等优点,被广泛地应用于数字电路中。

简易位数字密码锁控制电路设计实验报告

简易位数字密码锁控制电路设计实验报告Coca-cola standardization office【ZZ5AB-ZZSYT-ZZ2C-ZZ682T-目录一、前言 (2)二、课设任务 (2)三、方案设计、原理分析 (2)四、译码电路设计 (8)五、报警信号产生器 (10)六、调试及结果..........................................(12)七、体会 (13)一、前言本次课程设计的基本任务是着重提高学生在EDA知识学习与应用方面的实践技能。

学生通过电路设计安装、调试、整理资料等环节,初步掌握工程设计方法和组织实践的基本技能,逐步熟悉开展科学实践的程序和方法。

EDA技术是电子信息类专业的一门新兴学科,是现代电子产品设计的核心,其任务是掌握在系统可编程逻辑器件及其应用设计技术,为电子产品开发研制打下坚实基础。

本课程设计对学生有如下要求:根据设计任务和指标,初步电路;通过调查研究,设计计算,确定电路方案;选择元器件,在计算机上连好线路,独立进行试验,并通过调试、仿真、改进方案;分析实验结果,写出设计总结报告:学会自己分析,找出解决问题方法;对设计中遇到的问题,能独立思考、查阅资料,寻找答案。

二、课设任务1、14位数字密码分成高7位(DH6…DH0)和低7位(DL6…DL0),用数字逻辑开关预置,输出信号out为1表示开锁,否则关闭。

2、14位数字密码分时操作,先预置高7位,然后再置入低7位。

3、要求电路工作可靠,保密性强,开锁出错立即报警。

4、利用MAX plus2 软件进行设计、编译,并在FPGA芯片上实现。

5、简易14位数字密码锁模块的框图如下:三、方案设计、原理分析首先我是一班的三号,所以我的密码时0100010 0000011。

我所做的设计是先把高七位输入锁存,然后在输入低七位,最后判断密码是否正确,密码正确就开锁,密码错误就报警。

数字密码锁控制电路的组成部分:YMQ 模块,1、IC9A的设计设计要求14位数字密码分时操作,先预置高七位0100010,而后置低七位0000011,首先可以使用寄存器将高七位存起来,而后与低七位一起进行译码,如果密码正确,输出OUT2为1,否则为0.2、数字密码锁控制电路原理图:输入密码正确时波形图输入错误密码时波形图数字密码锁控制电路的VHDL语言编程原理分析:当CLR为0时,寄存器与D触发器被清零,此时在A……G输入高七位密码0100010,用CLK给一个脉冲,由于此时输出端Q为0,经过一个非门为1,与CLK一起经过一个与门,送入寄存器CLK 端,产生上升沿;而经过非门的CLR为1,送入寄存器中,将高七位通过寄存器送入译码器的高七位中。

数字逻辑电路实验--基于有限状态机的密码锁

数电实验三报告姓名:xxx班级:xxx 学号:xxxx实验:基于有限状态机的密码锁一、实验目的学习如何通过Verilog HDL 编程,利用Basys3板上的开关控制七段数码管实现四位密码锁。

二、实验要求使用有限状态机设计一个 4 位密码锁。

利用 Basys3 板上的滑动开关 sw[0]到sw[9]分别代表 0‐9 十个数字,依次输入 4 位不重复的密码。

如果密码输入顺序与设计设置的一致,则显示大写字母P,否则显示大写字母F。

注意,即使密码输入错误,也必须在输入完整的 4 位密码输入,才能显示大写字母 F。

三、实验设计及内容1.基础版实验代码module doorlock(input CLK,input clr,input [9:0] sw,output reg [10:0] display_out);reg[3:0] present_state,next_state;parameter S0=4'b0000,S1=4'b0001,S2=4'b0010,S3=4'b0011,S4=4'b0100,E1=4'b0101,E2=4'b0110,E3=4'b0111,E4=4'b1000;reg [29:0] count;reg [9:0] keys=0;always @(posedge CLK or posedge clr)beginif (clr) count<=0;else count<=count+1;endassign clk_3=count[24];// ~3Hzalways @(posedge clk_3 or posedge clr) // STATE TRANSITIONbeginif (keys!=sw) keys <= sw;if (clr) present_state <= S0;else present_state <= next_state;end// Demo for Finite State Machine// the correct password is 0->1->2->3 (Switch sw[0]->sw[1]->sw[2]->sw[3] in order. always @(*)begincase (present_state)S0: beginif (~|keys[9:0]) next_state <=S0; // no key pressedelse if (keys[2]) next_state <=S1; // first valid key pressedelse next_state <=E1; // first invalid key pressedendS1: beginif (~|keys[9:3]&&~|keys[1:0]) next_state <=S1; // no key pressedelse if (keys[1]) next_state <=S2;// second valid key pressedelse next_state <=E2;// second invalid key pressedendS2: beginif (~|keys[9:3]&&~|keys[0]) next_state <=S2; // no key pressedelse if (keys[7]) next_state <=S3; // third valid key pressedelse next_state <=E3;// third invalid key pressedendS3: beginif (~|keys[9:8]&&~|keys[6:3]&&~|keys[0]) next_state <=S3; // no key pressedelse if (keys[3]) next_state <=S4;// fourth vaild key pressedelse next_state <=E4;// fourth invalid key pressedendS4: beginif (~|keys[9:8]&&~|keys[6:4]&&~|keys[0]) next_state <=S4; // no keypressedelse next_state <=E1; // fifth key pressed, but ignored *** endE1:beginif (keys!=sw) next_state <=E2; // second invalid key pressedelse next_state <=E1; // no key pressedendE2:beginif (keys!=sw) next_state <=E3; // third invalid key pressedelse next_state <=E2; // no key pressedendE3:beginif (keys!=sw) next_state <=E4; // fourth invalid key pressedelse next_state <=E3; // no key pressedendE4: next_state <=E4; // the additional keys are ALL ignored ***default: next_state <=S0;endcaseendalways @(*) // indicate the number of inputs and display the tag begincase(present_state)S4: display_out<=11'b0111_0011000;// P in left-most segmentE4: display_out<=11'b1110_0111000;// F in right-most segmentS0: display_out<=11'b1001_0011100;// oo in the middle segmentsS1,E1: display_out<=11'b1001_0111111;// confirm first inputS2,E2: display_out<=11'b1001_0011111;// confirm second inputS3,E3: display_out<=11'b1001_0011110;// confirm third inputdefault:display_out<=11'b1111_1111111; // no displayendcaseendendmodule2.进阶版实验代码module doorlock2(input CLK,input clr,input [9:0] sw,output reg [10:0] display_out);reg[3:0] present_state,next_state;reg [19:0]count1=0;reg [2:0] sel=0;parameter S0= 4'b0000,S1=4'b0001,S2=4'b0010,S3=4'b0011,S4=4'b0100, S01=4'b1001,S02=4'b1010,S03=4'b1011,E1=4'b0101,E2=4'b0110,E3=4'b0111,E4=4'b1000;parameter T1MS=50000,T2MS=20000_0000;reg [29:0] count;reg [32:0] count2=0;reg [9:0] keys=0;reg flag;always @(posedge CLK or posedge clr)beginif (clr)begincount<=0;endelse count<=count+1;endwire clk_3;assign clk_3=count[24];// ~3Hzalways @(posedge clk_3 or posedge clr) // STATE TRANSITIONbeginif (keys!=sw) keys <= sw;if (clr) present_state <= S0;else present_state <= next_state;endalways@(posedge CLK or posedge clr)beginif(present_state == S4)beginif(count2<T2MS)begincount2<=count2+1;flag<=1'b0;endelsebeginflag<=1'b1;endendif(clr) count2<=0;end// Demo for Finite State Machine// the correct password is 0->1->2->3 (Switch sw[0]->sw[1]->sw[2]->sw[3] in order. always @(*)begincase (present_state)S0: beginif (~|keys[9:0]) next_state <=S0; // no key pressedelse if (keys[2]) next_state <=S1; // first valid key pressedelse next_state <=E1; // first invalid key pressedendS1: beginif (~|keys[9:3]&&~|keys[1:0]) next_state <=S1; // no key pressed//else if (!sw) next_state <=S01;// second valid key pressedelse if(keys[1]&&keys[2]) next_state<=S2;else next_state <=E2;// second invalid key pressedendS01:beginif(!sw) next_state<=S01;else if(sw[2]) next_state<=S2;else next_state<=E2;endS2: beginif (~|keys[9:3]&&~|keys[0]) next_state <=S2; // no key pressed//else if (!sw) next_state <=S02; // third valid key pressedelse if (keys[2]&&keys[1]&&keys[3]) next_state <=S3;else next_state<=E3;// third invalid key pressedendS02: beginif(!sw) next_state<=S02;else if(sw[1]) next_state<=S3;else next_state<=E3;endS3: beginif (keys[1]&&keys[2]&&keys[3]) next_state <=S3; // no key pressed else if (!sw[3]) next_state <=S03;// fourth vaild key pressedelse next_state <=E4;// fourth invalid key pressedendS03:beginif(~|keys[9:3]&&~|keys[0]) next_state<=S03;else if(keys[3]) next_state<=S4;else next_state<=E4;endS4: beginif (~|keys[9:4]&&~|keys[0]) next_state <=S4; // no key pressedelse next_state <=E1; // fifth key pressed, but ignored *** endE1:beginif (keys!=sw) next_state <=E2; // second invalid key pressedelse next_state <=E1; // no key pressedendE2:beginif (keys!=sw) next_state <=E3; // third invalid key pressedelse next_state <=E2; // no key pressedendE3:beginif (keys!=sw) next_state <=E4; // fourth invalid key pressedelse next_state <=E3; // no key pressedendE4: next_state <=E4; // the additional keys are ALL ignored ***default: next_state <=S0;endcaseendalways@(posedge CLK)begincount1<=count1+1;if(count1==T1MS)begincount1<=0;sel<=sel+1;if(sel==4)sel<=0;endendalways @(posedge CLK) // indicate the number of inputs and display the tagbegincase(present_state)S0: begincase(sel)0:display_out<=11'b0111_0101000;1:display_out<=11'b1011_0110000;2:display_out<=11'b1101_1000100;3:display_out<=11'b1110_0110110;default:display_out<=11'b1111_1111111;endcaseendS1: begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1110111;2:display_out<=11'b1101_1110111;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseend // confirm first inputS2: begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_1110111;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseend // confirm second inputS3: begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_0000110;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseend // confirm third inputS4: beginif(!flag)begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_0000110;3:display_out<=11'b1110_0000110;default:display_out<=11'b1111_1111111;endcaseendelse display_out<= 11'b0111_0011000 ;end // P in left-most segmentS01:begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1110111;2:display_out<=11'b1101_1110111;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseendS02:begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_1110111;3:display_out<=11'b1110_1110111; default:display_out<=11'b1111_1111111;endcaseendS03: begincase(sel)0:display_out<=11'b0111_0010010;1:display_out<=11'b1011_1001111;2:display_out<=11'b1101_0000110;3:display_out<=11'b1110_1110111;default:display_out<=11'b1111_1111111;endcaseendE1: display_out<=11'b0111_0111000;E2: display_out<=11'b1011_0111000;E3: display_out<=11'b1101_0111000;E4: display_out<=11'b1110_0111000;// F in right-most segment default:display_out<=11'b1111_1111111; // no displayendcaseendendmodule约束文件代码:## Clock signalset_property PACKAGE_PIN W5 [get_ports CLK]set_property IOSTANDARD LVCMOS33 [get_ports CLK]## Switchesset_property PACKAGE_PIN V17 [get_ports {sw[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]set_property PACKAGE_PIN V16 [get_ports {sw[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]set_property PACKAGE_PIN W16 [get_ports {sw[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]set_property PACKAGE_PIN W17 [get_ports {sw[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]set_property PACKAGE_PIN W15 [get_ports {sw[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]set_property PACKAGE_PIN V15 [get_ports {sw[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]set_property PACKAGE_PIN W14 [get_ports {sw[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]set_property PACKAGE_PIN W13 [get_ports {sw[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}]set_property PACKAGE_PIN V2 [get_ports {sw[8]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}]set_property PACKAGE_PIN T3 [get_ports {sw[9]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}]## sw[15]set_property PACKAGE_PIN R2 [get_ports {clr}]set_property IOSTANDARD LVCMOS33 [get_ports {clr}]## 7-seg displayset_property PACKAGE_PIN W4 [get_ports {display_out[10]}]set_property PACKAGE_PIN V4 [get_ports {display_out[9]}]set_property PACKAGE_PIN U4 [get_ports {display_out[8]}]set_property PACKAGE_PIN U2 [get_ports {display_out[7]}]set_property PACKAGE_PIN W7 [get_ports {display_out[6]}]set_property PACKAGE_PIN W6 [get_ports {display_out[5]}]set_property PACKAGE_PIN U8 [get_ports {display_out[4]}]set_property PACKAGE_PIN V8 [get_ports {display_out[3]}]set_property PACKAGE_PIN U5 [get_ports {display_out[2]}]set_property PACKAGE_PIN V5 [get_ports {display_out[1]}]set_property PACKAGE_PIN U7 [get_ports {display_out[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[9]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[8]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[7]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[6]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[5]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[4]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {display_out[10]}]四、实验结果1基础结果图2.进阶结果图进阶实验成品效果说明:进阶视频演示:正确示范:密码输入错误示范:五、实验总结1.通过本次实验了解了时钟信号的作用原理以及对时序电路的控制机理。

数字电路设计实验-简易密码锁

数字电路设计实验报告——简易密码锁学院:班级:学号:姓名:目录●任务要求●系统设计✓设计思路✓总体框图✓分块设计●波形仿真及波形分析●源代码●功能分析●故障分析及问题解决●总结及结论●任务要求设计并实现一个数字密码锁,密码锁有四位数字密码和一个确认开锁按键,密码输入正确,密码锁打开,密码输入错误进行警示。

基本要求:1、密码设置:通过键盘进行4 位数字密码设定输入,在数码管上显示所输入数字。

通过密码设置确定键(BTN 键)进行锁定。

2、开锁:在闭锁状态下,可以输入密码开锁,且每输入一位密码,在数码管上显示“-”,提示已输入密码的位数。

输入四位核对密码后,按“开锁”键,若密码正确则系统开锁,若密码错误系统仍然处于闭锁状态,并用蜂鸣器或led 闪烁报警。

3、在开锁状态下,可以通过密码复位键(BTN 键)来清除密码,恢复初始密码“0000”。

闭锁状态下不能清除密码。

4、用点阵显示开锁和闭锁状态。

提高要求:1、输入密码数字由右向左依次显示,即:每输入一数字显示在最右边的数码管上,同时将先前输入的所有数字向左移动一位。

2、密码锁的密码位数(4~6 位)可调。

3、自拟其它功能。

●系统设计设计思路将电子密码锁系统分为三个部分来进行设计,数字密码输入部分、密码锁控制电路和密码锁显示电路。

密码锁输入电路包括时序产生电路,键盘扫描电路,键盘译码电路等,将用户手动输入的相关密码信息转换为软件所能识别的编码,作为整个电路的输入。

密码锁控制电路包括相应的数据存储电路,密码核对电路,能够进行数值的比较,进行电路解锁,开锁,密码的重新设置等。

密码锁显示电路包括将待显示数据的BCD 码转换成数码管的七段显示驱动编码,密码锁在相应的状态下的点阵输出以及蜂鸣器的报警输出。

总体框图按复位键 键入初始密码0000 密码错误密码正确 按确认键 按复位键按确认键密码锁显示电路 密码锁控制电路 数码管显示报警电路密码更改与密码设计电路键入状态闭锁状态开锁状态 报警状态分块设计✓键盘扫描电路首先,向列扫描地址逐列输出低电平,然后从行码地址读回,如果有键摁下,则相应行的值应为低,如果没有按键按下,由于上拉的作用,行码为高。

密码锁文档

数字电路实验综合设计二

一.实验名称:设计一个四位密码锁。

二.实验要求:设计一个密码锁,假如有四位密码输入,同时还需使用钥匙,如果密码和钥匙都正确,则密码锁打开,输出端Z为高电平,如果钥匙正确,而密码错误,这则输出端L为高电平同时报警。

根据组合电路的设计过程,设计电路,设计的电路要求符合客观实际的要求,用与非门来实现。

三.设计步骤:

1.设ABCD=1111为初设密码。

如果钥匙错误,则不管密码是否正确都将无法打开锁,所以将钥匙E设为使能端。

如果钥匙正确E=1,密码正确ABCD=1111,则开锁Z=1.

如果钥匙正确E=1,密码错误,则输出响铃L=1.

如果钥匙和密码都不正确,则Z=0,L=0.

2.根据以上可以作出真值表:

3.从上图真值表很容易得出其开锁端Z和报警端L的逻辑表达式如下:

4.根据逻辑表达式可以设计出逻辑电路图如下:(用与非门实现)

5.功能仿真:

(1)当钥匙错误时,不管你输入的密码是否正确。

两灯都是低电平,都没有反应。

仿真图如上图。

(2)当钥匙正确,密码错误时,D2变亮(即输出为高电平,且报警)。

(3)当钥匙正确,密码也正确时,D1变亮(即输出高电平,开锁成功)。

仿真图如下:

6.综上就是设计过程,经过仿真也达到要求。

不过我的设计中也许还有许多不足之处,希望老师查阅后给出意见。

谢谢老师!。

简易密码锁设计实验报告(一)

简易密码锁设计实验报告(一)简易密码锁设计实验报告研究背景在当前的社会中,密码锁已经广泛应用于各种领域,如个人家庭、办公场所、银行等。

密码锁在保障安全的同时,也带来了便捷。

因此,设计一款简易密码锁具有重要意义。

实验目的本次实验旨在设计一款简易密码锁,能够通过输入正确的密码从而打开锁,同时能够保护用户的安全。

实验步骤1.确定锁的锁舌位置和大小,确定锁的存储方式。

2.选择合适的电子元件,如单片机、键盘、LED灯等。

3.设计程序流程,完成程序并进行调试。

4.进行实验,并测试相关数据。

5.对实验结果进行分析,总结实验过程中的问题并提出改进方案。

实验结果及分析经过一段时间的实验,我们设计出了一款简易密码锁。

该密码锁通过输入正确的密码可以打开锁,密码为“123456”。

在打开锁的过程中,如果输入错误的密码,则锁将不会打开,并提示密码错误。

同时,该密码锁还具有防止暴力破解的功能,在输入密码错误达到一定次数时,将自动锁死。

在实验过程中,我们发现了一些问题,如电路连线不够稳定、程序层次不够清晰等。

针对这些问题,我们进行了相应的改进,在稳定电路连线的同时,也简化了程序层次,提高了密码锁的使用体验。

结论通过本次实验,我们成功地设计出了一款简易密码锁,并成功地实现了输入正确密码可以打开锁的功能。

在实验过程中,我们遇到了一些问题,但经过不断地实验和调整,最终得到了一个较为完善的版本。

参考文献无。

实验心得通过本次实验,我进一步了解了密码锁的设计和工作原理。

在实验过程中,我采用科学严谨的方法去解决问题,例如测试数据、重新设计程序以及频繁的测试与优化。

这个过程让我深深地体会到了科学实验具有的重要性,只有不断地实验、总结、优化,才能得到一个经得起实验检验的好结果。

同时,在实验过程中我还学会了合理地进行电路的布线以及如何选取合适的元件,这些都是我在日后实际工作中所必备的技能。

在实验过程中,我还发现设计中的细节问题常常决定一个产品的品质,在以后的工作中,我会更加注重产品的细节设计。

简易位数字密码锁控制电路设计实验报告

简易位数字密码锁控制电路设计实验报告目录一、前言 (2)二、课设任务 (2)三、方案设计、原理分析 (2)四、译码电路设计 (8)五、报警信号产生器 (10)六、调试及结果 (12)七、体会 (13)一、前言本次课程设计的基本任务是着重提高学生在EDA知识学习与应用方面的实践技能。

学生通过电路设计安装、调试、整理资料等环节,初步掌握工程设计方法和组织实践的基本技能,逐步熟悉开展科学实践的程序和方法。

EDA技术是电子信息类专业的一门新兴学科,是现代电子产品设计的核心,其任务是掌握在系统可编程逻辑器件及其应用设计技术,为电子产品开发研制打下坚实基础。

本课程设计对学生有如下要求:根据设计任务和指标,初步电路;通过调查研究,设计计算,确定电路方案;选择元器件,在计算机上连好线路,独立进行试验,并通过调试、仿真、改进方案;分析实验结果,写出设计总结报告:学会自己分析,找出解决问题方法;对设计中遇到的问题,能独立思考、查阅资料,寻找答案。

二、课设任务1、14位数字密码分成高7位(DH6…DH0)和低7位(DL6…DL0),用数字逻辑开关预置,输出信号out为1表示开锁,否则关闭。

2、14位数字密码分时操作,先预置高7位,然后再置入低7位。

3、要求电路工作可靠,保密性强,开锁出错立即报警。

4、利用MAX plus2 软件进行设计、编译,并在FPGA芯片上实现。

5、简易14位数字密码锁模块的框图如下:三、方案设计、原理分析首先我是一班的三号,所以我的密码时0100010 0000011。

我所做的设计是先把高七位输入锁存,然后在输入低七位,最后判断密码是否正确,密码正确就开锁,密码错误就报警。

数字密码锁控制电路的组成部分:YMQ模块,1、IC9A的设计设计要求14位数字密码分时操作,先预置高七位0100010,而后置低七位0000011,首先可以使用寄存器将高七位存起来,而后与低七位一起进行译码,如果密码正确,输出OUT2为1,否则为0.2、数字密码锁控制电路原理图:输入密码正确时波形图输入错误密码时波形图数字密码锁控制电路的VHDL语言编程原理分析:当CLR为0时,寄存器与D触发器被清零,此时在A……G输入高七位密码0100010,用CLK给一个脉冲,由于此时输出端Q为0,经过一个非门为1,与CLK一起经过一个与门,送入寄存器CLK 端,产生上升沿;而经过非门的CLR为1,送入寄存器中,将高七位通过寄存器送入译码器的高七位中。

利用数字电路实现电子密码锁-毕业设计

利用数字电路实现电子密码锁学生:XXX 指导老师:XXX内容摘要:本数字密码锁采用单片机AT89S52为主控芯片,由EEPROM存储密码。

硬件部分包括主控制系统、人机交互界面以及输出系统三大部分。

主控制系统中主控制芯片使用了AT89S52单片机,该单片机性能优良,能满足一般的普通应用;EEPROM采用AT24C02芯片,掉电后可以存储密码,从而保证了系统的安全性。

人机交互通道部分采用了4×4矩阵键盘输入以及LCD1602标准字符型液晶显示。

输出系统部分包括驱动开锁电路和报警电路;其中,在本系统设计中,驱动开锁电路用发光二极管表示,而报警电路则使用蜂鸣器。

本系统中使用的AT24C02芯片是一个带有I2C总线接口的EEPROM存储器。

I2C总线是一种双向二线制总线,它的结构简单,可靠性和抗干扰性能好。

I2C总线结构很简单,只有两条线,包括一条数据线(SDA)和一条串行时钟线(SCL)。

具有I2C接口的器件可以通过这两根线接到总线上,进行相互之间的信息传递。

本数字密码锁的功能为:密码位数为8位,可选值为0~9,从而保证足够的锁体强度;用户可以自行设定和修改密码;防止密码被盗,输入密码错误次数超过3次则报警;友好的人机界面;输入正确的密码后,驱动开锁电路。

软件部分应用单片机C语言实现了本设计的全部控制功能。

C语言编译方便,易读性好,且移植性方便,能够满足实现本系统的功能要求。

在设计过程中,给出了本系统C语言编程的原理和流程图。

本数字密码锁系统稳定性好,设计人性化,由于使用单片机控制并有记忆模块,功能齐全可靠,并有很好的扩展性,而且成本低廉,具有良好的发展前景。

关键词:数字密码锁 AT24C02芯片安全性Electronic combination lockAbstract:Using the digital circuit realize electronic combination lock This digital locks USES the monolithic integrated circuit AT89S52 as the controller chip, by EEPROM memory password. Hardware including master control system, man-machine interface and output system of three.The Lord control system used in the control chip AT89S52 SCM, this single chip good performance, can satisfy the general common application; The AT24C02 chip EEPROM, after power off can be stored password, so as to ensure the security of the system. Man-machine interactive channel part adopts the 4 x 4 matrix keyboard input and LCD1602 standard character type LCD display. The output of system including drive circuit and alarm lock circuit; Which, in the system design, drive the lock circuit using light-emitting diodes said, and alarm circuit is using a buzzer.The system used AT24C02 chip is a with the I2C bus interface EEPROM memory. The I2C bus is a two-way two wire bus, its simple structure, reliability and anti-interference capability. The I2C bus structure is simple, only two lines, including a data line (SDA) and a serial clock line (SCL). Has the I2C devices through this interface to two lines on the bus, the mutual information transfer.This digital locks function for: password digits for eight, optional value is 0 ~ 9, so as to ensure enough lock body strength; The user can set and modify the password; To prevent the password is stolen, the input password mistake number more than three times the alarm; Friendly human-machine interface; To enter the correct password, drive the lock circuit.Application software of single chip microcomputer C language realized this design of all control function. C compiler convenient, easy to read the gender is good, and easy portability, and can meet the requirement of system function realization. In the design process are given, and the system of the C programming language principle and flow chart.This digital locks system stability, humanized design, because use asingle-chip microcomputer control and a memory module, complete function and reliable, and have a good scalability, and the cost is low, have good development prospect.Keywords: Electronic combination lock AT24C02 chip safety目录前言 (1)1 系统的硬件设计 (2)1.1 硬件的总体结构和原理 (2)1.1.1 硬件系统的总体结构图 (2)1.1.2 硬件系统组成 (2)1.1.3 系统的可能性分析 (3)1.2 单片机AT89S51简介 (4)1.2.1 主要性能 (4)1.2.2 引脚功能描述 (5)1.3 AT24C02简介 (7)1.3.1 功能描述 (7)1.3.2 管脚描述 (7)1.3.3 I2C总线协议 (8)1.4 LCD1602介绍 (8)1.4.1 引脚描述 (9)1.4.2 LCDI602控制指令 (9)1.4.3 LCDI602读写控制时序 (11)1.5 4×4矩阵键盘 (11)1.6 复位电路 (12)1.7 振荡电路 (12)1.8 发光二极管LED电路 (13)1.9 报警电路 (13)1.10 电源输入电路 (14)1.11 使用到的元器件列表 (15)2 软件程序设计 (15)2.1 编译器Keil uVision2简介 (16)2.2 软件总设计流程图 (16)2.3 具体功能软件实现 (17)2.3.1 4×4矩阵键盘扫描程序 (17)2.3.2 显示程序 (19)2.3.3 时钟运行子程序 (19)2.3.4 时钟时、分修改子程序 (20)2.3.5 掉电存储服务程序 (21)2.3.7 密码修改子程序 (23)3 结束语 (24)附录1:PCB原理图 (26)附录2:仿真原理图 (27)附录3:单片机硬件实物图 (28)参考文献 (29)利用数字电路实现电子密码锁前言随着社会物质财富的日益增长,安全防盗已成为社会问题。

简易电子密码锁课程设计

简易电子密码锁课程设计一、课程目标知识目标:1. 学生能理解电子密码锁的基本原理,掌握其组成结构和功能。

2. 学生能掌握二进制计数原理及其在电子密码锁中的应用。

3. 学生能了解简易电子密码锁的电路设计与搭建。

技能目标:1. 学生能够运用所学知识,设计并搭建一个简易的电子密码锁。

2. 学生能够运用二进制计数原理,进行密码的组合与破解。

3. 学生能够通过实际操作,培养动手能力和团队协作能力。

情感态度价值观目标:1. 学生能够培养对电子技术的兴趣,激发创新意识和探索精神。

2. 学生能够认识到科技在生活中的应用,提高对科学技术的重视程度。

3. 学生能够在团队协作中,培养沟通能力、责任感和合作精神。

课程性质:本课程为实践性课程,结合电子技术与实际操作,培养学生动手实践能力和创新能力。

学生特点:六年级学生对电子技术有一定的基础,具备初步的动手能力和探究精神。

教学要求:教师应注重理论与实践相结合,引导学生通过实际操作,掌握电子密码锁的相关知识,提高学生的实践能力和创新能力。

在教学过程中,关注学生的个体差异,鼓励学生积极参与,培养团队合作精神。

通过课程目标的分解,使学生在学习过程中达到预期的学习成果。

二、教学内容1. 电子密码锁原理:介绍电子密码锁的基本原理,包括密码的设置与识别、锁的开关控制等。

- 相关教材章节:第四章第二节《电子锁的原理与应用》2. 二进制计数原理:讲解二进制计数的基本方法,及其在电子密码锁中的应用。

- 相关教材章节:第三章《数字逻辑电路基础》3. 简易电子密码锁设计与搭建:a. 设计原理:介绍简易电子密码锁的设计原理,包括电路图绘制、元器件选择等。

- 相关教材章节:第五章《数字电路设计与实践》b. 搭建过程:指导学生进行实际操作,搭建简易电子密码锁。

- 相关教材章节:第五章《数字电路设计与实践》4. 密码组合与破解:教授二进制密码的组合方法,引导学生进行密码破解实践。

- 相关教材章节:第六章《数字电路应用实例》教学进度安排:第一课时:电子密码锁原理与二进制计数原理学习。

简易密码锁设计实验报告

简易密码锁设计实验报告

密码锁作为一种常见的安全锁具,广泛应用于各种安全场合。

在本次实验中,我们将设计一个简易的密码锁,并通过实验验证其功能和安全性能。

原理

密码锁主要由以下几个部分组成:输入设备、控制器和输出设备。

输入设备通常是键盘或按键开关,控制器用于接收输入信号并判断是否正确,输出设备可以是电子门锁、LED 指示灯或蜂鸣器等。

在本次实验中,我们将采用单片机作为控制器,用矩阵键盘作为输入设备,用LED灯和蜂鸣器作为输出设备。

具体原理如下:

输入设备

矩阵键盘是一种常见的数字输入设备,在本次实验中我们将使用4*4矩阵键盘。

该键盘由16个按键组成,分别对应09数字和AF字母共16个字符。

控制器

我们将使用STM32F103C8T6单片机作为控制器。

该单片机具有较高的性能和丰富的外设资源,在密码锁设计中可以充分发挥其优势。

控制器主要工作流程如下:

(1) 初始化:对单片机进行初始化,并定义好输入输出引脚。

(2) 输入密码:从矩阵键盘读取用户输入的密码。

(3) 判断密码:将读取到的密码与预设的正确密码进行比较,如果相同则解锁,否则报警。

(4) 解锁/报警:如果密码正确,则点亮LED灯并发出解锁提示音;否则点亮红色LED灯并发出警示音。

输出设备

我们将使用两个LED灯和一个蜂鸣器作为输出设备,用于提示用户解锁状态。

其中绿色LED灯表示解锁成功,红色LED灯表示解锁失败,蜂鸣器用于发出提示音。

数电课程设计密码锁

数电课程设计密码锁 Last updated on the afternoon of January 3, 2021

数电课程设计

1.设计题目:

密码锁

2.设计要求:

该锁有4个密码拨动开关(设定0和1)来设置密码,一个开箱钥匙孔(能接通电池)。

当用钥匙开箱时,如果输入的4位密码正确,箱被打开;否则,电路将发出警报(发光二极管亮表示)。

要求锁的密码在第一次使用时能由用户自行进行一次性设定(机械方式)。

设计框图

3.设计思路

4.设计分析 个密码拨动开关,4位密码的输入用DSWPK-4实现。

DSWPK-4

(2)与设定密码比较

可用74x85 4位比较器,但由于未在multisim 里找到,于是用4个74x86代替。

74x86

真值表

A

B 输出 0

0 0 0

1 1 1

0 1 1

1 0 (3) 组合逻辑控制

将两个74x138 3-8译码器级联成4-16译码器,如下图 密码输入 与设定密码

设定密码

组合逻辑控制 箱子打

报警信

其中6口接高电平

74x138真值表

5.电路原理图

Led1灯亮的时候是报警信号,led2灯亮的时候说明锁已打开,用开关A模拟钥匙,闭合时视为插入钥匙。

5v的VCC视为电池。

使用到的其他元件有,8输入与非门,3kΩ电阻,2输入或门,开关等。

数电课程设计-电子密码锁

数电课程设计-电子密码锁电子密码锁设计任务及要求:使用电子器件设计制作一个密码锁,只有输入正确的代码时才能开锁。

在锁的控制电路中设一个可以修改的4位代码,当输入的代码和控制电路的代码一致时,锁打开。

用红灯亮、绿灯灭表示关锁,绿灯亮、红灯灭表示开锁。

如果30秒内未将锁打开,则电路自动复位进入自锁状态,并发报警信号。

方案设计及论证:设计思路是设多组用户输入键,其中只有4个是有效的密码按键,其它的都是干扰按键,若按下干扰键,键盘输入电路自动清零,输入的密码无效。

电路内部设置一个密码校验电路来验证密码正确与否,只有密码输入正确才能输出开锁所需的信号。

还应设置一组密码修改按键。

但用户按动输入开始键开始计时(只有按动了输入开始键之后输入的密码才有效),密码输入时间超过设定时间电路将报警,只有输入正确密码或断开电源报警铃才能停止,同时电路自锁,防止他人的非法操作。

具体方案如下:设17个用户输入键,其中只有4个是有效的密码按键,其它都是干扰键,还预设了4个密码修改键。

打开输入开关,电路开始计时,输入密码,开始校验,密码正确则开锁(绿灯亮表示开锁)同时停止计时;如果密码输入错误,则运行555单稳态电路密码锁定5分钟(红灯亮表示关锁),输入时间超过30秒密码也会锁定。

本文介绍了一个基于逻辑电路原理设计的电子密码锁电路。

该电路包括16个密码按键,其中4个为有效输入按键,采用4位密码输入。

只有在输入正确的密码后,才能实现对灯的电子控制。

该电路还包括各种附加电路,如报警和锁定功能,从而具有较高的安全系数。

该电路经过多次修改和整理,可以满足人们的基本要求。

但是,由于水平有限,该电路中存在一定的问题。

例如,电路的计时功能有误差,不能精确地对电路进行限时输入。

此外,用开关作为74LS112的CLK脉冲不是很稳定,可以考虑调换其他高速开关或计数脉冲。

最后,电路中未加显示电路,但可以通过其他数字模块实现这一功能。

为了进一步完善该电路,本文使用EWB软件对设计电路进行了逐步调试。

数电实验—密码锁报告

电子密码锁实验报告姜岳松一、实验目的1.了解电子密码锁的原理,学会用硬件描述语言来建立电子密码锁的模块。

2.利用该软件进行可编程逻辑器件设计,完成电子密码锁的逻辑仿真功能。

3.使用编译器将设计实现,下载到JDEE—10实验箱上进行调试和验证所设计的电子密码锁的功能。

二、实验器材1.Pentium—Ⅲ计算机一台;2.JDEE—10实验箱一只;三、实验要求设计一个电子密码锁,实现以下的功能:用8个拨码开关分别代表预设的密码和输入待验证的密码。

一个微动开关做为触发判断。

判断结果通过点阵和蜂鸣器表示。

正确的话,所有点阵的绿色灯点亮,同时蜂鸣发出“di”声。

否则,点阵显示红色,同时蜂鸣“do”音。

四、实验方案及设计过程1.第一部是实验电子密码锁的基本功能,该程序的主体是一个密码判断程序:首先是将输入的预设的密码和待验证密码用数组储存起来进行比较,比较结果通过IF语句,相同则触动绿色点阵和蜂鸣器的一个频率,不同则触动红色点阵和蜂鸣器的另一个频率2.开始丰富附肢程序:两种不同的响声需要两个计数器来产生不同的频率;要有一个上升沿保证颜色显示程序和密码判断程序以一个高频率运行,需要一个计数器;一个密码验证开关,由微动开关实现,在密码验证开关触动后能够保持一个高电位,这样则需要一个由D触发器构成的锁存器来锁定高电平。

3.点阵的显示:点阵的显示控制,由于显示OK的原代码之前已经练习过,然后设计好NO的字符,可以直接完成拓展之一。

此部分不需要详述。

五、拓展功能设计拓展主要是为了实现八位密码,这样所有的拨码开关都要用上,所以还需要两个微动开关来确定密码设定和输入。

同时,微动开关启动后,能够将拨码开关的密码储存到数组A[7..0]和B[7..0]中,待判断开关启动后调用,所以要用寄存器储存起来,所以声明一个串进串出的寄存器。

同时对主程序的判断器的输入变量进行修改。

六、顶层文件和源程序文本文件顶层文件文本:SUBDESIGN ECLOCK ( a[7..0],b[7..0]:input;key: input;freq1,freq2: input;red: output;green: output;spk: output;)begindefaultsred=gnd; green=gnd;spk=gnd;end defaults;if key thenif a[]==b[] then red=vcc;spk=freq1;else green=vcc;spk=freq2;end if;end if;end;点阵显示文本:subdesign leddiaplay( green,red: input;clk[2..0]: input;row[8..1],colred[16..1],colgreen[16..1]: output; )begindefaultscolred[]=h"ffff";colgreen[]=h"ffff";end defaults;if green thentableclk[2..0]=>row[8..1],colgreen[16..1];H"0" =>H"1", H"DBC3"; %1101 1011 1100 0011% H"1" =>H"2", H"EBDB";H"2" =>H"4", H"EBDB";H"3" =>H"8", H"F3DB";H"4" =>H"10", H"F3DB";H"5" =>H"20", H"EBDB";H"6" =>H"40", H"EBDB";H"7" =>H"80", H"DBC3";end table;end if;if red thentableclk[2..0]=>row[8..1],colred[16..1];h"0" =>h"1", h"C3DB";h"1" =>h"2", h"DBD3";h"2" =>h"4", h"DBD3";h"3" =>h"8", h"DBC3";h"4" =>h"10", h"DBCB";h"5" =>h"20", h"DBCB";h"6" =>h"40", h"DBCB";h"7" =>h"80", h"C3DB";end table;end if;end;寄存器文本:SUBDESIGN register(clk,load,d[7..0] :input;q[7..0] :OUTPUT;)VARIABLEff[7..0] :DFFE;BEGINff[].clk=clk;ff[].ena=load;ff[].d=d[];q[]=ff[].q;end;七、试验中遇到的问题1、设计八位密码的时候,需要将八位的密码输进判断器,起初采取的不是寄存器的手段,而是自己定义了一个使能开关,当微动开关高电平就允许密码通过使能开关到达a[7..0]或者b[7..0],但是实验发现这样密码并不能被储存起来,后来想明白应该是由于并没有变量储存的机制,所以要想将变量储存必须有寄存器才行,根据教材定义寄存器后,该问题得到解决。

简易密码锁

课程设计报告课程:《数字逻辑电路》课程设计学号:姓名:班级:教师:徐州师范大学计算机科学与技术学院课程设计任务书设计名称:简易密码锁日期:设计内容:1.密码由3个0—7中的数组成。

2.系统提供8个按键.分别表示0-7,用来输入密码;可以用一个开关阵列用于预置和改动密码。

3.在依次按下3个键后.系统有如下反应。

若3个键按下的顺序和代表的数字和预置密码相同,系统发出开锁信号,用LED1表示;否则,用LED2表示错误。

若连续错误3次则发出报警信号,亮LED3表示。

4.应有一个键用于清除报警状态,或者限定报警时间,使系统能够回到初始状态。

5.输入按键应有防抖措施。

设计目的与要求:1.学习数字逻辑等电路设计方法,熟知编码器、比较器、计数器、译码显示的工作原理及特点;2.培养勤奋认真、分析故障和解决问题的能力。

设计环境或器材、原理与说明:1.器材: ·数据选择器·8线—3线优先编码器·数值比较器·开关若干·电源2.原理与说明此设计方案是根据任务书要求,设定三位密码,因此选择三个数码管显示数字,设定一个输入锁定键S0,可以控制输入,当高电平时方可允许输入。

密码显示是根据输入密码而显示数字的,因为初始化清零,数码管上全显示“000”,因此设定一个清零的开关S 接入移位显示电路以控制寄存器清零。

当密码设定完毕后,设定一个锁存键S1,锁定设置的密码,再由输入数字键输入开锁密码。

起初检验开关S2为低电平,则灯都不亮,当输入完开锁密码后开始进行检验密码时,打开检验开关S2,观察灯亮情况,得出密码匹配结果。

利用多功能虚拟软件Multism8进行电路的制作、调试,并生成文件。

设计过程(步骤)或程序代码:1.密码锁电路包含:键盘输入、密码检测、开锁电路、执行电路、报警电路。

2.用8个数码开关设置密码,密码输入为串行输入,每次用拨码开关输入1位密码,按单步脉冲把这个密码输入。

数电课程设计密码锁

数电课程设计密码锁一、课程目标知识目标:1. 让学生理解数字电路基础知识,特别是组合逻辑电路的原理和应用;2. 掌握使用逻辑门设计简单的密码锁电路,并能够用逻辑表达式表示;3. 了解数字电路在实际应用中的安全性和可靠性,特别是在密码锁系统中的作用。

技能目标:1. 培养学生运用所学的数字电路知识,解决实际问题的能力;2. 能够使用逻辑门和触发器设计并搭建简单的密码锁电路;3. 学会使用相关软件工具(如Multisim等)进行电路仿真,验证设计电路的正确性。

情感态度价值观目标:1. 激发学生对数字电路和电子技术的学习兴趣,培养创新意识和探索精神;2. 培养学生团队协作精神,在小组合作中共同分析问题、解决问题;3. 引导学生认识到科技发展对社会安全的重要性,树立正确的科技伦理观念。

分析:本课程针对高中年级学生,他们在前期课程中已经学习了基础的数字电路知识,具有一定的电路分析和设计能力。

课程性质为实践性强的设计与实验课,旨在通过设计密码锁的实践活动,深化对数字电路知识的理解和应用。

教学要求:1. 结合教材内容,通过实例引入,使学生将理论与实践相结合;2. 引导学生通过小组讨论和动手实践,培养解决实际问题的能力;3. 强调安全性、可靠性和科技伦理,培养学生对社会负责的态度。

二、教学内容1. 理论知识回顾:- 复习数字电路基础,特别是逻辑门的工作原理和逻辑表达式;- 温习组合逻辑电路的设计方法和步骤。

2. 实践教学内容:- 密码锁的原理介绍,包括常见的密码锁类型和安全性分析;- 使用逻辑门设计密码锁电路,涉及基本的逻辑运算和组合逻辑设计;- 引导学生了解触发器在密码锁中的应用,如RS触发器、D触发器等。

3. 教学大纲安排:- 教材章节:第五章“组合逻辑电路”和第六章“时序逻辑电路基础”;- 第一课时:回顾数字电路基础,介绍密码锁原理;- 第二课时:设计和分析密码锁的组合逻辑部分;- 第三课时:引入时序逻辑,探讨触发器在密码锁中的应用;- 第四课时:动手实践,小组合作设计并搭建简单的密码锁电路。

数字电路课程设计电子密码锁

《数字电子技术》课程设计报告电子密码锁控制电路设计人:黄亮学号:1887090112专业:09网络工程班级:1班成绩:评阅人:安徽科技学院理学院2011/6/16设计要求1、设计一个密码锁的控制电路,当输入正确代码时,输出开锁信号以推动执行机构工作,用红灯亮、绿灯熄灭表示关锁,用绿灯亮、红灯熄灭表示开锁;2、在锁的控制电路中储存一个可以修改的4位代码,当开锁按钮开关(可设置成6位至8位,其中实际有效为4位,其余为虚设)的输入代码等于储存代码时,开锁;3、从第一个按钮触动后的10秒内若未将锁打开,则电路自动复位并进入自锁状态,使之无法再打开,并由扬声器发出持续20秒的报警信号。

一.实验目的①利用小规模电路设计一个简易的电子密码锁控制电路。

②设计一个电子密码锁的控制电路,当输入正确时,会输出开锁信号以推动执行机构工作。

用灯1亮表示开锁。

③学习使用Multisim 10.0软件进行数字电路设计。

二.实验内容电子密码锁的控制电路中储存一个可以修改的4为代码。

当开锁按钮开关(可以设置成6~8位,其中有效的是4位,其余为虚设)的输入代码等于储存代码时,发出开锁信号(用灯2亮表示报警)。

电子密码共分为两个输入区:密码输入区和密码修改区。

密码输入区内,有4个是有效地密码按键,1个为密码启动键(可当做干扰键)。

若不按启动键,则无法开锁。

如果输入密码的时间超过20s(一般而言用户不会超过20s),电路将锁定键盘并报警,防止他人非法操作。

密码修改区内,有4个是密码更改键,另一个是电路复位键(解除锁定)。

电子密码锁的控制仿真电路如下:电路剖析:此电路可以分为三个部分:●密码检测与修改电路开始时可以在电路中设置起始开锁密码,只有当输入密码与设置密码相同时,锁才能被打开;并且,如果你想换密码,也很容易,只要将电路中的密码修改区中的几个开关变换一下就可以了。

●键盘输入限时电路:如果输入密码的时间超过10s(一般而言用户不会超过10s),电路将锁定键盘并报警,防止他人非法操作。

数电课程设计-电子密码锁

数字电子技术课程设计一、设计题目电子密码锁二、主要内容及要求(1)用电子器件设计制作一个密码锁,使之在输入正确的代码时开锁。

(2)在锁的控制电路中设一个可以修改的4位代码,当输入的代码和控制电路的代码一致是锁打开。

(3)用红灯亮、绿灯灭表示关锁,绿灯亮、红灯灭表示开锁(4)如5s内未将锁打开,则电路自动复位进入自锁状态,并发报警信号。

四、总评成绩指导教师学生签名电子密码锁一、设计任务与要求(1)用电子器件设计制作一个密码锁,使之在输入正确的代码时开锁。

(2)在锁的控制电路中设一个可以修改的4位代码,当输入的代码和控制电路的代码一致是锁打开。

(3)用红灯亮、绿灯灭表示关锁,绿灯亮、红灯灭表示开锁(4)如30s内未将锁打开,则电路自动复位进入自锁状态,并发报警信号。

二、方案设计与论证设计思路:设多组用户输入键,其中只有4 个是有效的密码按键,其它的都是干扰按键,若按下干扰键,键盘输入电路自动清零,输入的密码无效。

电路内部设置一个密码校验电路来验证密码正确与否,只有密码输入正确才能输出开锁所需的信号。

还应设置一组密码修改按键。

但用户按动输入开始键开始计时(只有按动了输入开始键之后输入的密码才有效),密码输入时间超过设定时间电路将报警(老师要求的输入时间5秒太短了),只有输入正确密码或断开电源报警铃才能停止,同时电路自锁,防止他人的非法操作。

方案一:我共设了17个用户输入键,其中只有4个是有效的密码按键,其它都是干扰键,还预设了4个密码修改键。

打开输入开关,电路开始计时,输入密码,开始校验,密码正确则开锁(绿灯亮表示开锁)同时停止计时;如果密码输入错误,则运行555单稳态电路密码锁定5分钟(红灯亮表示关锁),输入时间超过30秒密码也会锁定。

大概思路:用四个74LS112 JK触发器串联,输入密码正确与否,输入的电平不同,由此达到密码校验。

密码的输入有16组开关控制,分为0和1两种情况。

限时30秒由74LS160计数器控制,而锁定时间则由555单稳态电路控制,开锁、关锁由指示灯点亮模拟。

数电实验 数字锁

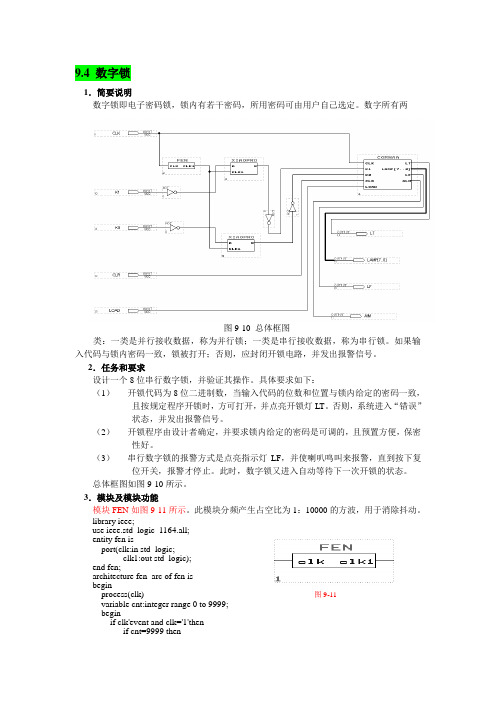

9.4 数字锁1.简要说明数字锁即电子密码锁,锁内有若干密码,所用密码可由用户自己选定。

数字所有两图9-10 总体框图类:一类是并行接收数据,称为并行锁;一类是串行接收数据,称为串行锁。

如果输入代码与锁内密码一致,锁被打开;否则,应封闭开锁电路,并发出报警信号。

2.任务和要求设计一个8位串行数字锁,并验证其操作。

具体要求如下:(1)开锁代码为8位二进制数,当输入代码的位数和位置与锁内给定的密码一致,且按规定程序开锁时,方可打开,并点亮开锁灯LT。

否则,系统进入“错误”状态,并发出报警信号。

(2)开锁程序由设计者确定,并要求锁内给定的密码是可调的,且预置方便,保密性好。

(3)串行数字锁的报警方式是点亮指示灯LF,并使喇叭鸣叫来报警,直到按下复位开关,报警才停止。

此时,数字锁又进入自动等待下一次开锁的状态。

总体框图如图9-10所示。

3.模块及模块功能模块FEN如图9-11所示。

此模块分频产生占空比为1:10000的方波,用于消除抖动。

library ieee;use ieee.std_logic_1164.all;entity fen isport(clk:in std_logic;clk1:out std_logic);end fen;architecture fen_arc of fen isbeginprocess(clk) 图9-11variable cnt:integer range 0 to 9999;beginif clk'event and clk='1'thenif cnt=9999 thencnt:=0;clk1<='1';elsecnt:=cnt+1;clk1<='0';end if;end if;end process;end fen_arc;模块XIAOPRO如图9-12所示。

它是消抖同步模块。

library ieee;use ieee.std_logic_1164.all;entity xiaopro isport(a,clk1:in std_logic;b:out std_logic);end xiaopro;architecture xiao_arc of xiaopro is 图9-12signal tmp1:std_logic;beginprocess(clk1,a)variable tmp3,tmp2:std_logic;beginif clk1'event and clk1='0'thentmp1<=a;tmp2:=tmp1;tmp3:=not tmp2;end if;b<=tmp1 and tmp3 and clk1;end process;end xiao_arc;模块CORNAA如图9-13所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电路设计实验报告——简易密码锁学院:班级:学号:姓名:目录●任务要求●系统设计✓设计思路✓总体框图✓分块设计●波形仿真及波形分析●源代码●功能分析●故障分析及问题解决●总结及结论●任务要求设计并实现一个数字密码锁,密码锁有四位数字密码和一个确认开锁按键,密码输入正确,密码锁打开,密码输入错误进行警示。

基本要求:1、密码设置:通过键盘进行4 位数字密码设定输入,在数码管上显示所输入数字。

通过密码设置确定键(BTN 键)进行锁定。

2、开锁:在闭锁状态下,可以输入密码开锁,且每输入一位密码,在数码管上显示“-”,提示已输入密码的位数。

输入四位核对密码后,按“开锁”键,若密码正确则系统开锁,若密码错误系统仍然处于闭锁状态,并用蜂鸣器或led 闪烁报警。

3、在开锁状态下,可以通过密码复位键(BTN 键)来清除密码,恢复初始密码“0000”。

闭锁状态下不能清除密码。

4、用点阵显示开锁和闭锁状态。

提高要求:1、输入密码数字由右向左依次显示,即:每输入一数字显示在最右边的数码管上,同时将先前输入的所有数字向左移动一位。

2、密码锁的密码位数(4~6 位)可调。

3、自拟其它功能。

●系统设计设计思路将电子密码锁系统分为三个部分来进行设计,数字密码输入部分、密码锁控制电路和密码锁显示电路。

密码锁输入电路包括时序产生电路,键盘扫描电路,键盘译码电路等,将用户手动输入的相关密码信息转换为软件所能识别的编码,作为整个电路的输入。

密码锁控制电路包括相应的数据存储电路,密码核对电路,能够进行数值的比较,进行电路解锁,开锁,密码的重新设置等。

密码锁显示电路包括将待显示数据的BCD 码转换成数码管的七段显示驱动编码,密码锁在相应的状态下的点阵输出以及蜂鸣器的报警输出。

总体框图按复位键 键入初始密码0000 密码错误密码正确 按确认键 按复位键按确认键密码锁显示电路 密码锁控制电路 数码管显示报警电路密码更改与密码设计电路键入状态闭锁状态开锁状态 报警状态分块设计✓键盘扫描电路首先,向列扫描地址逐列输出低电平,然后从行码地址读回,如果有键摁下,则相应行的值应为低,如果没有按键按下,由于上拉的作用,行码为高。

这样就可以通过输出列码和读取的行码来判断按下的是什么键。

在判断有按键的按下后,要有一定的延时,防止键盘抖动。

entity keyboard isport(row:in std_logic_vector(3 downto 0);col:out std_logic_vector(3 downto 0);keyout:out std_logic_vector(3 downto 0);q:out std_logic;clk:in std_logic);end keyboard;architecture struct of keyboard issignal col_buffer1:std_logic_vector(3 downto 0);signal col_buffer2:std_logic_vector(3 downto 0);signal key :std_logic_vector(7 downto 0);signal counter:integer range 0 to 3;signal delay:integer range 0 to 10;signal stop:std_logic;begincol <= col_buffer2;q <= stop;process(CLK,row,stop)beginif clk'event and clk = '1' thenif counter = 3 thencounter <= 0;elsecounter <= counter + 1;//由于只要求输入四个数字所以需要计数end if;case counter iswhen 0 => col_buffer1 <= "1110";when 1 => col_buffer1 <= "1101";when 2 => col_buffer1 <= "1011";when 3 => col_buffer1 <= "0111";end case;end if;end process;key <= row & col_buffer2;process(clk,key)beginif clk'event and clk = '0' thencase key iswhen "01111110" => stop<='1';keyout<="0000";when "01111101" => stop<='1';keyout<="0001";when "01111011" => stop<='1';keyout<="0010";when "01110111" => stop<='1';keyout<="0011";when "10111110" => stop<='1';keyout<="0100";when "10111101" => stop<='1';keyout<="0101";when "10111011" => stop<='1';keyout<="0110";when "10110111" => stop<='1';keyout<="0111";when "11011110" => stop<='1';keyout<="1000";when "11011101" => stop<='1';keyout<="1001";when others => stop <= '0';//仅仅在摁0~9的时候会有显示,在摁除了这十个键之外的键的时候是不会有反应的,将keyout的值转换为相应的数码管值,来控制数码管的显示end case ;end if;end process;process(clk,stop)beginif clk'event and clk = '1'thenif stop = '0' thencol_buffer2 <= col_buffer1;end if;end if;end process;end struct;点阵显示电路采用行扫描的方式,每经过一段时间,给一行一个低电平。

则若在列的方向上如果接入高电平,则会使相应的二极管发光。

由于人眼的的暂留效应就回使我们看到我们想要的图案。

library ieee;use ieee.std_logic_1164.all;entity led isport(row:out std_logic_vector(7 downto 0);num:in std_logic_vector(1 downto 0);clk:in std_logic;col:out std_logic_vector(7 downto 0));end entity;architecture struct of led issignal counter : integer range 0 to 7;beginprocess(clk)beginif clk'event and clk = '1' thenif counter = 7 thencounter <= 0;elsecounter <= counter +1;end if;end if;end process;process(clk,counter)beginif clk'event and clk = '0' thenif num <= "00" then//键入状态case counter iswhen 0 => row <= "11111110"; col <= "00111100";when 1 => row <= "11111101"; col <= "00111100";when 2 => row <= "11111011"; col <= "00111100";when 3 => row <= "11110111"; col <= "00111100";when 4 => row <= "11101111"; col <= "00111100";when 5 => row <= "11011111"; col <= "00011000";when 6 => row <= "10111111"; col <= "00111100";when 7 => row <= "01111111"; col <= "00011000";end case;elsif num = "01" then//闭锁状态case counter iswhen 0 => row <= "11111110"; col <= "11111111";when 1 => row <= "11111101"; col <= "11111111";when 2 => row <= "11111011"; col <= "11111111";when 3 => row <= "11110111"; col <= "11111111";when 4 => row <= "11101111"; col <= "01000010";when 5 => row <= "11011111"; col <= "01000010";when 6 => row <= "10111111"; col <= "01000010";when 7 => row <= "01111111"; col <= "00111100";end case;elsif num = "10" then//开锁状态case counter iswhen 0 => row <= "11111110"; col <= "00000000";when 1 => row <= "11111101"; col <= "00011111";when 2 => row <= "11111011"; col <= "00011111";when 3 => row <= "11110111"; col <= "00011111";when 4 => row <= "11101111"; col <= "10011111";when 5 => row <= "11011111"; col <= "10001000";when 6 => row <= "10111111"; col <= "10001000";when 7 => row <= "01111111"; col <= "01110000";end case;elsecase counter is//报警状态when 0 => row <= "11111110"; col <= "00011000";when 1 => row <= "11111101"; col <= "00111100";when 2 => row <= "11111011"; col <= "00011000";when 3 => row <= "11110111"; col <= "00011000";when 4 => row <= "11101111"; col <= "00111100";when 5 => row <= "11011111"; col <= "00111100";when 6 => row <= "10111111"; col <= "00111100";when 7 => row <= "01111111"; col <= "00011000";end case;end if;end if;end process;end struct;数码管显示其中引脚图的两个COM端连在一起,是公共端,共阴数码管要将其接地,共阳数码管将其接正5伏电源。