5)SCI串行通信接口

5)SCI串行通信接口

一个开始位 1~8个数据位(通常为8位) 一个奇/偶校验位或无奇偶校验位 1~2个停止位

区分地址和数据的附加位(仅地址位模式时存在)

与RS232 格式兼容

8

SCI数据格式的配置

SCIA的通信控制寄存器

STOP BITS:指定发送时停止位个数,0-1个停止位,1-2个停止位; EVEN/ODD PARITY:奇偶校验选择, 0-奇校验, 1-偶校验; PARITY ENALBE:校验使能, 0-禁止奇偶校验,1-允许奇偶校验; LOOPBACK ENA:环路测试模式使能,1-TX数据内部送Rx,0-禁止 ADDR/IDLE MODE:多处理器模式选择,0-空闲线模式,1-地址位模式 SCICHAR2~0:数据长度选择,1~8位数据(000-111)。

第四讲 内容回顾

1、DSP开发系统组成 1)硬件开发工具;2)软件开发工具;3)DSP应用板。 2、DSP最小系统 1)DSP芯片;2)时钟电路;3)电源与复位电路; 4)JTAG仿真接口。 3、人机接口 1)输入:键盘、开关、按钮等; 2)输出:LED、LCD等

1

DSP原理及其应用技术

串行通信接口(SCI)

1)臵RXENA=1(SCICTL1.D0),使能接收器接收器数据; 2)数据到达SCIRXD引脚后,检测起始位(SCI自动实现); 3)数据从RXSHF寄存器移位到接收缓冲寄存器(SCIRXBUF), 产生一个中断请求,同时接收器数据准备好标志RXRDY=1;

4)用户程序读取SCIRXBUF寄存器,标志位RXRDY自动清零;

1)首先置位TXWAKE(SCICTL1.3),控制数据发送特征;

2)写一个数据字节(内容不重要)到SCITXBUF,发送一个块 开始信号( 11位的空闲时间);

串行通信接口SCI

串行通信分为同步通信和异步通信。

串行通信接口都具有发送引脚TXD和接收引脚RXD,它们是TTL平电。

如果要利用这两个引脚与外界实行异步通信,必须将TTL电平转化为RS-232电平。

SCI是一种全双工异步串行通信接口,主要用于MCU与其他计算机或设备之间的通信,几个独立的MCU也能通过SCI实现串行通信,形成网络。

从编程角度看,先设定好波特率,通信格式,是否校验,是否允许中断等。

接着发送数据时,先检查相应的标志位是否允许发送数据,如果可以,则把数据放入SCI数据寄存器即可,剩下的工作芯片自动完成:将数据从SCI数据寄存器送到发送移位寄存器,硬件驱动将发送移位寄存器里的数据按规定发送到发送引脚TXD,供对方接收。

接收时,数据逐位从接收引脚RXD进入到接收移位寄存器,当收到一个完整字节时,芯片会自动将数据送到SCI数据寄存器,并置相应的标志位,我们就可以根据标志位的情况来读取数据了。

SCIBDH:TNP[1:0]:发送窄脉冲位。

此位的设定与SCI传送的脉冲对应关系如下表:SCIBDL:SBR[12:0]:波特率设定位当IREN=0时,SCI波特率=SCI总线时钟/(16*SBR[12:0])当IREN=1时,SCI波特率=SCI总线时钟/(32*SBR[12:1])SCICR1:控制寄存器1(当AMAP=0时有效)LOOPS:循环模式选择位。

LOOPS=0时,为正常模式。

LOOPS=1时,为自发自收模式,在此模式下,RXD引脚与SCI内部断开,内部发送数据直接作为接收的输入,用于测试。

接收器的输入由RSRC位决定。

SCISWAI:当SCISWAI=0时,SCI可以在等待模式下工作。

当SCISWAI=1时,SCI 不可以在等待模式下工作。

RSRC:当LOOPS=1时,RSRC位决定接收移位寄存器接收数据的来源。

RSRC=1,RXD引脚与SCI模块断开,SCI用TXD引脚来发送及接收。

RSRC=0时,发送器的输出作为接收器的输入。

第五章2_串行通信接口

PIE 模块

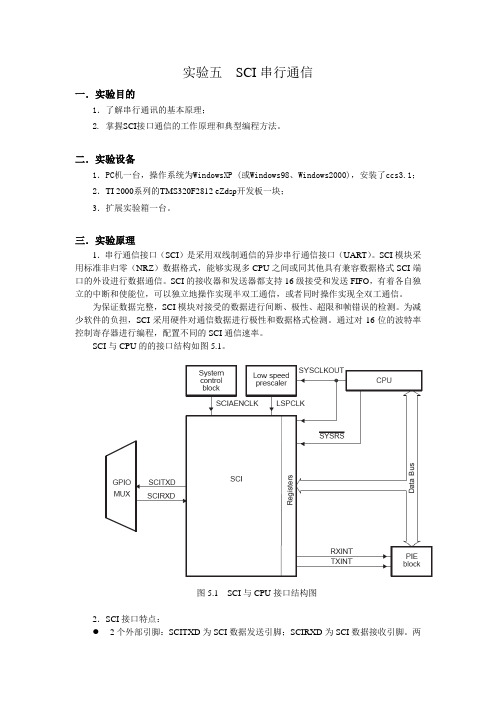

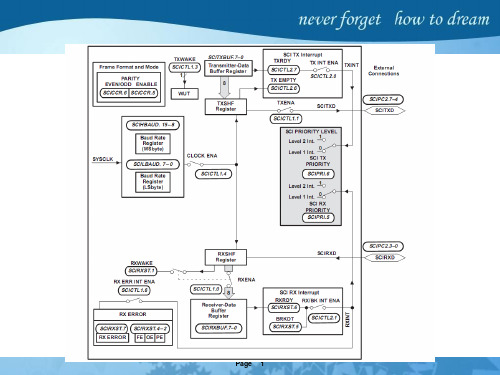

图6-1-1 SCI与CPU接口图

第5.2节 串行通信接口(SCI)

一、概述

√四个错误检测标志位:奇偶性、溢出、帧和间断检测。 √两种唤醒多处理器模式:空闲线唤醒和地址位唤醒。 √半双工或全双工通信。 √双缓冲接收和发送功能。 √发送器和接收器可通过带有状态标志的中断驱动或polled算法完成操作。 √独立的发送和接收中断使能位(BRKDT除外)。 √ NRZ格式。 √ 13个SCI模块控制寄存器,起始地址为7050H。 √自动波特率检测硬件逻辑(比F240x多出的功能)。 √ 16级发送/接收FIFO(比F240x多出的功能)。

第5.2节 串行通信接口(SCI)

二、SCI 结构特点

SCI 可编程数据格式

▲ SCI接收和发送的数据都采用NRZ格式: √ 1个起始位; √ 1~8位数据; √ 1个奇、偶或无校验位(可选); √ 1~2位停止位; √ 1个区分数据与地址的附加位(仅用于地址位模式)。 ▲字符 —— 数据的基本单元称为,其长度为1~8位。每一个字符包含1个

▲ 对接收到的数据进行间断、奇偶性、溢出和帧错误检测 ▲ 通过使用16位的波特率选择寄存器能设置不同的位速率

第5.2节 串行通信接口(SCI)

一、概述

▲ SCI与CPU之间的接口图如P149 所示 ▲ SCI模块主要特点如下 √两个多功能复用引脚,如果不用于SCI通信,可以作为通用I/O口。

SCITXD:数据发送引脚; SCIRXD:数据接收引脚。

第5.2节 串行通信接口(SCI)

二、SCI 结构特点

空闲线多处理器模式

空闲线多处理器模式(ADDR/IDLE MODE=0)中,块 , 与块之间的空闲时间大于块中各帧之间的空闲时间。如果一 帧之后有10个或更多的高电平位的空闲时间,就表明了下一 个新数据块的开始。每位的时间可以由波特率值(位每秒) 计算出来。空闲线多处理器模式(ADDR/IDLE MODE位是 SCICCR.3)通信格式P255所示。

sci串口通信原理

sci串口通信原理SCI(Serial Communication Interface,串行通信接口)是一种广泛应用于嵌入式系统和电子设备中的串行通信协议。

SCI通常指的是UART(Universal Asynchronous Receiver/Transmitter,通用异步收发传输器)的一种实现方式。

在SCI通信原理中,数据以串行的方式通过一根或多根信号线进行发送和接收。

基本的通信参数包括波特率(bits per second, bps)、数据位数、停止位数和校验类型等。

1. 波特率:指每秒钟传输的比特数,是通信双方必须同步的一个重要参数。

2. 数据格式:1)数据位数(Data Bits):通常为5、6、7或8位。

2)停止位(Stop Bits):通常为1或2位,用于表示一个字符数据包的结束。

3)校验位(Parity Bit):奇偶校验,可选无校验、奇校验或偶校验,用于检测数据传输过程中可能出现的错误。

3. 通信过程:1)发送端将并行数据转换为串行数据,并按照设定的波特率和格式输出。

2)接收端则按照相同的参数设置解码接收到的串行数据,还原成并行数据。

4. 控制信号:1)RTS (Request to Send) 和CTS (Clear to Send) 用于硬件握手,确保双方都准备好进行通信。

2)DTR (Data Terminal Ready) 和DSR (Data Set Ready) 另一对硬件握手信号,用于设备之间表明就绪状态。

3)TXD (Transmit Data) 是发送数据的信号线,RXD (Receive Data) 是接收数据的信号线。

4)其他可能还包括中断请求线(如IRQ)等。

在嵌入式系统中,例如使用TMS320F28xx系列DSP芯片时,SCI模块负责处理这些串行通信任务,通过配置相应的寄存器来设定上述参数,然后利用中断机制实现在数据发送和接收过程中的实时响应与处理。

DSP课件-SCI串行通信接口

8255A

打印机插座

CPU

PA0~7

PC7 PC2

地

DATA0~7

STB BUSY 地

8255A并行打印机接口电路框图

3

串行通信概述

串行通信:通信线上既传输数据信息,也传输联络信息,因 此收发双方就必须要有通信协议。特点是串行传输成本低, 适用于远距离通信,但传输速度低。 串行通信分类:1)同步通信;2)异步通信。

同步通信:发送器和接收器通常使用同一时钟源来同步。方法是在发送器 发送数据时同时包含了时钟信号,接收器利用该时钟信号进行接收。 异步通信:收发双方的时钟不是同一个时钟,是由双方各自的时钟实现数 据的发送和接收。但要求双方使用同一标称频率,允许有一定偏差。 同步方法:要正确传输字符,准确读取每一位是必须用各自的时钟同步的, 为克服不同时钟的偏差,每个字符都有一个起始位进行同步。

发送过程:在FIFO功能使能的情况下,缓冲寄存器SCITXBUF从TX FIFO中获 取要发送的数据,然后将数据传输给发送移位寄存器TXSHF,若SCI的发送功 能使能,将接收到的数据逐位的移到SCITXD引脚上。

8

SCI的数据格式

SCI的数据格式包括: 一个开始位 1~8个数据位(通常为8位) 一个奇/偶校验位或无奇偶校验位 1~2个停止位 区分地址和数据的附加位(仅地址位模式时存在)

CPU SCIRXBUF

每个字符6个数据位

RXSHF

SCIRXD

地址位模式

12

通信过程中的发送器信号 3个数据位

地址位模式

1)TXENA=1(SCICTL1.D1),使能发送器发送数据; 2)程序写数据到SCITXBUF寄存器,此时发送器不为空,TXRDY变低; 3)SCI发送数据到移位寄存器TXSHF后,产生中断请求,同时TXRDY变高; 4)TXRDY变高后,程序写第二个字符到SCITXBUF,随后TXRDY又变低; 5)发送完第一个字符,开始将第二个字符移位到寄存器TXSHF;

第05章串行通信接口SCI

地址链接文件

M CU 映 像 寄 存 器 名 定 义 头 文 件

嵌入式系统--使用HCS12微控制器的设计与应用

工程说明文件

20

5.5 串行通信通用函数与测试实例 5.5.2 查询方式收发测试工程

4.中断方式测试工程辅助工具

嵌入式系统--使用HCS12微控制器的设计与应用

21

5.5 串行通信通用函数与测试实例 5.5.2 查询方式收发测试工程

13

5.3 DG128 SCI模块寄存器

5.3.6 SCI数据寄存器

1. 缩写:SCI0DRH、SCI0DRL、SCI1DRH、SCI1DRL 2. 位定义:

数据位 D7 D6 T8 0 D7 R7 T7 0 D6 R6 T6 0 D5 R5 T5 0 D4 R4 T4 0 D3 R3 T3 0 D2 R2 T2 0 D1 R1 T1 0 D0 R0 T0 D5 D4 D3 D2 D1 D0

15 H X 0 8 7

M CU 的

内

部

总

线

(In te rn a l B u s )

7 SCI 控 制 寄 存 器

0

S C I状 态 寄 存 器

S C I波 特 率 寄 存 器

7

嵌入式系统--使用HCS12微控制器的设计与应用 7

5.3 DG128 SCI模块寄存器

5.3.1 SCI波特率寄存器

嵌入式系统--使用HCS12微控制器的设计与应用 17

5.5 串行通信通用函数与测试实例 5.5.2 查询方式收发测试工程

1.查询方式收发测试工程主函数文件main.c 1.禁止总中断 2.芯片初始化 3.SCI模块初始化

等待从PC机接收一个数据

向PC机发送一个数据

SCI

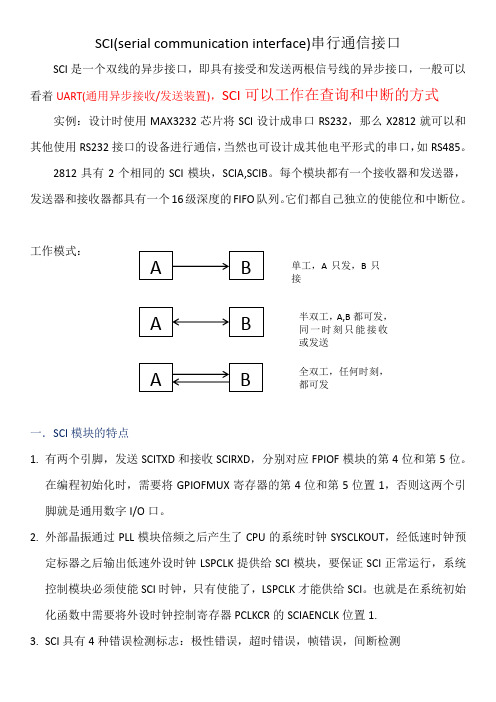

SCI(serial communication interface)串行通信接口SCI 是一个双线的异步接口,即具有接受和发送两根信号线的异步接口,一般可以看着UART(通用异步接收/发送装置),SCI可以工作在查询和中断的方式实例:设计时使用MAX3232芯片将SCI 设计成串口RS232,那么X2812就可以和其他使用RS232接口的设备进行通信,当然也可设计成其他电平形式的串口,如RS485。

2812具有2个相同的SCI 模块,SCIA,SCIB 。

每个模块都有一个接收器和发送器,发送器和接收器都具有一个16级深度的FIFO 队列。

它们都自己独立的使能位和中断位。

工作模式:一.SCI 模块的特点1. 有两个引脚,发送SCITXD 和接收SCIRXD ,分别对应FPIOF 模块的第4位和第5位。

在编程初始化时,需要将GPIOFMUX 寄存器的第4位和第5位置1,否则这两个引脚就是通用数字I/O 口。

2. 外部晶振通过PLL 模块倍频之后产生了CPU 的系统时钟SYSCLKOUT ,经低速时钟预定标器之后输出低速外设时钟LSPCLK 提供给SCI 模块,要保证SCI 正常运行,系统控制模块必须使能SCI 时钟,只有使能了,LSPCLK 才能供给SCI 。

也就是在系统初始化函数中需要将外设时钟控制寄存器PCLKCR 的SCIAENCLK 位置1.3. SCI 具有4种错误检测标志:极性错误,超时错误,帧错误,间断检测A A ABB B单工,A 只发,B 只接半双工,A,B 都可发,同一时刻只能接收或发送全双工,任何时刻,都可发4.具有双缓冲接收和发送功能,接收缓冲寄存器位SCIRXBUF,发送缓冲寄存器为SCITXBUF。

独立的发送器和接收器使得SCI可以工作于半双工或全双工5.可以产生两个中断:SCIRXINT和SCITXINT,即接收中断和发送中断,SCI模块具有独立的发送中断使能位和接收中断使能位,发送和接收可以通过中断方式实现,也可以查询中断方式是实现6.在多处理器模式下,SCI模块具有两种唤醒方式:空闲线方式和地址位方式。

SCI串行通信

实验五SCI串行通信一.实验目的1.了解串行通讯的基本原理;2. 掌握SCI接口通信的工作原理和典型编程方法。

二.实验设备1.PC机一台,操作系统为WindowsXP (或Windows98、Windows2000),安装了ccs3.1;2.TI 2000系列的TMS320F2812 eZdsp开发板一块;3.扩展实验箱一台。

三.实验原理1.串行通信接口(SCI)是采用双线制通信的异步串行通信接口(UART)。

SCI模块采用标准非归零(NRZ)数据格式,能够实现多CPU之间或同其他具有兼容数据格式SCI端口的外设进行数据通信。

SCI的接收器和发送器都支持16级接受和发送FIFO,有着各自独立的中断和使能位,可以独立地操作实现半双工通信,或者同时操作实现全双工通信。

为保证数据完整,SCI模块对接受的数据进行间断、极性、超限和帧错误的检测。

为减少软件的负担,SCI采用硬件对通信数据进行极性和数据格式检测。

通过对16位的波特率控制寄存器进行编程,配置不同的SCI通信速率。

SCI与CPU的的接口结构如图5.1。

图5.1 SCI与CPU接口结构图2.SCI接口特点:2个外部引脚:SCITXD为SCI数据发送引脚;SCIRXD为SCI数据接收引脚。

两个引脚为多功能复用引脚,如果不使用可以作为通用数字量I/O。

●可编程通信速率,可以设置64K种通信速率。

●数据格式:1个启动位;1-8个可编程数据字长度;可选择奇校验、偶校验或无校验位模式;1或2位的停止位。

●4种错误检测标志位:奇偶错误、超时错误、帧错误和间断错误。

●2种唤醒多处理器方式:空闲线唤醒(Idle-line)和地址位唤醒(Address Bit)。

●全双工或半双工通信模式。

●双缓冲接收和发送功能。

●发送和接收可以采用中断和状态查询2种方式。

图5.2 SCI通信模块接口框图●独立的发送和接收中断使能控制。

●NRZ(非归零)通信格式。

●13个SCI模块控制寄存器,起始地址为7050H。

sci串口通信原理 -回复

sci串口通信原理-回复SCI(串行通信接口)是一种常见的串口通信协议,被广泛应用于各种电子设备中。

在本文中,我们将一步一步回答关于SCI串口通信原理的问题,包括它的工作原理、常见的应用场景以及一些技术细节。

首先,让我们来了解SCI串口通信的工作原理。

SCI是一种串行通信接口,它通过使用单一的线路来传输数据。

这条线路被分为两个方向,一个用于传输数据(TX),一个用于接收数据(RX)。

通过在这两个方向上的电位变化,可以实现数据的传输。

SCI串口通信一般使用异步传输模式,即数据按照一个位一个位地传输,每个位之间使用起始位和停止位进行分隔。

在SCI串口通信中,每个数据位通常是8位或9位。

其中,8个数据位中的7个用于传输数据的真正内容,而最高位为校验位。

校验位有助于检测数据传输错误,提高数据传输的可靠性。

在接收端,接收器会比对接收到的校验位和传输过程中计算得到的校验位,以检测并纠正任何可能的错误。

除了数据位外,SCI串口通信还使用两个控制信号:RTS(请求发送)和CTS(清除发送)。

RTS信号由发送端控制,用于请求发送数据。

而CTS 信号由接收端控制,用于指示接收端是否准备好接收数据。

这两个控制信号的使用可以有效地控制数据的传输速率,避免数据传输丢失或溢出的情况发生。

SCI串口通信可以应用于多种场景中。

例如,它常用于个人电脑与其他外部设备之间的通信,如打印机、调制解调器、数码相机等。

此外,它还可以用于嵌入式系统中,如工业自动化、机器人控制、仪器仪表等。

由于SCI串口通信具有简单、可靠、成本低廉等特点,因此在各种场景下都有广泛的应用。

在SCI串口通信中,还有一些技术细节需要考虑。

首先是波特率的选择,波特率表示数据传输速度,常用的波特率有9600、19200、38400等。

选择合适的波特率能够平衡数据传输速度和系统资源的利用率。

其次是数据格式的设置,包括数据位数、校验位和停止位。

不同的应用场景可能需要不同的数据格式设置,需要根据具体需求进行调整。

sci串行通信接口工作原理

sci串行通信接口工作原理

SCI(Serial Communication Interface)是一种串行通信接口,用于在数字系统中进行串行数据传输。

SCI通常包括发送和接收端,通过串行方式传递数据,它在嵌入式系统和通信领域中被广泛使用。

以下是SCI串行通信接口的基本工作原理:

1.帧结构:SCI通信以帧为单位,每一帧包含了一定数量的比特,通常包括起始位、数据位、奇偶校验位(可选)、停止位等。

这种帧结构有助于接收端正确解析和识别数据。

2.波特率设置:波特率是SCI通信的速率,表示每秒传输的比特数。

在SCI通信中,发送端和接收端必须配置相同的波特率,以确保数据的正确传输。

3.起始位和停止位:为了使接收端能够准确识别帧的起始和结束,通常在每帧的开始设置一个起始位,结束时设置一个或多个停止位。

4.数据传输:数据以二进制形式传输,由发送端按照事先定义好的帧结构进行发送。

接收端在正确配置的情况下,能够识别并解析这些帧,将二进制数据还原为原始数据。

5.同步机制:为确保数据的同步传输,通常在帧的开始设置一个起始位,作为同步信号,帮助接收端正确解析后续的数据。

6.协议选择:在SCI通信中,数据的传输可以使用不同的协议,例如异步传输和同步传输。

异步通信不需要与时钟同步,而同步通信则需要与外部时钟同步。

总体而言,SCI串行通信接口通过在帧中使用起始位、数据位、停止位等结构,按照事先定义好的协议传输数据。

这种方式具有灵活性和可靠性,适用于许多嵌入式系统和通信场景。

串行通信接口模块(SCI)概要

电气工程学院

Electrical Engineering Institute of NEDU

2020年1月29日星期三

12.2.2 SCI的多处理器通信

1.空闲线多处理器模式(ADDR/IDLE MODE=0)

数据块被块间的时间间隔分开,该时间间隔 比块中的数据帧之间的时间间隔要长,一帧后的 空闲时间(10个或更多个高电平位)表明了一个 新块的开始。如下页图所示:

Electrical Engineering Institute of NEDU

TXD RXD

从机n

2020年1月29日星期三

12.2.1串行通信接口可编程的数据格式 串行通信接口的NRZ数据格式包括:

一个起始位; 1~8个数据位; 一个奇/偶校验位 或 无奇/偶校验位; 1~2个停止位; 一个用于区分数据和地址的额外位。

BRR=24000000/(9600*8)–1=311.5

取138H 所以波特率选择寄存器设置为 SCIHBUAD=01H,SCILBAUD=38H

电气工程学院

Electrical Engineering Institute of NEDU

2020年1月29日星期三

12.3串行通信接口控制寄存器

第十二章 串行通信接口模块(SCI) Serial Communication Interface

电气工程学院

Electrical Engineering Institute of NEDU

2020年1月29日星期三

12.1串行通信接口概述

SCI模块支持异步通信;

SCI接收器和发送器是双缓冲的,各自有独立 的使能位和中断标志位。可以独立工作,或全 双工方式工作;

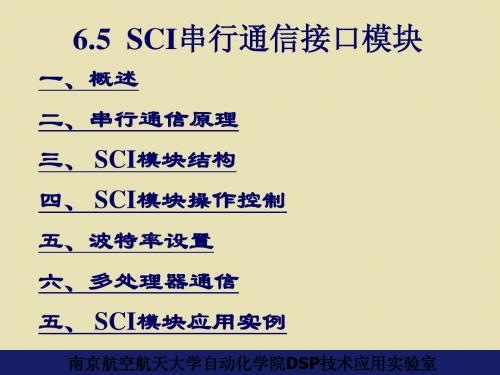

6.5_串行通信接口SCI模块080408

接收缓冲器/间断中断使 能

0

TX INT ENA

发送缓冲器中断使能控 制TXRDY标志引起的 中断

0-禁止TXRDY中断; 1-使能TXRDY中断

南京航空航天大学自动化学院DSP技术应用实验室

(4)SCI优先级控制寄存器SCIPRI 规定SCI发送和接收中断的优先级以及 SCI模块在仿真挂起时的操作.

2. SCI接收操作 ⑤接收器继续接收下一帧数据,检测起始位, 重复上述操作。 ⑥若第二帧数据尚未接收完毕(时刻6), RXENA=0,则将这一帧数据全部接收完毕后再 停止,但RXSHF中的数据并不传送到SCIRXBUF 中。

南京航空航天大学自动化学院DSP技术应用实验室

四、 SCI操作控制

3. SCI错误处理操作

7052h

SCIHBAUD

SCI波特率选择寄存器高8位

7053h

7054h

SCILBAUD

SCICTL2

SCI波特率选择寄存器低8位

SCI控制寄存器2

保存波特率控制数据低8位

发送中断使能,接收缓冲器/ 间断中断使能,发送准备好 标志和发送空标志。 存放7个接收状态标志

7055h

SCIRXST

SCI接收状态寄存器

四种错误:间断错误、奇偶性错误、溢出错误和帧错 误 ① 数据帧错误(Framing error):若超过一段时间 后仍收不到期待的停止位。 发生数据帧错误时,FE(SCIRXST.4)置位。 ②奇/偶校验错误(Parity error):检测接收到的数 据中1的个数是否正确,用于有限差错检测。 发生奇偶校验错误时,PE(SCIRXST.2)置位。

南京航空航天大学自动化学院DSP技术应用实验室

2. SCI模块的主要部件

串行口SCI

串行通信接口SCI 串行通信接口

SCI同步方式: 同步方式: 同步方式 以数据格式以及发收双方时钟相同设置进行同步。 以数据格式以及发收双方时钟相同设置进行同步。 主从机具有相同时钟周期(波特率) 主从机具有相同时钟周期(波特率)在特定数据格式下收发 数据可以同步(起始位 数据位 校验位+停止位 空闲位) 数据位+校验位 停止位+空闲位 数据可以同步(起始位+数据位 校验位 停止位 空闲位) SCI异步通信可使用半双工或全双工模式通信。在这种 异步通信可使用半双工或全双工模式通信。 异步通信可使用半双工或全双工模式通信 模式下,一个帧包括 个起始位 个起始位、 个数据位 个数据位、 个 模式下,一个帧包括1个起始位、1-8个数据位、1个 可选的奇偶校验位以及1-2个停止位。每个数据占 可选的奇偶校验位以及 个停止位。每个数据占8 个停止位 个SCICLK周期。 周期。 周期

Page 15

识别地址

处理器根据多处理器的模式来识别一个地址字节,例如: 处理器根据多处理器的模式来识别一个地址字节,例如: • 空闲线模式在地址字节前留有一段静空间。数据块之间 空闲线模式在地址字节前留有一段静空间。 个或10个以上连续空闲位 是10个或 个以上连续空闲位,同一帧数据字符间空闲 个或 个以上连续空闲位, 位应小于10个 该模式没有一个附加的地址/数据位, 位应小于 个。该模式没有一个附加的地址/数据位,在 处理包含多于10个字节的数据块的情况下,其效率比地址 处理包含多于 个字节的数据块的情况下, 个字节的数据块的情况下 位模式更高。 位模式更高。 • 地址位模式为每个字节增加一个附加位 地址位 来 地址位模式为每个字节增加一个附加位(地址位 地址位)来 从数据中识别地址。该模式在处理多个小数据块时 从数据中识别地址。 更有效。 更有效。

SCI,SPI,UART三种串行总线协议的区别

SCI,SPI,UART三种串行总线协议的区别SCI (串行通讯接口)模块对其进行控制。

(注:SCI 首先由Motorola 微串口微控制器而得名,SCI 另一种说法是UART 控制器)常用的许多芯片中都包含了SCI ,例如ARM 的S3C2410X 芯片内嵌了3 个串行接口控制器,而Nios等软核芯片则可以用选用UART(RS232) 的IP 对UART 进行控制。

PC 机则常用16650 UART,16750 UART 等控制串口。

--这样说来SCI 只不过属于UART里面比较特殊的一种串行通讯方式了。

确实也只是在飞思卡尔芯片上遇见过。

第一个区别当然是名字:SCI(Serial Communicate Interface:串行通信接口)SPI(Serial Peripheral Interface:串行外设接口)另外曾在一官方datasheet 里面看见这种说法:Serial Parallel Interface:串并行接口UART(Universal Asynchronous Receiver Transmitter:通用异步收发器)第二,区别在电气信号线上:SPI 总线由三条信号线组成:串行时钟(SCLK)、串行数据输出(SDO)、串行数据输入(SDI)。

SPI 总线可以实现多个SPI 设备互相连接。

提供SPI 串行时钟的SPI 设备为SPI 主机或主设备(Master),其他设备为SPI 从机或从设备(Slave)。

主从设备间可以实现全双工通信,当有多个从设备时,还可以增加一条从设备选择线。

如果用通用IO 口模拟SPI 总线,必须要有一个输出口(SDO),一个输入口(SDI),另一个口则视实现的设备类型而定,如果要实现主从设备,则需输入输出口,若只实现主设备,则需输出口即可,若只实现从设备,则只需输入口即可。

UART 总线是异步串口,因此一般比前两种同步串口的结构要复杂很多,一般由波特率产生器(产生的波特率等于传输波特率的16 倍)、UART 接收器、UART 发送器组成,硬件上由两根线,一根用于发送,一根用于接收。

串行通信接口模块(SCI).

Electrical Engineering Institute of NEDU

3. 4.

5.

2018年7月31日星期二

12.1串行通信接口概述 全双工模式下SCI的主要部件

1.

2. 3. 4.

一个发送器(TX)及和它相关的主要寄存器; 一个接收器(RX)及和它相关的主要寄存器; 一个可编程的波特率发生器; 控制和状态寄存器。

电气工程学院

Electrical Engineering Institute of NEDU

2018年7月31日星期二

12.2.2 SCI的多处理器通信

地址字节的识别 空闲线模式在地址字节前留有一定长度的 空闲空间, 这种模式对于大数据块传输更有效。 地址位模式在每帧中加入额外地址/数据位, 这种模式对于小数据块传输更有效。

第十二章 串行通信接口模块(SCI) Serial Communication Interface

电气工程学院

Electrical Engineering Institute of NEDU

2018年7月31日星期二

12.1串行通信接口概述

SCI模块支持异步通信; SCI接收器和发送器是双缓冲的,各自有独立 的使能位和中断标志位。可以独立工作,或全 双工方式工作; SCI对接收到的数据进行间断检测,奇偶校验, 越限和帧出错的检查; 数据传输速度可编程为65535种方式;

电气工程学院

Electrical Engineering Institute of NEDU

2018年7月31日星期二

12.2.2 SCI的多处理器通信

空闲线模式下有两种方法可传送块的开始信号

1.

在前一块的最后一帧的数据传送与新块的地址 帧传送之间留出10位或更多位的空闲时间。 首 先 将 发 送 唤 醒 位 TXWAKE 置 1 , 然 后 再 向 SCITXBUF 写入任意一个数据,这样可以在数 据线上产生11位的空闲时间。

异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线

异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线(USB)等,这些总线在速度、物理接口要求和通信方法学上都有所不同。

本文详细介绍了嵌入式系统设计的串行总线、驱动器和物理接口的特性,并为总线最优选择提供性能比较和选择建议。

由于在消费类电子产品、计算机外设、汽车和工业应用中增加了嵌入式功能,对低成本、高速和高可靠通信介质的要求也不断增长以满足这些应用,其结果是越来越多的处理器和控制器用不同类型的总线集成在一起,实现与PC软件、开发系统(如仿真器)或网络中的其它设备进行通信。

目前流行的通信一般采用串行或并行模式,而串行模式应用更广泛。

微处理器中常用的集成串行总线是通用异步接收器传输总线、串行通信接口、同步外设接口(SPI)、内部集成电路(I2C)和通用串行总线,以及车用串行总线,包括控制器区域网(CAN)和本地互连网(LIN)。

这些总线在速度、物理接口要求和通信方法学上都有所不同。

本文将对嵌入式系统设计的串行总线、驱动器和物理接口这些要求提供一个总体介绍,为选择最优总线提供指导并给出一个比较图表(表1)。

为了说明方便起见,本文的阐述是基于微处理器的设计。

串行与并行相比串行相比于并行的主要优点是要求的线数较少。

例如,用在汽车工业中的LIN串行总线只需要一根线来与从属器件进行通信,Dallas公司的1-Wire总线只使用一根线来输送信号和电源。

较少的线意味着所需要的控制器引脚较少。

集成在一个微控制器中的并行总线一般需要8条或更多的线,线数的多少取决于设计中地址和数据的宽度,所以集成一个并行总线的芯片至少需要8个引脚来与外部器件接口,这增加了芯片的总体尺寸。

相反地,使用串行总线可以将同样的芯片集成在一个较小的封装中。

另外,在PCB板设计中并行总线需要更多的线来与其它外设接口,使PCB 板面积更大、更复杂,从而增加了硬件成本。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4

计算机通信接口

5

6.2 SCI模块

主要特点:

串行通信接口(SCI-Serial Communication Interface) F2812包含两个SCI接口,记做SCIA和SCIB SCI是一种异步串行通信接口,即通常所说的UART SCI支持16级接收和发送FIFO,有助于减少CPU的开销 如果不使用FIFO时,SCI接收器和发送器采用两级缓冲方式 SCI可工作于半双工或全双工模式(RS485/422) 两种多处理器通信模式:空闲线与地址位多处理器模式 为保证数据的完整性,SCI模块对接收到的数据可以进行间 断、奇偶、超限和帧错误检测。

+5V~+15V 规定为逻辑 “0”

23

RS-232接口的硬件连接

RS232的信号定义: TXD/RXD : 是一对数据线,TXD称发送数据输出,RXD称接收数据输入,当 两台计算机以全双工方式直接通信时,双方的这两根线应交叉连接。 GND: 所有的信号都要通过信号地线构成回路。

其余为联络(握手信号)信号线.

第四讲 内容回顾

1、DSP开发系统组成 1)硬件开发工具;2)软件开发工具;3)DSP应用板。

2、DSP最小系统 1)DSP芯片;2)时钟电路;3)电源与复位电路; 4)JTAG仿真接口。 3、人机接口 1)输入:键盘、开关、按钮等; 2)输出:LED、LCD等

1

DSP原理及其应用技术

串行通信接口(SCI)

同步通信:发送器和接收器通常使用同一时钟源来同步。方法是在发送器 发送数据时同时包含了时钟信号,接收器利用该时钟信号进行接收。

异步通信:收发双方的时钟不是同一个时钟,是由双方各自的时钟实现数 据的发送和接收。但要求双方使用同一标称频率,允许有一定偏差。 同步方法:要正确传输字符,准确读取每一位是必须用各自的时钟同步的, 为克服不同时钟的偏差,每个字符都有一个起始位进行同步。

6)TXENA=0,禁止发送数据,SCI继续完成当前字符的发送; 7)第二个字符发送完成后,发送器变空,TXEMPTY=1。

CPU

SCITXBUF

TXSHF

SCITXD

12

SCI的中断

SCI通信过程可以使用中断方式或查询方式控制接收器和发送器的工作; 发送器和接收器有独立的中断使能位(TX INT ENA、RX/BK INT、RX ERR INT ENA). 当中断被屏蔽时,但标志位仍然有效,可以反映发送和接收状态; 发送器有一个SCITXBUF空标志(TXRDY=1),接收器有3个中断标志:

SCI波特率= LSPCLK

BRR+1= LSPCLK

(BRR+1)×8

SCICLK×8

注意:如果BRR=0,则波特率=LSPCLK/16. BRR--Baud-Select Register

SYSCLKOUT/4

15

SCI多处理器通信

在同一条串行连线上,多处理器通信模式允许一个处理器 (主机)向串行线上其它处理器(从机)发送数据。

13

SCI的中断(续)

2、接收器/间断中断:

如果置位RX/BK INT ENA (SCICTL2.1), 则下列条件之一产生接收器中断: 1)SCI接收到一个完整的帧,并将RXSHF中的数据送SCIRXBUF,就会产生 接收器中断,同时将RXRDY置位(SCICTL2.6); 2)间断检测条件发生(在一个缺少的停止位后,SCIRX保持10周期的低电 平)。该操作将BRKDT置位,并产生中断。

如何识别地址字节? SCI的两种模式均支持多处理器通信。

17

空闲线多处理器模式

数据块被各数据块间的空闲时间分开;

一帧空闲时间(10位或更多位个高电平)表示数据块的开始;

空闲时间

ADDR/IDLE MODE=0

18

空闲线多处理器模式

块起始信号的产生:

方法一:人为地在两个数据块间增加10或更多位的空闲时间。

19

地址位多处理器模式 地址位多处理器协议中,每帧的最后一个数据位后有一个附加的地址位;

数据块的第一帧的地址位设置为1,其余帧的地址位为0; 数据传输与数据块间的空闲周期无关。

ADDR/IDLE MODE=1

20

地址位多处理器模式 TXWAKE=1发送地址 TXWAKE=0发送数据

数据块发送:

PC机1

RXD 2 TXD 3 GND 5 DCD 1 DTR 4 DSR 6 RTS 7 CTS 8

PC机2 双绞线:小于50英尺

2 RXD 3 TXD 5 GND 1 DCD 4 DTR 6 DSR 7 RTS 8 CTS

DCD 1

RXD TXD DTR GND

2 3 4 5

6 DSR

7 8 9

3、 在接收器错误中断服务子程序中,可以检测错误条件: 1)FE:当检测不到一个期望的停止位时,帧错误标志置位; 2)OE:在前一个字符被CPU读取前,有新的字符送到SCIRXBUF中时,置 位超时错误标志,此时前一个字符被覆盖; 3)PE:当接受字符中1的个数和它的奇偶校验位之间不匹配时(含地址位), 且校验模式被使能时,奇偶校验错误标志置位。

一条串行线上每刻只能有一个节点发送数据(发送使能控 制),但可以多个节点同时接受数据。 1、地址字节

发送节点发送信息的第一个字节是地址字节(各个从机的地址预先定义 好),所有接受节点都读取该地址字节。只有地址字节与接受节点的地址 字相符,才能接受数据,否则等待下一个地址字节。

2、Sleep位 (接收器休眠位)

较高,通常应用于11个或更少字节的数据块传送。而数据块较 大时推荐使用空闲线模式。

21

SCI的增强特性

SCIFIFO描述 发送器与接收器各有16级FIFO,有3个专门的寄存器控制; 复位时,SCI工作于标准模式,禁止FIFO功能。

自动波特率检测 自动检测SCI通信的波特率,并刷新BRR寄存器。

错误标志位不能被直接清除,只能通过软件复位或系统复位来清除。 14

SCI的波特率计算

波特率:串行通信过程每秒钟传送的二进制脉冲数目,单位: bit/s (位/秒) 串行时钟SCICLK由低速外设时钟LSPCLK和波特率选择寄存器确定;

SCI使用16位波特率选择寄存器,可以设定为64K种波特率;

连接到串行总线上的所有处理器都将SCI Sleep位置1,这样只有检测到 地址字节后才会中断。当数据块地址与用户软件设置的处理器地址相符时, 用户必须清除Sleep位,以便SCI能够在接受每个数据字节时产生中断。

16

SCI多处理器通信

多处理器模式下,接受步骤如下: 接受地址块时,SCI端口被唤醒并申请中断,读取地址块 的第一帧,该帧包含目的处理器的地址; 比较接受的地址字节与内存中存放的器件地址; 如果二者一致,则编程使CPU清除SLEEP位,并读取数据 块中各个数据帧;否则,退出接受子程序并保持SLEEP置位, 直到下一个地址块的开始才接受中断。

1)发送地址帧:TXWAKE位置1,并写适当地地址值到SCITXBUF寄存器; 这样串行总线上的其它微处理器会读取该地址。 2)发送数据帧:将TXWAKE位清零,然后向SCITXBUF中写入要发送的第 一个数据; 3)依次发送其余的数据帧,直至整个数据块发送完毕。

提示: 地址位模式下数据块间不需要等待,传输小数据块时效率

RTS CTS RI

DBቤተ መጻሕፍቲ ባይዱ9型连接器

24

半双工RS485通信

RS -485采用平衡线路,每个信号都有专用的导线对,其中一根导线上的 电压等于另一根导线上的电压取反,测量的是电压差。可以消除共模噪声 的影响,不受接地电势差异的影响。 • VA-VB > 0.2V 逻辑“1” • VA-VB >- 0.2V 逻辑“0”

1)接收器数据准备好(RXRDY=1); 2)接收器错误标志位(RX ERROR=1); 3)如果SCIRXD引脚连续保持至少10个低电平,则产生一个间断条件 ( BRKDT =1)。

1、发送器中断:

1)置位TX INT ENA(SCICTL2.0); 2)只要SCITXBUF中数据传送到TXSHF中,就会产生发送器中断; 3)该操作将TXRDY置位(SCICTL2.7),表示CPU可以继续写数据。

1)置RXENA=1(SCICTL1.D0),使能接收器接收器数据; 2)数据到达SCIRXD引脚后,检测起始位(SCI自动实现); 3)数据从RXSHF寄存器移位到接收缓冲寄存器(SCIRXBUF),

产生一个中断请求,同时接收器数据准备好标志RXRDY=1; 4)用户程序读取SCIRXBUF寄存器,标志位RXRDY自动清零; 5)数据的下一个字节到达SCIRXD引脚,检测到起始位; 6)RXENA=0,禁止接受数据。继续向RXSHF装载数据,但不送入SCIRXBUF。

方法二: 利用TXWAKE位产生11位的空闲时间 1)首先置位TXWAKE(SCICTL1.3),控制数据发送特征; 2)写一个数据字节(内容不重要)到SCITXBUF,发送一个

块开始信号( 11位的空闲时间); 3)写一个新的地址到SCITXBUF,当TXSHF再次空闲后, SCITXBUF内容送TXSHF,TXWAKE被清零; 4)随后依次发送各个数据帧。

6.1 计算机通信概述 6.2 SCI串行通信接口 6.3 标准串行通信总线 6.4 SCI编程举例

2

6.1 计算机通信概述

计算机间或计算机与外部设备间交换信息,称为计算机通信。

计算机通信方式:1)串行通信;2)并行通信。

并行通信:一般包括8条数据线,几条控制线和状态线。特点 是传输速度快,但通信距离短、传输线多。 例如XINTF、并行打印机接口、仪器仪表用IEEE 488总线等。

CPU SCIRXBUF

每个字符6个数据位

RXSHF