第11章 DSP串行通信接口SCI

DSP课件-SPI串行外设接口

传输速率较很高,可达75M×16=1200Mbps 信号线多(DB8/16,AB等) 限用于板级扩展外设的输入/输出接口。

4

SPI模块的特点与信号

F281x包含一个四线制SPI接口,可工作于全双工模式 数据长度:1~16位可编程 波特率:126种可编程 可同时进行发送和接收操作

SPI中断使能位(SPICTL.0):1-使能中断,0-禁止中断 当中断使能置位,且满足中断条件时,产生相应的中断。 SPI中断标志位(SPISTS.6):只读,由硬件设置。 指示SPI接收器中已经存放字符可以被读取或已完成指定长度的数据发送。 该位置位时已接收数据送入SPIRXBUF,当DSP读SPIRXBUF中的数据后 自动清除中断标志。

SPICCR.3~SPICCR.0确定了字符的位数(1~16); 当数据写入SPIDAT和SPITXBUF寄存器时必须左对齐; 当数据从SPIRXBUF读取时,必须是右对齐; SPIRXBUF中包含最新接收的字符,以及上次接收且已移位到左边的位。 例1:发送数据长度为1,SPIDAT当前值为737BH,数据格式见下图。

讲授人:奚伯齐 Email: 2015dsp@ 密码:2015dsp

SPI串行外设接口

Serial Peripheral Interface(SPI) 1 SPI模块概述 2 SPI的工作原理 3 通过SPI接口扩展外设 4 软件编程举例

2

1 SPI模块概述

SPI与SCI有什么区别?

两种工作方式:主/从工作方式 4种时钟模式:由极性和相位控制 接口方式:中断或查询

4个外部引脚 只能以 16位方 式访问

12个寄存器

同步时钟

5

模 块 框 图

串行通信接口SCI

串行通信分为同步通信和异步通信。

串行通信接口都具有发送引脚TXD和接收引脚RXD,它们是TTL平电。

如果要利用这两个引脚与外界实行异步通信,必须将TTL电平转化为RS-232电平。

SCI是一种全双工异步串行通信接口,主要用于MCU与其他计算机或设备之间的通信,几个独立的MCU也能通过SCI实现串行通信,形成网络。

从编程角度看,先设定好波特率,通信格式,是否校验,是否允许中断等。

接着发送数据时,先检查相应的标志位是否允许发送数据,如果可以,则把数据放入SCI数据寄存器即可,剩下的工作芯片自动完成:将数据从SCI数据寄存器送到发送移位寄存器,硬件驱动将发送移位寄存器里的数据按规定发送到发送引脚TXD,供对方接收。

接收时,数据逐位从接收引脚RXD进入到接收移位寄存器,当收到一个完整字节时,芯片会自动将数据送到SCI数据寄存器,并置相应的标志位,我们就可以根据标志位的情况来读取数据了。

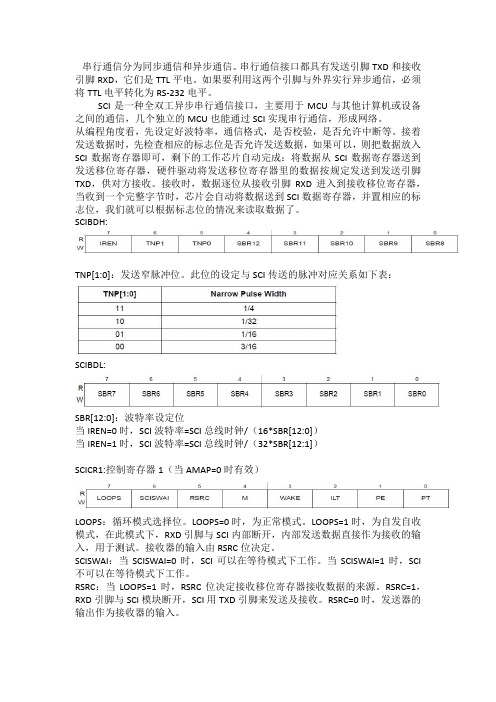

SCIBDH:TNP[1:0]:发送窄脉冲位。

此位的设定与SCI传送的脉冲对应关系如下表:SCIBDL:SBR[12:0]:波特率设定位当IREN=0时,SCI波特率=SCI总线时钟/(16*SBR[12:0])当IREN=1时,SCI波特率=SCI总线时钟/(32*SBR[12:1])SCICR1:控制寄存器1(当AMAP=0时有效)LOOPS:循环模式选择位。

LOOPS=0时,为正常模式。

LOOPS=1时,为自发自收模式,在此模式下,RXD引脚与SCI内部断开,内部发送数据直接作为接收的输入,用于测试。

接收器的输入由RSRC位决定。

SCISWAI:当SCISWAI=0时,SCI可以在等待模式下工作。

当SCISWAI=1时,SCI 不可以在等待模式下工作。

RSRC:当LOOPS=1时,RSRC位决定接收移位寄存器接收数据的来源。

RSRC=1,RXD引脚与SCI模块断开,SCI用TXD引脚来发送及接收。

RSRC=0时,发送器的输出作为接收器的输入。

DSP课件-SCI串行通信接口

CPU

SCITXBUF

TXSHF

SCITXD

13

SCI的中断

SCI通信过程可以使用中断方式或查询方式控制接收器和发送器的工作; 发送器和接收器有独立的中断使能位(TX INT ENA、RX/BK INT、RX ERR). 当中断被屏蔽时,但标志位仍然有效,可以反映发送和接收状态; 发送器有一个SCITXBUF空标志(TXRDY=1),接收器有3个中断标志:

22

地址位多处理器模式 地址位多处理器协议中,每帧的最后一个数据位后有一个附加的地址位;

数据块的第一帧的地址位设置为1,其余帧的地址位为0; 数据传输与数据块间的空闲周期无关。

ADDR/I多处理器模式

数据块发送:

TXWAKE=1发送地址 TXWAKE=0发送数据

1)接收器数据准备好(RXRDY=1); 2)接收器错误标志位(RX ERROR=1); 3)如果SCIRXD引脚连续保持至少10个低电平,则产生一个间断条件 ( BRKDT =1)。

1、发送器中断:

1)置位TX INT ENA(SCICTL2.0); 2)只要SCITXBUF中数据传送到TXSHF中,就会产生发送器中断; 3)该操作将TXRDY置位(SCICTL2.7),表示CPU可以继续写数据。

1166

中断方式

中断方式:通过中断进行控制SCI的发送和接收数据,必 须使能外设中断、PIE中断和CPU中断。SCIA的发送和接收 中断对应CPU中断的INT9。TXRDY是发送中断标志位,置1 时产生发送中断事件,则响应SCI的发送中断函数。同样, 当接收中断标志位RXRDY置1时,产生接收中断事件,则响 应SCI的接收中断函数。

第7章 串行通信接口(SCI)

第7章串行通信接口(SCI)目前几乎所有的台式电脑都带有9芯的异步串行通信口,简称串行口或COM口。

有的台式电脑带有两个串行口,分别称为COM1、COM2口。

大部分的笔记本电脑也带有串行口。

随着USB接口的普及,串行口的地位逐渐变低了。

但是,作为设备间的一种简便的通信方式,在相当长的时间内,串行口还不会消失。

因为简单且常用的串行通信只需要三根线(发送线、接收线和地线),所以,串行通信可以作为MCU与外界通信的简便方式之一。

大部分嵌入式MCU都具有串行通信接口(Serial Communication Interface,SCI),掌握SCI的编程是学习MCU的重要内容之一。

本章从掌握规范的SCI基本编程角度讨论串行通信编程,把与芯片型号相关内容和与芯片型号无关内容区别开来,便于读者融会贯通与实际应用。

本章7.1、7.2节是与芯片无关的有关串行通信的通用基础知识,只有理解这些基础知识,才能进行串行通信的应用。

7.3、7.4节阐述GP32芯片的SCI模块的编程方法,在此基础上,重点掌握7.5节给出的编程实例。

注意,在汇编程序中,只有初始化子程序与GP32相关,收发程序在整个08系列中是通用的,在C程序中,只有初始化子程序与GP32相关,收发程序对任何芯片是通用的。

当然,要注意头文件SCI.h相关位的定义。

关于串口程序的测试,最好利用教学资料中提供的PC机方的高级语言源程序进行。

根据自己对高级语言的熟悉程度选用VB、C#、VC或其他高级语言。

实际上,掌握一门PC机方的高级语言编程对嵌入式系统开发是必要的。

7.1异步串行通信的基础知识本节简要概括了串行通信中的通常使用的相关基本概念,为学习MCU的串行接口编程做准备。

对于已经了解这方面知识的读者,可以略读本节。

7.1.1基本概念“位”(bit)是单个二进制数字的简称,是可以拥有两种状态的最小二进制值,分别用“0”和“1”表示。

在计算机中,通常一个信息单位用8位二进制表示,称为一个“字节”(byte)。

SCI

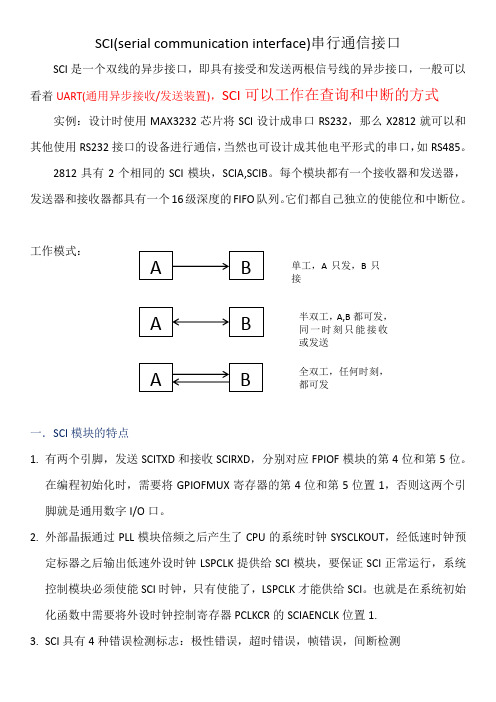

SCI(serial communication interface)串行通信接口SCI 是一个双线的异步接口,即具有接受和发送两根信号线的异步接口,一般可以看着UART(通用异步接收/发送装置),SCI可以工作在查询和中断的方式实例:设计时使用MAX3232芯片将SCI 设计成串口RS232,那么X2812就可以和其他使用RS232接口的设备进行通信,当然也可设计成其他电平形式的串口,如RS485。

2812具有2个相同的SCI 模块,SCIA,SCIB 。

每个模块都有一个接收器和发送器,发送器和接收器都具有一个16级深度的FIFO 队列。

它们都自己独立的使能位和中断位。

工作模式:一.SCI 模块的特点1. 有两个引脚,发送SCITXD 和接收SCIRXD ,分别对应FPIOF 模块的第4位和第5位。

在编程初始化时,需要将GPIOFMUX 寄存器的第4位和第5位置1,否则这两个引脚就是通用数字I/O 口。

2. 外部晶振通过PLL 模块倍频之后产生了CPU 的系统时钟SYSCLKOUT ,经低速时钟预定标器之后输出低速外设时钟LSPCLK 提供给SCI 模块,要保证SCI 正常运行,系统控制模块必须使能SCI 时钟,只有使能了,LSPCLK 才能供给SCI 。

也就是在系统初始化函数中需要将外设时钟控制寄存器PCLKCR 的SCIAENCLK 位置1.3. SCI 具有4种错误检测标志:极性错误,超时错误,帧错误,间断检测A A ABB B单工,A 只发,B 只接半双工,A,B 都可发,同一时刻只能接收或发送全双工,任何时刻,都可发4.具有双缓冲接收和发送功能,接收缓冲寄存器位SCIRXBUF,发送缓冲寄存器为SCITXBUF。

独立的发送器和接收器使得SCI可以工作于半双工或全双工5.可以产生两个中断:SCIRXINT和SCITXINT,即接收中断和发送中断,SCI模块具有独立的发送中断使能位和接收中断使能位,发送和接收可以通过中断方式实现,也可以查询中断方式是实现6.在多处理器模式下,SCI模块具有两种唤醒方式:空闲线方式和地址位方式。

DSP-12章SCI

(2)主程序: .text

_c_int0 SETC INTM CLRC SXM CLRC OVM CLRC CNF LDP #0E0H SPLK #81FEH,SCSR1 SPLK #0E8h,WDCR CALL SCI_INIT LDP #5H SPLK #00H,SCI_FLAG

TXD_LOOP: LDP #5H BIT SCI_FLAG,BIT0 BCND TXD_DATA,TC B WAIT

Clock

波特率选择

RXWAKE

接收唤醒标志

SCIRXST.1

SCIRXST.7.4-2

错误标志 奇偶错 帧出错 超时错

优先级TX

RX优先级

RXSHF

接收移位器

SCIRXD

RXENA(接收使能)

SCICTL1.0

(RX/BRKDT)

INTENA

接收缓冲器

SCI RXRDY

RXBUF

BRKDT

接收中断使能

SCI_RX_END:

CLRC INTM RET

(5)假中断程序: PHANTOM

KICK_DOG RET END

发送:

1:置发送唤醒位为1.TXWAKE=1。 2:将任意字写入SCITXBUF以发送块的开始信号(11位)。

在块住处发送时,该字被忽略,发送11位空闲位且清TXWAKE。 3:将新地地址写入SCITXBUF。

2.地址位多处理器模式(ADD/IDLE MODE=1)

发送: 1:TXWAKE为附加数据位的1,因此置位TXWAKE(地址帧),写地址到

SCILBAVD 5.状态寄存器:SCIRXST:定义:接收唤醒标志[1].错误标志[2,3,4,5]

接收器准备好[6].总错误标志位[7] 6.接收缓冲器:SCIRXBUF 7.仿真接收缓冲器:SCIRXEMU 8.发送数据缓冲器:SCITXBUF 9.优先级控制寄存器:SCIPR1

第11章 MC9S12XS系列串行通信接口模块及其应用实例

11.3 SCI模块寄存器

11.3.5 SCI可选控制寄存器2(SCIACR2)

如果AMAP=1时,读:任何时刻;如果AMAP=1时,写:任何时刻。 BERRM1~BERRM0:位错误模式,这两位组合确定位错误模式的探测 特性,详见表11-4。

BKDFE:间隔探测特性使能位,该位使能允许使用间隔探测电路。 0表示禁用间隔探测电路; 1表示使用间隔探测电路。

接收器帧错误检测;

地址标志唤醒;

奇偶校验检测;

1/16位时间噪声检测。

《MC9S12XS单片机原理及嵌入式系统开发》

11.3 SCI模块寄存器

MC9S12XS128的SCI模块共有11个寄存器,详见表11-1。对于 112引脚的MC9S12XS128,内部有2个SCI模块,分别是SCI0和SCI1, 表11-1中分别列出了SCI0和SCI1两个模块中各寄存器地址。

《

11.3.1 SCI波特率寄存器(SCIBDH,SCIBDL)

SCI波特率寄存器(SCI Baud Rate Registers)用来设置SCI波特率,同 时还用于控制红外调制/解调子模块,由SCI波特率高字节寄存器(SCIBDH) 和SCI波特率低字节寄存器(SCIBDL)组成。该寄存器如图11.2和图11.3所示。 波特率计算公式为

《MC9S12XS单片机原理及嵌入式系统开发》

11.3 SCI模块寄存器

11.3.5 SCI可选控制寄存器2(SCIACR2)

SCI可选控制寄存器2(SCI Alternative Control Register 2,SCIACR2), 如图11.9所示。

《MC9S12XS单片机原理及嵌入式系统开发》

MC9S12XS128内置的SCI模块是全双工、波特率 可编程设置、可编程选择8位数据或9位数据格式的串 行通信接口(简称串口)。本章着重介绍SCI模块的 特性、寄存器功能及设置,并通过一些应用实例和 SCI模块在自主寻迹智能车上的应用,让读者掌握 SCI模块的应用及编程方法。

DSP原理及应用技术第7.3节 串行通信接口(SCI)

TXINT TXINT

7.3 串行通信接口(SCI)

2)SCI自动波特率

SCI模块的增强功能支持硬件上的自动波特率检测逻辑。自动波特率 检测的流程如下:

①使能自动波特率检测模式:设置CDC位(SCIFFCT.13)为1并通过 向ABDCLR位(SCIFFCT.14)写1清除ABD位(SCIFFCT.12)。

7.3 串行通信接口(SCI)

(3)SCI多处理器通信

多处理器通信格式允许一个处理器在同一串行线路中将数据块有 效地传给其它处理器。在一条串行线上每次只有一个处理器发送数据 地址字节: 休眠位: 识别地址字节:

两种多处理器模式的接收顺序如下: 1)在接收一个地址块时,SCI端口被唤醒并请求中断(SCICTL2 寄存器的RX/BK INT ENA位必须使能以发送中断请求)。读取包含目 的地址的第一帧数据。 2)通过中断进入一个软件服务程序,检测即将到来的地址,将 接收到的地址字节与存储在内存中的器件地址进行比对。 3)如果检测结果表明数据块的地址与该设备CPU地址一致,则 CPU清零SLEEP位,并读取数据块的其余部分;如果不是则退出子程序 ,SLEEP仍然保持置位,并且在下一个数据块开始之前不会产生接收 中断。

SCI模块与CPU的连接如图7-29所示。

7.3 串行通信接口(SCI)

1. SCI模块具有以下特征:

➢ 两个外部引脚(不用于SCI通信时,可作为通用I/O口): SCITXD:SCI发送-输出引脚; SCIRXD:SCI接收-输入引脚; ➢ 可编程为多达64K种不同的波特率; ➢ 可编程的数据字格式; ➢ 四个错误检测标志:奇偶校验、溢出、帧错误和间断检测; ➢ 两种多处理器唤醒模式:空闲线和地址位; ➢ 半双工或者全双工操作; ➢ 双缓冲接收或发送功能; ➢ 发送器和接收器操作的完成可以通过中断驱动或者软件查询状态标志来

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SCI模块的结构 11.1.2 SCI模块的结构 模块主要包括以下部件: 模块主要包括以下部件: 发送器(1)发送器-TX SCITXBUF-发送数据缓冲寄存器,存发送数据。 SCITXBUF-发送数据缓冲寄存器,存发送数据。 TXSHF-发送移位寄存器,每次1位送到SCITXD TXSHF-发送移位寄存器,每次1位送到SCITXD 引脚。 引脚。 接收器(2)接收器-RX RXSHF-接收移位寄存器,每次1位将SCIRXD SCIRXD引 RXSHF-接收移位寄存器,每次1位将SCIRXD引 脚上的数据移入。 脚上的数据移入。 SCIRXBUF-接收数据缓冲寄存器, RXSHF接收 SCIRXBUF-接收数据缓冲寄存器,存RXSHF接收 到数据。 到数据。 (3)一个可编程的波特率发生器。 一个可编程的波特率发。 可编程数据位。 数据位 长度为1 可编程停止位 停止位。 (4)长度为1位或2位的可编程停止位。 (5)内部产生的串行时钟。 内部产生的串行时钟。 产生的串行时钟 四个错误的检测标志 错误的检测标志: (6)四个错误的检测标志: 奇偶性错误、超限错误、帧错误、 奇偶性错误、超限错误、帧错误、间断检测 半双工或全双工。 (7)半双工或全双工。 双缓冲接收和发送功能 接收和发送功能。 (8)双缓冲接收和发送功能。 (9)发送和接收操作均可通过中断或查询进行。 发送和接收操作均可通过中断或查询进行。 中断 进行 (10)非归零格式(NRZ)。 10)非归零格式(NRZ)

第11章 串行通信接口(SCI) 11章 串行通信接口( SCI接口模块 接口模块: SCI接口模块:实现与其它外设之间的异步串行数据通 波特率可编程。 信。波特率可编程。 SCI的发送器与接收器都是双缓冲的 各自有工作使能 的发送器与接收器都是双缓冲的。 SCI的发送器与接收器都是双缓冲的。各自有工作使能 中断控制。可工作于全双工模式 全双工模式。 和中断控制。可工作于全双工模式。 11.1 概述 11.1.1 串行通信接口的物理描述 (1)两个I/O引脚:SCIRXD与SCITXD 两个I/O引脚:SCIRXD与 I/O引脚 (2)一个16位的波特率选择寄存器可编程,可得到 一个16位的波特率选择寄存器可编程, 16位的波特率选择寄存器可编程 65536种的不同速率。 65536种的不同速率。 536

11.2 可编程的数据格式 串行口的数据无论是收、发都采用NRZ(非归零) 串行口的数据无论是收、发都采用NRZ(非归零) NRZ(非归零 格式: 格式: • 1个起始位 • 1-8个数据位. 数据位. • 1个或无奇偶校验位 个或无奇偶校验位 • 1-2个停止位

SCI通信模式 11.4 SCI通信模式 SCI异步通信可使用半双工或全双工模式通信。 SCI异步通信可使用半双工或全双工模式通信。在这种 异步通信可使用半双工 模式通信 模式下,一个帧包括1个起始位、 模式下,一个帧包括1个起始位、1-8个数据位、1个 包括 个数据位、 可选的奇偶校验位以及1 个停止位。每个数据占 可选的奇偶校验位以及1-2个停止位。每个数据占8 以及 个SCICLK周期。 SCICLK周期。 周期 接收器在接收到一个有效的起始位后开始工作。一个 接收器在接收到一个有效的起始位后开始工作。 有效的起始位由 有效的起始位由4个连续的内部SCICLK周期的零位来 连续的内部SCICLK周期的零位来 SCICLK 识别。如果任何一个位都不为0 识别。如果任何一个位都不为0,则处理器重新启动 并开始寻找另一个起始位。 并开始寻找另一个起始位。