Cadence 实验

cadence实验报告三实验报告

实验报告三:Cadence实验报告

1. 实验目的

本实验旨在熟悉Cadence软件的使用,并通过设计和仿真一个简单的2输入AND门,学习使用更多的Cadence工具。

2. 实验步骤及结果

2.1 绘制原理图

首先使用Cadence软件新建一个库文件,命名为“And2_lib”,并打开Library Manager工具,如下图所示:

Library Manager

Library Manager

在Library Manager工具中,我们可以进行各种管理操作,包括新建、删除、重命名库文件等操作,还可以查看库文件中的各种信息。

接下来,我们使用Schematic Composer工具绘制2输入AND门的原理图,如下图所示:2-input AND Gate Schematic

2-input AND Gate Schematic

其中,我们使用了以下基本元件:

•Pmosa:NMOS器件

•Nmosa:PMOS器件

•Resistor:电阻器件

•Vdc:直流电源

•Vground:地电源

绘制完成后,使用“Save As”命令将原理图保存为“And2”即可。

2.2 设计Layout布局

在完成原理图设计后,接下来需要对其进行布局设计。

我们首先在Design Manager工具中打开“And2”原理图文件,并使用Create Cell View工具为该原理图新建一个Layout布局,如下图所示:

Create Cell View

Create Cell View

然后,我们进入Virtuoso Layout Editor工具,选中。

实验报告cadence实验报告三篇_082文档

2020实验报告cadence实验报告三篇_082文档EDUCATION WORD实验报告cadence实验报告三篇_082文档前言语料:温馨提醒,教育,就是实现上述社会功能的最重要的一个独立出来的过程。

其目的,就是把之前无数个人有价值的观察、体验、思考中的精华,以浓缩、系统化、易于理解记忆掌握的方式,传递给当下的无数个人,让个人从中获益,丰富自己的人生体验,也支撑整个社会的运作和发展。

本文内容如下:【下载该文档后使用Word打开】PSpiceSimulationExperience620xx0xx21236张双林Workrequirement:pleasereadtheexerciseofpage117fromthespicebook,butsimulat ethedevicemodelparametersandoperationalpointat30degreeand100degree.PleaseRuntheTEMPanalysiswithPspiceandanswerthequestionoft heexercisePleasehandoutae-reportaboutyourworkI.Net-listsandcircuitfigure:Andthenet-listfilegoes:EX3DCAnalysysexapal1.2.MODELMELQNPNBF=100IS=1E-16Q1210MELQRB31200KRC321KVCC30DC5.temp30100.OP.ENDII.Simulationresult:Accordingtotheoutputfile,wecandrawatabletocontrastthediff erence:a.b.III.Conclusion:Withaninspectionofthecircuitparametersindifferenttemperat ures,wecanfindthatthevalueofISchangeslargely,about1000tim es,andGM,about16percent,whileabout500mvdecreasingonVCEcau sed.SothebehaviorofTransistorscanbeaffectedbytemperatures largely.。

cadence 使用 实验二——反相器版图绘制

(2)、建立反相器设计单元(cell)的版图视图(layout view)。 在 主 窗 口 中 FileàNewàcell view, 或 者 Library Manager 窗 口 中 使 用 菜 单 FileàNewàCell View,弹出的窗口中确定 Library Name 为前面新建的设计库(1), Cell Name 可以自己决定,例如我们输入 inv_1 (2),View Name 输入“layout”(3),此 项也可以不填,通过下面的 Tool 下拉菜单选中 Virtuoso,则会自动改变为 layout。 最 后点“OK”(4)。

IM

第二层多晶硅电阻阻挡层

PC poly Cap,用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅

详细的工艺信息请参考设计规则(0.6umDPDMMixedSignalTechnologyTopological DesignRule.pdf),本次实验将会用到的层为 TB、TO、GT、SP、SN、W1、A1、W2、A2

TB

tub,n阱,作为pmos器件衬底

TO

Thin Oxide,有源区,作为mos的源漏区

GT gate,多晶硅1,作为mos栅极

SP

P+注入区

SN N+注入区

W1 接触孔,金属1到多晶硅和有源区的接触孔

A1

铝1,第一层金属

W2 通孔1,金属1和金属2的接触孔

A2

铝2,第二层金属

CP bond pad,pad开孔

本课程中使用csmc双硅双金属混合信号工艺主要的设计层包括tbtubn阱作为pmos器件衬底thinoxide有源区作为mos的源漏区gtgate多晶硅1作为mos栅极spp注入区snn注入区w1接触孔金属1到多晶硅和有源区的接触孔a1铝1第一层金属w2通孔1金属1和金属2的接触孔a2铝2第二层金属cpbondpadpad开孔im第二层多晶硅电阻阻挡层pcpolycap用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅详细的工艺信息请参考设计规则06umdpdmmixedsignaltechnologytopologicaldesignrulepdf本次实验将会用到的层为tbtogtspsnw1a1w2a2这些图层对于我们的设计工具来说是通过工艺文件来进行定义的

Cadence实验指导书

% pwd /home/dong/work % cd/ % pwd / % /cd/home/dong/work % pwd /home/dong/work % cd ~ % pwd /dong/work 3. 查阅目录 查找文本信息使用 Is 命令,基本的显示格式中只包含文件名。例如: % pwd / % Is work group homework 若要显示更多的信息,可以用 Is 的-1(长格式)选项, 显示信息包括 7 项,从左至右分别 为:目录内容和显示权限、链接数、文件所有者、文件大小(字节数) 、最后一次的修改日期和时 间、文件名称等,如下所示。 -rwxr----1 bill 6784 Feb 3 10:54 addendum Drw--x--1 bill 367 Mar 15 08:37 balance -rw-r--r-2 bill 9285 Apr 22 15:21 call-125 drwx-----1 bill 294 Jan 18 11:46 deadline -rwxrw---1 bill 8349 Dec 17 08:59 end.odd -rw-rw-rw5 bill 7956 May 24 10:03 first 长格式显示中的每一行字符用于确定此文件是普通文件(-)还是目录(d) 。 4. 创建目录 UNIX 中创建目录的命令是 mkdir(make directory)。例如: % pwd /usr/paul % mkdir news %_ 该命令在/usr/paul 下创建了一个名为 news 的子目录,即/usr/paul/news。 5. 删除目录 删除目录的命令是 rmdir(remove directory)。在删除目录之前必须删除该目录下的所有文 件,然后移到父目录下去,在删除此目录。下面的例子说明如何删除/usr/paul/letters: % cd.. % pwd /usr/paul % rmdir letters %_

cadence实验报告

实验报告实验项目名称:基于TI MSP430的低功耗低数据量的小型通信系统实验地点:指导教师:学生姓名:学号:一、实验原理:利用cadence软件制作流程,即基于TI MSP430的低功耗低数据量的小型通信系统的设计进行原理图的绘制,按对应的芯片手册进行封装的制作以及进行PCB的布局布线等操作,以及生成Gerber制造文件。

二、实验目的:熟悉cadence软件的使用方法,掌握综合设计过程中所必需的电路原理图绘制、PCB绘制和电路仿真的基本技能及整个流程的规范。

并通过一个基于TI MSP430的低功耗低数据量的小型通信系统设计把握利用cadence软件进行PCB绘制详细流程。

三、实验内容:1)基于ORCAD/Capture CIS的电路原理图设计;2)基于PCB Editor的元器件封装设计(焊盘制作)3)基于PCB Editor的PCB布局、布线、及覆铜4)Gerber制造文件生成四、实验器材(设备、元器件):计算机(安装cadence软件平台);五、实验步骤:A. ORCAD设计原理图过程A1、创建元器件符号(1)以MAX8880为例,相关设置:(New Part)(2)原理符号:(Place –>相关选项)(3)同理依次可画出如下元器件的原理符号(由于篇幅有限,仅列出结果)::A2、根据电路设计要求设计原理图(1)以WakeReceiver电路为例放置元器件(Place –>Part)(2)原理图的器件布局(3)完成连线(4)、同理依次画出整个系统的原理图如下:(由于篇幅有限,仅列出结果)A3、顶层top设计如下:(1)、部分设计:(2)、整体设计:A4、Annotate自动编号(1)、自动编号设置(Tools->Annotate)(2)、点击确定之后,原理图上的元器件依次按类型从1开始编号,保证了元器件编号不会重复,为DRC检查和生成网表文件做准备。

A5、DRC(Design Rule Check)电规则和物理规则检查(1)、规则设置如下图(Tools->Design Rules Check):(2)、刚开始检查结果出现一些错误,比如经过排查错误后,DRC检查无错误,意味着可以顺利生成网表文件。

cadence_实验

• 4、vi .cdsinit 在文件的最后一行的上面添加如下 内容(添加内容的前面没有分号) : • load(“/opt/mentor/caliber/lib/caliber.skl”) • load(“/opt/mentor/caliber/lib/caliber.4.3.skl”) • 主要用于版图的验证使用 • 如图所示:

• 接着添加vdd 与gnd

• 添加管脚,使用快捷键p,Pin Names 为in,Direction 为input, Usage 为schematic,然后在原理图编辑窗口空白处点击一下鼠标, 会出现输入管脚in 。

• 使用相同的方法,添加输出管脚out,此时Pin Names 为out, Direction 为output,Usage 为schematic 。

•

• 创建视图单元/原理图(cell view):在主 窗口中Tools->Library Manager,在 Library 中单击 wo(刚才建立的新库),在 Library Manager 窗口,然后选择File->New->Cell View,设置Cell Name为inv,View Name 为Schematic,Tool为ComposerSchematic,点击OK ,弹出Schematic Editing的空白窗口。

一、实验环境搭建

• 1、解压TSMC0.35.tgz 使用命令:tar –xzf TSMC0.35.tgz • 2、新建一个工作目录:mkdir jiang 将用到的工艺文件和 显示文件(在TSMC035/Virtuoso 下面)拷贝至工作目录 jiang下 。 • 工艺文件:035ms.tf 显示文件:display.drf • 3、拷贝IC工具自带的.cdsinit文件到工作目录jiang下面 3 IC .cdsinit jiang • cp /opt/asic_labs/apps/IC5141/tools.lnx86/dfII/cdsuser/.cdsi nit ./ • 这样,在原理图和版图界面中就可以使用快捷键了。

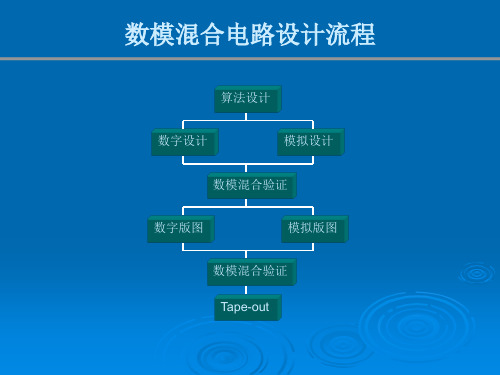

Cadence 实验系列12_数模混合电路设计_spetreVerilog!10

制作顶层文件

混合信号模拟的特点

建立层次文件

操设作置示仿例真环境

仿真

数字设计

模拟设计

2

1制作顶层文件 3

4

建立层次化文件

配置仿真环境 仿真验证

2-1 数字-模拟电路设计

1.数-模电路设计 2.数字电路设计 3. 模拟电路设计

2-1 数字-模拟电路设计

1.数-模电路设计

手工型

顺序型

偶合型

+

配对型

= spetr巢(套l型ock-step)同步法 集成型 = Cadence spetreverilog

框架型

1-1 数模混合模拟的定义

3. 混合信号模拟 Cadence spetreverilog解决方案

混合仿真环境

2.设置模式层次显示

2-4 设置仿真环境

2.设置Analog环境 1.设置仿真器工作模式

2-4 设置仿真环境

2. 配置仿真环境 2.设置引用工艺库

2-4 设置仿真环境

2. 配置仿真环境 3.设置模拟仿真器激励

2-4 设置仿真环境

2. 配置仿真环境 4.设置数字仿真器激励

2-4 设置仿真环境

schemetic

schemetic

Verilog-editor

时钟发生器

计数器

2-1 数字-模拟电路设计

1.数-模电路设计

Verilog

Lib

Counter_1

Clk_1

symbo schem

2-1 数字-模拟电路设计

1.数-模电路设计

1 建立自己的设计库 名字 design_101

2-1 数字-模拟电路设计

cadence实验报告pmos总结

实验主题:cadence实验报告pmos总结实验内容:1. 实验目的:本次实验旨在通过使用Cadence软件对PMOS进行仿真,掌握PMOS的基本原理和特性。

2. 实验原理:PMOS(Positive Metal-Oxide-Semiconductor)是一种场效应晶体管,其工作原理是通过不同电压控制栅极与漏极的电流流动。

当栅极电压高于漏极电压时,PMOS导通;当栅极电压低于漏极电压时,PMOS截止。

3. 实验步骤:3.1 确定PMOS的工作电压:设置不同的栅极电压和漏极电压,观察PMOS的导通和截止情况。

3.2 测量PMOS的电流和电压:记录不同条件下PMOS的电流和电压数值,分析PMOS的工作特性。

4. 实验结果:4.1 PMOS工作电压范围:经过实验测量和仿真分析,确定PMOS 的工作范围为-5V到0V。

4.2 PMOS的电流和电压关系:根据实验数据和曲线图,得出PMOS的电流与电压呈负相关关系,符合PMOS的基本特性。

5. 实验结论:通过本次实验,进一步了解了PMOS的工作原理和特性,并掌握了使用Cadence软件对PMOS进行仿真的方法。

总结:本次实验对于理解PMOS的工作原理和特性具有重要意义,通过实验数据和分析,可以更加深入地理解PMOS的工作机制,为日后的电路设计和工程实践提供重要参考。

由于PMOS具有重要的工程应用价值,因此我们将继续分析PMOS的性能,并深入探讨其在集成电路设计中的实际应用。

6. PMOS的性能分析:6.1 PMOS的漏电流特性:在实际应用中,PMOS的漏电流是一个重要的参数。

漏电流的大小直接影响着电路的功耗和稳定性。

通过进一步的仿真和实验,我们可以测量不同工作条件下的PMOS漏电流,并分析其与温度、电压等因素的关系。

这有助于优化电路设计,降低功耗并提高系统稳定性。

6.2 PMOS的开关特性:除了传统的工作特性外,我们还可以进一步研究PMOS的开关特性。

通过设置不同的控制信号和输入信号,观察PMOS的开关响应时间、延迟特性等,并分析其对集成电路的影响。

课程实验一 Cadence使用基础

IC工艺及版图设计课程实验一一、实验目的:1 掌握Cadence软件的启动方法2 了解原理图编辑器使用方法3 掌握Cadence版图编辑软件的使用方法二、实验软件:Cadence IC 5141 Virtuoso Layout Editor三、实验要求:实验前请做好预习工作,实验后请做好练习,较熟练的使用Cadence软件。

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)实验内容:项目一、Linux系统与Cadence软件介绍1.Cadence软件介绍◎全球最大的EDA公司,产品涵盖电子设计的整个流程,自1991年以来,连续在EDA市场中销售额稳居第一。

◎提供系统级至版图级的全线解决方案,产品包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制IC设计,IC物理验证,PCB设计和硬件仿真建模等。

◎系统庞杂,工具众多,不易入手◎具有广泛的应用支持,全球知名半导体公司与电子系统公司均将Cadence软件作为其全球设计的标准。

2.Cadence 全定制IC设计软件◎Virtuoso Schematic Composer◎Analog Design Environment◎Spectre◎Virtuoso Layout Editor◎Assura◎Dracula & Diva◎Virtuoso Layout Synthesizer自动版图◎ICCragtsman布局工具3.系统环境◎.cshrc:指定Cadence软件和License文件所在路径(用户目录下,隐藏文件)◎.cdsenv:包含Cadence软件的一些环境设置(用户目录下,隐藏文件)◎.cdsinit:Cadence初始化设置(用户目录下,隐藏文件)◎ cds.lib:Cadence调用的设计库文件◎ techfile:工艺文件包含了设计必须的信息,版图设计时必须包含该文件。

Cadence 实验

实验说明

212实验室的电脑,只有F盘能够保存数据,因此要把cadence的工作目 录转移到F盘中的文件夹。具体方法: 在F盘的RedHat_Share中,以自己的学号名建文件夹,如12120036. 然后启动cadence,右键>打开终端,输入如下命令, cd .. cd .. cd mnt cd hgfs cd Redhat_Share cd 14120024 icfb& 注意:一次输一行命令,每输完一行命令之后要敲回车键。以后每次实验 都在该路径下打开icfb&。

2.File>Open…

1.1启动VMware

3.找到redhat所在目录(E:\Redhat),导入redhat

4.单击绿色三角形,启动VMware

1.1启动VMware

5.用户登陆 User:cadence Passward:cadence

1.2启动&退出 IC5141

在桌面点击右键>打开终端>输入:icfb& 出现如图所示的CIW(Command Interpreter Window)窗口。从CIW窗口就可以调用许多工具并完 成许多任务。 CIW>File>Exit.. 可以退出IC5141

2.3复制库

2.4重命名库

选中所要复制的Library Library Manager>Edit>Rename… 右键>Rename… To Library 填入新的Library Name

2.5新建Cell View

选中所要添加Cell View的Library (Category) 输入Cell Name 选择Tools>Ok 不同的Tools对应不同的View Name

优秀的cadence实验报告作业

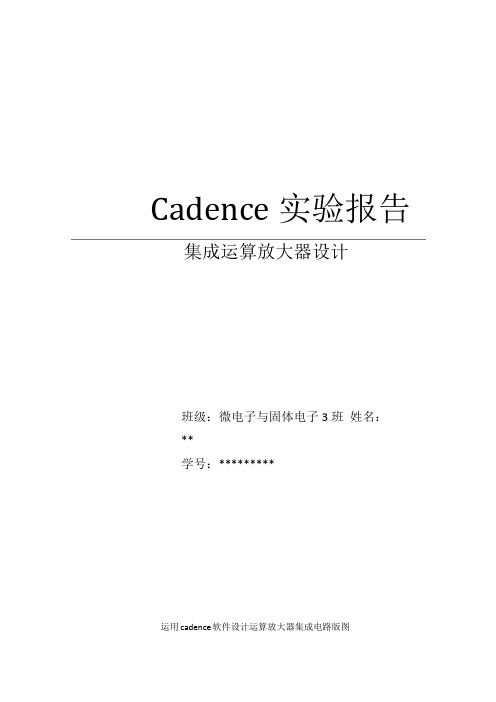

Cadence 实验报告集成运算放大器设计班级:微电子与固体电子3 班姓名:**学号:*********运用cadence 软件设计运算放大器集成电路版图目录一、实验要求 (3)二、实验目的 (3)三、实验内容 (3)1.打开cadence 界面 (3)2.建立Libarary (3)3. 绘制原理图 (4)4. 原理图仿真 (5)5. 版图设计 (7)6. 版图DRC 验证 (9)四、实验总结 (9)实验报告一、实验要求实验为在Cadence 软件环境下自己设计一个放大器,绘制放大器版图并利用Cadence 环境下的Dracular 进行DRC 验证。

要求通过实验熟悉版图设计,可以熟练使用各种快捷键,并在版图设计中使用共质心等设计来减小电路可能产生的二级效应。

二、实验目的通过自行设计一个运算放大器了解集成电路版图设计的流程,从建立一个libarary 和cellview 到可以独立完成一个普通运放的原理图绘制、仿真、版图设计、版图验证。

熟悉cadence 软件的使用,用各种软件环境完成版图。

学会在设计中发现问题解决问题,如调整管子的宽长比来提高增益获得更好的波形,使用共质心画法消除一定二级效应等。

三、实验内容1.打开cadence 界面首先要进入linux 操作环境,之后在linux 下输入指令打开cadence,我用的是实验室的V20z 服务器,在实验室机器桌面上找到Xmanager 进入然后双击Xbrowser 找到对应服务器V20z 点击进入输入帐号密码便可进入linux 操作界面。

打开终端(Terminal)之后输入命令icfb&之后可以看到CIW 窗口,标志正式进入cadence 操作环境。

2.建立Libarary如图1 所示,在CIW 窗口中进入libarary manager,依次点击file-New-Libarary 即可进入新建libaray 窗口,匹配一个工艺库后就能建立一个自己的Libarary,我用的是0.18um 的工艺。

Cadence实验

实验报告要求:1、封面要求:集成电路设计技术实验报告专业、学号、姓名2、正文要求:要求有以下几项:A、实验名称B、实验目的C、实验步骤D、出现问题及解决方法E 时间试验1名称:Candence软件操作准备试验目的:了解熟悉虚拟机的概念、linux常用命令;熟练操作文件的挂载,虚拟机以及Candence 的启动。

试验步骤:熟悉相关概念,启动虚拟机,建立自己的文件夹,挂载库“csmc06lib_ver4”以及文件夹“models”并拷贝到自己建立的文件夹中;在自己建立文件夹的路径下启动Candence。

出现问题及解决:虚拟机:虚拟机(VM)是支持多操作系统并行运行在单个物理服务器上的一种系统,能够提供更加有效的底层硬件使用。

在虚拟机中,中央处理器芯片从系统其它部分划分出一段存储区域,操作系统和应用程序运行在“保护模式”环境下。

在一台电脑上将硬盘和内存的一部分拿出来虚拟出若干台机器,每台机器可以运行单独的操作系统而互不干扰,这些“新”机器各自拥有自己独立的CMOS、硬盘和操作系统,你可以像使用普通机器一样对它们进行分区、格式化、安装系统和应用软件等操作,还可以将这几个操作系统联成一个网络。

在虚拟系统崩溃之后可直接删除不影响本机系统,同样本机系统崩溃后也不影响虚拟系统,可以下次重装后再加入以前做的虚拟系统。

虚拟机以及Candence的启动见计算机中拷贝的相关资料。

文件的挂载:就是将windows操作系统下的文件共享到linux操作系统中,见计算机中拷贝的相关资料。

本实验将windows下的库“csmc06lib_ver4”共享到linux中,并拷贝到自己建立的目录中。

实验一虚拟机以及Candence的启动1、点击桌面“VMare Workstation”的图标,进入VMare Workstation工作界面。

2、点击菜单“file”中的子菜单“open”,找到虚拟机的安装路径。

3、路径找到后,点击文件名为“red hat linux”的虚拟机文件,然后点击“打开”。

实验一、Cadence软件操作步骤

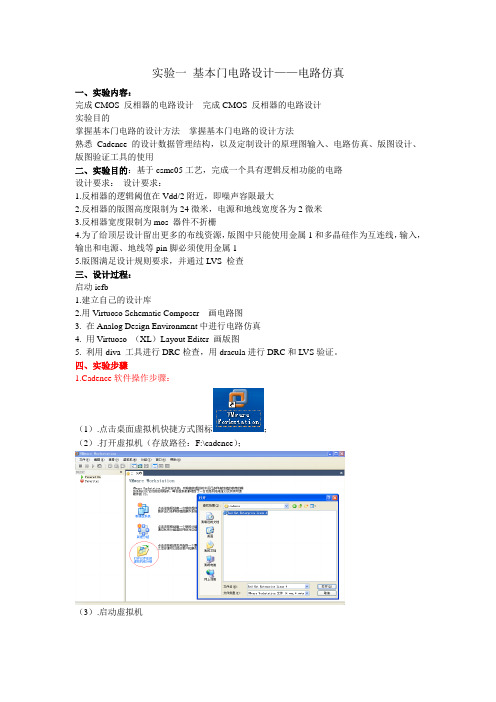

实验一基本门电路设计——电路仿真一、实验内容:完成CMOS 反相器的电路设计完成CMOS 反相器的电路设计实验目的掌握基本门电路的设计方法掌握基本门电路的设计方法熟悉Cadence 的设计数据管理结构,以及定制设计的原理图输入、电路仿真、版图设计、版图验证工具的使用二、实验目的:基于csmc05工艺,完成一个具有逻辑反相功能的电路设计要求:设计要求:1.反相器的逻辑阈值在Vdd/2附近,即噪声容限最大2.反相器的版图高度限制为24微米,电源和地线宽度各为2微米3.反相器宽度限制为mos 器件不折栅4.为了给顶层设计留出更多的布线资源,版图中只能使用金属1和多晶硅作为互连线,输入,输出和电源、地线等pin脚必须使用金属15.版图满足设计规则要求,并通过LVS 检查三、设计过程:启动icfb1.建立自己的设计库2.用Virtuoso Schematic Composer 画电路图3. 在Analog Design Environment中进行电路仿真4. 用Virtuoso (XL)Layout Editer 画版图5. 利用diva 工具进行DRC检查,用dracula进行DRC和LVS验证。

四、实验步骤1.Cadence软件操作步骤:(1).点击桌面虚拟机快捷方式图标;(2).打开虚拟机(存放路径:F:\cadence);(3).启动虚拟机(4).单击右键,Open Teminal,弹出终端对话框,输入Cadence启动命令icfb&(&是后台运行的意思)。

2.. 新建一个库建立自己的Design Lib第一步:CIW-> Tools-Library manager第二步:File-New弹出“New Library ”对话框,在“Name”项填写要建的design lib的名字,这里是“lesson1”,选择“Attach to an existing techfile”第三步:弹出”Attach Design Library to Technology File”对话框,在“Technology Library”中选择st023.新建一个电路图(1)File->New->Cellview(2)弹出“Create New File”对话框,“Library Name”项选择“lesson1”“Cell Name”项填入”inv”,“Tool”项选择”Composer-Schematic”“Tool”项确定后, 相应的“View Name”项会出现内容因而无需输入”,点击“OK”后就进入Virtuso Schematic。

cadence实验报告三篇_实验报告_

cadence实验报告三篇篇一:Cadence PSpice实例(实验报告) 6PSpice Simulation Experience 620xx0xx21236 张双林Work requirement :please read the exercise of page 117 from the spice book, but simulate the device model parameters andoperational point at 30 degree and 100 degree.Please Run the TEMP analysis with Pspice and answer the question of the exercise Please hand out a e-report about your work I.Net-lists and circuit figure :And the net-list file goes :EX3 DC Analysys exapal1.2.MODEL MELQ NPN BF=100 IS=1E-16 Q1 2 1 0 MELQ RB 3 1 200K RC 3 2 1K VCC 3 0 DC 5 .temp 30 100 .OP .END II. Simulation result :According to the output file, we can draw a table to contrast the difference:a.b.III. Conclusion:With an inspection of the circuit parameters in different temperatures, we can find that the value of IS changes largely, about 1000 times, and GM, about 16 percent, while about 500mv decreasing on VCE caused. So the behavior of Transistors can be affected by temperatures largely.篇二:Cadence报告Cadence2-10进制加减计数器设计报告一、实验目的:1、掌握2-10进制加减CMOS计数器的逻辑设计;2、了解和掌握使用Cadence进行集成电路的设计过程。

cadence实验:PMOS、NMOS设计步骤

cadence实验:PMOS、NMOS设计步骤PMOS、NMOS 版图设计尺⼨参考说明:数字1、2、3……代表画版图时,第⼀层、第⼆层、第三层……或说成第⼀步、第⼆步、第三步……,⼀步⼀步做下来。

⼀、PMOS版图有关尺⼨参考1、THIN (薄氧化层):与DIFF(扩散区/有源区)等价,在画版图时可以⽤DIFF代替。

长度3.4 宽度1.2 (默认单位um)2、GPOL Y:多晶硅导电层做mos管的栅极,可以⽤POL Y1代替,也可以做互连线。

长:2.4 宽:0.4 离有源区(即上⾯的THIN)左边缘1.5u ,⽐有源区上下各长出0.6u3、CONT:引线孔,连接⾦属与多晶硅/有源区,第⼀层⾦属的接点。

⼤⼩0.4*0.4 离有源区上边缘0.4 左边缘0.34、METAL1:第⼀层⾦属,⽤于⽔平布线,如电源和地,器件之间的连接必须依靠它。

⼤⼩:0.8*0.8 离CONT各0.25、THIN(或DIFF):⼤⼩1.0*1.0 离CONT各0.3 , 或离METAL1 各0.16、PPIMP (或PIMP):P型注⼊掩膜。

长:4.0 宽:1.8 离有源区上边缘0.3 ,离有源区左边缘0.37、NWELL:N阱,不仅⽤在制造P型器件,常在隔离的时候也看到它。

长6.5宽5.7 ,离PPIMP 左边缘1.2 ,离PPIMP 上边缘2.78、再另外做⼀个节点:CONT(0.4*0.4),METAL1(0.8*0.8),THIN (1.0*1.0)在已经画好图形的上⽅,CONT 离PPIMP 上端1.35 ,离NWELL 左端1.8 9、在新节点上加⼀个NPIMP(或NIMP):N型注⼊掩膜,⼤⼩为1.7*1.7 ,离THIN 各0.35⼆、NMOS版图有关尺⼨参考1、THIN :长3.4 宽0.42、GPLOY :与PMOS 相同离有源区(即上⾯的THIN)左边缘1.5u ,⽐有源区上下各长出0.6u3、CONT :0.4*0.4 ,离有源区上边缘0.3 ,左边缘0.34、METAL1 :与PMOS 相同5、THIN :与PMOS 相同6、NPIMP :长4.0 宽1.6 离有源区上边缘0.3 ,离有源区左边缘0.37、再另外做⼀个节点:CONT(0.4*0.4),METAL1(0.8*0.8),THIN (1.0*1.0)在已画好图形的下⽅,CONT 离NPIMP 下端1.15 ,离NPIMP 左端0.6 8、在新节点上加⼀个PPIMP:⼤⼩1.7*1.7 离THIN 各0.35第三部分:画⼀个反相器时要做⼀个输⼊引脚1、GPOL Y:⼤⼩为1.6*1.6 (⼤⼩可以随意),离PMOS 的NWELL 下边缘0.7u(距离可以随意),此线框进⼊PMOS与NMOS 相连的GPOL Y 深度为0.2 。

CADENCE实验报告

收集相关电路设计资料,了解实验原理和电路设计要求。

实验操作流程制定

根据实验目的和要求,制定详细的实验操作流程,确保实验顺利 进行。

电路设计

01

02

03

电路原理图绘制

使用CADENCE软件绘制 电路原理图,确保电路设 计正确无误。

元器件选型与布局

根据电路设计需求,选择 合适的元器件,并进行合 理的布局,以提高电路性 能。

实验细节

在实验过程中,我对一些细节问题处理不够得当,影响了 实验结果。未来应更加注重实验细节,确保每一步操作的 准确性。

对未来实验的展望

拓展实验内容

01

希望未来能够进一步拓展实验内容,涵盖更多的CADENCE软件

功能和技术领域。

加强理论结合

02

希望能够加强理论与实践的结合,使实验内容更加丰富和有意

Cadence

Palladium

这是一个高保真度模拟器,用于 在数字和模拟混合信号IC设计中 进行精确仿真。

Cadence

Encounter

这是一个全面的IC物理验证解决 方案,用于确保设计的正确性和 可靠性。

电路设计基本流程

1. 需求分析

明确设计目标,理解系统需求。

2. 规格制定

定义电路性能参数,如功耗、速度和面积等 。

7. 导出GDSII

将版图导出为GDSII格式,供制造使用。

实验涉及的理论知识

电路分析

数字电路设计

理解电阻、电容、电感等基本元件的 工作原理。

理解逻辑门、触发器等数字电路的基 本设计方法。

模拟电路设计

了解放大器、滤波器等模拟电路的基 本设计方法。

03 实验步骤与操作

实验准备

Cadence实验教程

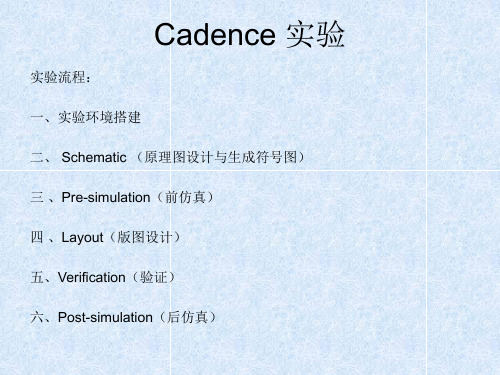

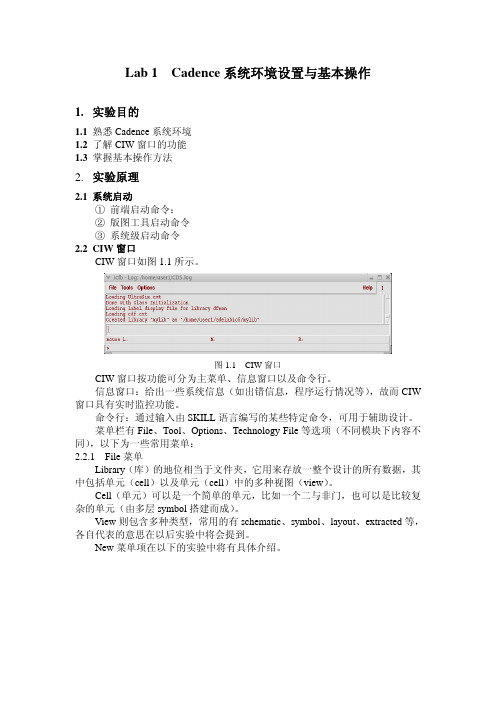

Lab 1 Cadence系统环境设置与基本操作1.实验目的1.1熟悉Cadence系统环境1.2了解CIW窗口的功能1.3掌握基本操作方法2.实验原理2.1系统启动① 前端启动命令:② 版图工具启动命令③ 系统级启动命令2.2CIW窗口CIW窗口如图1.1所示。

图1.1 CIW窗口CIW窗口按功能可分为主菜单、信息窗口以及命令行。

信息窗口:给出一些系统信息(如出错信息,程序运行情况等),故而CIW 窗口具有实时监控功能。

命令行:通过输入由SKILL语言编写的某些特定命令,可用于辅助设计。

菜单栏有File、Tool、Options、Technology File等选项(不同模块下内容不同),以下为一些常用菜单:2.2.1File菜单Library(库)的地位相当于文件夹,它用来存放一整个设计的所有数据,其中包括单元(cell)以及单元(cell)中的多种视图(view)。

Cell(单元)可以是一个简单的单元,比如一个二与非门,也可以是比较复杂的单元(由多层symbol搭建而成)。

View则包含多种类型,常用的有schematic、symbol、layout、extracted等,各自代表的意思在以后实验中将会提到。

New菜单项在以下的实验中将有具体介绍。

图1.2 New Library窗口图1.3 Create New File Library窗口分为Library和Technology File两部分。

Library部分有Name和Directory两项,分别对应要建立的Library名称和路径,Library名称可以自定义。

一般Technology部分选择Don’t need a techfile选项。

如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的工艺文件)或Attach to an existing techfile(使用原有的工艺文件)。

cadence报告

目录一、实验目的二、实验原理三、实验内容及仿真结果四、结果分析五、问题及实验总结一、实验目的1、熟练掌握cadence的操作2、了解IC电路设计的流程3、利用所学设计一个D触发器4、掌握cadence的前仿真5、学会分析仿真结果设计优化三、实验原理D触发器具有置“0”和置“1”的功能。

设Q=0、[D]=1,当CP来到后,触发器将置“1”,触发器各点的逻辑电平如图所示。

在执行置“1”操作时,C门输出高电平;D门输出低电平,此时应保证置“1”和禁止置“0”。

为此,将D=0通过加到C门的输入端,保证C=1,从而禁止置“0”。

同时D=0通过加到F门的输入端,保证F=1,与CP=1共同保证D=0,从而维持置“1”,。

置“0”过程与此类似。

设Q=1、[D]=0,当CP来到后,触发器将置“0”。

在执行置“0”操作时,C 门输出低电平,此时应保证置“0”和禁止置“1”。

为此,将C=0通过加到E门的输入端,保证E=1,从而保证C=0,维持置“0”。

同时E=1通过加到F门的输入端,保证F=0,从而使D=1,禁止置“1”D触发器真值表D Qn Qn^0 0 00 1 01 0 11 1 1其中SD和RD是控制时能端,分别为低电平有效。

三、实验的内容及仿真结果根据实验前准备的原理图在cadence软件中画出,首先要画出原理图中的基本单元三输入与非门如下图,具体的画图步骤参考实验指导书。

然后通过前仿真验证其符合理论的逻辑关系即Y=(AB)ˊ上图因为输入间没有延时出现竞争冒险的现象比较严重,如果再输入间加入延时的话可减小竞争冒险如下图通过验证上述验证得到三输入与非门符合理论结果然后生成cadence库里的symbol继续整个原理图的设计分别得到如下三输入与非symbolDFF原理图将以上原理图通过参数设定仿真在正常工作下的到其波形图为通过cadence波形输出窗口的calculator功能得到其正常工作下的电流为可计算到该情况下功耗W=V·I=接下来的就是测试D触发器的另一个指标:最大的工作频率如下vcc的最高频率测试图随输入频率的增大发生变形如图原理图的两个使能端作用此时RD为低电平下结果输出Q只为高电平,这与原理图是相符合的此时SD为低电平下结果输出Q只为高电平,这与原理图是相符合的结果分析本实验D触发器在设计的过程中出现很多问题,刚开始得到的D触发器输出波形完全不对,经过分析发现带电路的原理图中的一根线连错了,经过组员的仔细检查排除问题后我们再次进行仿真遗憾的是我们的波形还是离目标图形较远,后来仔细观察波形发现我们设置的仿真参数有问题,一个是因为将两个使能端接在高电平导致Q输出没有出现CP在上升延时根据D的变化,原理中的真值表不相符。

cadence 实验手册

Virtuoso Analog Design Environment中文实验手册Version 5.1.41虚拟机:操作平台:Linux AS5 软件版本:IC 5141 实验模块:ADE编译:06级-程涛目录实验一、熟悉Virtuoso Analog Design Environment (1)实验二、Schematic Entry (5)实验三、模拟仿真 (12)实验四、显示仿真结果 (21)实验五、仿真结果分析 (30)实验六、参数分析 (42)实验七、使用OCEAN 和SKILL语言(略) (45)实验八、使用Corner分析工具 (46)实验九、Monte Carlo 分析 (49)实验十、优化分析 (58)实验十一、Component Description Format(CDF)参数 (63)实验十二、Macromodels、Subcircuits和Inline Subcircuits (67)实验十三、例化设计 (73)实验十四、继承连接 (76)实验一、熟悉Virtuoso Analog Design Environment实验步骤:一、登录Linux操作系统,用安装软件的用户登录,最好不要用root用户。

二、打开Linux的终端,进入软件所在文件夹,比如我的是/home/chengtao/adelabic5,输入cd /home/chengtao/adelabic5,即可进入,注意在安装时有一个lnx86.cshrc的文件,在每次进入Cadence之前都应该先运行以下命令:source lnx86.cshrc ,然后再终端中输入icms & ,稍等片刻,即可进入Cadence 图形界面CIW,如下图所示(会弹出一个Cadence的介绍窗口,关闭即可)。

三、打开一个尖峰检测电路。

1、选择Tool下的Library Manager ,即可弹出Library Manager对话框,总共有三栏分别为:Library、Cell、View,只有在Library下有目录,另外两个是空的,点traning,在Cell下便会显示很多目录,我们选择点击peakTestv,在View下会出现一个schematic,双击便会弹出一个对话框,如下图所示:2、选中peakDetectv ,peakDetectv会被白色的正方形线包围,然后依次执行Design—Hierarchy—Descend Edit (可以使用快捷键E),会蹦出一个小对话框,在View Name中选择schematic,点击Ok,则会弹出一个电路图,如下图所示:3、用鼠标选中一个Ampv,按下E键,将ViewName设置为Veriloga,点击OK,即可弹出这个器件的Verilog-a语言描述,可以仔细参考一下,先不要关闭。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.4移动元件

按键m(M)>选中元件>放置元件

按键m(M)>选中元件>按键F3>设置 Rotate—旋转,Sideways—左右翻转, Upside Down—上下翻转 放置元件 m与M的区别:m—与移动的元件相连的未选择的 线仍然相连,M —未选择的线不动

3.5复制元件

按键c>选中元件>放置元件

3.绘制原理图

3.1添加元件

Add>Instances… 快捷键I Browse>找到要添加的元件,如: smic18mmrf >n18>symbol(也可自己填写) w=5u l=0.18u 修改相应的参数 Rotate, Sideways, Upside Down可以旋转,翻转元件。Rows, Columns用于添加多个相同的元件。 Hide 按右键也可以旋转元件 移到放置位置,点左键即可;继续点左键可以继续添加,按Esc取 消 库analogLib有许多虚拟元件、常用,包括vdd,gnd,res,cap, 各种信号源等

Cadence lab1

盛昕禹14120024@ 周 雅 14120042@

实验内容

以一个共源放大器为例,介绍模拟IC设计流程。包括 原理图设计 符号图设计 电路仿真(dc,ac,tran) 版图设计(DRC,LVS,RCX) 后仿真

实验说明

212实验室的电脑,只有F盘能够保存数据,因此要把cadence的工作目 录转移到F盘中的文件夹。具体方法: 在F盘的RedHat_Share中,以自己的学号名建文件夹,如12120036. 然后启动cadence,右键>打开终端,输入如下命令, cd .. cd .. cd mnt cd hgfs cd Redhat_Share cd 14120024 icfb& 注意:一次输一行命令,每输完一行命令之后要敲回车键。以后每次实验 都在该路径下打开icfb&。

实验要求

实验要求

Cadence IC 5141

IC5141是Cadence全定制IC设计工具包,其中包 括原理图设计工具Composer,版图设计工具 Virtuso,版图验证工具Diva、Dracula等。

参考书目: 《模拟集成电路设计与仿真》

1.准备工作

1.1启动VMware

1.双击

4.1新建Symbol

画好原理图并保存 Design>Create Cellview>From Cellview>OK 修改四个方向摆放Pin的名字(用空格隔开 )>OK 就会出现默认的Symbol图形,点击左侧按 钮 保存

4.1新建Symbol

4.1新建Symbol

4.2修改Symbol

按键c>选中元件>按键F3>设置 设置Rows,Columns可以复制多个 Rotate—旋转,Sideways—左右翻转, Upside Down—上下翻转 放置元件

3.6旋转和翻转元件

按键m>选中元件>按键F3>设置 Rotate—旋转,Sideways—左右翻转, Upside Down—上下翻转 放置元件

Bus类型的线,Bus Expression,Placement 的设置与添加Pin类似 相同Wire Name的不同线默认连接在一起(即 使在原理图中并未连接)

3.10添加线名

3.11查找元件

Edit>Search>Find… >Replace…

3.12添加Note

Add>Note>Note Text…添加注释 可以从文档读入,可以设置字体大小类型 >Shape…添加图形注释 可以选择各种图形

2.3复制库

2.4重命名库

选中所要复制的Library Library Manager>Edit>Rename… 右键>Rename… To Library 填入新的Library Name

2.5新建Cell View

选中所要添加Cell View的Library (Category) 输入Cell Name 选择Tools>Ok 不同的Tools对应不同的View Name

3.绘制原理图

3.绘制原理图

使用 Cadence 软件进行绘图操作时,应注 意掌握其软件设计思想。无论在原理图设计、 符号设计还是版图设计,都有一个“操作模 式”的概念。 Cadence 软件适合“批量式”操作 切换操作的方法有两种,一是“Esc”键退回 到默认的模式。也可以直接去菜单中选择另 一个操作模式。

3.1添加元件

3.2连线

按键w(W)>点击连线起点位置>(点右键可 以改变连线模式)>继续点击>在终点双击结 束连线(如果线连接到元件端口自动结束) Esc可取消连线 Add>Solder Dot…可以添加结点(避免十 指交叉结点,会有Warning)

3.3选择元件

按住左键拉出一个框可选择框住的元件(线) 按住shift,点击元件(线) Ctrl + a 全选 点击一条线可选中这条线(变白色),继续双 击可以选中与之相连的更多线 Edit>Select>By Property…> >Filter…> 高级选项

3.绘制原理图

新建原理图(Schematic) 鼠标停留在右侧按键符号可以出现其功能 原理图中的快捷键(默认)

i c m M(shift+m ) del p q 添加元件 复制 移动 移动(断线) 删除 添加pin 查看属性 l w W(shift+w ) n [ ] f 添加线名 添加连线 添加粗线 添加注释 缩小 放大 显示全部 x S(shift+s) u U(shift+u) e Ctrl+e L (shift+l) 保存并检查 保存 取消上一步 恢复上一步 进入下一层 返回上一层 添加注释

1.2启动&退出 IC5141

CIW

1.3添加工艺库

1.Tools>Library Manager

2.Edit>Library Path…

1.3添加工艺库

3.Edit>Add Library…

4.找到目录: /mnt/hgfs/share/smic18mmrf_1P6M_200902271315 在library栏下选择smic18mmrf,点击”OK”

从Library Manager中打开一个已经存在的 Symbol 基本操作和快捷键与原理图中基本相似 Add>Shape>可以添加各种图形 Add>Pin(或左侧按钮 )可以添加Pin 旋转用快捷键r 或者Edit>Rotate [@instanceName]和[@partName]是器件的名 称和标号 绘制符号时应注意使标志输入、输出Pin的红色方 块恰好放在红色边框的线上

2.File>Open…

1.1启动VMware

3.找到redhat所在目录(E:\Redhat),导入redhat

4.单击绿色三角形,启动VMware

1.1启动VMware

5.用户登陆 User:cadence Passward:cadence

1.2启动&退出 IC5141

在桌面点击右键>打开终端>输入:icfb& 出现如图所示的CIW(Command Interpreter Window)窗口。从CIW窗口就可以调用许多工具并完 成许多任务。 CIW>File>Exit.. 可以退出IC5141

3.10添加线名

Edit>Wire Name… 按键l 与添加Pin类似,填写Name(多个Name之间用空 格隔开),可以设置线名的大小及类型(Font Height & Font Style) Hide>依次点击要添加线名的线(注意Wire Name 下的小方块一定要点在线上)

2.库文件的管理

2.库文件的管理

CIW>Tools> Library Manager 可以在Library Manager中已存在的Cell View

库(library):特定工艺相关的单元集合 单元(cell):构成系统或芯片模块的设计对象 视图(view):单元的一种预定义类型的表示 CIW:命令解释窗口 属性(attributes):预定义的名称-值对的集合 搜索路径(search path):指向当前工作目录和 工作库的指针

3.12添加Note

3.13保存&检查

点击左侧按钮 保存,如果有错误或警告, 会有弹窗提示,并在原理图中用黄色小方块 提示 注意MOS管的衬底不要忘记连接

3.13保存&检查

4.生成符号视图

4.生成符号视图

在原理图上直接添加信号源,然后进行仿真分析是 可以的,但更好的做法是先生成一个 Cell 的符号 Symbol,并利用该符号,另建一个原理图视图, 在这个新建的视图中进行仿真分析。 其好处有以下两点: (1) 在设计流程的后续阶段,需要将原理图与版 图对比(LVS),如果直接在原理图中增加了信号 源,在做 LVS阶段还需要去掉。 (2) 生成符号后,该原理图成为一个元件,可在 其它的原理图中多次调用。

1.3添加工艺库

1.3添加工艺库

5.File>Save As…

库的路径

若发现Library Manager中没有basic,analogLib,smic18mmrf这三 个库,按如下方法添加: Edit>Library Path… 会出来Library Path Editor对话框 在Library Path Editor中,Edit>Add Library,分别按如下路径添加各 个库: basic库所在路径:/tools/cds5/tools.lnx86/dfII/etc/cdslib/basic analogLib库所在路径: /tools/cds5/tools.lnx86/dfII/etc/cdslib/artist/analogLib smic18mmrf库所在路径: /mnt/hgfs/RedHat_Share/smic18mmrf_1P6M_200902271315/s mic18mmrf 添加之后要保存