MIPSI指令集32位CPU设计实例

Microchip拓展更高性能32位MIPS内核产品(二)

z FTP 服务器 z SNMP代理 z Web 服务器 z 图形函数库

预计于明年第一季度开始提供

所有均免费提供,包括完整的源代码

18

PIC32 第三方工具/ 操作系统:

现已开始icrochip全新的32位单片机系列

新器件具有更高性能和更大的存储空间,与现有PIC®单片机系列 兼容

25

z 在全国12个主要城市开设了12家区域培训中心

23

Microchip中国培训计划

z Microchip第八届“中国技术精英年会” (MASTERs)于2007年10月在北京、上海和深 圳巡回举行

z 在全国90所主要大学开设嵌入式控制设计课程, 帮助工科学生使用PIC®单片机、模拟和存储产品

24

衷心感谢您的参与!

购买

49.99美元

16

PIC32 入门工具包扩展板

以太网扩展板

z RJ45、SD卡及OLED 显示器

I/O 扩展板

z 支持 PICtail™ Plus子板

QVGA 显示器 z 触摸屏接口

将于今年第四季度开始提供

17

Microchip软件库:

加快客户产品的上市时间,降低成本

z FAT16 文件系统 z IP自举程序 z TCP/IP协议栈

商标:

Microchip的名称和徽标组合、Microchip的徽标、Accuron、dsPIC、KEELOQ、microID、MPLAB、PIC、PICmicro、PICSTART、PRO MATE、PowerSmart、rfPIC以及 SmartShunt均为Microchip Technology Inc.在美国及其他国家或地区的注册商标。AmpLab、FilterLab、Migratable Memory、MXDEV、MXLAB、PICMASTER、SEEVAL、 SmartSensor以及 The Embedded Control Solutions Company均为Microchip Technology Inc.在美国的注册商标。 Analog-for-the-Digital Age、Application Maestro、dsPICDEM、、dsPICworks、ECAN、ECONOMONITOR、FanSense、FlexROM、fuzzyLAB、In-Circuit Serial Programming、ICSP、ICEPIC、MPASM、MPLIB、MPLINK、MPSIM、mTouch、PICkit、PICDEM、、PICtail、PowerCal、PowerInfo、PowerMate、PowerTool、 rfLAB、rfPICDEM、Select Mode、Smart Serial、SmartTel以及Total Endurance均为Microchip Technology Inc.在美国及其他国家或地区的商标。SQTP为Microchip Technology Inc. 在美国的服务商标。 在此提及的其他商标均为各持有公司所有。

基于MIPS 32位处理器的简易智能家居控制系统设计详解

基于MIPS 32位处理器的简易智能家居控制系统设计详解一.研究背景与意义随着智能电网理念的提出,基于家庭智能交互终端的电能计量和营销方案已逐步形成,这意味着家居控制将迈向智能化。

智能家居是近几年产生并迅速崛起的一种新型家居住宅,家居的智能化为住户提供了一种更加安全、舒适、方便、快捷和开放的智能化、信息化的生活空间,极大的方便了用户。

因此,组建一套以家庭交互终端为核心的家居控制系统,对智能电网的改造和实施有重大的意义。

但目前的家居智能化系统存在一个很大的局限,即只是实现了局部的智能化。

而真正意义上的家居智能化则应该是拥有一个集中的终端控制系统,通过该终端对家居的所有设备进行智能化的控制和监控,这也将是智能家居系统未来的发展方向。

本设计以MIPS公司的32位处理器为核心来组建智能显示终端,并以具备无线通讯的智能插座为被控节点,搭建了一套简易的智能家居控制系统。

该系统可通过远程(手机短信),和本地(智能显示终端)两种方式进行控制。

下面将对本系统的构成和实现方案,以及各模块中涉及的关键问题进行分析。

二.系统的构成与工作原理1 系统构成与原理本系统由手机,智能显示终端,智能插座构成。

手机与智能显示终端之间通过GSM模块进行通讯,智能显示终端和智能插座之间采用Zigbee进行通讯。

智能插座作为基本的控制单元,能够实时采集每个房间的用电信息,并将信息实时传送到智能显示终端。

当发现用电异常时,智能插座自动断电并将执行结果发送到智能显示终端。

智能显示终端也将这一结果发送到用户手机。

手机实现用户的远程控制和信息接收。

用户外出时,通过手机发送的指令(如预启动,预关闭,限时供电等)将被智能终端接收并下发到智能插座。

另外,智能插座的所有执行动作都将通过智能显示终端发送到手机。

智能显示终端既能够接收手机发送的指令,也能够接收智能插座发送的数据。

智能显示终。

数字系统设计实验流水线MIPS微处理器设计

一、实验目的(1)了解提高CPU性能的方法。

(2)理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

(3)掌握流水线MIPS微处理器的工作原理。

(4)掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器,具体要求如下设计要求:(1)至少执行下列MIPS32指令。

①算数运算指令:ADD ADDU SUB SUBU ADDI ADDU②逻辑运算指令:AND OR NOR XOR ANDI ORI XORI SLT SLTISLTU SLTIU③移位指令:SLL SLLV SRL SRLV SRA④条件分支指令:BEQ BNE BGEZ BGTZ BLEZ BLTZ⑤无条件跳转指令:J JR⑥数据传输指令:LW SW⑦空指令:NOP(2)在用5级流水线技术,对数据冒险实现转发或阻塞功能。

(3)在XUP Vietex-II Pro开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz.三、实验原理1.流水线MIPS CPU总体设计流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用在高档CPU的构建中。

根据MIPS处理器指令的特点,将整体的处理过程分为取指令(IF)、指令译码、执行、存储器访问和寄存器写回五级,对应多周期CPU的五个处理阶段。

如图1所示,一个指令的执行需要五个时钟周期,每个时钟周期上升沿来临时,此指令所代表的一系列数据和控制信息转移到下一级处理。

图1 流水线流水作业示意图一条MIPS指令分为五个处理步骤,即五级流水线,的具体执行过程如图2所示。

图2 五级流水线MIPS CPU初步原理框图流水线寄存器:为了在其它四级流水线中各条指令保持各自的值,从指令存储器中读出的指令必须保存在寄存器中。

同样的方法应用到每个流水线步骤中,需要在上图中各级之间加入寄存器,如图3所示。

图3.在各级分割线添加寄存器后的框图由于在流水线中,数据和控制信息将在时钟上升沿转移到下一级,所以规定流水线转移的变量命名遵守如下格式:名称_流水线级名称。

32位MIPS处理器说明

32位MIPS处理器说明一、实验目的熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。

二、实验原理及实验内容该32位MIPS处理器主要需要设计ALU、单周期、流水线。

下面分别讲述这三个部分的设计原理及实验内容。

1.ALUALU即算数逻辑单元,要求设计一个32位的ALU,实现基本的算术、逻辑、关系、位与移位运算。

输入32bit的A和B作为操作数,5bit的控制输入ALUFun和一位控制输入Sign,输出32bit的结果Z。

其功能表如下图所示:根据功能表和要求,我们在顶层模块中设计了32bit输入ALUSrc1和ALUSrc2,以及5bit控制ALUFunc,1bit控制Sign,32bit输出ALUOut。

设计了四个主要模块:ALU_ADD_SUB,ALU_CMP,ALU_Logic,ALU_Shift,并根据ALUFunc的值来确定使用的模块。

设计框图思路如下:(1)ALU_ADD_SUB这部分是ALU设计中最重要的一部分。

采用了8位超前进位级联,用与门来实现32位全加器。

减法由加法实现,在运算的开始由ALUFunc判断进行的是加法还是减法,如果是加法则直接将两个操作数输入全加器,最低进位为0,如果是减法则取ALUSrc2的反码之后再做加法运算,最低进位是1。

需要注意的是运算结束之后需要判断结果是否为0(这个在branch指令中尤为重要),是否为负数,还有是否溢出。

是否为溢出还需要检查控制符号,如果控制符号为有效(即有符号计算)则两正数相加得负或两负数相加得正则溢出,溢出则结果符号位反了,再进而判断是否为负。

若为无符号运算,加法结果溢出则最高进位为1,且结果不为负;减法结果溢出等价于结果为负,即最高进位为0。

而结果为0等价于全部位都取0。

(2)ALU_Shift移位运算分别有逻辑左移,逻辑右移,算术右移三种情况。

首先判断是逻辑移位还是算术移位来决定填充0还是填充逻辑位。

之后采取先将操作数根据左移还是右移的判断做出32位扩充,再根据shamt从最高位到最低位判断是否为0来决定取那几位操作数,最后得到移位的结果。

mips控制器设计实验原理

mips控制器设计实验原理MIPS(Microprocessor without Interlocked Pipelined Stages)是一种32位的RISC (Reduced Instruction Set Computing)处理器架构,旨在提高处理器效率和性能。

MIPS 架构的处理器被广泛应用于各种领域,包括计算机、嵌入式系统、网络设备、数字信号处理等需要高性能的应用中。

在本实验中,我们将学习如何设计一个基于MIPS控制器的处理器。

控制器是一个能够控制处理器各个子系统如存储器、算术逻辑单元(ALU)、输入/输出设备等的模块。

MIPS控制器的设计是关键,因为它可以决定处理器的运行效率和性能。

MIPS控制器的设计需要考虑以下几个方面:1. 指令解码MIPS指令集包含了大量的指令,但是由于指令采用RISC架构,指令集中的每一个指令都很简单,只有少量的寄存器、立即数和内存操作。

控制器需要能够识别每一个指令,并正确地解码指令中的操作数。

为了实现这个目标,控制器需要包含适当的译码电路和其他必要的逻辑门电路。

2. 流水线控制流水线是一种增加处理器效率和性能的技术,通过将指令的执行拆分为多个阶段,多个指令可以在同一时刻被处理。

MIPS架构使用了5级流水线结构,即取指令、指令译码、执行、访问存储器和写回结果。

控制器需要能够控制流水线的各个阶段,确保它们按照正确的顺序执行。

3. 异常处理处理器在执行指令时可能会出现各种错误,如未定义的指令、内存访问冲突、算术溢出等。

这些错误称作异常。

处理器需要能够捕获异常并采取适当的措施,如停止当前指令的执行、中断指令流并处理异常。

控制器需要包含适当的硬件和逻辑电路来处理异常。

4. 输入/输出一个处理器需要有输入/输出接口来连接外部设备,如键盘、鼠标、显示器、网络等。

这些设备通过输入输出端口(I/O端口)与处理器相连。

控制器需要能够控制I/O端口的数据传输,并确保数据在正确的时刻被传输。

32位软处理器MicroBlaze的体系结构及其应用 (图)

Xilinx公司的MicroBlaze32位软处理器核是业界最快的软处理解决方案。

支持CoreConnect总线的标准外设集合为MicroBlaze设计人员提供了兼容性和重复利用能力。

MicroBlaze处理器运行在150MHz 时钟下,可提供125 D-MIPS的性能,非常适合设计针对网络、电信、数据通信、嵌入式和消费市场的复杂系统。

MicroBlaze的体系结构MicroBlaze就是基于Xilinx公司FPGA的微处理器IP核,利用它和其他外设IP核一起,就可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze处理器是采用RISC架构和哈佛结构的独立32位指令和数据总线,可以全速度执行存储在片上存储器和外部存储器中的程序并访问其中的数据。

其内核结构如图1所示。

● 内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器——PC指针和MSR状态标志寄存器。

为了提高性能,MicroBlaze还具有指令和数据缓存。

所有的指令字长都是32位,有三个操作数和两种寻址模式。

指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。

指令执行的流水线是并行流水线,它分为3级流水:取指、译码和执行。

CoreConnect技术CoreConnect是由IBM开发的片上总线通信链,它使多个源的芯片核相互连接成为一个完整的新芯片成为可能。

CoreConnect技术使整合变得更为容易,而且在标准产品平台设计中处理器、系统以及外围的核可以重复使用,以达到更高的整体系统性能。

CoreConnect总线架构包括处理器本机总线(PLB)、片上外围总线(OPB)、一个总线桥、两个判优器,以及一个设备控制寄存器(DCR)总线,CoreConnect总线架构如图4所示。

Xilinx将为所有嵌入式处理器用户提供IBM CoreConnect许可,因为它是所有Xilinx嵌入式处理器设计的基础。

计算机组成与系统结构课程设计-单周期32位CPU的设计

学号:计算机组成与系统结构课程设计设计说明书单周期32位CPU的设计起止日期:2014 年1 月13 日至2014 年1 月17 日学生姓名班级11计算机2班成绩指导教师(签字)计算机与信息工程学院2014年1月17日目录1、指令系统设计 ............................................................................................................ 错误!未定义书签。

2、控制部件设计 (4)3、单周期中央处理器cpu设计 (10)4、计算机主机系统设计 (12)5、调试程序编制及主机系统调试 (13)6、心得体会 (17)参考资料 (17)1、指令系统设计R型指令(op=0001)│←─━━━op────→│←rs →│←rt →│←rd →│←─━━━━func━━add(func=000001):将rs寄存器中的值和rt寄存器中的值相加,结果存入rd寄存器sub(func=000010):将rs寄存器中的值和rt寄存器中的值相减,结果存入rd寄存器and(func=000011):将rs寄存器中的值和rt寄存器中的值相与,结果存入rd寄存器or(func=000100):将rs寄存器中的值和rt寄存器中的值进行或运算,结果存入rd寄存器I型指令│←─━━━op────→│←rs →│←rt →│←─━━━━━━━立即数━━━addi(op=1000):将rs寄存器中的值与(补零成32位的)立即数减,结果存入rt寄存器ori(op=0010):将rs寄存器中的值与(补零成32位的)立即数或,结果存入rt寄存器lw(op=0011):将RAM中地址为[rs+立即数]单元的值写入rtsw(op=0100):将rt中的值写入RAM中地址为[rs+立即数]单元beq(op=0101):若rs中的值=rt中的值,则跳转到(原本的下一个地址+立即数)wr(op=0111):把(补零成32位的)立即数写入寄存器rtJ型指令│←─━━━op────→│←───invalid ──→│←─━━━━━━━地址━━━━━jump(op=0110):直接跳转到目的地址(8位)开始执行指令译码器的作业是对取指令操作中得到的指令进行译码,确定这条指令需要完成的操作。

基于MIPS的PIC32MM系列32位单片机介绍

基于MIPS的PIC32MM系列32位单片机介绍本文主要详解基于MIPS的PIC32MM系列32位单片机,首先介绍了MIPS32位架构,其次介绍了PIC32MM系列主要特点及PIC32MM系列模拟集成,最后阐述了PIC32MM系列目标应用,具体的跟随小编来详细的了解一下。

MIPS简介MIPS是世界上很流行的一种RISC处理器。

MIPS的意思是无内部互锁流水级的微处理器(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

它最早是在80年代初期由斯坦福(Stanford)大学Hennessy 教授领导的研究小组研制出来的。

MIPS公司的R系列就是在此基础上开发的RISC工业产品的微处理器。

这些系列产品为很多计算机公司采用构成各种工作站和计算机系统。

MIPS是出现最早的商业RISC架构芯片之一,新的架构集成了所有原来MIPS指令集,并增加了许多更强大的功能。

MIPS32位架构详解MIPS32架构刷新了32位嵌入式处理器的性能标准。

它是MIPS科技公司下一代高性能MIPS-Based处理器SoC发展蓝图的基础,并向上兼容MIPS6464位架构。

MIPS架构拥有强大的指令集、从32位到64位的可扩展性、广泛的软件开发工具以及众多MIPS科技公司授权厂商的支持,是领先的嵌入式架构。

MIPS32架构是以前的MIPS I 和MIPS II指令集架构(ISA)的扩展集,整合了专门用于嵌入式应用的功能强大的新指令,以及以往只在64位R4000 和R5000 MIPS处理器中能见到的已经验证的存储器管理和特权模式控制机制。

通过整合强大的新功能、标准化特权模式指令以及支持前代ISA,MIPS32架构为未来所有基于32位MIPS的开发提供了一个坚实的高性能基础。

MIPS32架构基于一种固定长度的定期编码指令集,并采用导入/存储(load/store)数据模型。

(完整word版)32位单周期RISC处理器设计

第一章32 位单周期RISC处理器设计要设计一款处理器,首先要选择体系结构,本题选择的是RISC体系结构,因为它适合于流水线设计。

然后需要选择一个标准的指令集,本题选择的MIPS指令集并按照常规的五段流水的方式来实现流水线。

流水线的实现过程将在第二章介绍。

1.1目标处理器指令集与指令格式本题目标CPU以能实现部分MIPS指令为目标,具体指令如下表1:(slti)无条件跳跳转(jL)J转空操作空操作(nop)表1 目标CPU指令集1.2 从指令具体行为反推设计方案CPU要执行一条指令,不外乎需要完成以下几个过程:取指令,指令译码,将译码出的指令放到算术逻辑运算部件ALU上执行运算,根据ALU算得的访存地址进行访存和将访存的结果写回寄存器等。

当然,不同的指令类型(R、I、J)可能经过的过程稍有不同,即它们的数据通路有所不同,以下将具体介绍:1、R格式指令数据通路:1)从指令寄存器Instr MEM中取出指令,同时PC增值(即加1等待下个CLK到来);2.)寄存器单元rs1和rs2的内容从寄存器堆Reg File中读出;3.)ALU根据功能码Opcoder确定操作方式,对从寄存器堆读出的数据进行计算;4.)ALU运算结果被写入寄存器堆,由rd确定写入的寄存器堆存储单元地址。

图1 R指令数据通路2. I 指令(除lw、sw和分支指令)数据通路如图2:1.)从指令寄存器Instr Mem中取出指令,同时PC增值(即加1等待下个CLK到来);2.)寄存器单元rs1的内容从寄存器堆Reg File中读出;3.)ALU将从寄存器堆rs1单元中读出的数据与符号扩展后的指令低16位值相加;4.)ALU的运算结果被写入寄存器堆,由rt确定写入的寄存器堆存储单元地址。

图2 I 指令(除lw、sw和分支指令)数据通路3、Lw指令数据通路如图3:1.)从指令寄存器Instr Mem中取出指令,同时PC增值(即加1等待下个CLK到来);2.)寄存器单元rs1的内容从寄存器堆Reg File中读出;3.)ALU将从寄存器堆rs1单元中读出的数据与符号扩展后的指令低16位值相加;4.)将ALU的运算结果作为数据存贮器的地址读出相应单元的内容;5)把从数据存储单元取出的数据写入寄存器堆,由rt确定写入的寄存器存储单元地址。

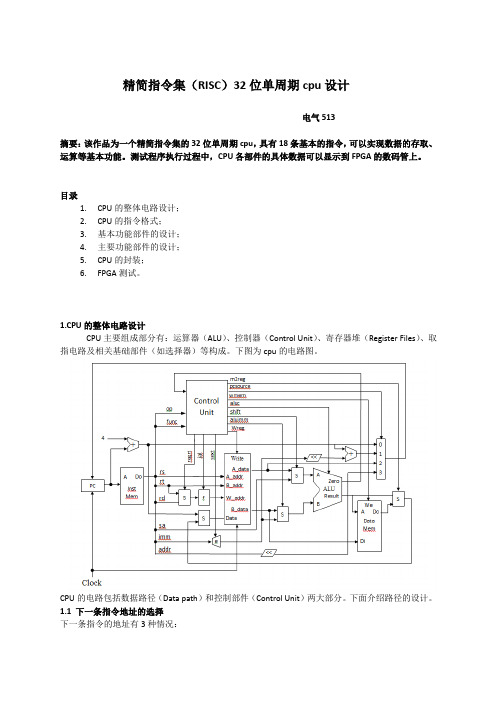

电子科技大学CPU设计:精简指令集(RISC)32位单周期cpu设计

精简指令集(RISC)32位单周期cpu设计电气513摘要:该作品为一个精简指令集的32位单周期cpu,具有18条基本的指令,可以实现数据的存取、运算等基本功能。

测试程序执行过程中,CPU各部件的具体数据可以显示到FPGA的数码管上。

目录1.CPU的整体电路设计;2.CPU的指令格式;3.基本功能部件的设计;4.主要功能部件的设计;5.CPU的封装;6.FPGA测试。

1.CPU的整体电路设计CPU主要组成部分有:运算器(ALU)、控制器(Control Unit)、寄存器堆(Register Files)、取指电路及相关基础部件(如选择器)等构成。

下图为cpu的电路图。

CPU的电路包括数据路径(Data path)和控制部件(Control Unit)两大部分。

下面介绍路径的设计。

1.1 下一条指令地址的选择下一条指令的地址有3种情况:1.程序不转移时下一条指令的地址为PC+4;2.执行beq和bne指令发生转移时,下一条指令的地址是PC加4,再加上符号扩展的偏移量左移2位的和;3.执行j指令时转移的目标地址是指令中的低26位地址左移2位,再与PC+4的高4位拼接在一起。

下一条指令地址的产生和选择电路如图所示。

图中控制器(Control Unit)根据op、func和zero(对于beq和bne指令)信号产生相应的转移控制选择信号pcsource。

1.2 ALU的输入端ALU的输入端有2个:A输入端和B输入端。

A、B输入端分别有2种输入情况。

对于A输入端,有寄存器堆的A_data和移位数sa输入。

对于B输入端,有寄存器堆的B_data和符号扩展后的立即数imm输入。

其输入数据路径如图所示。

ALU的A、B端具体输入哪路数据由控制器(Control Unit)根据指令译码产生控制信号shift和aluimm 来选择。

1.3寄存器堆的输入端寄存器堆的A_addr和B_addr的输入来自指令,分别只有一种输入,W_addr有2种,而Data有4种输入。

【最新】CPU实验——单周期MIPS处理器设计

单周期MIPS处理器设计实验报告完成人:笪腾飞2012011263一、实验目的1、设计一个32位的单周期MIPS处理器,具备定时器、数码管等外设;2、编写一个编译器,可以将mips代码编译为二进制机器码;3、编写一个计算两个整数的最大公约数的汇编程序。

二、设计方案根据理论课所学的单周期MIPS处理器数据通路的知识,结合本次试验的具体要求,最终设计方案如下:1、系统时钟为了综合后能够在开发板上正确运行程序,我们决定采取50MHz的CPU时钟,因此编写了一个时钟分频模块,对开发板提供的100MHz时钟进行二分频,从而得到50MHz时钟。

2、PC产生模块原理图如下:如上图左半部分所示,多路选择器由一个always语句中的if…else if…else语句实现。

其中,将ALU中的加减法部分提取出来实现一个加法器,用于产生PC+4和ConBA两个PC来源。

将I型指令中的16位立即数左移两位后再符号位j m扩展成32位地址,与PC+4相加得到分支地址ConBA 。

将跳转指令中的26位目标地址左移两位后,与当前PC的高四位拼接得到跳转地址JT。

将第一个操作数寄存器中的值取出作为PC的一个输入,这是为了实现jr和jalr指令,从$Xp和$Ra寄存器中读取跳转地址。

ILLOP和XADR分别是发生中断和异常时的跳转地址。

下一指令地址的选择由PCSrc决定,而PCSrc是译码后由控制信号模块根据每条指令的操作码(opcode)和函数码(funct)产生。

3、译码模块原理图如上图右半部分所示,将PC作为ROM模块的地址输入,输出即为PC所对应的指令。

分别取出指令中的某些片段,得到$Rs,$Rt,$Rd,shamt,funct,16位立即数和26位跳转地址。

4、控制模块控制模块即控制信号产生模块,六位操作码OpCode,六位函数码[5:0] Funct,定时器中断信号irq和PC最高位PC31作为输入,输出为以下控制信号:(1) R型指令指示信号IsR,值为1表示当前指令为R型指令,否则非R型指令;(2) PC产生的选择信号[2:0] PCSrc,取值0,1,2,3,4及其它,分别选择下一指令不同的PC;(3) 目的寄存器选择信号[1:0]RegDst,被写入的寄存器有四种选择:$Rd,$Rt,$Ra,$Xp,分别由RegDst不同取值完成选择;(4) 写寄存器使能信号RegWr,值为1表示允许对寄存器进行写操作;(5) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将移位量shamt 进行0扩展后作为输入,值为0表示将$Rs寄存器中的值作为输入;(6) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将扩展后的32位立即数作为输入,值为0表示将$Rt寄存器中的值作为输入;(7) ALU运算控制信号[5:0] ALUFunc,作为ALU的输入选择不同的运算操作;(8) 有无符号数指示信号Sign,值为1表示有符号数,值为0表示无符号数;(9) 写存储器使能信号MemWr,值为1表示允许对存储器进行写操作;(10) 读存储器使能信号MemRd,值为1表示允许对存储器进行读操作;(11) 写寄存器值的选择信号[1:0] MemToReg,选择ALU结果,存储器读取结果和PC+4其中之一作为写入目的寄存器的值;(12) 符号位扩展指示信号EXTOp,值为1表示对16位立即数进行符号位扩展,值为0表示0扩展;(13) 立即数高位取指令指示信号LUOp,值为1表示当前指令为lui指令,选择将立即数载入高16位低位填0的32位立即数作为ALU输入,值为0表示将正常扩展后的32位立即数作为ALU输入;控制信号的具体产生过程此处略去,在控制信号说明文件中进行详述。

32位CPU的流水线设计

结束语 随着科学技术的迅猛发展, 根据 国内外发 展的新形势 ,本文作者依据教学改革 大纲 的要 求 , 当前先进 的 F G 把 P A技术应用 到本科教学 实验当中。在设计 5级流水线 C U的过程 中, P 合理地利用现有硬件来提高 C U的处理能力。 P

流水 线技术虽 然能够 提高指令 的执行 速 度, 其各个级之间存 在着很强的依赖关系。 相关 问题是流水线操作中比较重要 的问题 ,它解决 的好坏直接影 响到流水线性能的高低。 因此 , 设 计一个基 于流水线的 R S P ,必须熟知 流 IC C U 水线的相关问题 , : 即 结构相关 , 数据相关 , 制 控 相关问题 。 我们 的解决方 法是首 先采用 哈佛体系 结 构, 从硬件的角度上解决结构相关 。 在设计存储 器时 , 使用两个独立 的存储器模块 , 分别存储 指 令和数据 。每个存储模块都不允许指令 和数 据 并存 。 然后 , 通过暂停 流水线 的方法解决数据相 关和控制相关问题 。 该方法优点是对软 、 硬件的 要求都十分简单 ,因此可称为是流水线中解决 相关问题的最筒单而有效的方法 , 较适用 于本 科实验教学。 3基于 F G P A的 C U设计实验平台 P 基于 F G P A的验证方法 有很 多 , 主要分 为 软件仿真验证 和物理验证。本文采用软件仿 真 验证 , 通过建 立先进 的软件测试平台 , 能够较好 的验证 C U在 R L级设 计上 的合理 性和可靠 P T

性。

时序要求p 】 。我们 的实验 的设计思想是 : 改变过 去以验证为主的陈旧和落后的学习状态 , 实现 以设计为主的实验教学创新模式和培养知识创 新人才的教学 目 ,让学生真正感受 到流水线 标 的运作过程 。 在该实验 平台上, 所有实验 目标的 设计与验证均使用硬件描述语言完成 , 实验平 台的建立使实验者可专心于实验的设计 与验证

计算机体系结构实验-多周期MIPS处理器

13

多周期 控制

CLK

PCWrite

Branch

IorD Control PCSrc

MemWrite Unit ALUControl2:0

IRWrite

ALUSrcB1:0

31:26 Op 5:0 Funct

ALUSrcA RegWrite

MemtoReg

RegDst

CLK

PC'

PC

EN

CLK

WE

Memory WD

CLK Instr 25:21

EN

CLK

CLK

WE3

A1

RD1

A

A2

RD2

A3 Register File

WD3

SignImm

15:0

Sign Extend

SignImm是Instr的组合功能,在当前指令处 理过程中不会改变,因此不需要寄存。

6

多周期 数据路径-4

lw rt, imm(rs)

1

00

4 01 SrcB 10

11

ALU

CLK

ALUResult

ALUOut

SignImm

15:0

Sign Extend

11

多周期 数据路径-9

R-Type

• Read from rs and rt • Write ALUResult to register file • Write to rd (instead of rt)

Instr 25:21

20:16

EN

CLK

20:16 0 15:11 1

Data

CLK

CLK

WE3

A1

RD1

32位MIPS CPU 设计 实验报告详解

数字逻辑与处理器基础实验32位MIPS CPU设计综述:我们的最后验收结果时钟频率是84.9MHz。

本实验报告主要分为实验设计说明与实验收获总结两个部分。

附件中有CPU工程文档与模块代码。

第一部分实验设计一、ALU设计1、设计思路实现基本的算术、逻辑、关系、位与移位运算,尽量优化以达到最小的面积延时积。

结构图如下:主要设计思想:A. 加法运算实现可以采用逐次进位、超前进位等结构,减法可以通过加法实现(参见见面理论课讲义或者前面实验);同时输出Z(结果为零)、V(结果溢出)、N(结果为负)等标志位,注意有符号数和无符号数标志产生的不同。

B. 比较运算根据减法运算的结果(Z/V/N)产生,自行分析比较操作与算术运算之间的关系。

C. 移位运算可以考虑将移位操作拆分为16 位移位、8 位移位、4 位移位、2 位移位、1位移位等几个子运算的组合,然后级联形成最后的运算结果。

D. 逻辑运算可以根据要求直接产生。

功能表接口说明2、主要模块a)32bit加法器采用8个4bit超前进位加法器极连的方式,构成32bit加法器。

对于逸出位v的处理如下:由有符号数的性质可知,对最高位32和次高位31位取抑或,输出信号则为是否逸出。

对32位运算结果取反后,再对相邻两位反复取与,最终得到结果是否为零的输出z.如果是有符号数,则符号位=n。

由于这一方法部分程度上减弱了高位计算对低位计算的依赖程度,因此可以实现延时的降低。

同时,由于其超前进位网络的大量逻辑运算,较大程度上提升了电路的面积,造成最终的面积延时积特性恶化。

关键代码见附录1b)32bit减法器对加法器按位取反,再加一。

关键代码见附录1c)32bit 右移32bit 左移32bit 算术右移将移位操作拆分为16 位移位、8 位移位、4 位移位、2 位移位、1位移位等几个子运算的组合,然后级联得到最后的运算结果。

关键代码见附录1d)32bit 逻辑比较单元采用行为级语句直实现逻辑比较功能。

基于MIPS指令集的32位RISC处理器逻辑设计

本科生毕业论文题目:基于MIPS指令集的32位RISC处理器逻辑设计院系:信息科学与技术学院专业:计算机科学与技术学生姓名:***学号:********指导教师:李国桢副教授二〇〇九年四月摘要CPU是计算机系统的核心部件,在各类信息终端中得到了广泛的应用。

处理器的设计及制造技术也是计算机技术的核心之一。

MIPS是世界上很流行的一种RISC 处理器。

MIPS的意思是“无内部互锁流水级的微处理器”(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

本文在详细研究32位MIPS处理器体系结构的基础之上,在Quartus II 7.2环境中,完全依靠自己的研发设计能力,采用硬件描述语言VHDL完成了拥有自主知识产权的基于MIPS指令集的32位RISC处理器的逻辑设计。

共开发出单周期、多周期、五级流水线等3个不同版本的32位RISC处理器,均通过Quartus II进行了时序仿真和性能比较分析。

本文的首先概述了MIPS指令集的重要特征,为讨论CPU的具体设计奠定基础。

本文设计的3个版本的CPU均实现了一个共包含59条指令的32位MIPS指令子集。

本文的主体部分首先详细描述了处理器各个独立功能模块的设计,为后续的整体设计实现提供逻辑功能支持。

随后按照单周期、多周期、流水线的顺序,循序渐进的围绕着指令执行过程中需经历的五个阶段,详细描述了3个版本的处理器中各阶段的逻辑设计。

在完成了各个版本的CPU的整体逻辑设计后,通过Quartus II时序仿真软件在所设计的CPU上运行了测试程序,测试输出波形表明了处理器逻辑设计的正确性。

本文还通过Quartus II 7.2中的Quartus II Time Quest Timing Analyzer软件,基于Altra公司的FPGA器件比较分析了所设计的3个版本CPU的性能。

mips指令集设计

mips指令集设计要求:指令集功能尽可能完备,指令条数尽可能少。

成员:思路:仿照mips指令集的编码方法,每条指令采用32位编码方式。

由于要使指令条数尽可能少,还要具有可扩充性,保留一定的操作码空间,故使用5位给操作码编码。

使用64个64位通用寄存器,故使用6位进行地址码编码。

所以三种不同的指令格式为:R型指令:0 4 5 10 11 16 17 22 23 31 OPCODE RS1 RS2 RD FUNCI型指令:0 4 5 10 11 16 17 31 OPCODE RS1 RS2 IMM/UIMMJ型指令:0 4 5 31 OPCODE OFFSETR型指令的操作码均为00000,包含指令有:加法指令、减法指令、无符号加法指令、无符号减法指令、逻辑指令(与、或、或非、抑或)、移动指令。

I型指令的操作码为00001—01000,包含指令有:立即数加指令、无符号立即数加指令、逻辑左移指令、逻辑右移指令、Store指令、Load指令、等于零时分支指令、不相等时分支指令。

J型指令的操作码为01001—01100,包含指令有:逻辑指令(非)、跳转指令、跳转并链接指令、寄存器跳转指令。

具体指令设计如下:R型指令:加法指令:0 4 5 10 11 16 17 22 23 31 00000 000000 000001 000010 000000000减法指令:0 4 5 10 11 16 17 22 23 31 00000 000011 000100 000101 000000001无符号加法指令:0 4 5 10 11 16 17 22 23 31 00000 000110 000111 001000 000000010无符号减法指令:0 4 5 10 11 16 17 22 23 31 00000 001001 001010 001011 000000011与:0 4 5 10 11 16 17 22 23 31 00000 001100 001101 001110 000000100或:0 4 5 10 11 16 17 22 23 31 00000 001111 010000 010001 000000101或非:0 4 5 10 11 16 17 22 23 31 OPCODE 010010 010011 010100 000000110抑或:0 4 5 10 11 16 17 22 23 31 OPCODE 010101 010110 010111 000000111移动指令:0 4 5 10 11 16 17 22 23 31OPCODE 011000 011001 011010 000001000I型指令:立即数加指令:0 4 5 10 11 16 17 31 00001 011011 011100 immediate无符号立即数加指令:0 4 5 10 11 16 17 31 00010 011101 011110 immediate(unsign)逻辑左移指令:0 4 5 10 11 16 17 31 00011 011111 100000 immediate逻辑右移指令:0 4 5 10 11 16 17 31 00100 100001 100010 immediateStore指令:0 4 5 10 11 16 17 31 00101 100011 100100 immediateLoad指令:0 4 5 10 11 16 17 31 00110 100101 100110 immediate等于零时分支指令:0 4 5 10 11 16 17 31 00111 100111 101000 immediate不相等时分支指令:0 4 5 10 11 16 17 31 01000 101001 101010 immediateJ型指令:非:0 4 5 31 01001 OFFSET跳转指令:0 4 5 31 01010 OFFSET跳转并链接指令:0 4 5 31 01011 OFFSET寄存器跳转指令:0 4 5 31 01100 OFFSET。

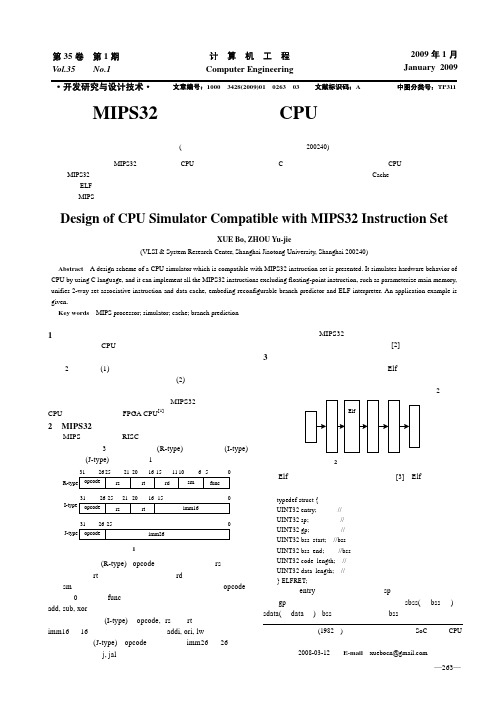

MIPS32指令集兼容的CPU模拟器设计

2009年1月January 2009计 算 机 工 程Computer Engineering 第35卷 第1期Vol.35 No.1·开发研究与设计技术·文章编号:1000—3428(2009)01—0263—03文献标识码:A中图分类号:TP311MIPS32指令集兼容的CPU 模拟器设计薛 勃,周玉洁(上海交通大学芯片与系统研究中心,上海 200240)摘 要:描述一个与MIPS32指令集兼容的CPU 模拟器设计方案,该方案用C 语言描述处理器的硬件行为,模拟CPU 指令的执行过程,实现MIPS32除浮点运算指令以外的所有指令,有大小可配的主存储器、指令和数据统一的二相关高速缓存Cache ,内置类型可配的分支预测器和ELF 文件解析器,并给出设计的应用实例。

关键词:MIPS 处理器;模拟器;高速缓存;分支预测Design of CPU Simulator Compatible with MIPS32 Instruction SetXUE Bo, ZHOU Yu-jie(VLSI & System Research Center, Shanghai Jiaotong University, Shanghai 200240)【Abstract 】A design scheme of a CPU simulator which is compatible with MIPS32 instruction set is presented. It simulates hardware behavior of CPU by using C language, and it can implement all the MIPS32 instructions excluding floating-point instruction, such as parameterize main memory,unifies 2-way set associative instruction and data cache, embeding reconfigurable branch predictor and ELF interpreter. An application example is given.【Key words 】MIPS processor; simulator; cache; branch prediction1 概述软件形式的CPU 模拟器是现代桌面处理器和嵌入式处理器设计的重要前期步骤,它在硬件处理器的设计流程中的作用有2个方面:(1)在设计初期,探索处理器体系结构的设计形式,并分析其对处理器性能的影响;(2)辅助硬件设计,用和底层硬件结构类似的软件语法描述硬件行为,能有效简化硬件设计的复杂度。

MIPS处理器

Jump 0 0 0 0 1

Branch 0 0 0 1 x

Mem Read 0 1 0 0 0

Mem ToReg 0 1 X X x

AluOp (*2) 1x 00 00 01 xx

Mem Write 0 0 1 0 0

AluSrc 1 0 0 1 x

Reg Write 1 1 0 0 0

指令用到的功能单元

MIPS通用寄存器

定时方法

定时方法规定的状态单元(寄存器,存储器)的读出 和写入操作与时钟信号的关系。 读出

无控制信号:不需要控制信号,持续读出 有控制信号:当控制信号电平有效时读出 无控制信号:只要时钟的有效跳变沿到来,就写入 有控制信号:时钟有效跳变沿到来,且控制电平有效,写入

写入:边沿触发

mem[(rs)+eimm]

存取指令/R指令的数据通路合并

RS

RT

RT RD

存取指令/R指令的数据通路合并

Beq指令的数据通路

rs (rs) rt (rt)

—

R类型、存取、beq指令的数据通路

ALU的控制信号

ALU的控制信号

ALU的控制信号

真值表

加入ALU控制后的数据通路

指令[15~11]

实验x学号姓名寄存器组包含32个32位寄存器32位alur型指令的数据通路rsrtrdrsrtfunc数据存储器数据存取指令的数据通路rsrtrtimmrseimmrtmemrseimm存取指令r指令的数据通路合并rsrtrdrt存取指令r指令的数据通路合并beq指令的数据通路rsrtrsrtr类型存取beq指令的数据通路alu的控制信号alu的控制信号alu的控制信号真值表加入alu控制后的数据通路指令1511控制信号小结加上控制单元的数据通路控制单元的真值表指令操作码r型指令000000lw100011sw101011beq000100j指令加上j指令后的数据通路opregdstjumpbranchmemreadmemtoregaluopmemwritealusrcregwrite000000r指令用到的功能单元多周期实现方案多周期数据通路设计思路把任意指令的执行分解为一系列步骤这些步骤的执行时间差不多每步用一个时钟周期执行执行一条指令需要n个时钟周期

基于FPGA的32位MIPS-CPU平台开发

基于FPGA的32位MIPS-CPU平台开发

孙建辉;王春栋

【期刊名称】《电子与封装》

【年(卷),期】2010(10)4

【摘要】文章参考opencores组织的开源代码,完成基于5级流水线的32位MIPS CPU的设计,并通过增加相关逻辑解决流水线冒险与竞争.设计的CPU文中称为OPS1-CPU,使用基于Windows·DOS系统搭建gccmips-elf编译系统,用来对应用程序进行编译、链接与执行,生成相应汇编语言程序以及仿真向量文件.最终将设计的OPS1-CPU成功下载到ALTERA公司的FPGA芯片EP1C6Q240,进行了板级的指令级调试与验证,证明OPS1-CPU硬件系统与编译系统运行正常,完成MIPS系统的平台搭建.

【总页数】4页(P20-23)

【作者】孙建辉;王春栋

【作者单位】中国电子科技集团公司第58研究所,江苏,无锡,214035;中国电子科技集团公司第58研究所,江苏,无锡,214035

【正文语种】中文

【中图分类】TN402

【相关文献】

1.基于FPGA的32位片上网络设计与验证 [J], 王荣阳;袁泉;陈栋;王科

2.基于FPGA的32位循环型除法器设计 [J], 李文彬;陈金鹰;王惟洁;任小强

3.基于FPGA的32位多并行2DFFT处理器的设计 [J], 毛宇河; 伍松

4.基于FPGA的32位多并行2DFFT处理器的设计 [J], 毛宇河; 伍松

5.Xilinx FPGA处理器解决方案为嵌入式系统设计人员提供强大的性能优势独立测试结果再次肯定了Xilinx业界最全面的基于FPGA的32位嵌入式处理解决方案的领先地位 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。