Lab1_体系结构实验报告

lab1

實驗1. 庫倫作用力 ---自然界的四個作用力之一一、簡介1789年法國工程師庫倫提出了庫倫定律,靜電力的大小與距離平方成反比、與電量成積成正比,其形式恰與"重力引力"的形式相同,從此電磁學的發展有了定量的數學形式,也開啟了所謂"統一場論"的研究。

本實驗乃利用庫倫力平衡(Coulomb Balance)裝置去檢驗庫倫作用力中,電磁力與距離、電荷的關係,並由此得到庫倫常數(Coulomb constant)k 。

二、原理1789年法國工程師庫倫提出了庫倫定律,靜電力的大小與距離平方成反比、與電量成積成正比,其形式可寫成:221R Q Q k F =(1)其中,F 為庫倫靜電力,Q 1及Q 2分別為電荷之電量,R 為兩電荷之間距。

本實驗的原理可用圖一來說明:首先我們將兩石墨球充電帶有電荷,其中一個小球固定在軌道上,另一小球則透過轉矩可帶動鋼絲細線扭轉,兩者組成所謂的庫倫力平衡(Coulomb Balance)裝置。

當兩小球靠近時,靜電力將造成細鋼線的扭轉形變,產生一個扭轉角q ,力越大扭轉角越大,呈現性正比關係,裝置上有一個轉盤可讓我們解讀轉角大小。

我們也可以以外加力來扭轉細剛絲,當反扭力與庫倫作用力達成平衡時,細鋼線之扭力等於電荷間之靜電力,所以可利用計算扭力的方式來求得帶電荷球之間的作用力,即21R Q Q k F k e tor ==q (2)又,小球可視為球型電容a C o e p 4=,a 為小球半徑。

所以在外加電壓為V 的情況下,小球所被充電的電荷為:V a CV Q o e p 4==(3)其次,式(1)中的tor k ,可利用重力所產生之力矩與Torsion wire 之扭力平衡關係求得。

我們將庫倫平衡儀傾倒,在石墨球上而放上小砝碼(質量為m),利用重力帶動細鋼絲扭轉,故可得到gtor mgk q =(4)因此,將式(3)及(4)代入式(2),則可得到靜電常數Coulumb constantk 為202)4(aV R mg k e g pe q q =(5)並由這些量測可驗證庫倫力與電荷和距離之間的關係。

软件体系结构实验一实验报告

protected:

virtual void DoDataExchange(CDataExchange* pDX); // DDX/DDV support

//}}AFX_VIRTUAL

// Implementation

protected:

//{{AFX_MSG(CAboutDlg)

if (!ProcessShellCommand(cmdInfo))

return FALSE;

// The one and only window has been initialized, so show and update it.

m_pMainWnd->ShowWindow(SW_SHOW);

ON_COMMAND(ID_FILE_PRINT_SETUP, CWinApp::OnFilePrintSetup)

END_MESSAGE_MAP()

/////////////////////////////////////////////////////////////////////////////

ON_COMMAND(ID_APP_ABOUT, OnAppAbout)

// NOTE - the ClassWizard will add and remove mapping macros here.

// DO NOT EDIT what you see in these blocks of generated code!

#include "Hotel_MIS.h"

#include "MainFrm.h"

#include "Hotel_MISDoc.h"

标准实验报告(参考)

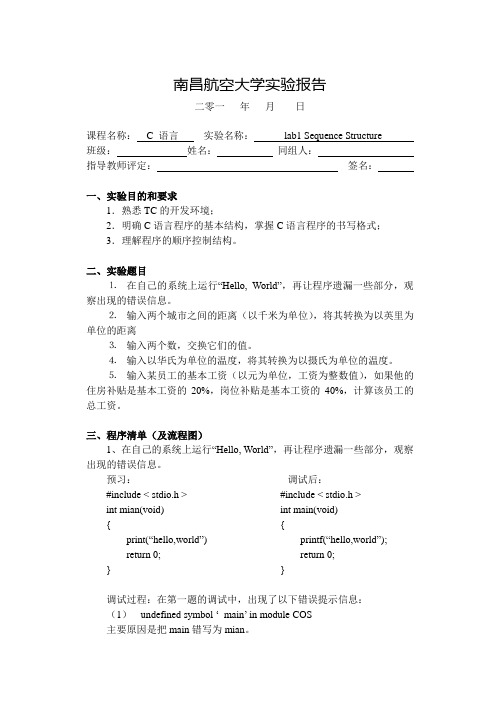

南昌航空大学实验报告二零一年月日课程名称: C 语言实验名称:lab1 Sequence Structure班级:姓名:同组人:指导教师评定:签名:一、实验目的和要求1.熟悉TC的开发环境;2.明确C语言程序的基本结构,掌握C语言程序的书写格式;3.理解程序的顺序控制结构。

二、实验题目⒈在自己的系统上运行“Hello, World”,再让程序遗漏一些部分,观察出现的错误信息。

⒉输入两个城市之间的距离(以千米为单位),将其转换为以英里为单位的距离⒊输入两个数,交换它们的值。

⒋输入以华氏为单位的温度,将其转换为以摄氏为单位的温度。

⒌输入某员工的基本工资(以元为单位,工资为整数值),如果他的住房补贴是基本工资的20%,岗位补贴是基本工资的40%,计算该员工的总工资。

三、程序清单(及流程图)1、在自己的系统上运行“Hello,World”,再让程序遗漏一些部分,观察出现的错误信息。

预习:调试后:#include < stdio.h >int mian(void){print(“hello,world”)return 0;} #include < stdio.h >int main(void){printf(“hello,world”);return 0;}调试过程:在第一题的调试中,出现了以下错误提示信息:(1)undefined symbol …_main‟ in module COS主要原因是把main错写为mian。

(2)statement missing …;‟ in function main主要原因是print(“hello,world”)后分号;没有输入。

(3)undefined symbol …_print‟ in module hello.c主要原因是把输出函数printf错写为print。

……2、……3、……四、实验结果1、调试无错误后,分别用下列数据作为输入可得到以下结果:可以在屏幕上输出hello world的字符串。

OS-lab1实验报告

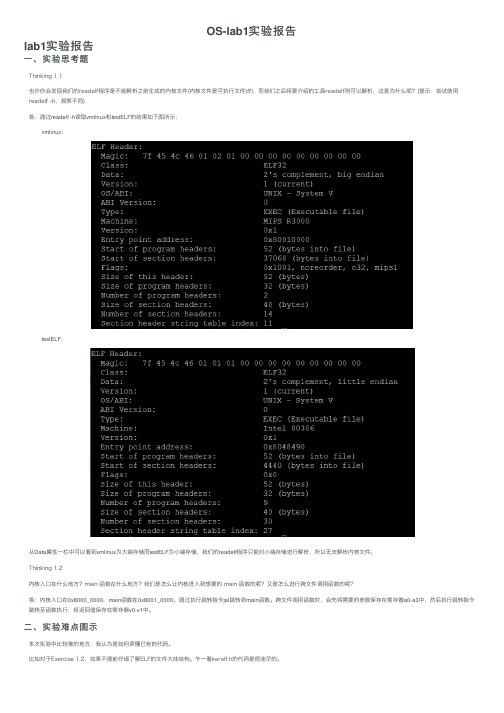

OS-lab1实验报告lab1实验报告⼀、实验思考题Thinking 1.1也许你会发现我们的readelf程序是不能解析之前⽣成的内核⽂件(内核⽂件是可执⾏⽂件)的,⽽我们之后将要介绍的⼯具readelf则可以解析,这是为什么呢?(提⽰:尝试使⽤readelf -h,观察不同)答:通过readelf -h读取vmlinux和testELF的结果如下图所⽰:vmlinux:testELF:从Data属性⼀栏中可以看到vmlinux为⼤端存储⽽testELF为⼩端存储,我们的readelf程序只能对⼩端存储进⾏解析,所以⽆法解析内核⽂件。

Thinking 1.2内核⼊⼝在什么地⽅?main 函数在什么地⽅?我们是怎么让内核进⼊到想要的 main 函数的呢?⼜是怎么进⾏跨⽂件调⽤函数的呢?答:内核⼊⼝在0x8000_0000,main函数在0x8001_0000。

通过执⾏跳转指令jal跳转到main函数。

跨⽂件调⽤函数时,会先将需要的参数保存在寄存器a0-a3中,然后执⾏跳转指令跳转⾄函数执⾏,将返回值保存在寄存器v0-v1中。

⼆、实验难点图⽰本次实验中⽐较难的地⽅,我认为是如何读懂已有的代码。

⽐如对于Exercise 1.2,如果不提前仔细了解ELF的⽂件⼤体结构。

乍⼀看kerelf.h的代码是很迷茫的。

这样“冗长”的⼀个结构体到底是什么意思,结构体中的各个变量代表着什么属性,只有结合注释和理论的知识才能理解,从⽽加以运⽤。

对于Exercise 1.5,这⼀点就更加明显了。

想要完成Exercise 1.5,需要阅读三个代码⽂件,了解printf函数的具体实现过程,需要了解这三个⽂件之中与printf实现相关的函数功能以及具体实现⽅法,⽐如printf.c中的myoutput函数和printf函数,这两个函数与我们需要补写的内容密切相关。

了解了这两个函数之后再去读print.c的函数内容,才能⽐较好的理解lp_Print函数的具体实现过程。

系统结构 第一、二次试验报告

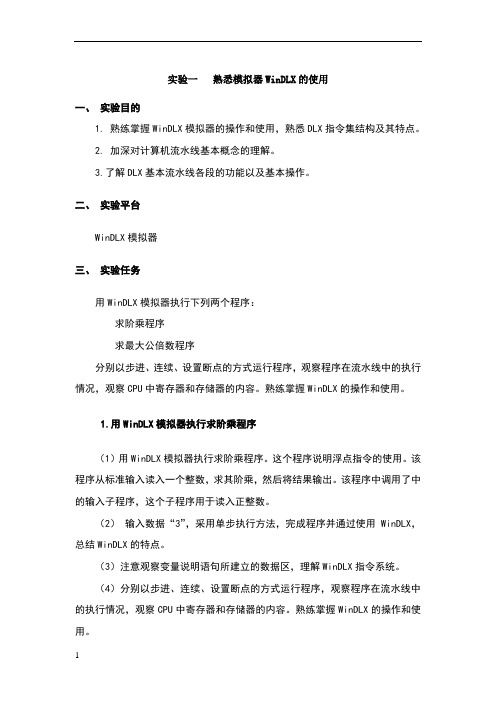

实验一熟悉模拟器WinDLX的使用一、实验目的1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点。

2. 加深对计算机流水线基本概念的理解。

3.了解DLX基本流水线各段的功能以及基本操作。

二、实验平台WinDLX模拟器三、实验任务用WinDLX模拟器执行下列两个程序:求阶乘程序求最大公倍数程序分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU中寄存器和存储器的内容。

熟练掌握WinDLX的操作和使用。

1.用WinDLX模拟器执行求阶乘程序(1)用WinDLX模拟器执行求阶乘程序。

这个程序说明浮点指令的使用。

该程序从标准输入读入一个整数,求其阶乘,然后将结果输出。

该程序中调用了中的输入子程序,这个子程序用于读入正整数。

(2)输入数据“3”,采用单步执行方法,完成程序并通过使用WinDLX,总结WinDLX的特点。

(3)注意观察变量说明语句所建立的数据区,理解WinDLX指令系统。

(4)分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU中寄存器和存储器的内容。

熟练掌握WinDLX的操作和使用。

2.用WinDLX模拟器求最大公约数程序(1)用WinDLX模拟器执行程序。

该程序从标准输入读入两个整数,求他们的greatest common measure,然后将结果写到标准输出。

该程序中调用了中的输入子程序。

(2)给出两组数6、3和6、1,采用单步和连续混合执行的方法完成程序,注意中间过程和寄存器的变化情况,观察流水线工作情况。

然后单击主菜单上的execute/display dlx-i/o,观察结果。

(3 ) 分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU中寄存器和存储器的内容。

实验结果:1、(1)导入和代码(2)单步执行流水线:寄存器的值:由图可知:PC寄存器中存放下一条要执行的语句的地址,IMAR中存放当前执行的语句的地址。

系统结构实验一报告

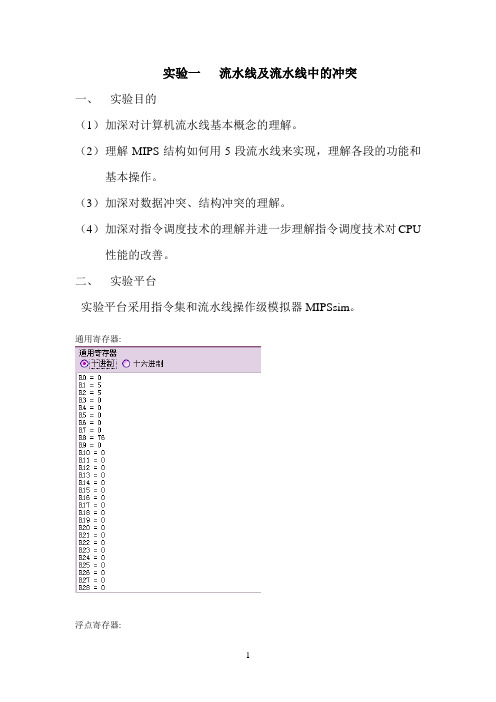

实验一流水线及流水线中的冲突一、实验目的(1)加深对计算机流水线基本概念的理解。

(2)理解MIPS结构如何用5段流水线来实现,理解各段的功能和基本操作。

(3)加深对数据冲突、结构冲突的理解。

(4)加深对指令调度技术的理解并进一步理解指令调度技术对CPU 性能的改善。

二、实验平台实验平台采用指令集和流水线操作级模拟器MIPSsim。

通用寄存器:浮点寄存器:特殊寄存器:流水寄存器:第13个时钟周期的时钟周期图如下:各段指令为:(1)学号为单数的同学自己编写一段关于结构冲突的汇编语言程序,分析该段程序存在结构冲突的指令以及导致结构冲突的部件,记录由结构冲突引起的停顿时钟周期数,计算停顿周期数占总执行周期数的百分比。

分析结构冲突对CPU性能的影响。

编写的代码如下:.textmain:ADD.D $f2,$f0,$f1ADD.D $f3,$f0,$f1ADD.D $f4,$f0,$f1ADD.D $f5,$f0,$f1ADD.D $f6,$f0,$f1ADD.D $f7,$f0,$f1ADD.D $f8,$f0,$f1ADD.D $f9,$f0,$f1TEQ $r0,$r0由结构冲突引起的停顿周期数为:35个计算停顿周期数占总执行周期数的百分比为:67.30769%ADD.D $f3,$f0,$f1和ADD.D $f4,$f0,$f1指令间存在结构冲突,由于读f0和f1的值都要访存,又因为执行一条流水线时只能有有一条指令访存,所有产生结构冲突。

结构冲突降低了CPU的性能,是执行周期时间变长,并行性较差。

(2)加载样例schedule.s观察程序在流水线中的执行情况。

通过查看统计数据和时钟周期图,找出并记录程序执行过程中各种冲突发生的次数,发生写后读冲突的指令组合以及程序执行的总时钟周期数。

RAW停顿:12 占周期总数的百分比:41.37931%load停顿:3 占所有RAW停顿的百分比:25%浮点停顿:0 占所有RAW停顿的百分比:0%WAW停顿:0 占周期总数的百分比:0%结构停顿:0 占周期总数的百分比:0%控制停顿:0 占周期总数的百分比:0%自陷停顿:1 占周期总数的百分比:3.448276%停顿周期总数:13 占周期总数的百分比:44.82759%发生写后读冲突的指令:LW $r2,0($r1)和MUL $r24,$r26,$r14等程序执行的总时钟周期数为:29(3)采用指令调度技术对程序进行指令调度,消除冲突,将调度后的程序重新加载,执行该程序观察程序在流水线中的执行情况,记录程序执行的总周期数。

BUAAOS——Lab1实验报告

BUAAOS——Lab1实验报告lab1实验报告实验思考题1.1也许你会发现我们的readelf程序是不能解析之前⽣成的内核⽂件(内核⽂件是可执⾏⽂件)的,⽽我们之后将要介绍的⼯具readelf则可以解析,这是为什么呢?(提⽰:尝试使⽤readelf -h,观察不同)通过linux内置的readelf⼯具即使⽤readelf -h命令⾏分别对testELF⽂件和之前⽣成的内核⽂件vmlinux的elf⽂件头进⾏查看:可以很清楚的看出,之前⽣成的vmlinux内核⽂件为⼤端存储,⽽testELF为⼩端存储。

因此我们⾃⼰编写的readelf程序只能解析testELF⽽不能解析vmlinux内核⽂件,因为编写readelf程序使⽤c语⾔不能简单的读取⼤端存储的数据。

1.2内核⼊⼝在什么地⽅?main 函数在什么地⽅?我们是怎么让内核进⼊到想要的 main 函数的呢?⼜是怎么进⾏跨⽂件调⽤函数的呢?内核的⼊⼝的起始地址为0x80000000,main函数在0x80010000。

在⼊⼝函数本实验为start.S内部使⽤跳转指令jal跳转到指定的函数地址。

跨⽂件调⽤函数通过跳转指令来调⽤,同时在跳转之前需要将数据存⼊栈中。

实验难点图⽰本次课下实验的难点其实就是能否读懂现有代码以及学习如何调⽤现有的⼯具。

例如在编写readelf.c⽂件中,我们可以从ELF⼿册中得知每个elf⽂件头结构体的结构,以及它内部的数据,随后根据适当的处理得出每个Section的结构体,再从其中获取所需要的数据。

即思路可以概括为⼀下步骤:知道结构体中的数据typedef struct {unsigned char e_ident[EI_NIDENT]; /* Magic number and other info */// 存放魔数以及其他信息Elf32_Half e_type; /* Object file type */// ⽂件类型Elf32_Half e_machine; /* Architecture */// 机器架构Elf32_Word e_version; /* Object file version */// ⽂件版本Elf32_Addr e_entry; /* Entry point virtual address */// ⼊⼝点的虚拟地址Elf32_Off e_phoff; /* Program header table file offset */// 程序头表所在处与此⽂件头的偏移Elf32_Off e_shoff; /* Section header table file offset */// 段头表所在处与此⽂件头的偏移Elf32_Word e_flags; /* Processor-specific flags */// 针对处理器的标记Elf32_Half e_ehsize; /* ELF header size in bytes */// ELF⽂件头的⼤⼩(单位为字节)Elf32_Half e_phentsize; /* Program header table entry size */// 程序头表⼊⼝⼤⼩Elf32_Half e_phnum; /* Program header table entry count */// 程序头表⼊⼝数Elf32_Half e_shentsize; /* Section header table entry size */// 段头表⼊⼝⼤⼩Elf32_Half e_shnum; /* Section header table entry count */// 段头表⼊⼝数Elf32_Half e_shstrndx; /* Section header string table index */// 段头字符串编号} Elf32_Ehdr;了解readelf.c⽂件中已有代码如何获取结构体中的数据仿照已有代码获取所需要的数据:e_shoff、e_shentsize、e_shnum再例如补全print.c⽂件中的代码,需要的也是这种思路:了解已有的specifier的处理过程查看已有的printNum、printChar等⽅法获取所需要的各种参数仿照已有的specifier的处理过程,对d、D进⾏处理同时需要充分熟悉有关C语⾔指针的知识⽽对于更多的细节,对于本次实验练习关系并不是很⼤,只需要⼤致了解内核启动和编译链接的过程。

清华大学操作系统实验lab1实验报告

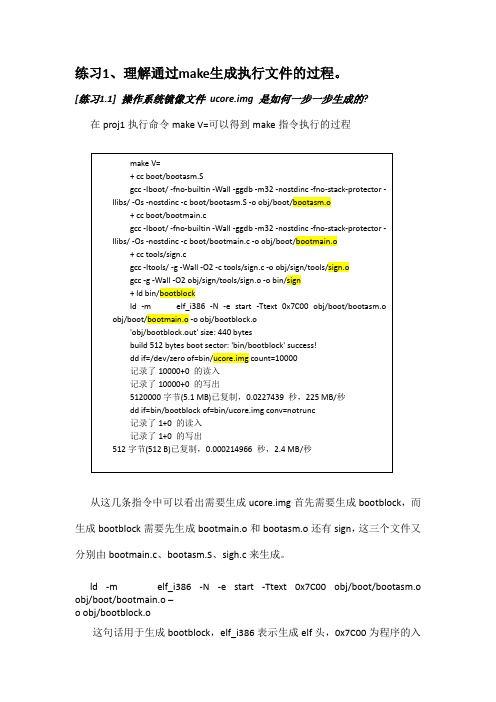

练习1、理解通过make生成执行文件的过程。

[练习1.1] 操作系统镜像文件ucore.img 是如何一步一步生成的?在proj1执行命令make V=可以得到make指令执行的过程从这几条指令中可以看出需要生成ucore.img首先需要生成bootblock,而生成bootblock需要先生成bootmain.o和bootasm.o还有sign,这三个文件又分别由bootmain.c、bootasm.S、sigh.c来生成。

ld -m elf_i386 -N -e start -Ttext 0x7C00 obj/boot/bootasm.o obj/boot/bootmain.o –o obj/bootblock.o这句话用于生成bootblock,elf_i386表示生成elf头,0x7C00为程序的入口。

'obj/bootblock.out' size: 440 bytes这句话表示生成的bootblock的文件大小,因为大小不到512字节,所以需要给blootblock填充,填充的功能在sign.c中有所体现,最后两字节设置为了0x55,0xAAbuf[510] = 0x55;buf[511] = 0xAA;FILE *ofp = fopen(argv[2], "wb+");size = fwrite(buf, 1, 512, ofp);[练习1.2] 一个被系统认为是符合规范的硬盘主引导扇区的特征是什么?前面已经提到过:引导扇区的大小为512字节,最后两个字节为标志性结束字节0x55,0xAA,做完这样的检查才能认为是符合规范的磁盘主引导扇区。

Sign.c文件中有作检查:if (size != 512) {fprintf(stderr, "write '%s' error, size is %d.\n", argv[2], size);return -1;}练习2:使用qemu执行并调试lab1中的软件。

清华大学操作系统lab1_实验报告

实验1:系统软件启动过程练习1:(1)操作系统镜像文件ucore.img 是如何一步一步生成的?在命令行中输入“make V=”1、首先把C的源代码进行编译成为.o文件,也就是目标文件(红色方框内)2、ld命令将这些目标文件转变成可执行文件,比如此处的bootblock.out(绿色方框内)3、dd命令把bootloder放到ucore.img count的虚拟硬盘之中4、还生成了两个软件,一个是Bootloader,另一个是kernel。

(2)一个被系统认为是符合规范的硬盘主引导扇区的特征:在/lab1/tools/sign.c中我们可以了解到规范的硬盘引导扇区的大小为512字节,硬盘结束标志位55AA练习2:(1)从CPU 加电后执行的第一条指令开始,单步跟踪BIOS 的执行改写Makefile文件lab1-mon: $(UCOREIMG)$(V)$(TERMINAL) -e "$(QEMU) -S -s -d in_asm -D $(BINDIR)/q.log -monitor stdio -hda $< -serial null"$(V)sleep 2$(V)$(TERMINAL) -e "gdb -q -x tools/lab1init"在调用qemu时增加-d in_asm -D q.log参数,便可以将运行的汇编指令保存在q.log 中。

(2)在初始化位置0x7c00 设置实地址断点,测试断点正常。

在tools/gdbinit结尾加上set architecture i8086b *0x7c00 //在0x7c00处设置断点。

continuex /2i $pc //显示当前eip处的汇编指令(3)将执行的汇编代码与bootasm.S 和bootblock.asm 进行比较,看看二者是否一致。

Notice:在q.log中进入BIOS之后的跳转地址与实际应跳转地址不相符,汇编代码也与bootasm.S 和bootblock.asm不相同。

lab1汇编语言与DOS系统实验报告

汇编语言与DOS系统实验报告一、实验目的1、掌握x86体系段式内存组织方式,了解如何用程序指令访问不同的内存空间2、了解DOS系统的基本操作3、掌握汇编语言的编译和调试方法二、实验条件1、DOS操作系统平台三、实验原理1、x86实模式下内存采用分段的组织方式,将20位的地址空间分为16位的段地址和16位的偏移地址,表示为“段地址:偏移地址”的形式,实际物理地址=段地址×16+偏移地址。

2、DOS系统基本操作命令:(1)cd命令进入磁盘或文件夹(2)dir命令列出目录下的文件(3)makedir创建目录(4)del删除文件(5)copy复制文件(6)rename文件重命名3、汇编语言编译命令:(1)edit命令编辑程序(2)masm生成目标文件(3)link链接生成可执行文件(4)输入文件名运行程序4、程序调试方法使用debug命令调试程序,常用的调试参数有:(1)-u反汇编生成程序的汇编代码(2)-d查看内存地址的内容(3)-p/t单步调试(4)-g设置断点(5)-e修改指定地址内容四、实验内容1、写出A+B problem的汇编代码,使用编译命令生成可执行文件并使用debug加载可执行程序。

实验代码如下:DATA SEGMENTADDER1 DB 35HADDER2 DB 48HSUM DB ?DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA START: MOV AX,DATA MOV DS,AXMOV AL,ADDER1ADD AL,ADDER2MOV SUM,ALMOV AX,4C00HINT 21HCODE ENDSEND START首先将源文件使用masm命令和link命令生成可执行文件,使用debug命令调试程序,使用-u参数显示汇编代码,g命令设置断点到MOV SUM,AL指令处,此时使用d ds:0000即可在内存中显示两个加数以及两个数的和的数值,可以使用-e命令修改参数。

深入理解计算机系统LAB1实验报告

LAB1实验报告语法检查:正确性检查:1.bitAnd源代码:return ~(~x|~y);思路:可以直接运用摩尔定律,写出与的等价形式。

2.getByte源代码:return (x>>(n<<3))&0xff;思路:向右移动3n位,再用11111111B按位与,截取出所需要的字节3.logicalShift源代码:int logic=~(((1<<31)>>n)<<1);return logic&(x>>n);思路:设置一个变量logic,并通过算数移位将其前n为设置成0,后面32-n位设置为1。

利用这个变量按位与移位后的x即可。

4.bitCount源代码:int bitCount(int x) {int result;int half_one=(0x55)|(0x55<<8);int one=(half_one)|(half_one<<16);int half_two=(0x33)|(0x33<<8);int two=(half_two)|(half_two<<16);int half_three=(0x0f)|(0x0f<<8);int three=(half_three)|(half_three<<16);int four=(0xff)|(0xff<<16);int five=(0xff)|(0xff<<8);result=(x&one)+((x>>1)&one);result=(result&two)+((result>>2)&two);result=(result+(result>>4))&three;result=(result+(result>>8))&four;result=(result+(result>>16))&five;return result;}思路:主要还是使用二分法,通过以为设置五个字符串:010101010101010101010101 0101 01010011 0011 0011 0011 0011 0011 0011 00110000 1111 0000 1111 0000 1111 0000 11110000 0000 1111 1111 0000 0000 1111 11110000 0000 0000 0000 1111 1111 1111 1111分别通过按位与统计1的个数,并将个数记录在下一个字符串1出现的位置。

系统结构综合性实验报告

综合性实验报告2012-2013-2课程名称:《计算机体系结构》班级:学号:姓名:实验项目:指令流水线相关性分析1 实验目的与要求:通过使用WINDLX模拟器,对程序中的三种相关现象进行观察,并对使用专用通路,增加运算部件等技术对性能的影响进行考察,加深对流水线和RISC处理器的特点的理解。

2 实验内容:指令流水线中主要有结构相关、数据相关、控制相关。

相关影响流水线性能。

流水线中的相关是指相邻或相近的指令因存在某种关联,后面的指令不能在原指定的时钟周期开始执行。

实验设备环境:WinDLX模拟器可以装入DLX汇编语言程序,然后单步、设置断点或者连续执行该程序。

CPU的寄存器、流水线、I/O和存储器都可以使用图形的方式表示出来。

模拟器还提供了对流水线操作的统计功能。

该模拟器对理解流水线和RISC处理器的特点很有帮助。

使用WinDLX模拟器,对求阶乘程序Fact.s做分析。

3实验过程给出分析结果,相关理论依据实验过程、分析结果和相关理论依据:本实验中所有浮点运算部件的延时都设定为4个周期,而且一开始未使用Forwarding部件。

)1.实验中浮点运算部件的设置如下图:2.指出程序中出现的数据/控制/结构相关的指令组合。

a.fact.s汇编源代码如下(指令相关性已注):.dataPrompt: .asciiz "An integer value >1 : " PrintfFormat: .asciiz "Factorial = %g\n\n" .align 2PrintfPar: .word PrintfFormat PrintfValue: .space 8.text .global main main: ;*** Read value from stdin into R1 addi r1,r0,Prompt jal InputUnsigned ;*** init values movi2fp f10,r1cvti2d f0,f10 addi r2,r0,1 movi2fp f11,r2cvti2d f2,f11 movd f4,f2 Loop:led f0,f4 bfpt Finish ;*** Multiplication and next loop multd f2,f2,f0 subd f0,f0,f4 ;此句与循环开始的led f0,f4因f0、f4产生RAW 相关j Loop ;Finish: ;*** write result to stdoutsd PrintfValue,f2 addi r14,r0,PrintfPar trap 5 ;*** end trap 0b. input.s 汇编源代码如下(相关性见标注):.data ReadBuffer: .space 80ReadPar: .word 0,ReadBuffer,80;*** Data for Printf-Trap PrintfPar: .space 4因转移指令产生控制相关 因f4产生RAW 相关 因r2产生RAW 相关 因f11产生RAW 相关因f2产生RAW 相关 因f10产生RAW 相关SaveR2: .space 4 SaveR3: .space 4 SaveR4: .space 4 SaveR5:.space 4.text.global InputUnsigned InputUnsigned:;*** save register contents sw SaveR2,r2 sw SaveR3,r3 sw SaveR4,r4 sw SaveR5,r5;*** Promptsw PrintfPar,r1addi r14,r0,PrintfPar trap 5;*** call Trap-3 to read line addi r14,r0,ReadPar trap 3;*** determine valueaddi r2,r0,ReadBuffer addi r1,r0,0 addi r4,r0,10Loop: ;*** reads digits to end of line lbu r3,0(r2) seqi r5,r3,10 bnez r5,Finish subi r3,r3,48 multu r1,r1,r4add r1,r1,r3 addi r2,r2,1j Loop ;Finish: ;*** restore old register contents lw r2,SaveR2 lw r3,SaveR3 lw r4,SaveR4 lw r5,SaveR5 jr r31 ; 因转移指令产生控制相关因转移指令产生控制相关 因r1产生RAW 相关因r3产生RAW 相关 因PrintfPar 产生RAW 相关3.运行输出及统计结果:a.运行时输入20,输出如下:b.统计结果如下:c.统计结果分析:i.总计(运行时输入数据为20):1.一共执行了272个时钟周期。

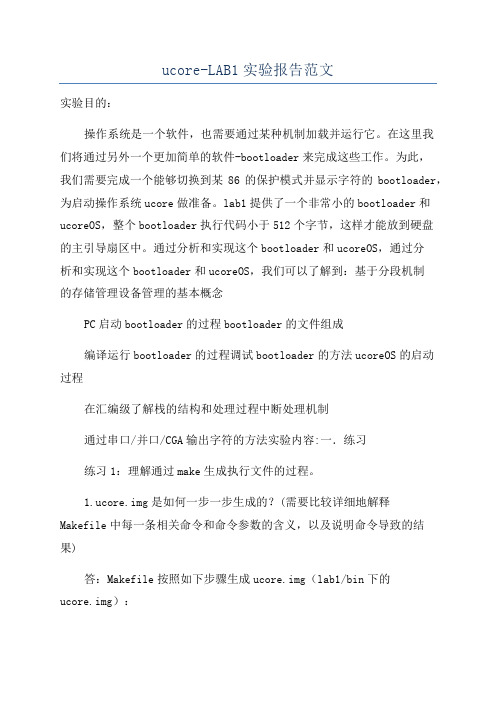

ucore-LAB1实验报告范文

ucore-LAB1实验报告范文实验目的:操作系统是一个软件,也需要通过某种机制加载并运行它。

在这里我们将通过另外一个更加简单的软件-bootloader来完成这些工作。

为此,我们需要完成一个能够切换到某86的保护模式并显示字符的bootloader,为启动操作系统ucore做准备。

lab1提供了一个非常小的bootloader和ucoreOS,整个bootloader执行代码小于512个字节,这样才能放到硬盘的主引导扇区中。

通过分析和实现这个bootloader和ucoreOS,通过分析和实现这个bootloader和ucoreOS,我们可以了解到:基于分段机制的存储管理设备管理的基本概念PC启动bootloader的过程bootloader的文件组成编译运行bootloader的过程调试bootloader的方法ucoreOS的启动过程在汇编级了解栈的结构和处理过程中断处理机制通过串口/并口/CGA输出字符的方法实验内容:一.练习练习1:理解通过make生成执行文件的过程。

1.ucore.img是如何一步一步生成的?(需要比较详细地解释Makefile中每一条相关命令和命令参数的含义,以及说明命令导致的结果)答:Makefile按照如下步骤生成ucore.img(lab1/bin下的ucore.img):①为每一个源文件(.c和.S文件)产生一个描述其依赖关系的makefile文件,以.d为后缀。

即对于一个源文件“NAME.c”,对应的这个makefile文件为“NAME.d”。

包括分别生成ign.c、bootmain.c、bootam.S的makefile依赖文件ign.d、bootmain.d、bootam.d,具体执行的命令如下:mkdir-pobj/ign/toolgcc-Itool/-g-Wall-O2-MMtool/ign.c-MT\obj/ign/tool/ign.dmkdir-pobj/bootgcc-Iboot/-fno-builtin-Wall-ggdb-m32-notdinc-fno-tack-protector-Ilib/-O-notdinc-MMboot/bootmain.c-MT\gcc-Iboot/-fno-builtin-Wall-ggdb-m32-notdinc-fno-tack-protector-Ilib/-O-notdinc-MMboot/bootam.S-MT\gcc重要的编译参数:-I指定搜索系统头文件的目录,可以重复使用多个该选项指定多个目录-Wall显示所有的警告消息-O2优化(级别为2)-m32指明目标代码32位-O对生成的二进制代码进行尺寸上的优化-ggdb提供编译信息-notdinc只为头文件寻找-I选项指定的目录-fno-builtin除非利用\进行引用,否则不识别所有内建函数-fno-tack-protector不检测缓存溢出②编译源文件,只生成目标文件但不链接。

lab1 操作系统试验

实验一 Linux系统的基本操作1.目的要求熟悉Linux系统运行环境,掌握Linux操作系统上的基本操作。

2、实验内容1)登录Linux系统和使用GNOMEa)在启动系统,登陆进入系统后,桌面上有3个图标,它们的名字和作用是什么?它们和windows系统的什么软件功能相当?A.B.C.b)在屏幕的最下方,有一个快捷栏,其中有哪些图标,它们的名字和作用是什么?它们和windows系统的什么软件功能相当?A.B.C.D.E.F.2)Linux系统的基本命令a)列举打开Linux终端的两种方式,分别叙述其过程A.B.b) 使用命令可以查看用户当前所处的工作目录,你的工作目录是b)使用__________________命令可以查看当前文件夹的内容c)分别键入命令who,man date,cal5,exit解释各个命令具体实现的功能A.B.C.D.3)Linux系统的文件、目录和权限a)查询当前用户所处的位置b)在当前文件夹下创建一个名为os的文件夹c)使os目录成为当前目录d)创建一个名为file.c的文本文件,该文件放置在文件夹os中e)把file.c文件拷贝到用户主目录中(登陆进系统时所处的目录),文件名不变f)把主目录中的file.c文件更名为source.cg)返回到主目录h)使用命令"ls –l",其显示内容是什么?对各列内容进行解释?i)删除文件夹osj)删除当前目录下所有以source开始的文件4)Linux通配符的使用。

在当前目录下创建五个文件(inv1jig.c、inv2jig.c、inv3jig.c、invinitjig.c、invpar.c) ,列出下述每个命令的运行结果,并解释原因命令:$ ls inv?jig.c结果:____________________________________________________________________ 原因:命令:$ ls inv[13]jig.c结果:____________________________________________________________________ 原因:命令:$ ls inv[1-3]jig.c结果:____________________________________________________________________ 原因:命令:$ ls inv*jig.c结果:____________________________________________________________________ 原因:命令:$ ls *[0-9]*.[co]结果:____________________________________________________________________ 原因:4)Linux文件系统a) 使用"cd /"和"ls"两个命令后,你能看到一些什么文件夹,它们的主要作用是什么?列举几个你所熟悉的文件夹A.B.C.D.5)Linux系统注销方式,至少两种A.B.3、准备工作1)Linux操作系统、获取登陆帐户和密码。

系统结构实验报告

系统结构实验报告系统结构实验报告引言:系统结构是计算机科学中的一个重要概念,它描述了一个系统的组成部分以及它们之间的相互关系。

在本次实验中,我们将探索系统结构的基本原理,并通过实际操作来加深对系统结构的理解。

一、系统结构的定义与作用系统结构是指一个系统的组成部分以及它们之间的连接方式和关系。

它决定了系统的功能、性能和可靠性。

一个良好的系统结构设计能够提高系统的效率和可维护性,降低系统的成本和风险。

二、系统结构的基本组成一个系统的结构通常由以下几个基本组成部分构成:1. 处理器:负责执行指令和控制系统的运行。

2. 存储器:用于存储数据和指令。

3. 输入设备:用于接收外部输入。

4. 输出设备:用于向外部输出结果。

5. 总线:用于连接各个组件,传输数据和控制信号。

三、系统结构的层次结构系统结构可以分为多个层次,每个层次负责不同的功能和任务。

常见的系统结构层次包括:1. 应用层:负责处理用户的请求和提供服务。

2. 操作系统层:负责管理硬件资源和提供系统服务。

3. 中间件层:负责处理分布式系统的通信和协调。

4. 数据库层:负责管理和维护数据。

5. 硬件层:负责执行指令和存储数据。

四、系统结构的优化与改进为了提高系统的性能和可靠性,我们可以采取一些优化和改进措施,例如:1. 并行处理:利用多个处理器同时执行任务,提高系统的处理能力。

2. 分布式系统:将系统分布在多个节点上,提高系统的可伸缩性和容错性。

3. 冗余设计:在关键部件上增加冗余,提高系统的可靠性和可恢复性。

4. 缓存技术:利用高速缓存存储器提高数据访问速度。

5. 虚拟化技术:通过虚拟化将物理资源划分为多个逻辑资源,提高资源利用率。

五、实验过程与结果在本次实验中,我们搭建了一个简单的系统结构,并进行了一系列测试和优化。

通过测试,我们发现系统的性能在并行处理和缓存技术的应用下得到了显著提升。

同时,我们也发现系统的可靠性在冗余设计和虚拟化技术的应用下得到了增强。

体系结构实验报告

.课程实验报告软件系统结构专业软件工程学生辉班级软件151学号1510701117指导老师莉实验一C/S结构应用设计(1)一、实验目的设计并实现一个基于多层C/S结构的数据库应用,熟悉多层C/S体系结构及其基本处理流程,了解多层结构表现层、业务逻辑层(功能层)、数据访问层所完成的功能,掌握多层C/S结构的数据库应用设计方法,对这三层进行明确分割,并在逻辑上使其独立。

学生通过本实验的训练能够熟练掌握对小型数据库应用系统三层结构层次划分方法及系统实现技术。

本次实验目的:(1)熟悉并掌握二层C/S软件体系结构的相关知识;(2)掌握二层C/S结构应用系统的分析和设计;(3)掌握一种开发二层C/S结构应用系统的技术线路;(4)实际开发出一个简单的基于二层C/S结构的应用实例——个人通讯录管理系统。

要求:(1)需要预先掌握SQL server 2000数据库基本操作、(用C#语言)编程技术和多层C/S软件体系结构的概念;(2)进行二层C/S结构应用系统的分析和设计,在实验报告中写出个人通讯录管理系统的设计方案;(3)在SQL server 2000数据库系统中建立数据库并输入数据;(4)在中用C#语言编写表现层(UI)程序;(5)在中用C#语言编写业务逻辑层(BLL)程序;(6)完成系统调试,得出正确的实验结果;(7)做完实验后写出本实验的实验报告。

二、实验环境奔腾以上计算机,装有SQL Server 2000数据库系统和Visual Studio 2000软件。

三、实验容1、分别采用二层C/S结构和多层C/S结构实现个人通讯录系统。

该系统的设计目标是能够轻松地管理个人的联系人信息,包括添加、修改和删除操作。

联系人信息包括、住址、。

整个系统的功能图如下图所示:分析系统需求,完成软件体系结构设计及模块划分、数据库设计,采用Visual C#实现系统功能四、实验操作过程在电脑上安装好Microsoft Visual Studio 2010 用于系统的开发需要实际设计开发出一个简单的基于两层C/S结构的应用系统——个人通讯录管理系统,主要步骤和容如下:1、在SQL Server 2000中建立数据库Contact,建立表friend。

Lab1实验报告

2012 FPGA 基础实验:SWITCH, PUSHBUTTON andLEDLAB1实验报告王红宾5090519061SJTU | F09051031实验概述1.1实验名称FPGA 基础实验:SWITCH, PUSHBUTTON and LED1.2 实验目的1.掌握Xilinx逻辑设计工具ISE的设计流程2.掌握UCF(用户约束文件)的用法和作用3.初步掌握使用VerilogHDL硬件描述语言进行简单的逻辑设计4.熟悉Xilinx Spartan 3E实验板卡1.3实验范围本次实验将覆盖以下范围:1.ISE11.1的使用2.iMPACT的使用3.编辑UCF4.Spartan 3E实验板的使用5.使用VerilogHDL进行逻辑设计1.4注意事项1. 本实验的逻辑设计工具为Xilinx ISE11.1。

2新建工程,导入文件2.1实验描述2.1.1新建工程1.启动ISE 11.1。

2.选择File > New Project… 出现New Project Wizard。

3.Project Name填写lab1,选择工程Project Location,Top-level Source Type选择HDL。

点击Next。

4. Device Properties 中各属性填写如下:Product Category: ALLFamily: Spartan3EDevice: XC3S500EPackage: FG320Speed: -4Synthesis Tool: XST(VHDL/Verilog)Simulator: ISim (VHDL/Verilog)Preferred Language: Verilog确认Enable Enhanced Design Summary 已勾选5. 点击Next6. 在New Project Wizard 中点击New Source…。

文件类型选择Verilog Module,文件名填写led,勾选Add to project。

数字系统设计LabA1实验报告

实验报告 课程名称: 数字系统设计实验Ⅰ 指导老师: 屈民军/唐奕/马洪庆 成绩:__________________ 实验名称: 补充实验一 常用组合电路模块的设计和应用_实验类型:设计型_一、实验目的和要求(必填) 二、实验内容和原理(必填)三、主要仪器设备(必填) 四、操作方法和实验步骤五、实验数据记录和处理 六、实验结果与分析(必填)七、讨论、心得一、 实验目的略二、 实验内容和原理实验内容:1. 任务一两数之差的绝对值电路的设计(1)编写一位全加器的Verilog HDL 代码,并用ModelSim 软件进行功能仿真。

(2)编写N 位二选一数据选择器的Verilog HDL 代码及其测试代码,并用ModelSim 软件进行功能仿真。

注意,N 为参数,表示数据选择器数的位数。

(3)编写N 位比较器的Verilog HDL 代码,并用ModelSim 软件进行功能仿真。

注意,N 为参数,表示比较器的位数。

(4)对两数之差的绝对值电路进行功能仿真。

(5)建立ISE 工程文件,对工程进行综合、引脚约束、实现,并下载到开发实验板中对设计进行验证,注意:①本设计为组合电路,所以无需进行时序约束。

②本设计的引脚约束内容如表A.2所示。

2. 任务二模式比较器编写模式比较器的Verilog HDL 代码,并用ModelSim 软件进行功能仿真。

实验原理略 三、 主要仪器设备计算机四、 操作方法和实验步骤1、 依照给出的顶层设计代码完善各模块代码:比较器中用if 语句比较a ,b 大小并靠改变agb 的值输出结果;数据选择器直接用assign 连续赋值语句,根据sel 的值选择输出;全加器考虑进位,因此根据二进制特点将位输出用异或运算表示,将进位输出用与或运算表示;2、 将代码复制到虚拟机,打开Modelsim 进行功能仿真,中途出现的error/warning 等尝试修改代码进行修复,直到仿真成功。

然后观察波形,分析设计代码是否正确;3、 打开ISE 工程文件,对工程进行综合、引脚约束、实现,并在实验室将工程下载到开发实验板中对设计进行验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2012年3月1日一、实验目的和要求1.understand the principles of ALU and master methods of ALU design2.understand the principles of ALU controller and master methods of ALUcontroller design3.understand the principles of register file and master methods of register filedesignso the task isfirst, design a ALU with ALU controllerthen, design a register file二、实验内容和原理2.1 ALU with ALU controllerWe input the operand r, s; both are 32 bit integer, and aluc is the control code that defines the operation.So we just make the code block, totally as ALU block, ALUC block, display block.Figure 1 the input and output diagramFigure 2 ALU operationsFigure 3 the truth table of operation cod eFigure 4 principle of ALU2.2 register fileThe process is similar to the 2.1, when we get the principle of register file , it can be easily coding.Figure 5 the input and outputFigure 6 The Circuit Integrating ALU三、实验过程和数据记录1.ALU and ALU ControllerHere is the code:Top block:module ALUC(input CCLK, input [1:0]BTN, input [3:0] SW, output LCDRS, LCDRW, LCDE, output [3:0] LCDDAT,output LED);wire [3:0] lcdd;wire rslcd, rwlcd, elcd;wire o_zf;wire [31:0] o_alu;wire [2:0] i_aluc;wire [1:0] alu_op;wire [3:0] func;reg [31:0] o_alu_old;reg [255:0] strdata;reg [31:0] i_r;reg [31:0] i_s;reg rst;assign LCDDAT[3] = lcdd[3];assign LCDDAT[2] = lcdd[2];assign LCDDAT[1] = lcdd[1];assign LCDDAT[0] = lcdd[0];assign LCDRS = rslcd;assign LCDRW = rwlcd;assign LCDE = elcd;assign LED = o_zf;assign func[0] = SW[0];assign func[1] = SW[1];assign func[2] = SW[2];assign func[3] = SW[3];assign alu_op[0] = BTN[0];assign alu_op[1] = BTN[1];initial beginstrdata = "1111 2222 ";i_r = 32'h1111;i_s = 32'h2222;rst = 0;o_alu_old = 0;enddisplay M0 (CCLK, rst, strdata, rslcd, rwlcd, elcd, lcdd); single_alu M1(i_r, i_s, i_aluc, o_zf, o_alu);single_aluc M2(alu_op, func, i_aluc);always @(posedge CCLK) beginif (o_alu_old != o_alu) beginstrdata[127:120] = 8'h30 + o_alu[15:12];strdata[119:112] = 8'h30 + o_alu[11:8];strdata[111:104] = 8'h30 + o_alu[7:4];strdata[103:96] = 8'h30 + o_alu[3:0];o_alu_old = o_alu;endelserst = 0;endendmoduledisplay:module display(input CCLK, reset,input [255:0]strdata, output rslcd, rwlcd, elcd,output [3:0] lcdd);wire [7:0] lcddatin;lcd M0 (CCLK, resetlcd, clearlcd, homelcd, datalcd, addrlcd,lcdreset, lcdclear, lcdhome, lcddata, lcdaddr,rslcd, rwlcd, elcd, lcdd, lcddatin, initlcd);genlcd M1 (CCLK, reset, strdata, resetlcd, clearlcd, homelcd, datalcd,addrlcd, initlcd, lcdreset, lcdclear, lcdhome,lcddata, lcdaddr, lcddatin); endmodulemodule genlcd(input CCLK, debpb0, input [255:0]strdata, output reg resetlcd,output reg clearlcd, output reg homelcd,output reg datalcd, output reg addrlcd,output reg initlcd, input lcdreset, lcdclear,input lcdhome, lcddata, lcdaddr,output reg [7:0] lcddatin);reg [3:0] gstate; // state register integer i;always@(posedge CCLK)beginif (debpb0==1)beginresetlcd=0;clearlcd=0;homelcd=0;datalcd=0;gstate=0;endelsecase (gstate)0: begininitlcd=1;gstate=1;end1: begininitlcd=0;gstate=2;end2: beginresetlcd=1;if (lcdreset==1)beginresetlcd=0;gstate=3;endend3: begininitlcd=1;gstate=4;end4: begininitlcd=0;gstate=5;end5: beginclearlcd=1;if (lcdclear==1)beginclearlcd=0;gstate=6;endend6: begininitlcd=1;gstate=7;end7: begininitlcd=0;i=255;gstate=8;end8: beginif(i>127)lcddatin[7:0]=8'b0000_0000;elselcddatin[7:0]=8'b0100_0000;addrlcd=1;if (lcdaddr==1)beginaddrlcd=0;gstate=9;endend9: begininitlcd=1;gstate=10;end10: begininitlcd=0;gstate=11;end11: beginlcddatin[7:0]=strdata[i-:8];datalcd=1;if (lcddata==1)begindatalcd=0;gstate=12;endend12: begininitlcd=1;gstate=13;end13: begininitlcd=0;gstate=14;end14: begini=i-8;if (i<0)gstate=15;else if (i==127)gstate=8;elsegstate=11;end15: gstate=15;default: gstate=15;endcaseendendmodulemodule single_alu(i_r,i_s,i_aluc,o_zf,o_alu);input [31:0] i_r; //i_r: r inputinput [31:0] i_s; //i_s: s inputinput [2:0] i_aluc; //i_aluc: ctrl inputoutput o_zf; //o_zf: zero flag outputoutput [31:0] o_alu; //o_alu: alu result outputreg o_zf;reg [31:0] o_alu;always @(i_aluc or i_r or i_s) begincase (i_aluc)3'b010:o_alu=i_r+i_s;3'b110:o_alu=i_r-i_s;3'b000:o_alu=i_r&i_s;3'b001:o_alu=i_r|i_s;3'b111:o_alu=i_r<i_s?1:0;/////////////////////////////////////////在此添加根据i_aluc的值对o_alu和o_zf进行赋值endcaseif(o_alu==0)o_zf=1;elseo_zf=0;endendmodulemodule single_aluc(aluop, func, aluc);input [1:0] aluop;input [5:0] func;output [2:0] aluc;reg [2:0] aluc;always @(aluop or func) begincase (aluop)2'b00:aluc=3'b010;2'b01:aluc=3'b110;default:begincase (func[3:0])4'b0000:aluc=3'b010;4'b0010:aluc=3'b110;4'b0100:aluc=3'b000;4'b0101:aluc=3'b001;4'b1010:aluc=3'b111;endcaseend//根据aluop和func的不同值,对aluc进行赋值。