计算机组成与 结构试题A卷2009-2010

计算机体系结构试卷2009-2010 2B(标准答案)

(答案要注明各个要点的评分标准)一、 名词解释(每小题5分,共20分)1、 答:程序在执行时所访问地址的分布不是随机的,而是相对地簇聚;这种簇聚包括指令和数 据两部分。

2、 答:当第一次访问一个块时,该块不在Cache 中,需从下一级存储器中调入Cache ,这就是强制性失效。

3、 答:当一条指令需要用到前面某条指令的结果,从而不能重叠执行时,就发生了数据相关。

4、 答:计算机体系结构的定义:程序员所看到的计算机的属性,即概念性结构与功能特性。

二、 简答题(每小题10分,共30分)1、 (1)全相联映。

主存中的任一块可以被放置到Cache 中的任意一个位置。

(2分)(2)直接映象:主存中的每一块只能被放置到Cache 中唯一的一个位置。

(2分)(3)组相联:主存中的每一块可以被放置到Cache 中唯一的一个组中的任何一个位置。

(2分)全相联映像的查找过程复杂,但失效率低,而直接映像的查找过程简单,但失效率高。

而组相联影响的优缺点介于全相联映像和直接映像之间。

(4分)2、答:从用户的角度来看,存储器的三个主要指标是:容量,速度,价格(每位价格)。

而这三个指标是相互矛盾的。

因此,解决方法就是采用多种存储器技术,构成存储层次。

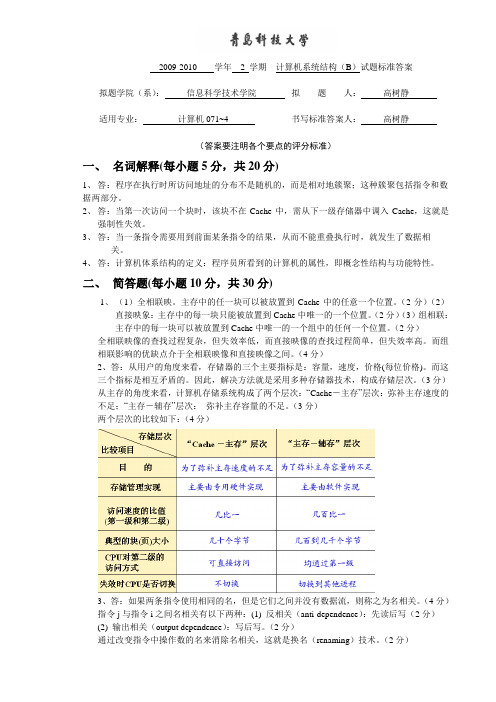

(3分) 从主存的角度来看,计算机存储系统构成了两个层次:“Cache -主存”层次:弥补主存速度的不足;“主存-辅存”层次: 弥补主存容量的不足。

(3分)两个层次的比较如下:(4分)3、答:如果两条指令使用相同的名,但是它们之间并没有数据流,则称之为名相关。

(4分) 指令j 与指令i 之间名相关有以下两种:(1) 反相关(anti-dependence ):先读后写(2分)(2) 输出相关(output dependence ):写后写。

(2分)通过改变指令中操作数的名来消除名相关,这就是换名(renaming )技术。

(2分)4、答:增加块大小会增加失效开销增加块大小引起的双重作用:(1)减少强制性失效;(2)块大小增加后,块数目减少,增加冲突失效。

2009(2010计算机基础考试试卷(附答案))-

2009(2010计算机基础考试试卷(附答案))-在XXXX年,计算机中使用的基本电子元件经历了四个发展阶段,通常被称为计算机发展的四个阶段,以b为发展顺序A、晶体管、电子管、中小规模集成电路、大规模和超大规模集成电路B、电子管、晶体管、中小规模集成电路、大规模和超大规模集成电路C,中小规模集成电路,电子管,晶体管,大规模和超大规模集成电路D,大规模和超大规模集成电路,电子管,晶体管,中型小型集成电路2的思想和冯·诺依曼的“程序存储”首先体现在C计算机上1993年,爱德华·罗伯茨在1971年发明了第一台微型计算机。

A,苹果ⅱB,国际商用机器公司个人电脑/个人电脑C,牛郎星d,织女星4,指令的数量和类型由a决定A、中央处理器B、动态随机存取存储器C、静态随机存取存储器D、基本输入输出系统5和主板的性能主要由C芯片决定。

甲、中央处理器乙、南桥丙、北桥丁、内存6,微机硬件的主要技术指标有:性能、功能、乙、兼容性等技术参数A,安全性b,可靠性c,实用性d,经济性7。

在计算机硬件上配置的第一层软件是b语言处理程序b,操作系统c,工具软件d,数据库管理系统8,在视窗XP中将当前屏幕图像复制到剪贴板的键名是bA,Alt+空格B,PrintScreen(Prtsc) C,Alt+ PrintScreen(Prtsc) D,F19,视窗XP任务栏不能做的是DA,显示改变系统日期和时间b,启动应用程序C,在多个程序和任务之间切换d,在桌面上排列图标10,标志的大写字母锁定键是AA,大写锁定B,数字锁定C,滚动锁定D,暂停11,回收站是在D中打开的用于存储已删除文件或文件夹的空间A,内存b,动态随机存取存储器C,闪存d,硬盘12,在不同磁盘之间移动文件或文件夹是一个A操作目录结构为A,复制b,移动c,粘贴d,删除13和视窗XP,用于组织和管理文件属于cA,层次类型b,关系类型c,树类型d,网络类型14。

《计算机组成与结构》复习题及答案 (1)

《计算机组成与结构》复习题及答案第1章一、一、选择题1、1、计算机系统应包括()。

A)运算器、存储器、控制器B)主机与外部设备C)硬件系统与软件系统D)系统软件与应用软件2、2、下列描述不正确的是()。

A)一种计算机的机器语言就是计算机的指令系统。

B) 汇编语言是一种符号语言,是与机器有关的语言。

C)高级语言是与机器无关的,高级语言源程序编译成目标程序之后,可在各种机器上运行。

D)只有机器语言程序在计算机中才能直接运行。

3、3、关于冯诺依曼计算机,下列叙述不正确的是()A)计算机硬件由控制器、运算器、存储器、输入设备、输出设备五部分组成。

B) 数据和程序在计算机中都用二进制数表示,且存放于计算机的存储器这中。

C)冯诺依曼计算机是一种虚拟计算机系统。

D)目前的大多计算机还是基于冯诺依曼计算机的。

4、4、硬件在功能实现上比软件强的是()。

A)速度快B)成本低C)灵活性强D)实现容易5、5、在计算机系统的层次结构中,不属虚拟机的层次是()。

A)高级语言计算机B)OS语言计算机C)汇编语言计算机D)机器语言6、6、把计算机的发展史划分为四代的依据是()。

A)计算机规模B) 计算机速度C)OS D)物理器件(逻辑元件)7、7、微型计算机出现在那一代()A)第一代B) 第二代C)第三代D)第四代8、8、下列叙述正确的是()。

A)大型计算机是指大型通用计算机,它属C/S模式的。

B) 巨型计算机更适合于高速度、大容量的计算机任务。

C)V AX、PDP都属于小型计算机,二者是相兼容的。

D)工作站可以认为是一种高性能的微型计算机。

9、9、下列计算任务与应用领域相匹配的是()A)卫星与运载火箭轨道的计算/计算科学B)企业信息系统/数据处理C)程控机床加工/计算机控制D)智能机器人/人工智能10、10、对英文缩写解释正确的是()A)CPU:中央处理单元B)ALU:算术逻辑部件C)DBMS:数据库管理系统D) CMD / CAD:计算机辅助制造/计算机辅助设计11、11、对计算机软件硬件资源进行管理的是()A)高级语言处理程序B)操作系统C)数据库管理系统D)应用程序12、12、计算机硬件系统直接运行的程序是()A)源程序B)目标程序C)汇编语言程序D)高级语言程序13、13、将高级语言源程序转化目标程序的过程是()A)汇编B)编译C)解释D)译码13.反映计算机基本功能的是( )。

南京大学计算机组成原理2019冬试题A答案 (1)

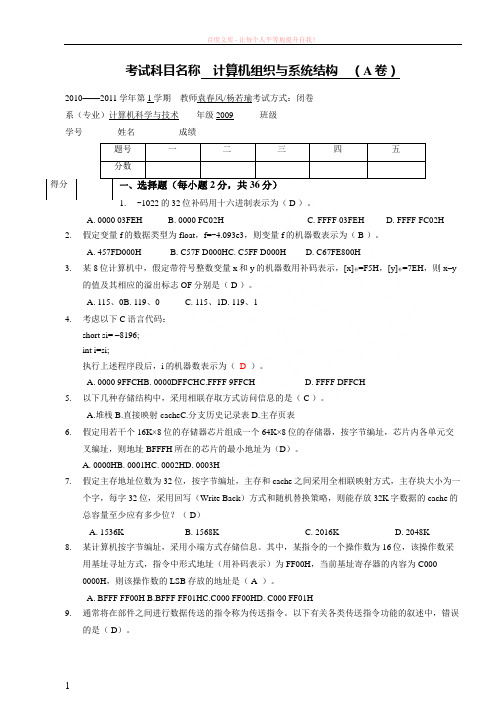

考试科目名称计算机组织与系统结构(A卷)2010——2011学年第1学期教师袁春风/杨若瑜考试方式:闭卷系(专业)计算机科学与技术年级2009班级学号姓名成绩题号一二三四五分数得分一、选择题(每小题2分,共36分)1.-1022的32位补码用十六进制表示为( D )。

A. 0000 03FEHB. 0000 FC02HC. FFFF 03FEHD. FFFF FC02H2.假定变量f的数据类型为float,f=-4.093e3,则变量f的机器数表示为( B )。

A. 457FD000HB. C57F D000HC. C5FF D000HD. C67FE800H3.某8位计算机中,假定带符号整数变量x和y的机器数用补码表示,[x]补=F5H,[y]补=7EH,则x–y的值及其相应的溢出标志OF分别是( D )。

A. 115、0B. 119、0C. 115、1D. 119、14.考虑以下C语言代码:short si= –8196;int i=si;执行上述程序段后,i的机器数表示为(D)。

A. 0000 9FFCHB. 0000DFFCHC.FFFF 9FFCHD. FFFF DFFCH5.以下几种存储结构中,采用相联存取方式访问信息的是( C )。

A.堆栈B.直接映射cacheC.分支历史记录表D.主存页表6.假定用若干个16K×8位的存储器芯片组成一个64K×8位的存储器,按字节编址,芯片内各单元交叉编址,则地址BFFFH所在的芯片的最小地址为(D)。

A. 0000HB. 0001HC. 0002HD. 0003H7.假定主存地址位数为32位,按字节编址,主存和cache之间采用全相联映射方式,主存块大小为一个字,每字32位,采用回写(Write Back)方式和随机替换策略,则能存放32K字数据的cache的总容量至少应有多少位?( D)A. 1536KB. 1568KC. 2016KD. 2048K8.某计算机按字节编址,采用小端方式存储信息。

计算机组成原理期末试卷A (1)东华理工

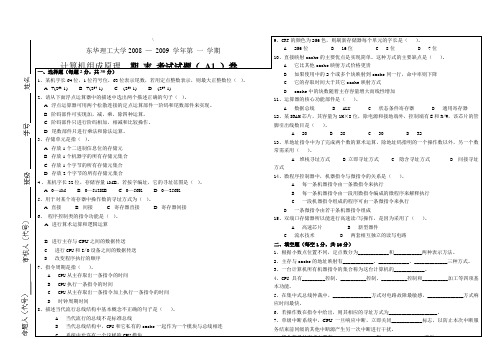

\东华理工大学2008 —2009 学年第一学期计算机组成原理期末考试试题(A1 )卷9、CRT的颜色为256色,则刷新存储器每个单元的字长是()。

A 256位B 16位C 8位D 7位10、直接映射cache的主要优点是实现简单。

这种方式的主要缺点是()。

A 它比其他cache映射方式价格更贵B 如果使用中的2个或多个块映射到cache同一行,命中率则下降C 它的存取时间大于其它cache映射方式D cache中的块数随着主存容量增大而线性增加11、运算器的核心功能部件是()。

A 数据总线B ALUC 状态条件寄存器D 通用寄存器12、某SRAM芯片,其容量为1M×8位,除电源和接地端外,控制端有E和R/W,该芯片的管脚引出线数目是()。

A 20B 28C 30D 3213、单地址指令中为了完成两个数的算术运算,除地址码指明的一个操作数以外,另一个数常需采用()。

A 堆栈寻址方式B 立即寻址方式C 隐含寻址方式D 间接寻址方式14、微程序控制器中,机器指令与微指令的关系是()。

A 每一条机器指令由一条微指令来执行B 每一条机器指令由一段用微指令编成的微程序来解释执行C 一段机器指令组成的程序可由一条微指令来执行D 一条微指令由若干条机器指令组成15、双端口存储器所以能进行高速读/写操作,是因为采用了()。

A 高速芯片B 新型器件C 流水技术D 两套相互独立的读写电路二、填空题(每空1分,共16分)1、根据小数点位置不同,定点数分为____________和___________两种表示方法。

2、主存与cache的地址映射有____________、____________、_____________三种方式。

3、一台计算机所有机器指令的集合称为这台计算机的____________。

4、CPU具有_________控制、__________控制、__________控制和__________加工等四项基本功能。

计算机组成与结构 试题及答案(2套)

试卷A一、填空题:(每空1分,共15分)1、原码一位乘法中,符号位与数值位(),运算结果的符号位等于()。

2、码值80H:若表示真值0,则为()码;若表示真值―128,则为()码。

3、微指令格式分为()型微指令和()型微指令,其中,前者的并行操作能力比后者强。

4、在多级存储体系中,Cache存储器的主要功能是()。

5、在下列常用术语后面,写出相应的中文名称:VLSI( ), RISC( ), DMA( ), DRAM( )。

6、为了实现CPU对主存储器的读写访问,它们之间的连线按功能划分应当包括(),()()。

7、从计算机系统结构的发展和演变看,近代计算机是以()为中心的系统结构。

二、单项选择题:(每题2分,共40分)1、寄存器间接寻址方式中,操作数处于()中。

A、通用寄存器B、主存C、程序计数器D、堆栈2、CPU是指()。

A、运算器B、控制器C、运算器和控制器D、运算器、控制器和主存3、若一台计算机的字长为2个字节,则表明该机器()。

A、能处理的数值最大为2位十进制数。

B、能处理的数值最多由2位二进制数组成。

C、在CPU中能够作为一个整体加以处理的二进制代码为16位。

D、在CPU中运算的结果最大为2的16次方4、在浮点数编码表示中,()在机器数中不出现,是隐含的。

A、基数B、尾数C、符号D、阶码5、控制器的功能是()。

A、产生时序信号B、从主存取出一条指令C、完成指令操作码译码D、从主存取出指令,完成指令操作码译码,并产生有关的操作控制信号,以解释执行该指令。

6、虚拟存储器可以实现()。

A、提高主存储器的存取速度B、扩大主存储器的存储空间,并能进行自动管理和调度C、提高外存储器的存取周期D、扩大外存储器的存储空间7、32个汉字的机内码需要()。

A、8字节B、64字节C、32字节D、16字节8、相联存储器是按()进行寻址的存储器。

A、地址指定方式B、堆栈指定方式C、内容指定方式D、地址指定方式与堆栈存储方式结合9、状态寄存器用来存放()。

2009-2010计算机考研真题及答案(含选择题解析)高清晰版

2009年统考计算机考研真题 (1)一.单项选择题,每小题2分,共80分。

(1)二.综合应用题。

共70分。

(5)2009年计算机统考真题参考答案 (9)一.选择题 (9)二.综合应用题 (21)2010年全国研究生考试计算机统考试题及答案242009年统考计算机考研真题一.单项选择题,每小题2分,共80分。

1.为解决计算机与打印机之间速度不匹配的问题,通常设置一个打印数据缓冲区,主机将要输出的数据依次写入该缓冲区,而打印机则依次从该缓冲区中取出数据。

该缓冲区的逻辑结构应该是A.栈B.队列C.树D.图2.设栈S和队列Q的初始状态均为空,元素abcdefg依次进入栈S。

若每个元素出栈后立即进入队列Q,且7个元素出队的顺序是bdcfeag,则栈S的容量至少是 A.1 B.2 C.3 D.43.给定二叉树图所示。

设N代表二叉树的根,L代表根结点的左子树,R代表根结点的右子树。

若遍历后的结点序列为3,1,7,5,6,2,4,则其遍历方式是 A.LRN B.NRL C.RLN D.RNL4.下列二叉排序树中,满足平衡二叉树定义的是5.已知一棵完全二叉树的第6层(设根为第1层)有8个叶结点,则完全二叉树的结点个数最多是A.39 B.52 C.111 D.1196.将森林转换为对应的二叉树,若在二叉树中,结点u是结点v的父结点的父结点,则在原来的森林中,u和v可能具有的关系是 I.父子关系 II.兄弟关系 III. u的父结点与v的父结点是兄弟关系A.只有IIB.I和IIC.I和IIID.I、II和III7.下列关于无向连通图特性的叙述中,正确的是I.所有顶点的度之和为偶数 II.边数大于顶点个数减1 III.至少有一个顶点的度为1A.只有IB. 只有IIC.I和IID.I和III8.下列叙述中,不符合m阶B树定义要求的是A.根节点最多有m棵子树 B.所有叶结点都在同一层上C.各结点内关键字均升序或降序排列 D.叶结点之间通过指针链接9.已知关键序列5,8,12,19,28,20,15,22是小根堆(最小堆),插入关键字3,调整后得到的小根堆是A.3,5,12,8,28,20,15,22,19B. 3,5,12,19,20,15,22,8,28C.3,8,12,5,20,15,22,28,19D. 3,12,5,8,28,20,15,22,1910.若数据元素序列11,12,13,7,8,9,23,4,5是采用下列排序方法之一得到的第二趟排序后的结果,则该排序算法只能是A.起泡排序 B.插入排序 C.选择排序 D.二路归并排序11.冯·诺依曼计算机中指令和数据均以二进制形式存放在存储器中,CPU区分它们的依据是 A.指令操作码的译码结果 B.指令和数据的寻址方式C.指令周期的不同阶段D.指令和数据所在的存储单元12.一个C语言程序在一台32位机器上运行。

计算机组成原理试卷

三类。

3. 响应时间和

吞吐率(或带宽,或数据传输率)

是衡量一个计算机系统好坏的两个基本性

能。不同应用场合,用户关心的性能不同。例如,对于银行、证券等事务处理系统来说,事务处理

用户主要关心的是

响应时间

。

4. 一个变量在计算机内部用 0 或 1 编码表示的数被称为 机器数 ,变量真正的值被称为 真值 。

3. 异常( Exception ) 由处理器内部异常事件引起的意外事件。如除数为

0,溢出、断点、单步跟踪、寻址错、访问超时、

非法操作码、堆栈溢出、缺页、地址越界、数据格式错等。 4. 旁路( Bypassing )

是一种处理数据冒险的措施,也称“转发”技术。通过将前面指令执行的结果从某个流水线段寄存 器直接引到后面指令的执行部件来消除数据冒险。

10

10×2

5. 已知 SN74181 和 SN74182 芯片分别是 4 位 ALU 部件和 4 位 BCLA 部件,用它们构成 64 位快速

ALU 时,分别需要几片 SN74181 和几片 SN74182 芯片?( D )

A. 8, 2 B.

8, 3 C.

16, 4 D.

16, 5

6. 在不考虑异常和中断的情况下,以下给出的

2009 年 6 月 计算机组织与系统结构 期终考试试卷

考试科目名称 计算机组织与系统结构 (A 卷)

2008——2009 学年第

2 学期

系(专业)

计算机科学与技术

学号

姓名

教师 袁春风 /窦万春 年级 2007 成绩

考试方式:闭卷 班级

题号

一

二

三

四

五

六

分数

得分

大学计算机基础试卷及答案2009~2010-1(A)

河南理工大学 2009~2010 学年第 1 学期《大学计算机基础》试卷(A卷)考试方式:闭卷本试卷考试分数占学生总评成绩的70 %注意:所有答案均写在答题纸上,写在试卷上的不得分。

.........................一、单项选择题(本题共50个小题,每题1分,共50分)1. 一个完整的计算机系统由组成。

A) 运算器、控制器、存储器、输入设备和输出设备B) 主机和外部设备C) 硬件系统和软件系统D) 主机箱、显示器、键盘、鼠标、打印机2. 以下软件中,是系统软件A) Word B) UnixC) Excel D) Microsoft Office3.计算机能直接识别的语言是。

A) 汇编语言 B) 自然语言C) 机器语言 D) 高级语言4. 任何程序都必须加载到中才能被CPU执行。

A) 磁盘 B) 硬盘 C)内存 D) 外存5. 下列四个不同进制的数中,最小的一个是。

A) 10001100B B) 150 C) (202)8 D) A0H6. 操作系统的作用是。

A) 把源程序翻译成目标程序B) 实现软件硬件的转换C) 管理计算机的硬件设备D) 控制和管理系统资源的使用7. Windows XP操作系统是。

A) 多用户多任务操作系统 B) 多用户单任务操作系统C) 单用户多任务操作系统 D) 单用户单任务操作系统8. 微机在工作中,由于某种原因突然“死机”,重新启动后则计算机将全部消失。

A) ROM 和 RAM 中的信息 B) ROM中的信息C) 硬盘中的信息 D) RAM中的信息9. 在Windows XP中,要改变屏幕保护程序的设置,应首先双击控制面板窗口中的。

A) “多媒体”图标B) “显示”图标C) “键盘”图标 D) “系统”图标10. 一个带有通配符的文件名F*.?可以代表的文件。

A) B) FABC.TXT C) FA.C D) FF.EXE11. Windows的文件夹组织是一种。

2009年计算机结构与逻辑设计期末考试

2009年计算机结构与逻辑设计期末考试(A 卷)学号_________________姓名__________________成绩___________________一 填空题(20分)1、将二进制数 10001.101 化成十进制数 ________________________________;2、将十进制数 24.6 化成二进制数(误差ε<2-6 )____ __________________;3、写出二进制原码10101001 对应的补码 _______________________________;4、将十进制数 128 表示为2421BCD 码___________________________;5、写出等式 B A B A A +=+ 的对偶等式_______________________________;6、求逻辑函数D C B A F +∙= 的反函数F _______________________________;7、一个某计算机指令字长16位,能完成32条不同的指令,那么该指令字中,操作码长度需要_____________位;可以访问______________byte 的存储空间。

8、逻辑与、或、非和集合论的交、并、补相对应,例如在图1a 所示 的集合图中A 、B 的公共阴影部分便对应着 A 与B : A ×B ,试在图1b 中标出A ⊙B 对应的图形。

(4分)图1a 图1b二 作出逻辑函数C B A BD B A D B A F +++⋅⋅=的卡诺图,将逻辑表达式化成最简与或表达式, 并用与非门实现之。

(10分)A B A B三 设有两个二进制数12x x X =和12y y Y =,若X > Y ,则F=1,否则F=0;图为PAL16L8的一部分电路,试用PAL16L8实现此功能。

(15分)六用D触发器设计一个序列信号发生器,要求所产生的周期性序列为:110010,要求写出设计过程,逻辑表达式,状态图,电路图。

计算机组成结构+期末试题+答案

全国考研专业课高分资料常州工学院《计算机组成与结构》期末题笔记:目标院校目标专业本科生笔记或者辅导班笔记讲 义:目标院校目标专业本科教学课件期末题:目标院校目标专业本科期末测试题2-3套模拟题:目标院校目标专业考研专业课模拟测试题2套复习题:目标院校目标专业考研专业课导师复习题真 题:目标院校目标专业历年考试真题,本项为赠送项,未公布的不送!第四模块 期末试题常州工学院2011-2012学年第1学期期末考试计算机组成与结构考试试题(A) 所有答案必须做在答案题纸上,做在试题纸上无效!一、 基本题(共50分)1、现代计算机系统如何进行多级划分?这种分级观点对计算机设计会产生什么影响?(10分)2、已知x和y,用变形补码计算x+y,同时指出结果是否溢出。

(16分)(1) x=+0.1101 y=+0.1001 (2) x=-0.1100 y=-0.10003、比较通道、DMA、中断三种基本I/O方式的异同点。

(10分)4、微程序控制器组成原理框图如下,简述各部件的功能及微程序控制器对指令的译码过程。

(14分)二、计算题(共25分)1. 设有浮点数x=2-5×0.0110011,y=23×(-0.1110010),阶码用4位补码表示,尾数(含符号位)用8位补码表示。

求[x×y]浮。

要求用补码完成尾数乘法运算,运算结果尾数保留高8位(含符号位),并用尾数低位字长的值处理舍入操作。

(15分)2. 设有一个具有20位地址和32位字长的存储器,问:(共10分)(1)该存储器能存储多少字节的信息? (4分)(2)如果存储芯片由512K×8位SRAM芯片组成,需要多少片?(4分)(3)需要多少位的地址作芯片选择?(2分)三、分析与设计题(共25分)1、设计题。

(10分)设某机器字长为32位,CPU有16个32位通用寄存器,设计一个能容纳64种操作的指令系统。

如果采用通用寄存器作为基址寄存器,则RS型指令的最大寻找空间是多大?2. 分析题。

《计算机组装与维护》期末试题与参考答案

《计算机组装与维护》期末试题与参考答案;.线姓_ _ _ _ _ _《计算机组装与维护》期末考试试卷2009 — 2010 学年度第一学期适用对象:考试时间: 90 分钟__ _ _ _ _ _ _ _ _ _ :名一、填空题(共 20 个空格每空 1 分共 20 分)1. 自年,在美国宾夕法尼亚大学成功研制出世界第一台电子数字计算机,并命名为:“”。

2. 人们通常把第五代计算机称为人工智能计算机。

3. 光驱包括只读光驱( CD-RO )M 、可擦写光驱( CD-R/W )、DVD 只读光驱和 DVD 可擦写光驱_等。

_ 4.CPU 按位数可分为 8 位 CPU 、16 位 CPU 、32 位 CPU 、64 位 CPU 等。

_ _ 5.CPU 按主频可分为 2.0GHz 、2.42.0GHz 、2.62.0GHz 、3.02.0GHz 。

_ _ 6.目前市场上的 CPU 多为 Intel 公司、 AMD 公司所生产。

_ 7.CPU 在单位时间内一次处理的二进制数的位数称为“字长”。

_ : 8.CPU 的频率是指计算机运行时的工作频率,也称为“主频”或“时钟频率” 。

号 9.CPU 的频率越高,在一个时钟周期内所完成的指令数也就越多,CPU 的运算速度也就越快。

学10. 通常所说的“奔腾4 3.0 ”中的“ 3.0 ”实际上就是指该 CPU 的工作频率是 3.0GHz ,即封3000MH 。

z11. 控制器和运算器集成在一起,合称为(中央处理器)。

12.主频 =(外频)×(倍频系数)。

主板按照结构可分为( AT 结构)和( ATX 结构)的主板。

密_可以往(RAM )中写入临时数据,但这些数据在系统断电后会全部丢失。

_ 按照显卡所使用主板的扩展槽可以把显卡分为(ISA )显卡、( PCI )显卡、( AGP )显卡。

_ _ _ 根据打印机的工作原理,目前市场上的打印机可以分为三类:(针式打印机)、(激光打印机)、(喷墨打_ _ 印机)。

0Uecoka2009-2010计算机基础考试试卷(附答案)

秋风清,秋月明,落叶聚还散,寒鸦栖复惊。

2009-2010计算机基础考试试卷(附答案)业(本科)学生使用1、在ENIAC诞生后的短短的50多年中,计算机所采用的基本电子元件已经经历了四个发展阶段,通常称为计算机发展的4个时代,按发展先后依次为 B 。

A、晶体管、电子管、中小规模集成电路、大规模和超大规模集成电路。

B、电子管、晶体管、中小规模集成电路、大规模和超大规模集成电路。

C、中小规模集成电路、电子管、晶体管、大规模和超大规模集成电路。

D、大规模和超大规模集成电路、电子管、晶体管、中小规模集成电路。

2、冯·诺依曼“程序存储”的设想首次在 C计算机上得到了体现。

A、ENIACB、PCC、EDVACD、大型3、爱德华·罗伯茨1971年发明了第一台微机 C 。

A、Apple ⅡB、IBM PC/PCC、牛郎星D、织女星4、指令的数量与类型是由 A 决定的。

A、CPUB、DRAMC、SRAMD、BIOS5、主板性能的高低主要由 C 芯片决定。

A、CPUB、南桥C、北桥D、内存6、微机硬件的主要技术指标有:性能、功能、B 、兼容性等技术参数。

A、安全性B、可靠性C、实用性D、经济性7、配置在计算机硬件上的第一层软件是 B 。

A、语言处理程序B、操作系统C、工具软件D、数据库管理系统8、在Windows XP中复制当前屏幕图像到剪贴板的键名为 B 。

A、Alt+SpaceB、PrintScreen(Prtsc)C、Alt+ PrintScreen(Prtsc)D、F19、Windows XP任务栏不能完成的工作是D 。

A、显示改变系统日期和时间B、启动应用程序C、多个程序和任务之间的切换D、桌面上图标的排列10、大写字母锁定键的标志是 A 。

A、Caps LockB、Num LockC、Scroll LockD、Pause11、回收站是在 D 中开辟的一块存放已删除文件或文件夹的空间。

2009-2010学年第二学期计算机组装期末试卷

龙港二职《计算机组装与维护》期末试卷班级_________________姓名_________________成绩_________________ 一.单项选择题(每题2分,共40分)1.第三代计算机的主要逻辑元件为:()A.晶体管B.大规模和超大规模集成电路C.电子管D.集成电路2.微型计算机系统由__________和__________两大部分组成。

A.硬件系统、软件系统B.显示器、机箱C.输入设备、输出设备D.CPU、电源3.以下不是购买计算机要遵循的原则是A.合理的配置B.实用的功能C.最新的配件D.最少的开支4.目前市场上,CPU的制作工艺不包括A. 20nm B. 45nmC.65nm D. 90nm5.适用于LGA775平台CPU也适用于以下哪种平台?A. LGA1366 B. Socket AMC.Socket AM+ D. 上述均不适用6.一台笔记本电脑的磁盘转速一般为A. 5400转/分 B. 7200转/分C. 10000转 /分 D. 12000转 /分7.以下内存的主频不属于第二代内存DDR2的是A.400MHz B. 533MHzC.667MHz D. 800MHz8.计算机硬盘在厂商描述时有120G,而换算成系统计算时,实际上有A.120G B. 114GC.124G D. 100G9.下列不属于SATA接口硬盘的特点是A.支持热插拔B. 布线简单,有利于散热C.不受主盘和从盘的设置限制D. 接口的传输速度为150Kbit/s。

10.以下光盘是不可以将计算机信息写入的是A.CD-ROM B. DVD-RWC.CD-RW D. DVD-R11.下列投影仪的灯泡,哪种使用的寿命相对来说要长A.金属卤素灯泡 B. UHE灯泡C.UHP高能灯泡 D. 灯泡寿命一样长12.以下哪种网卡可以支持接收数据的同时又能传送数据A.有线网卡 B. 无线网卡C.半双工网卡 D. 全双工网卡13.以下软件是一款专业的性能测试软件A.office B. WPSC.金山快译 D. Everest Ultimate Edition14.以下哪个是CPU正常工作的温度A、10℃~35℃B、20℃~30℃C、70℃~ 80℃D、50℃以下15.下列哪种输出接口的显卡只能传输模拟信号A、VGAB、DVIC、HDMID、以上选项均不对。

计算机组成与结构习题及答案

第一章:概述一、选择题1.完整的计算机系统应包括__ ___。

A. 运算器、存储器、控制器B. 外部设备和主机C. 主机和实用程序D. 配套的硬件设备和软件系统2.至今为止,计算机中的所有信息仍以二进制方式表示的理由是_ __。

A. 节约元件B. 运算速度快C. 物理器件的性能决定D. 信息处理方便3.从系统结构看,至今绝大多数计算机仍属于__ __型计算机。

A. 并行B. 冯.诺依曼C. 智能D. 实时处理4.计算机外围设备是指__ ___A. 输入/输出设备B. 外存储器C. 远程通讯设备D. 除CPU5.在微型机系统中,外围设备通过___ ___与主板的系统总线相连接。

A. 适配器B. 译码器C. 计数器D.6.冯·诺依曼机工作的基本方式的特点是__ ____。

A. 多指令流单数据流B. 按地址访问并顺序执行指令C. 堆栈操作D. 存贮器按内容选择地址7.微型计算机的发展一般是以_____A. 操作系统B.C. 磁盘D.8.下列选项中,___ ___A. CPUB. ASCIIC. 内存D.9.对计算机的软、硬件进行管理是__ ____A. 操作系统B. 数据库管理系统C. 语言处理程序D.10.下面的四个叙述中,只有一个是正确的,它是____。

A.系统软件就是买的软件,应用软件就是自己编写的软件B.外存上的信息可以直接进入CPU被处理C.用机器语言编写的程序可以由计算机直接执行,用高级语言编写的程序必须经过编译(解释)才能执行D.如果说一台计算机配置了FORTRAN语言,就是说它一开机就可以用FORTRAN 语言编写和执行程序答案:1.D 2C. 3.B. 4.D. 5.A. 6B 7.B 8. B 9. A 10. C二、判断题1.在微型计算机广阔的应用领域中,会计电算化应属于科学计算应用方面。

2.决定计算机计算精度的主要技术指标一般是指计算机的字长。

3.计算机“运算速度”指标的含义是指每秒钟能执行多少条操作系统的命令。

计算机系统结构试题及答案

2009-2010学年度第一学期2007级《计算机系统结构》期末考试试卷(A)(闭卷)姓名:学号:专业:(注:①考试时间为120分钟;②所有解答必须写在答题纸上.)一、单项选择题(每小题3分,共30分)1.在系列机中发展一种新型号机器,你认为下列()设想是不行的?【A】新增加字符数据类型和若干条字符处理指令【B】将中断分级由原来的4级增加到5级【C】在CPU和主存之间增设Cache存贮器【D】将浮点数的下溢处理法由原来的恒置“1"法,改为查表舍入法2.对计算机系统结构来说,不透明的是( )。

【A】存储器采用交叉存取还是并行存取【B】CPU内部的数据通路的宽度是8位还是16位【C】采用浮点数据表示还是标志符数据表示【D】指令采用硬联逻辑实现还是微程序实现3.一个平衡的计算机系统,应该是( )。

【A】1MIPS的CPU速度【B】1MB的主存容量【C】1Mb/s的I/O吞吐率【D】A、B和C4、()设计是现代计算机系统设计所采用的方法.【A】由上往下【B】由下往上【C】由中间开始【D】上下同时开始5.当今微型机中实现软件移植最好的方法是().【A】系列机【B】兼容机【C】仿真技术【D】统一高级语言6、不能够对向量数据结构提供直接支持的是()数据表示.【A】向量【B】堆栈【C】描述符【D】A和C7、采用整数边界存储技术,其主要目的是()。

【A】节约主存空间【B】提高数据的访问速度【C】一个主存周期可取多条指令【D】一个主存周期至少可取到一条指令8、在指令的操作码编码方式中,优化实用的编码是( )。

【A】Huffman编码【B】等长编码【C】Huffman扩展编码【D】BCD码9、流水计算机中将指令Cache和数据Cache分开,主要是为了( ).【A】提高存储系统的速度【B】增加主存容量【C】解决功能部件冲突【D】解决访存冲突10、当N=16时,能描述4组4元交换的函数是( )。

【A】C1+C2 【B】C0+C1 【C】C0+C2 【D】C2+C3二、(10分)在采用通用寄存器指令集结构的计算机上得到了如下所示的数据:假若编译器优化后能去掉50%的ALU指令,但不能去掉其它三类指令。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

C.控制器D.输入输出设备

2.CPU中,跟踪下一条要执行的指令的地址的寄存器是

A. PC B. MAR C. MDR D. IR

3.假定有4个整数用8位补码分别表示r1=FEH,r2=F2H,r3=90H,r4=F8H,若将运算结果放在一个8位寄存器中,则下列运算会发生溢出的是______。

6.(9分)某计算机指令格式下图所示。

其中I位为寻址特征位,其意义如下:

当I=0时,不变址;

X=1时,用变址寄存器X1进行变址

X=2时,用变址寄存器X2ห้องสมุดไป่ตู้行变址

X=3时,相对寻址。

设PC=1000H,X1=0052H,X2=1122H,确定下列指令的有效地址:

(1)8210H(2)1322H(3)A084H

A . r1*r2 B . r2*r3 C.r1*r4 D. r2*r4

4.计算机的外围设备是指______。

A.显示器、键盘、鼠标B .外存储器

C .远程通信设备D.除了CPU和内存以外的其它设备

5.设在网络中传送采用偶校验的ASCII码,当收到的数据位为10101001时,可以断定()

A.未出错B.出现偶数位错C.出现奇数位错D.未出错或者出现偶数位错

A. 10t B.7t C .12t D. 6t

16.下列选项中英文缩写都是总线标准的为()

A. PCI、CRT、USB、EISA B. ISA、CPI、VESA、EISA

C. ISA、SCSI、RAM、MIPS D. ISA、EISA、PCI、VESA

17.下列选项中哪项属于分布式仲裁()

A.菊花链方式B.计数器定时方式C .独立请求方式D .以上都不是

A. 1000 B. 1002 C. 1008 D. 1004

13.若某指令采用寄存器相对寻址,则()。

A.操作数在内存中B.操作数在寄存器中

C.操作数就在指令中D.无法确定操作数在哪里

14.在微程序控制中,控制部件向执行部件发出的某个控制信号称为()

A.微指令B.微命令C.微程序D.操作码

15.设CPU采用三级指令、双发射的超标量流水线,操作周期为t,则CPU连续运行10条指令所需要的时间为(),假设这些指令完全适合于流水线上的执行。

4.(8分)假设CPU执行某段程序时,950次从cache得到数据,50次从主存得到数据,已知cache存取周期为50ns,主存存取周期为200ns(假设每次访问时同时访问cache和主存,如果cache命中则中断主存访问),求:

(1)cache命中率;

(2)平均访问时间;

(3)cache—主存系统效率。

2009 - 2010学年第2学期

《计算机组成与结构》试题(A卷)

课程代码BB002014考试方式闭卷考试时长100分钟

姓名学号教学班号专业级班

题号

一

二

合计

满分

40

60

100

得分

阅卷人

注意:所有试题答案一律写在答题纸上,否则不得分。

一、选择题(本大题共40分,每小题2分)

1.下列不属于冯.诺依曼提出的计算机五大部件的是()

A.字节B.数据块C.字D.比特

二、综合应用题(共60分,第一题5分,第二题8分,第三题8分,第四题8分,第五题10分,第六题9分,第七大题12分)

1.(5分)请画出中断执行过程图,并设系统允许多级中断。

2.(8分)请写出(3.8125)10在IEEE 754标准的短实数形式下的机器数

3.(8分)一个128*128的DRAM芯片,每个2ms需要刷新一次,且刷新是按顺序对所有的128行的存储元进行内部读写操作完成的,设存储周期为0.5us,求分布式刷新的刷新间隔,并求刷新开销(进行刷新操作的时间所占百分比)。

A. RAM B. ROM C. cache D. cache、主存和外存

9.下列有关RAM和ROM的叙述中,正确的是()

I RAM是易失性存储器,ROM是非易失性存储器

II RAM和ROM都采用随机存取方式进行信息访问

III RAM和ROM都可以用作cache

IV RAM和ROM都需要进行刷新

A. I和II B. II和III C. I,II,III D.全部

6.两个浮点数进行加减运算,在尾数加减过程中如果出现溢出则需要()。

A .中断处理B .左规C.右规D .舍入

7.设机器数采用补码形式,若加法运算时,加数和被加数的最高两位不相同,则可以断定()。

A.运算结果一定为负

B.运算结果一定为正

C.运算结果一定不会溢出

D.运算结果一定溢出

8.计算机的存储系统指()

表7-1

5.(9分)某计算机CPU的主频为500MHz,CPI=5。假定某外设的数据传输率为0.5MB/s,采用中断方式与主机进行数据传送,以32位为传输单位,对应的中断服务程序包含18条指令,中断服务的其他开销相当于2条指令的执行时间。请回答下列问题(1)中断方式下,CPU用于该外设I/O的时间占整个CPU时间的百分比是多少?(2)当该外设的数据传输率达到5MB/s是,改用DMA方式传输数据。假定每次DMA传送块大小为5000B,且DMA预处理和后处理的总开销为500个时钟周期,则CPU用于该外设的I/O的时间占整个CPU时间的百分比是多少?

18.在独立编址方式下,访问主存储器和访问I/O设备是通过()来区分的

A.不同的地址码B.不同地址线C.不同的指令D.以上都不对

19.下列不属于DMA传送方式的是()

A. CPU周期挪用B.停止CPU访问

C.分时传送D. CPU和DMA交替访存

20.选择通道上可以连接若干设备,其数据传送是以()为单位进行的

7.(13分)某计算机的数据通路如图所示,设机器字长16位,采用16位定长指令字结构,图中带*为控制信号,所有控制信号为1时表示有效,为0时表示无效。

其中指令“ADD(R1),R0”代表将R1寄存器中指向的内存单元的内容与R0寄存器的内容相加,结果送向R1寄存器中指向的内存单元。同时表7-1中给出了取指令和译码阶段每个节拍的功能和有效控制信号,请按照表7-1中给出的信号形式,写出指令执行阶段每个节拍的功能和控制信号。

10.下已知单个存储体的存取周期为T,CPU连续从四体高位交叉存储器中取出N个字需要时间为()

A. 4T B.(N-1)T C. NT D.无法确定

11. cache和主存交换信息的单位是()。

A.字节B.机器字C.字块D.视cache情况而定

12.某机器字长32位,存储器按字节编址,当前PC值为1000,当取出着这条指令后,PC的值为()