芯片封装原理及分类.

芯片封装原理及分类

Ceramic substrate (Typically Alumina)

Solder Balls (typically 90Pb/10Sn) Metal Cap Adhesive

Caped

PQFP封装模型的建立

• Plastic Quad Flat Pack (thin version called TQFP) • 常用于逻辑芯片, ASIC芯 片, 显示芯片等 • 封装外管脚(Lead), 表面 贴装

PROFIT 项目 PRediction OF temperature gradients Influencing The quality of electronic products DELPHI项目 DEvelopment of Libraries of PHysical models for an Integrated design environment

Thermal grease

SOP/TSOP封装模型的建立

• Small Outline Package • Low profile version known as Thin Small Outline Package (TSOP) • 类似于 PQFP, 只是只有两边有管脚 • 广泛应用于内存芯片 • 常见的类型 - 常规 - Lead-on-Chip

qjx 使用的局限性

Convection/Radiation Conduction Con/Radiation

X

θjx

Junction

Conduction

• qjx 试图采用简单的热阻表示复杂的芯片传热现象 • 芯片内部的热传现象非常复杂,无法使用热阻来完美表示; • 热阻qjx 无法用于准确预测芯片的温度,只能提供定性的热性 能对比; • 如需准确预测特定工况下芯片的温度,我们需要其它的方法

chip原理及实验步骤

chip原理及实验步骤芯片(chip)是电子技术中常用的一个概念,它是指集成电路的一种封装形式。

芯片原理就是将多个电子器件、电路和元件集成到一块硅片上,并通过微影技术将电路图案化,最终形成一个完整的电子系统。

下面将介绍芯片的原理及实验步骤。

一、芯片原理芯片的原理主要包括以下几个方面:1.1、集成电路技术:芯片采用集成电路技术,将多个电子器件和电路集成到一块硅片上,通过微影技术将电路图案化,形成一个完整的电子系统。

1.2、微电子工艺:芯片的制造过程中采用微电子工艺,包括光刻、蒸镀、离子注入、扩散等步骤,通过这些工艺将电路图案化并形成电子器件。

1.3、材料选择:芯片的制造需要选择合适的材料,如硅片、金属、绝缘材料等,这些材料的性能和特点会直接影响芯片的性能和稳定性。

1.4、电路设计:芯片的设计是芯片原理的关键,通过合理的电路设计可以实现不同的功能和应用,如处理器芯片、存储芯片、传感器芯片等。

二、芯片实验步骤芯片的实验步骤主要包括芯片制造、芯片测试和芯片封装等过程。

2.1、芯片制造芯片的制造是芯片实验的第一步,主要包括以下几个步骤:(1)芯片设计:根据实验需求和功能要求,进行芯片电路设计,确定芯片的布局和电路结构。

(2)芯片加工:根据电路设计,采用微电子工艺将电路图案化,形成电子器件,包括光刻、蒸镀、离子注入等制造步骤。

(3)芯片测试:对制造好的芯片进行测试,检测芯片的性能和功能是否符合设计要求。

2.2、芯片测试芯片测试是为了验证芯片的性能和功能是否符合设计要求,主要包括以下几个步骤:(1)功能测试:对芯片进行功能测试,验证芯片是否能够正常工作和完成设计的功能。

(2)性能测试:对芯片进行性能测试,包括速度、功耗、温度等方面的测试,验证芯片的性能是否满足要求。

(3)可靠性测试:对芯片进行可靠性测试,包括老化测试、温度循环测试等,验证芯片的可靠性和稳定性。

2.3、芯片封装芯片封装是将制造好的芯片封装到外部封装材料中,以保护芯片并方便连接外部电路。

芯片封装原理及分类

芯片封装原理及分类1.芯片封装原理芯片封装是指将微电子器件(包括集成电路、晶体管等)连接到封装基座上的工艺过程。

其原理是将芯片导线通过焊接或焊球连接到封装基座上的金属脚,然后采用封装材料将芯片进行封装。

这样可以保护芯片免受外界环境的影响,并且提供了芯片与外部世界之间的连接接口。

2.芯片封装分类(1)DIP封装(Dual In-line Package)DIP封装是最早的一种芯片封装方式,其特点是通过两排金属脚与外部电路连接。

这种封装方式成本低、可焊接,但体积大,适用于较低密度的集成电路。

(2)SOP封装(Small Outline Package)SOP封装是DIP封装的改进版,其特点是脚距更近,体积更小,适用于较高密度的集成电路。

SOP封装有多种形式,如SOIC(Small Outline Integrated Circuit)、TSOP(Thin Small Outline Package)等。

(3)QFP封装(Quad Flat Package)QFP封装是一种表面贴装封装方式,其特点是四个侧面都带有金属端子,适用于较高密度、中等规模的集成电路。

QFP封装有多种形式,如TQFP(Thin Quad Flat Package)、LQFP(Low-profile Quad Flat Package)等。

(4)BGA封装(Ball Grid Array)BGA封装是一种表面贴装封装方式,在封装基座上布置了一定数量的焊球来实现与外部电路的连接。

BGA封装的特点是密封性好、性能稳定,并且适用于超高密度的集成电路。

BGA封装有多种形式,如CABGA (Ceramic Ball Grid Array)、TBGA(Thin Ball Grid Array)等。

(5)CSP封装(Chip Scale Package)CSP封装是一种紧凑型封装方式,其特点是尺寸和芯片相似,在封装基座上布置了少量焊球或焊盘。

CSP封装的优势在于占据空间小、重量轻、功耗低,并且适用于高密度的集成电路。

芯片封装介绍范文

芯片封装介绍范文芯片封装是一种将芯片器件封装在外部包装中的技术过程。

它起到保护芯片免受外界环境影响的作用,同时也为芯片与外部世界进行连接提供了可能。

芯片封装可分为多种形式,如塑封、球栅阵列封装(BGA)、无引线封装(QFN)等。

早期的芯片封装主要采用塑封封装。

塑封封装通过将芯片与塑料基片进行固定连接,然后使用塑料材料进行封装。

塑封封装方式简单、成本较低,适用于低功耗芯片,如逻辑芯片和存储器芯片。

然而,随着集成度的不断提高和功耗的增加,塑封封装的局限性也逐渐暴露出来,如散热不佳、引脚容易受损等。

为解决塑封封装的问题,球栅阵列封装(BGA)应运而生。

BGA封装采用无引线设计,通过在底部安装一个由球形焊球组成的阵列,与印刷电路板焊接在一起。

相较于塑封封装,BGA封装具有更好的热性能和导热性能,能够更好地满足高密度与高功率芯片的需求。

此外,BGA封装的焊点可靠性也较高,能够适应复杂环境和振动应力。

因此,BGA封装逐渐成为高性能芯片封装的主流技术。

除了BGA封装之外,无引线封装(QFN)也是一种常见的芯片封装形式。

与BGA封装类似,QFN封装也采用无引线设计,通过焊接芯片与印刷电路板的底部金属接触面相连接。

与BGA封装相比,QFN封装在尺寸上更加紧凑,适用于小型化和轻量化的应用,如移动设备和无线通信模块。

此外,QFN封装还具有低成本、良好的导热性能和可靠性等优势。

除了上述封装形式,另外还有多种芯片封装技术,如多芯片模块(MCM)、3D封装等。

多芯片模块将多个芯片集成在一个封装中,以实现更高的功能集成和性能。

3D封装则是将多个芯片堆叠在一起,通过垂直连接实现信号传输和功耗管理。

这些封装形式在高端应用领域得到广泛应用,如服务器、网络设备和高性能计算机等。

总之,芯片封装是将芯片器件封装在外部包装中的技术过程,它为芯片提供了物理保护和外部连接的功能。

在不同类型的封装中,塑封封装适用于低功耗芯片,BGA和QFN封装适用于高性能芯片,而MCM和3D封装则适用于高度集成和功能复杂的芯片。

芯片封装流程及原理

芯片封装流程及原理下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!芯片封装是将芯片与外部环境隔离,并提供电气连接和机械保护的过程。

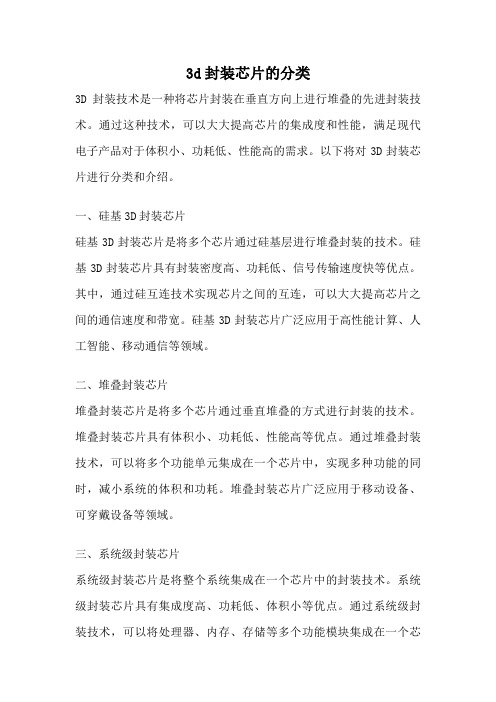

3d封装芯片的分类

3d封装芯片的分类3D封装技术是一种将芯片封装在垂直方向上进行堆叠的先进封装技术。

通过这种技术,可以大大提高芯片的集成度和性能,满足现代电子产品对于体积小、功耗低、性能高的需求。

以下将对3D封装芯片进行分类和介绍。

一、硅基3D封装芯片硅基3D封装芯片是将多个芯片通过硅基层进行堆叠封装的技术。

硅基3D封装芯片具有封装密度高、功耗低、信号传输速度快等优点。

其中,通过硅互连技术实现芯片之间的互连,可以大大提高芯片之间的通信速度和带宽。

硅基3D封装芯片广泛应用于高性能计算、人工智能、移动通信等领域。

二、堆叠封装芯片堆叠封装芯片是将多个芯片通过垂直堆叠的方式进行封装的技术。

堆叠封装芯片具有体积小、功耗低、性能高等优点。

通过堆叠封装技术,可以将多个功能单元集成在一个芯片中,实现多种功能的同时,减小系统的体积和功耗。

堆叠封装芯片广泛应用于移动设备、可穿戴设备等领域。

三、系统级封装芯片系统级封装芯片是将整个系统集成在一个芯片中的封装技术。

系统级封装芯片具有集成度高、功耗低、体积小等优点。

通过系统级封装技术,可以将处理器、内存、存储等多个功能模块集成在一个芯片中,实现系统级集成,提高系统的整体性能和功耗效率。

系统级封装芯片广泛应用于智能手机、平板电脑、电视等消费电子产品。

四、无线通信封装芯片无线通信封装芯片是将无线通信模块集成在一个芯片中的封装技术。

无线通信封装芯片具有体积小、功耗低、传输速率高等优点。

通过无线通信封装技术,可以将射频芯片、基带芯片等功能模块集成在一个芯片中,实现无线通信的高速稳定传输。

无线通信封装芯片广泛应用于移动通信、物联网等领域。

五、MEMS封装芯片MEMS封装芯片是将微机电系统(MEMS)器件集成在一个芯片中的封装技术。

MEMS封装芯片具有体积小、功耗低、响应速度快等优点。

通过MEMS封装技术,可以将传感器、执行器等功能模块集成在一个芯片中,实现多种传感和执行功能。

MEMS封装芯片广泛应用于汽车电子、医疗设备、智能家居等领域。

集成电路芯片封装技术第1章

(50~90)%

封装效率

封装效率

=2-7%(1970-) =10-30%(1980-)

封装效率

=20-80%(1990-)

封装效率

=50-90%(1993-)

封装效率的改进

35

表2.封装厚度的变化

封装形式

封装厚度

(mm)

PQFP/PDIP TQFP/TSOP UTQFP/UTSOP

解决途径:

1、降低芯片功耗:双极型-PMOS-CMOS-???

2、增加材料的热导率:成本

微电子技术发展对封装的要求

三、集成度提高 适应大芯片要求

热膨胀系数(CTE)失配—热应力和热变形

解决途径:

1、采用低应力贴片材料:使大尺寸IC采用CTE接近

Si的陶瓷材料,但目前环氧树脂封装仍为主流

2、采用应力低传递模压树脂 消除封装过程中的热应

目的

使各种元器件、功能部件相组合形成功能电路

难易程度

依据电路结构、性能要求、封装类型而异

需考虑的问题

ห้องสมุดไป่ตู้保护

苛刻的工程条件(温度、湿度、振动、冲击、放射性等)

超高要求

超高性能 (3D IC)

超薄型、超小型

超多端子连接

超高功率(采用热冷、金属陶瓷复合基板等)

电子封装实现的四种功能

① 信号分配:

② 电源分配:

何将聚集的热量散出的问

题

封装保护

芯片封装可为芯片和其他连

接部件提供牢固可靠的机械

支撑,并能适应各种工作环

境和条件的变化

确定封装要求的影响因素

成本

电路在最佳

性能指标下

的最低价格

外形与结构

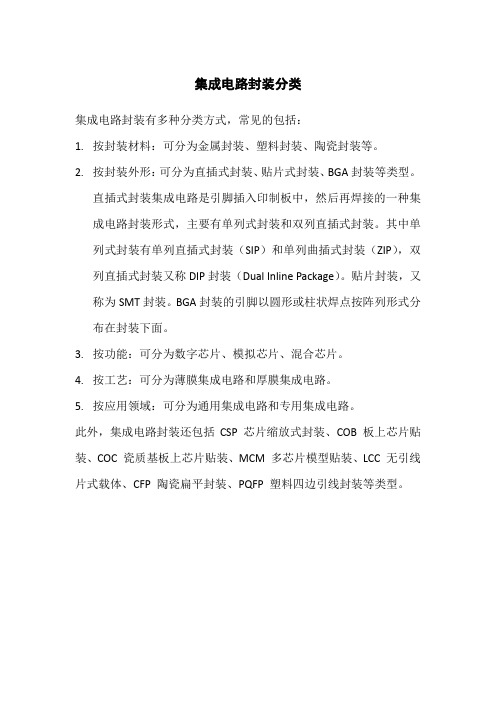

集成电路封装分类

集成电路封装分类

集成电路封装有多种分类方式,常见的包括:

1.按封装材料:可分为金属封装、塑料封装、陶瓷封装等。

2.按封装外形:可分为直插式封装、贴片式封装、BGA封装等类型。

直插式封装集成电路是引脚插入印制板中,然后再焊接的一种集成电路封装形式,主要有单列式封装和双列直插式封装。

其中单列式封装有单列直插式封装(SIP)和单列曲插式封装(ZIP),双列直插式封装又称DIP封装(Dual Inline Package)。

贴片封装,又称为SMT封装。

BGA封装的引脚以圆形或柱状焊点按阵列形式分布在封装下面。

3.按功能:可分为数字芯片、模拟芯片、混合芯片。

4.按工艺:可分为薄膜集成电路和厚膜集成电路。

5.按应用领域:可分为通用集成电路和专用集成电路。

此外,集成电路封装还包括CSP 芯片缩放式封装、COB 板上芯片贴装、COC 瓷质基板上芯片贴装、MCM 多芯片模型贴装、LCC 无引线片式载体、CFP 陶瓷扁平封装、PQFP 塑料四边引线封装等类型。

芯片封装分类

芯⽚封装分类芯⽚封装分类⼤全【1】双列直插封装(DIP)20世纪60年代,由于IC集成度的提⾼,电路引脚数不断增加,有了数⼗个I/O引脚的中、⼩规模集成电路(MSI、SSI),相应的封装形式为双列直插(DIP)型,并成为那个时期的主导产品形式。

70年代,芯⽚封装流⾏的是双列直插封装(DIP)、单列直插封装(SIP)、针栅阵列封装(PGA)等都属于通孔插装式安装器件。

通孔插装式安装器件的代表当属双列直插封装,简称DIP(Dualln-LinePackage)。

这类DIP从封装结构形式上可以分为两种:其⼀,军品或要求⽓密封装的采⽤陶瓷双例直插DIP;其⼆,由于塑料封装具有低成本、性价⽐优越等特点,因此,封装形式⼤多数采⽤塑料直插式PDIP。

塑料双便直插封装(PDIP)是上世纪80年代普遍使⽤的封装形式,它有⼀个矩形的塑封体,在矩形塑封体⽐较长的两侧⾯有双列管脚,两相邻管脚之间的节距是2.54mm,引线数为6-84,厚度约为2.0~3.6,如表2所⽰。

两边平等排列管脚的跨距较⼤,它的直插式管脚结构使塑封电路可以装在塑料管内运输,不⽤接触管脚,管脚从塑封体两⾯弯曲⼀个⼩⾓度⽤于插孔式安装,也便于测试或器件的升级和更换。

这种封装形式,⽐较适合印制电路板(PCB)的穿孔安装,具有⽐50年代的TO型圆形⾦属封装,更易于对PCB布线以及操作较为⽅便等特点。

这种封装适合于⼤批量低成本⽣产,便于⾃动化的线路板安装及提供⾼的可靠性焊接。

同时,塑料封装器件在尺⼨、重量、性能、成本、可靠性及实⽤性⽅⾯也优于⽓密性封装。

⼤部分塑封器件重量⼤约只是陶瓷封装的⼀半。

例如:14脚双列直插封装(DIP)重量⼤约为1g,⽽14脚陶瓷封装重2g。

但是双列直插封装(DIP)效率较低,⼤约只有2%,并占去了⼤量有效安装⾯积。

我们知道,衡量⼀个芯⽚封装技术先进与否的重要指标是芯⽚⾯积与封装⾯积之⽐,这个⽐值越接近1越好。

【2】四边引线扁平封装(QFP)20世纪80年代,随着计算机、通讯设备、家⽤电器向便携式、⾼性能⽅向的发展;随着集成电路技术的进步,⼤规模集成电路(LSI)I/O引脚数已达数百个,与之相适应的,为了缩⼩PCB板的体积进⽽缩⼩各种系统及电器的体积,解决⾼密度封装技术及所需⾼密度引线框架的开发,满⾜电⼦整机⼩型化,要求集成电路封装在更⼩的单位⾯积⾥引出更多的器件引脚和信号,向轻、薄、短、⼩⽅向发展。

封装和解封装的过程

封装和解封装的过程随着电子技术的不断发展,半导体芯片的应用越来越广泛,从计算机、手机到家电、汽车等各个领域都有半导体芯片的身影。

而半导体芯片的生产过程中,封装和解封装是非常重要的环节。

一、封装的定义和作用封装是将芯片加工成完整的电子元器件的过程,它是把芯片放在特定的载体上,并加上导线、壳体等外部结构,使得芯片能够与外部环境交互,从而组成完整的电子器件。

封装的主要作用有以下几点:1. 保护芯片:芯片是半导体工艺的核心,它具有极高的灵敏度和易损性。

封装可以将芯片放在一个相对安全的环境中,避免芯片受到外部环境的损害,从而保护芯片的可靠性和稳定性。

2. 提高芯片的可靠性:封装可以消除芯片与外部环境之间的干扰,从而提高芯片的可靠性和稳定性。

此外,封装还可以加强芯片与外部环境之间的电气连接,增强芯片的抗干扰能力。

3. 方便芯片的使用:封装可以将芯片转化为一个完整的电子器件,方便芯片的安装、使用和维护。

此外,封装还可以使芯片的功能更加多样化,满足不同用户的需求。

二、封装的分类根据芯片的封装形式,封装可以分为裸片封装、塑封封装和金属封装等几种类型。

1. 裸片封装:裸片封装是指将芯片直接焊接在载体上,不加任何封装材料。

裸片封装具有体积小、重量轻、成本低等优点,但其环境适应性差,易受到外部环境的干扰,因此应用范围有限。

2. 塑封封装:塑封封装是将芯片放在一个塑料封装中,再通过热压、注塑等工艺将封装材料封装在芯片的表面。

塑封封装具有成本低、结构简单、环保等优点,是目前应用最广泛的封装形式之一。

3. 金属封装:金属封装是将芯片放在一个金属封装中,通过焊接、胶合等工艺将封装材料封装在芯片的表面。

金属封装具有抗干扰能力强、耐高温、抗腐蚀等优点,适用于高端电子产品的封装。

三、解封装的定义和作用解封装是指将封装后的芯片进行拆解,还原成原始的芯片结构。

解封装的主要作用有以下几点:1. 检测芯片质量:解封装可以检测芯片的质量,包括芯片的制造工艺、材料质量、电气性能等方面。

mip和cob封装工艺

MIP和COB封装工艺1. 简介MIP(Molded Interconnect Package)和COB(Chip-on-board)是两种常见的封装工艺,用于集成电路的封装和连接。

它们在电子产品制造中起到关键作用,能够提高产品的性能和可靠性。

本文将详细介绍MIP和COB封装工艺的原理、特点、应用以及制造过程。

2. MIP封装工艺2.1 原理MIP封装工艺是一种将集成电路芯片和封装基板结合在一起的封装技术。

其原理是通过将芯片和基板分别制造,然后将芯片嵌入基板中,最后通过热压等工艺将芯片与基板连接在一起。

MIP封装工艺可以实现高密度封装和多功能集成,具有良好的电气性能和可靠性。

2.2 特点•高集成度:MIP封装工艺可以实现芯片和基板的紧密结合,从而实现高集成度的电路设计。

•尺寸小:MIP封装工艺可以实现小型化设计,适用于微型电子产品的制造。

•低功耗:MIP封装工艺采用多层结构,可以减少电路的功耗。

•高可靠性:MIP封装工艺可以减少引脚数量和连接点,从而提高了电路的可靠性。

2.3 应用MIP封装工艺广泛应用于手机、平板电脑、智能穿戴设备等消费电子产品中。

由于其尺寸小、功耗低、可靠性高的特点,MIP封装工艺能够满足现代电子产品对于高性能和高可靠性的要求。

3. COB封装工艺3.1 原理COB封装工艺是一种将芯片直接粘贴在基板上的封装技术。

其原理是将芯片裸露的金属焊盘与基板上的金属焊盘通过焊接连接在一起,然后用环氧树脂等材料进行封装。

COB封装工艺可以实现高密度封装和高可靠性连接。

3.2 特点•高密度封装:COB封装工艺可以实现芯片与基板的直接连接,从而实现高密度封装。

•高可靠性:COB封装工艺采用焊接连接,可以提高电路的可靠性。

•良好的散热性能:COB封装工艺将芯片直接粘贴在基板上,可以提高散热性能,减少芯片温度。

3.3 应用COB封装工艺广泛应用于LED灯、汽车电子、医疗器械等领域。

由于其高密度封装、高可靠性和良好的散热性能,COB封装工艺能够满足这些领域对于高性能和高可靠性的要求。

芯片封装原理及分类

部分芯片建模时可将各边管脚统一建立; 管脚数较小应将各管脚单独建出. fused lead 一定要单独建出 Tie bars 一般可以忽略.

Bond Wires

Die

Die Flag

Leadframe

常规

Die

Bond Wires

主要类型的PBGA封装

Wire-Bonded PBGA (Die-up)

BT Dielectric

Thermal Vias

Solder Balls (37Pb/63Sn)

Epoxy-based Encapsulant

Silicon Die

Die Attach & Solder Mask

Gold Bond Wires

封装参数 (结构、材料参数)

根据各种封装特点离散出 各种热阻网络拓朴结构

详细 模型

发布

简化 模型

多种边界条件可以表 示自然对流、强迫对流、 散热器等多种环境

根据各热阻节点的温度值优 化得出具有最小误差的热阻值

DELPHI项目组定义了99种 边界条件;

Flopack应用了44种或88种

PBGA封装模型的建立

Case

qjb

qjb 结板热阻

qjb 从结点至印制板的热阻 定义标准由文件 JESD51-8给出

严格地讲,Theta-JB不仅仅反映了芯片的内热阻,同时也反映了部份环境热阻,如印制板。正因如些, Theta-JB相对于其它热阻而言,虽然JEDEC组织在99年就发布了它的热阻定义方式,但是芯片供应商采用较慢。 部份传热路径严重不对称芯片,如TO-263目前尚无该热阻的定义标准

DEvelopment of Libraries of PHysical models for an Integrated design environment

lga封装原理

lga封装原理

LGA(Land Grid Array)封装是一种将集成电路芯片与印制电路板(PCB)连接的封装技术。

其原理是通过将芯片上的引脚与PCB板上的焊盘相对应

连接,实现信号传输和电力供应。

这些焊盘位于芯片的底部,形成一个网格状的排列结构。

在制造过程中,首先在印制电路板上制造一系列的焊盘,这些焊盘通常由金属材料制成,例如锡、铅、铜等。

然后将集成电路芯片制造成薄片,其上的引脚通过金属线与芯片外部的焊盘相连接。

接着,将芯片放置在印制电路板上,使芯片上的引脚与印制电路板上的焊盘对应。

最后,通过一种中间介质(例如焊球或焊盘)将芯片上的引脚与印制电路板上的焊盘互连,这种互连方式可以通过热压、热膨胀或超声波焊接等技术实现。

LGA 封装具有较高的引脚密度和稳定性,适用于多种集成电路和应用场景。

相比其他封装技术,LGA封装具有许多优势,例如由于引脚分布在芯片的底部,不会受到表面贴装技术中回流焊接引起的热应力影响;可以实现更高的引脚密度,提供更多的I/O接口和功能;具有较高的可靠性和散热性能等。

因此,LGA封装广泛应用于各个领域的电子产品制造中,如消费电子、通信、汽车电子、医疗器械和航空航天等领域。

在进行LGA封装设计时,需要考虑一

些关键因素,如PCB布局要合理安排焊盘的位置和大小,以确保与芯片引

脚的良好对应;选择适当的焊接材料和工艺参数,以保证焊接的可靠性和稳定性;散热设计也是重要的考虑因素,要确保芯片的温度在可接受范围内等。

随着科技的不断进步,LGA封装技术也在不断演进,未来对于更高引脚密度、更小封装尺寸和更高频率的需求将推动LGA封装的发展。

芯片封装种类汇总

1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

芯片分类封装大全

IC封装分类大全——小贝收集整理2010.05三极管封装图LQFP BQFP PQFPSC-70SOJSSOPSOP TQFP常见集成电路(IC)芯片的封装SIP(Single In-line Package)单列直插式封装PGA(Pin Grid Array Package)插针网格阵列封装PLCC(Plastic leaded.QFPCSP(Chip Scale Package)芯片缩放式封装DIP,SIP,SOP,TO,SOT元件封裝形式(图)各元器件封装形式图解,不知道有没有人发过.暂且放上!CDIP-----Ceramic Dual In-Line PackageCLCC-----Ceramic Leaded Chip CarrierCQFP-----Ceramic Quad Flat PackDIP-----Dual In-Line PackageLQFP-----Low-Profile Quad Flat PackMAPBGA------Mold Array Process Ball Grid ArrayPBGA-----Plastic Ball Grid ArrayPLCC-----Plastic Leaded Chip CarrierPQFP-----Plastic Quad Flat PackQFP-----Quad Flat PackSDIP-----Shrink Dual In-Line PackageSOIC-----Small Outline Integrated PackageSSOP-----Shrink Small Outline PackageDIP-----Dual In-Line Package-----双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

微电子工艺基础封装技术

微电子工艺基础封装技术

一、引言

微电子技术是21世纪新兴的技术,它以半导体技术和微机技术为基础,以芯片封装、电路能力优化、软件设计、系统集成、测试技术、校准

技术、无线通信技术等应用技术为实现系统的技术手段,用来实现手机、

计算机、智能家居、汽车等众多领域的电子设备的发展及制造。

微电子封

装技术是微电子技术的基础与重要组成部分,也是微电子产品出厂前质量

检查与完善的重要手段。

本文着重介绍微电子封装技术,包括其基本原理、术语、分类、应用和实施过程等。

二、微电子封装技术的基本原理

微电子封装技术是将晶圆、芯片、元器件组合在一起,将原来的小型

数字电路重新包装,使其功能更加全面,外形更加紧凑,就是微电子封装

技术。

将电子元器件物理、电气封装在一起,形成由介质连接的板块,具

有较强的功能性、可调整性和可靠性,是构建高效能、高可靠性的微电子

系统的基本要素。

微电子封装的基本工艺包括:铆焊、封装、清洁和测试,这四个基本

步骤必须在一定的步骤中逐步完成,经过这些步骤,半导体器件可以被成

功封装到电路板中,以实现电路的功能,为其余的电子系统构建提供基础

支撑。

三、封装技术术语。

半导体封装形式介绍

半导体封装形式介绍摘要:半导体器件有许多封装型式,从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技术指标一代比一代先进,这些都是前人根据当时的组装技术和市场需求而研制的。

总体说来,它大概有三次重大的革新:第一次是在上世纪80年代从引脚插入式封装到表面贴片封装,极大地提高了印刷电路板上的组装密度;第二次是在上世纪90年代球型矩正封装的出现,它不但满足了市场高引脚的需求,而且大大地改善了半导体器件的性能;晶片级封装、系统封装、芯片级封装是现在第三次革新的产物,其目的就是将封装减到最小。

每一种封装都有其独特的地方,即其优点和不足之处,而所用的封装材料,封装设备,封装技术根据其需要而有所不同。

驱动半导体封装形式不断发展的动力是其价格和性能。

关键词:半导体;芯片级封装;系统封装;晶片级封装中图分类号:TN305.94 文献标识码:C 文章编号:1004-4507(2005)05-0014-081 半导体器件封装概述电子产品是由半导体器件(集成电路和分立器件)、印刷线路板、导线、整机框架、外壳及显示等部分组成,其中集成电路是用来处理和控制信号,分立器件通常是信号放大,印刷线路板和导线是用来连接信号,整机框架外壳是起支撑和保护作用,显示部分是作为与人沟通的接口。

所以说半导体器件是电子产品的主要和重要组成部分,在电子工业有“工业之米"的美称。

我国在上世纪60年代自行研制和生产了第一台计算机,其占用面积大约为100 m2以上,现在的便携式计算机只有书包大小,而将来的计算机可能只与钢笔一样大小或更小。

计算机体积的这种迅速缩小而其功能越来越强大就是半导体科技发展的一个很好的佐证,其功劳主要归结于:(1)半导体芯片集成度的大幅度提高和晶圆制造(Wafer fabrication)中光刻精度的提高,使得芯片的功能日益强大而尺寸反而更小;(2)半导体封装技术的提高从而大大地提高了印刷线路板上集成电路的密集度,使得电子产品的体积大幅度地降低。

tab封装芯片的原理

tab封装芯片的原理

封装芯片是将芯片引脚通过一定的材料和工艺,将其封装在一个具有特定形状和引脚布局的外壳中,以便在电路板上进行固定、连接和保护的一种工艺。

其中,TAB(Tape Automated Bonding)封装是一种主要用于集成电路封装的封装技术。

TAB封装芯片的原理如下:

1.切割:将芯片切割成较小的芯片片段,每个片段上都有电路的功能。

2.薄化:将切割好的芯片片段进行薄化处理,以减小芯片的厚度,方便后续封装。

3.电路制作:在薄化的芯片片段上通过光刻、蒸镀等工艺制作电路图案,包括金属导线、电阻、电容等元件。

4.粘合:将薄化并制作好电路的芯片片段使用粘合剂固定在一条特殊的胶带上,用于后续的导线连接。

5.导线连接:使用导线将芯片片段上的电路连接到胶带的引脚上,通过微型焊接或激光焊接等方式实现芯片和胶带之间的电气连接。

6.模切:将连接好的芯片片段和胶带一并切割成独立的小片,每个小片上都有一部分芯片和引脚。

7.封装:将切割好的小片通过背胶和封装工艺封装在一种具有特定形状和引脚布局的塑料外壳中,形成最终的封装芯片。

8.测试:对封装好的芯片进行测试,确认芯片的功能和性能是否正常。

9.贴片焊接:将封装好的芯片通过表面贴装技术焊接到电路板上,与其他元器件连接组成完整的电路系统。

通过TAB封装技术,可以实现集成电路的小型化、高密度集成和高可靠性,在电子产品中有着广泛的应用。

yt8521原理封装

实 现 比 传 统 电池 系 统 高 2到 5倍 的 能 量 密 度 : 将

基 于有 机材 料 的太 阳能 电池直 接 整合 到车 辆 中 .

发 展 . 中 国 化 工 信 息 中心 将 于 1 0月 9 1 ~ 1日在 山

东龙 口举 办第二届 (00年 )中 国钛 白粉制遣及 21

应 用 论 坛 。 坛 将 以结 构 调 整 、 升 综 合 竞 争 力 为 论 提

马 .预 计 今 年 底 国 内钛 白粉 总 产 能 将 增 至 2 0万 2 吨 . 比增 长 4 .% . 场 竞 争 将 日趋 激 烈 . I 同 67 市 出S l 又 受 到 国家 取 消 “ 高 一 资 ” 产 品 出 口退 税 的制 两 约 。 邦 、 斯 创 等 国 际 钛 白粉 巨 头 在 中 国加 紧 布 杜 科

米/ 和 5 4 秒 04米 / 秒 检 测 结 果 达 到 混 装 乳 化 炸 药

的 爆 速 国 家 规 定 4 0 ~ 5 0米 / 的 规 范 要 求 . 00 5 0 秒 满

为 促 进 我 国 钛 白粉 行 业 进 一 步 健 康 、 持 续 可 足 了大 型 露 天 磷 矿 山 的 生 产 使 用 要 求 。

奖 。该 奖 项 旨 在 表 彰 汽 车 领 域 的 突 破 性 理 念 、 创

延 续 上 年 的 上 升 势 头 , 业 保 持 较 高 的盈 利 水 平 企 但 良好 的 市 场 形 势 难 掩 产 能 过 剩 、产 品 同质 化 严

重 的 隐 忧 。 前 。 大 批 新 建 和 扩 能 项 目正 纷 纷 上 当 一

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

qjx 使用的局限性

Convection/Radiation Conduction Convection Conduction Radiation Convection/Radiation

X

θjx

Junction

Conduction

• qjx 试图采用简单的热阻表示复杂的芯片传热现象 • 芯片内部的热传现象非常复杂,无法使用热阻来完美表示; • 热阻qjx 无法用于准确预测芯片的温度,只能提供定性的热性 能对比; • 如需准确预测特定工况下芯片的温度,我们需要其它的方法

根据各热阻节点的温度值优 化得出具有最小误差的热阻值

误差估计

简化 模型

PBGA封装模型的建立

• PBGA封装特点?

– 有机基片Organic substrate – 使用焊球(Solder balls)作为二级互联 主要应用: ASIC’s, 内存, 图形显示,芯片组,通讯等.

•

• PBGA封装优缺点? – I/O密度高; – 基片材BT具有较好的电性能; – 加工工艺类似PCB板,成本低廉 – 非气密封装,不适合于长时工作的芯片或军用芯片 – Die与基片(Substrate)间的CTE不匹配 – 如功耗大于2W,则可能需要加强散热手段

芯片的详细模型

建立所有芯片内部所有影响传热的结构

Die

硅或砷化镓材料,表面 有发热集成电路

Bond Wires

金或铝制,数目等同于外面管脚数

Solder Balls

通常材料为锡 铅合金95Pb/5Sn 或37Pb/63Sn.

Die Attach

通常为环氧树脂,厚为1-2mil

Leadframes

铜或铝42合金制

Signal Vias

Thermal Vias

Bottom Spreader

Power & Ground Planes

最主流的PBGA封装,相对成熟的加工技术,可处理5W以上热耗。

主要类型的PBGA封装

Fine-Pitch BGA

Bond Wires Die Attach & Solder Mask

主要类型的PBGA封装

Wire-Bonded PBGA (Die-up)

Epoxy-based Encapsulant BT Dielectric Die Attach & Solder Mask Gold Bond Wires Cu Traces

Silicon Die

Die Flag

Solder Balls (37Pb/63Sn)

Case

q jc

T j Tc P

Die

Junction

Substrate

PCB

qjb 结板热阻

qjb – 从结点至印制板的热阻 – 定义标准由文件 JESD51-8给出

q jb

T j Tb P

严格地讲,Theta-JB不仅仅反映了芯片的内 热阻,同时也反映了部份环境热阻,如印制板。 正因如些, Theta-JB相对于其它热阻而言,虽然 JEDEC组织在99年就发布了它的热阻定义方式, 但是芯片供应商采用较慢。 部份传热路径严重不对称芯片,如TO-263目 前尚无该热阻的定义标准

N

qjma 结-移动空气热阻

qjma – 空气流速范围为 0-1000 LFM – 定义标准由文件 JESD51-6给出

q jma

T j Ta P

– Ta = 空气温度,取点为风洞上流温度 – 印制板朝向为重大影响因素

qjc 结壳热阻

qjc

– 从结点到封装外表面(壳)的热阻,外表面壳取点尽量 靠近Die安装区域

PROFIT 项目 PRediction OF temperature gradients Influencing The quality of electronic products DELPHI项目 DEvelopment of Libraries of PHysical models for an Integrated design environment

Die Flag/Die Pad

铜制,用于加强传热或其它目地

Encapsulant

通常为环氧树脂材料

Substrate

通常由BT\FR4制 成(塑料芯片); 或氧化铝制成(陶 瓷芯片)

热阻网络模型-DELPHI模型

DELPHI 项目:从1993年到1996年,由欧盟资助,Flomerics公司负责协调 ,Alcatel Bell 、Alcatel Espace 、Philips CFT 、Thomson CSF 、Flomerics 、 NMRC 等公司合作,旨在开发芯片的简化热模型的精确表示方法。 PROFIT项目:同样由欧盟资助,由Philips公司负责协调,Flomerics、Nokia 、Infineon、Philips、ST、Micred、TIMA、等公司合作,旨在开发芯片热模型 的快速建立方法。 项目产生了一系列成果,如芯片的热阻网络模型DELPHI标准、JEDEC组 织认证的唯一热模型库FLOPACK、芯片热应力分析工具Flo/stress等。

• 由die-up PBGA变化而来 – 别名: FSBGA, ChipArrayTM Die Substrate – 焊球间隙较小 – 可归类为 Near-CSP – 建模也较困难 – 焊球间隙典型值为1mm,0.8mm,0.65mm,0.5mm,0.4mm – 经常缺少明显可见,比Die尺寸大的Die Pad,因为Die大小与封装大小相近 – 基片(substrate)中每个信号过孔都必须单独建出; – 在FLOPACK中,别名ChipArrayTM

DELPHI模型生成原理

封装参数 (结构、材料参数)

发布 详细 模型

标准实验验证

建立详细模型

多种边界条件可以表 示自然对流、强迫对流、 散热器等多种环境 DELPHI项目组定义了99种 边界条件; Flopack应用了44种或88种

在规定的N种边界条件下 批处理进行详细模型计算

根据各种封装特点离散出 各种热阻网络拓朴结构

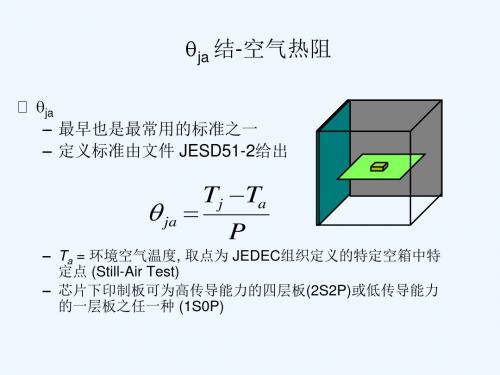

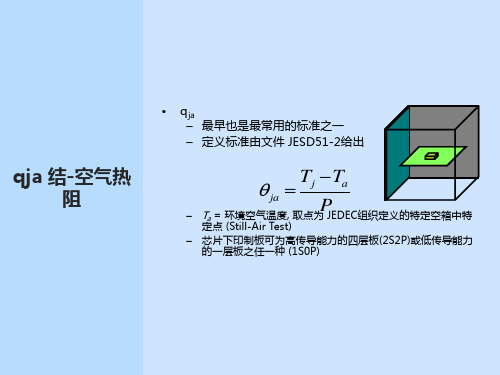

qja 结-空气热阻

qja – 最早也是最常用的标准之一 – 定义标准由文件 JESD51-2给出

q ja

T j Ta P

– Ta = 环境空气温度, 取点为 JEDEC组织定义的特定空箱中特 定点 (Still-Air Test) – 芯片下印制板可为高传导能力的Байду номын сангаас层板(2S2P)或低传导能力 的一层板之任一种 (1S0P)