dm9000中文芯片手册

4、元件介绍DM9000

下面我们来介绍一下TQ2440开发板上的另一个芯片—DM9000。

DM9000寄存器功能详细介绍总体看来DM9000是一个全集成、功能强、性价比高的快速以太网MAC层控制器。

它带有一个通用处理器接口、EEPROM接口、10/100 PHY和16KB的SRAM (其中13KB用来接收FIFO,3KB用来发送FIFO)。

电源模块采用的是单一电源,可以分别兼容3.3V和5V的IO接口电平。

DM9000支持MII(Media Independent Interface 介质无关)接口,可以连接到HPNA(Home Phone-line Networking Alliance)即家用电话网络联盟的设备上。

如果按照字面意思来理解,介质无关就是接口和介质没有关系。

在这里介质特指是指网络介质,也就是信号传输的媒介,如光纤、光缆、同轴电缆、各类双绞线等等。

介质无关接口作用是将不同类型的PHY与相同网络控制器(MAC)相连接。

MAC可以用同样的硬件接口与任意一个PHY相连接。

当然与之对应的是介质相关接口,用于PHY和传输介质的相连。

意味着对于不同的介质,相应的接口标准是不同的,故称之为“介质相关”。

DM9000以太网驱动器,内置一系列可被访问的控制状态寄存器。

这些字节对对齐的寄存器,在硬件或者软件复位时需要设置成初始值。

DM9000支持各类接口访问内部内部存储器,故而可以支持不同类型的处理器。

DM9000的物理层的协议接口支持使用10兆以下的第3类、4类、5类非屏蔽双绞线和100兆的第5类非屏蔽双绞线。

DM9000是一个集成度很高、功耗很低的高速网络控制器,用于各类开发板中。

它可以直接连接CPU部分,支持10M或100M的的快速以太网连接。

在DM9000内自带4K双字节的SRAM,其中13KB用来接收,另外3KB用来发送。

它支持8各类CPU,还有IEEE 802.3x全双工流量控制。

在整个流程中DM9000的操作很简单,故而用户可以轻易的移植系统里的端口驱动程序。

DM9000A中文手册完整版

DAVICOM Semiconductor, Inc.DM9000AEthernet Controllerwith General Processor InterfaceDATA SHEET(中文数据手册)PreliminaryVersion: DM9000A-DS-P03Apr. 21, 2005目录1. 概述 (5)2. 模块图 (5)3. 特性 (5)4. 引脚配置 (6)4.1(16位模式) (6)4.2(8位模式) (7)5. 引脚描述 (7)5.1处理器接口 (7)5.1.1 8位模式引脚 (8)5.2 EEPROM接口 (8)5.3时钟引脚 (9)5.4 LED接口 (9)5.5 10/100 PHY/Fiber (9)5.6其他 (10)5.7电源引脚 (10)5.8捆绑引脚列表(Strap pins table) (10)6. 控制和状态寄存器列表 (10)6.1网络控制寄存器(NCR) (12)6.2网络状态寄存器(NSR) (13)6.3发送控制寄存器(TCR) (13)6.4数据包1发送状态寄存器1(TSR I) (13)6.5数据包2发送状态寄存器2(TSR II) (14)6.6接收控制寄存器(RCR) (14)6.7接收状态寄存器(RSR) (15)6.8接收溢出计数寄存器(ROCR) (15)6.9背压阈值寄存器(BPTR) (15)6.10流控制阈值寄存器(FCTR) (16)6.11接收/发送流控制寄存器(RTFCR) (16)6.12 EEPROM与PHY控制寄存器(EPCR) (17)6.13 EEPROM与PHY地址寄存器(EPAR) (17)6.14 EEPROM与PHY数据寄存器(EPDRL/EPDRH) (18)6.15唤醒控制寄存器(WCR) (18)6.16物理地址(MAC)寄存器(PAR) (18)6.17多播地址寄存器(MAR) (19)6.18通用目的控制寄存器(GPCR) (19)6.19通用目的寄存器(GPR) (19)6.20 TX SRAM读指针地址寄存器(TRPAL/TRPAH) (20)6.21 RX SRAM写指针地址寄存器(RWPAL/RWPAH) (20)6.22厂家ID寄存器(VID) (20)6.23产品ID寄存器(PID) (20)6.24芯片版本寄存器(CHIPR) (20)6.25发送控制寄存器2(TCR2) (20)6.26操作测试控制寄存器(OCR) (21)6.27特殊模式控制寄存器(SMCR) (21)6.28即将发送控制/状态寄存器(ETXCSR) (22)6.29校验和控制寄存器(TCSCR) (22)6.30接收校验和控制状态寄存器(RCSCSR) (22)6.31内存数据预取读命令寄存器(地址不加1)(MRCMDX) (23)6.32内存数据读命令寄存器(地址不加1)(MRCMDX1) (23)6.33内存数据读命令寄存器(地址加1)(MRCMD) (23)6.34内存数据读地址寄存器(MRRL/ MRRH) (23)6.35内存数据写命令寄存器(地址不加1)(MWCMDX) (23)6.36内存数据写命令寄存器(地址加1)(MWCMD) (24)6.37内存数据写地址寄存器(MWRL/ MWRH) (24)6.38发送数据包长度寄存器(TXPLL/TXPLH) (24)6.39中断状态寄存器(ISR) (24)6.40中断屏蔽寄存器(IMR) (24)7.EEPROM格式 (25)8.PHY寄存器描述 (26)8.1基本模式控制寄存器(BMCR) (27)8.2基本模式状态寄存器(BMSR) (28)8.3 PHY ID标识符寄存器#1(PHYID1) (29)8.4 PHY ID标识符寄存器#2(PHYID1) (29)8.5自动协商通知寄存器(ANAR) (30)8.6自动协商连接对象寄存器(ANLPAR) (31)8.7自动协商扩展寄存器(ANER) (32)8.8 DAVICOM指定配置寄存器(DSCR) (33)8.9 DAVICOM指定配置和状态寄存器(DSCSR) (34)8.10 10BASE-T配置/状态(10BTCSR) (36)8.11掉电控制寄存器(PWDOR) (36)8.12指定配置寄存器(SCR) (37)9. 功能描述 (38)9.1 主机接口(HI) (38)9.2 直接内存访问控制(DMAC) (38)9.3 数据包发送(PT) (38)9.4 数据包接收(PR) (38)9.5 100Base-TX操作 (39)9.5.1 4B5B编码器 (39)9.5.2扰频器(Scrambler) (39)9.5.3 并--串转换 (39)9.5.4 NRZ码到NRZI码转换 (39)9.5.5 NRZI码到MLT-3码转换 (39)9.5.6 MLT-3驱动 (39)9.5.7 4B5B编码 (40)9.6 100Base-TX接收器 (40)9.6.1 信号检测 (41)9.6.2 自适应补偿 (41)9.6.3 MLT-3到NRZI解码 (41)9.6.4 时钟复原模块 (41)9.6.5 NRZI 到NRZ (41)9.6.6 串-并转换 (41)9.6.7 扰频器 (41)9.6.8 编码组对齐模块 (41)9.6.9 4B5B解码 (42)9.7 10Base-T操作 (42)9.8 冲突检测 (42)9.9 载波检测 (42)9.10 自动协商 (42)9.11 省电模式 (42)9.11.1 掉电模式 (43)9.11.2 降低发送损耗模式 (43)10 DC与AC电器特性 (43)10.1 最大绝对额定值 (43)10.1.1 工作条件 (43)10.2 DC电器特性(VDD=3.3V) (44)10.3 AC电器特性与时序 (44)10.3.1 TP接口 (44)10.3.2 晶振/振荡时钟 (44)10.3.3 I/O读时序 (45)10.3.4 I/O写时序 (45)10.3.5 EEPROM接口时序 (46)11应用说明 (46)11.1网络接口信号接线 (46)11.2 10Base-T/100Base-TX自动MDIX应用 (47)11.3 10Base-T/100Base-TX无自动MDIX变压器应用 (47)11.4电源退偶电容 (47)11.5地平面布局 (48)11.6电源平面分割 (49)11.7铁氧体磁珠选择指导 (50)11.8晶振选择指导 (50)12封装信息 (50)13订购信息 (52)DM9000A翻译人:许建华、刘煜、程志成2009-9-1版权:翻译版权归作者三方所有,不得随意传播。

DM9000中文手册

9.功能描述9.1主机接口主机接口是ISA总线兼容模式,有8个IO口基址,分别是300H、310H、320H、330H、340H、350H、360H、370H。

IO基址由设置引脚决定或者由EEPROM重载。

主机接口只有两个寻址口(addressing port),一个是索引口(index Port),另一个是数据口(data port)。

CMD=0时是索引口,CMD=1时是数据口。

索引口的内容是数据口的寄存器地址。

在读写任何寄存器之前,必须通过索引口保存这些寄存器的地址。

9.2直接数据存取控制DM9000提供了DMA功能、简化了内部存储器的存取。

在初始化了内部存储器的起始地址、发送了一个虚拟的读写指令将当前数据加载到内部数据缓冲区后,读写指令寄存器就可以读写内部指令寄存器的指定位置了。

存储器地址将按照当前运行模式(如8位模式、16位模式、32位模式)递增,而且下一个存储器地址的数据将自动被加载到数据缓冲区。

注意,第一次读取的一连串数据(即虚拟读写指令)必须忽略,因为这些数据是上一次读写指令的内容。

内部存储器空间是16K字节。

开始的3K字节用作包传输的数据缓冲区。

接下来的13K 字节用作接收包的缓冲区。

所以在写存储器操作时,当IMR的第七位置一时,如果存储器地址增量到达传输缓冲区的末尾(3K)时将强置为0。

类似的,在读存储器操作时,当IMR 的第七位置一时,如果存储器地址增量到达接收缓冲区的末尾(16K)时将强置为0x0C00。

9.3数据包传输有两个传输包,依次是INDEX I和INDEX II,可以被同时保存到发送SRAM中。

发送控制寄存器(02H)控制着冗余校验码和便签(pads)的插入。

传输包的状态被分别记录在发送状态寄存器I(03H)和发送状态寄存器II(04H)中。

传输的起始地址是00H,软件复位或者硬件复位后,当前包是INDEX I。

首先使用DMA 口写数据到TX SRAM,然后写字节数到的字节数寄存器,即发送包长度寄存器(0FCH/0FDH)。

DM9000网卡的基本工作原理

DM9000⽹卡的基本⼯作原理MAC:主要负责数据帧的创建,数据差错,检查,传送控制等。

PHY:物理接⼝收发器,当收到MAC过来的数据时,它会加上校验码,然后按照物理层的规则进⾏数据编码,再发送到传输介质上,接收过程则相反。

MII:媒体独⽴接⼝,“媒体独⽴”表明MAC⼀定情况下,任何类型的PHY设备都可以正常⼯作。

DM9000⽹卡部分函数实现:/*//实验步骤//初始化dm900//数据包发送//数据包接收*/#include "dm9000.h"#include "arp.h"#define DM_ADD (*((volatile unsigned short *)0x18000000))#define DM_DAT (*((volatile unsigned short *)0x18000004))/*Register*/#define MEM_SYS_CFG (*(volatile unsigned *)0x7E00F120)#define SROM_BW (*(volatile unsigned *)0x70000000)#define SROM_BC1 (*(volatile unsigned *)0x70000008)#define GPNCON (*(volatile unsigned *)0x7F008830) /* 中断相关寄存器 */#define EINT0CON0 (*(volatile unsigned *)0x7F008900)#define EINT0MASK (*(volatile unsigned *)0x7F008920)#define EINT0PEND (*(volatile unsigned *)0x7F008924)#define VIC0INTENABLE (*(volatile unsigned *)0x71200010)#define EINT7_VECTADDR (*(volatile unsigned *)0x71200104)#define VIC0ADDRESS *((volatile unsigned int *)0x71200f00)#define VIC1ADDRESS *((volatile unsigned int *)0x71300f00)u8 *buffer = &arpbuf;u8 host_mac_addr[6] = {0xff,0xff,0xff,0xff,0xff,0xff};u8 mac_addr[6] = {9,8,7,6,5,4};u8 ip_addr[4] = {192,168,1,113};u8 host_ip_addr[4] = {192,168,1,101};u16 packet_len;void cs_init(){// MEM_SYS_CFGSROM_BW &= (~(1<<4)); //设置位宽度SROM_BW |= (1<<4);SROM_BC1 = (0x0<<28)|(0x0<<24)|(0x7<<16)|(0x0<<12)|(0x0<<8)|(0x0<<4)|(0x0<<0); //设置时序参考uboot ok6410的⽹卡⽚选位于bank1 }void int_init() //中断初始化{GPNCON &= (~(0x3<<14));GPNCON |= (0x2<<14);// EINT0PEND &= (~(0x1<<7));// EINT0PEND |= (0x1<<7);}void dm9000_reg_write(u16 reg,u16 data){DM_ADD = reg;DM_DAT = data;}u8 dm9000_reg_read(u16 reg){DM_ADD = reg;return DM_DAT;}void dm9000_reset(){dm9000_reg_write(DM9000_GPCR, GPCR_GPIO0_OUT);dm9000_reg_write(DM9000_GPR, 0);dm9000_reg_write(DM9000_NCR, (NCR_LBK_INT_MAC | NCR_RST));dm9000_reg_write(DM9000_NCR, 0);dm9000_reg_write(DM9000_NCR, (NCR_LBK_INT_MAC | NCR_RST));dm9000_reg_write(DM9000_NCR, 0);}void dm9000_probe(void){u32 id_val;id_val = dm9000_reg_read(DM9000_VIDL);id_val |= dm9000_reg_read(DM9000_VIDH) << 8;id_val |= dm9000_reg_read(DM9000_PIDL) << 16;id_val |= dm9000_reg_read(DM9000_PIDH) << 24;if (id_val == DM9000_ID) {printf("dm9000 is found !\n");return ;} else {printf("dm9000 is not found !\n");return ;}}void dm9000_init(){u32 i;/*⽚选(独⽴芯⽚)*/cs_init();/*中断初始化*/int_init();/*设备复位操作*/dm9000_reset();/*捕获dm9000*/dm9000_probe();/*MAC初始化*//* Program operating register, only internal phy supported */dm9000_reg_write(DM9000_NCR, 0x0);/* TX Polling clear */dm9000_reg_write(DM9000_TCR, 0);/* Less 3Kb, 200us */dm9000_reg_write(DM9000_BPTR, BPTR_BPHW(3) | BPTR_JPT_600US);/* Flow Control : High/Low Water */dm9000_reg_write(DM9000_FCTR, FCTR_HWOT(3) | FCTR_LWOT(8));/* SH FIXME: This looks strange! Flow Control */dm9000_reg_write(DM9000_FCR, 0x0);/* Special Mode */dm9000_reg_write(DM9000_SMCR, 0);/* clear TX status */dm9000_reg_write(DM9000_NSR, NSR_WAKEST | NSR_TX2END | NSR_TX1END);/* Clear interrupt status */dm9000_reg_write(DM9000_ISR, ISR_ROOS | ISR_ROS | ISR_PTS | ISR_PRS);/*填充MAC地址*/for (i = 0; i < 6; i++)dm9000_reg_write(DM9000_PAR+i, mac_addr[i]);/*激活DM9000*/dm9000_reg_write(DM9000_RCR, RCR_DIS_LONG | RCR_DIS_CRC | RCR_RXEN);/* Enable TX/RX interrupt mask */dm9000_reg_write(DM9000_IMR, IMR_PAR);}void dm9000_tx(u8 *data,u32 length){u32 i;/*禁⽌中断*/dm9000_reg_write(DM9000_IMR,0x80);/*写⼊发送数据的长度*/dm9000_reg_write(DM9000_TXPLL, length & 0xff);dm9000_reg_write(DM9000_TXPLH, (length >> 8) & 0xff);/*写⼊待发送的数据*/DM_ADD = DM9000_MWCMD; // MWCMD是DM9000内部SRAM的DMA指针,根据处理器模式,写后⾃动增加for(i=0;i<length;i+=2){DM_DAT = data[i] | (data[i+1]<<8); //低8 ⾼8}/*启动发送*/dm9000_reg_write(DM9000_TCR, TCR_TXREQ);/*等待发送结束*/while(1){u8 status;status = dm9000_reg_read(DM9000_TCR);if((status&0x01)==0x00)break;}/*清除发送状态*/dm9000_reg_write(DM9000_NSR,0x2c);/*恢复中断使能*/dm9000_reg_write(DM9000_IMR,0x81);// printf("dm9000_tx");}#define PTK_MAX_LEN 1522u32 dm9000_rx(u8 *data){u8 status,len;u16 tmp;u32 i;/*判断是否产⽣中断,且清除*/if(dm9000_reg_read(DM9000_ISR) & 0x01)dm9000_reg_write(DM9000_ISR,0x01);elsereturn0;/*空读*/dm9000_reg_read(DM9000_MRCMDX);/*读取状态*/status = dm9000_reg_read(DM9000_MRCMD);/*读取包长度*/len = DM_DAT;/*读取包数据*/if(len<PTK_MAX_LEN){for(i=0;i<len;i+=2){tmp = DM_DAT;data[i] = tmp & 0x0ff;data[i+1] = (tmp>>8)&0x0ff; }}return len;}。

Linux设备树语法详解

Linux设备树语法详解Linux内核从3.x开始引⼊设备树的概念,⽤于实现驱动代码与设备信息相分离。

在设备树出现以前,所有关于设备的具体信息都要写在驱动⾥,⼀旦外围设备变化,驱动代码就要重写。

引⼊了设备树之后,驱动代码只负责处理驱动的逻辑,⽽关于设备的具体信息存放到设备树⽂件中,这样,如果只是硬件接⼝信息的变化⽽没有驱动逻辑的变化,驱动开发者只需要修改设备树⽂件信息,不需要改写驱动代码。

⽐如在ARM Linux内,⼀个.dts(device tree source)⽂件对应⼀个ARM的machine,⼀般放置在内核的"arch/arm/boot/dts/"⽬录内,⽐如exynos4412参考板的板级设备树⽂件就是"arch/arm/boot/dts/exynos4412-origen.dts"。

这个⽂件可以通过$make dtbs命令编译成⼆进制的.dtb⽂件供内核驱动使⽤。

基于同样的软件分层设计的思想,由于⼀个SoC可能对应多个machine,如果每个machine的设备树都写成⼀个完全独⽴的.dts⽂件,那么势必相当⼀些.dts⽂件有重复的部分,为了解决这个问题,Linux设备树⽬录把⼀个SoC公⽤的部分或者多个machine共同的部分提炼为相应的.dtsi⽂件。

这样每个.dts就只有⾃⼰差异的部分,公有的部分只需要"include"相应的.dtsi⽂件, 这样就是整个设备树的管理更加有序。

我这⾥⽤`Linux4.8.5源码⾃带的dm9000⽹卡为例来分析设备树的使⽤和移植。

这个⽹卡的设备树节点信息在"Documentation/devicetree/bindings/net/davicom-dm9000.txt"有详细说明,其⽹卡驱动源码是"drivers/net/ethernet/davicom/dm9000.c"。

dm9000中文芯片手册

各 种其 他 功能 引 脚

16~19 TEST1~4 I

48

TEST5 I

68~69 GPIO0~3 I/O

78

LINK_O O

79

WAKEUP O

工作模式

Test1~4(1, 1,0,0)正常 工作状态

必须接地

通用 I/O 端 口

通用 端口控制 寄存器和 通用端口 寄存器能 编程该系 列引脚

GPIO0 默 认输出为 高来关闭 物理层和 其他外部 介质无关 器件

外部介质 无关接口 接收错误

外部介质 无关接口 接收时钟

外部介质 无关接口 发送时钟

外部介质 无关接口 发送数据 低 4 位输

出

TXD[2:0] 决定内部 存储空间 基址:TXD [2:0]) * 10H + 300H

外部介质

无关接口

54

MDIO I/O

串行数据

通信

57

MDC O

外部介质 无关串行 数据通信 口时钟,且 与中断引 脚有关

带隙引脚

27

AVDD P

带隙与电 源保护环

28

AVDD P

接收端口 电源

29

RXI+ I

物理层接 收端的正 极

30

RXI-

I

物理层接 收端的负 极

31

AGND P

接收端口 地

32

AGND P

发送端口 地

33

TXO+ O

物理层发 送端口正 极

34

TXO- O

发送端口 负极

35

AVDD P

物理层发 送端口负 极

WAKEUP EEDO 总 线宽度

00 16 位

单芯片快速以太网MAC控制器DM9000介绍第二讲

单芯片快速以太网MAC控制器DM9000介绍DM9000内部寄存器DM9000包含一系列可被访问的控制状态寄存器,这些寄存器是字节对齐的,他们在硬件或软件复位时被设置成初始值。

以下为DM9000 的寄存器功能详解:NCR(00H):网络控制寄存器(Network Control Register)7:EXT_PHY:1选择外部PHY,0选择内部PHY,不受软件复位影响。

6:WAKEEN:事件唤醒使能,1使能,0禁止并清除事件唤醒状态,不受软件复位影响。

5:保留。

4:FCOL:1强制冲突模式,用于用户测试。

3:FDX:全双工模式。

内部PHY模式下只读,外部PHY下可读写。

2-1:LBK:回环模式(Loopback)00 通常,01MAC内部回环,10 内部PHY100M模式数字回环,11 保留。

0:RST:1 软件复位,10us后自动清零。

NSR(01H):网络状态寄存器(Network Status Register)7:SPEED:媒介速度,在内部PHY 模式下,0 为100Mbps,1 为10Mbps。

当LINKST=0 时,此位不用。

6:LINKST :连接状态,在内部PHY 模式下,0 为连接失败,1 为已连接。

5:WAKEST:唤醒事件状态。

读取或写1 将清零该位。

不受软件复位影响。

4:保留。

3:TX2END :TX(发送)数据包2完成标志,读取或写1 将清零该位。

数据包指针2传输完成。

2:TX2END :TX(发送)数据包1完成标志,读取或写1 将清零该位。

数据包指针1传输完成。

1:RXOV:RX(接收)FIFO(先进先出缓存)溢出标志。

0:保留。

TCR(02H):发送控制寄存器(TX Control Register)7:保留。

6:TJDIS:Jabber传输使能。

1使能Jabber传输定时器(2048字节),0 禁止。

注释:Jabber 是一个有 CRC 错误的长帧(大于1518byte而小于6000byte)或是数据包重组错误。

BL0972 交 直流电能计量芯片 数据手册 V1.0说明书

BL0972交/直流电能计量芯片数据手册V1.0目录1、产品简述 (5)2、基本特征 (6)2.1主要特点 (6)2.2系统框图 (7)2.3管脚排列(TSSOP20) (7)2.4性能指标 (8)2.4.1电参数性能指标 (8)2.4.2极限范围 (9)3、工作原理 (10)3.1电流电压波形产生原理 (10)3.1.1PGA增益调整 (10)3.1.2相位补偿 (11)3.1.3通道偏置校正 (11)3.1.4通道增益校正 (12)3.1.5电流电压波形输出 (12)3.2有功功率计算原理 (13)3.2.1有功波形的选择 (14)3.2.2有功功率输出 (14)3.2.3有功功率校准 (14)3.2.4有功功率的防潜动 (15)3.2.5有功功率小信号补偿 (15)3.3有功能量计量原理 (16)3.3.1有功能量输出 (16)3.3.2有功能量输出选择 (16)3.3.3有功能量输出比例 (17)3.4电流电压有效值计算原理 (17)3.4.1有效值输出 (18)3.4.2有效值输入信号的设置 (18)3.4.3有效值刷新率的设置 (18)3.4.4电流电压有效值校准 (19)3.4.5有效值的防潜动 (19)3.5快速有效值检测原理 (20)3.5.1快速有效值输出 (20)3.5.2快速有效值输入选择 (21)3.5.3快速有效值累计时间和阈值 (21)3.5.4电网频率选择 (21)3.5.5快速有效值超限数据保存 (22)3.5.6过流指示 (22)3.5.7继电器控制 (22)3.6温度计量 (23)3.7.1线周期计量 (23)3.7.2线频率计量 (23)3.7.3相角计算 (24)3.7.4功率符号位 (24)3.8故障检测 (25)3.8.1过零检测 (25)3.8.2峰值超限 (25)3.8.3线电压跌落 (26)3.8.4过零超时 (27)3.8.5电源供电指示 (28)4、内部寄存器 (30)4.1电参量寄存器(只读) (30)4.2校表寄存器(外部写) (30)4.3OTP寄存器 (32)4.4模式寄存器 (33)4.4.1 MODE1寄存器 (33)4.4.2 MODE2寄存器 (33)4.4.3 MODE3寄存器 (34)4.5中断状态寄存器 (34)4.5.1 STATUS1寄存器 (34)4.5.2 STATUS3寄存器 (34)4.6校表寄存器详细说明 (34)4.6.1 通道PGA增益调整寄存器 (34)4.6.2 相位校正寄存器 (35)4.6.3 有效值增益调整寄存器 (35)4.6.4 有效值偏置校正寄存器 (36)4.6.5 有功小信号补偿寄存器 (36)4.6.7 防潜动阈值寄存器 (36)4.6.8 快速有效值相关设置寄存器 (37)4.6.9 过流报警及控制 (38)4.6.11 能量读后清零设置寄存器 (39)4.6.12 用户写保护设置寄存器 (39)4.6.13 软复位寄存器 (39)4.6.14 通道增益调整寄存器 (40)4.6.15 通道偏置调整寄存器 (40)4.6.16 有功功率增益调整寄存器 (40)4.6.17 有功功率偏置调整寄存器 (41)4.6.20 CF缩放比例寄存器 (41)4.7电参数寄存器详细说明 (42)4.7.1 波形寄存器 (42)4.7.2 有效值寄存器 (42)4.7.3 快速有效值寄存器 (42)4.7.7 电能脉冲计数寄存器 (43)4.7.8 波形夹角寄存器 (44)4.7.9 快速有效值保持寄存器 (44)4.7.11 线电压频率寄存器 (44)5、SPI通讯接口 (45)5.1概述 (45)5.2工作模式 (45)5.3帧结构 (45)5.4读出操作时序 (46)5.5写入操作时序 (47)5.6SPI接口的容错机制 (48)6、典型应用图 (49)7、封装信息 (50)1、产品简述BL0972是一颗内置时钟的单相交/直流电能计量芯片。

DM9000EP存储器的研究

DM9000EP存储方式的研究摘要: 在智能变电站中,全站信息需共享。

在这个过程中,通信显得尤为重要。

多台MU采集多台馈线上的实时信息,通过交换机,以太网控制器,传至保护装置中,其中,以太网控制器起着承上启下的作用,以太网控制器选择DM9000EP芯片。

如果以太网控制器收不到包,整个保护失去作用。

在装置测试的过程中,发现在DM9000传数给保护板ARM时,会显现丢包现象,针对这种现象,猜测是DM9000没有收到包呢?还是保护板ARM与DM9000间的通信机制存在问题,DM9000能收到了所有的包,保护板arm处理不过来。

针对这个问题,仔细研究DM9000的通信原理,在程序上得以验证,DM9000的内部SRAM中能够收到13Kbyte 字节的数据,丢包原因是DM9000与ARM的通信机制问题。

关键词:DM9000EP;丢包;0 引言在智能变电站集成保护系统中,通信起着至关重要的作用。

目前,网络技术在继电保护中的应用越来越广,更多的设备需要提供网络接口,以方便与外部互联通讯。

在通信的过程。

以太网技术以其灵活方便的连接方式、良好的开放性、高效、低廉等优点,已经广泛地应用于各种继电保护中,并且还在不断的发展。

在智能变电站整机实验中,出现丢包问题,研究DM9000EP内部SRAM 的存储方式,研究发现在SRAM的收包缓存中能够存储13kbyte字节的包,DM9000能够完整的收到数据包。

导致丢包的原因是DM9000与ARM 通信机制问题。

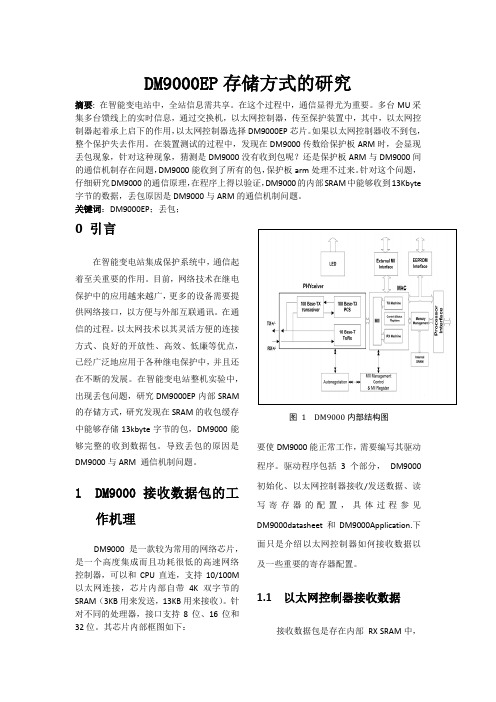

1DM9000接收数据包的工作机理DM9000是一款较为常用的网络芯片,是一个高度集成而且功耗很低的高速网络控制器,可以和CPU直连,支持10/100M 以太网连接,芯片内部自带4K双字节的SRAM(3KB用来发送,13KB用来接收)。

针对不同的处理器,接口支持8位、16位和32位。

其芯片内部框图如下:图1 DM9000内部结构图要使DM9000能正常工作,需要编写其驱动程序。

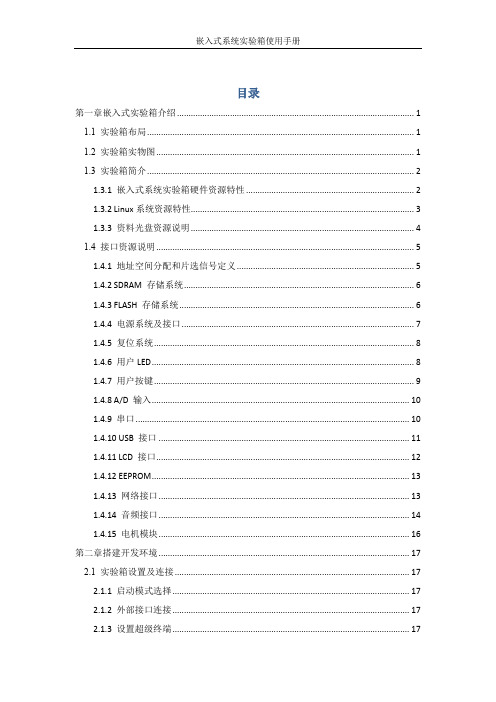

嵌入式系统实验箱使用手册

BL0942 内置时钟免校准计量芯片 数据手册说明书

BL0942 datasheetBL0942免校准计量芯片数据手册目录1产品简述 (4)1.1功能简介 (4)1.2主要特点 (4)1.3系统框图 (5)1.4封装与管脚描述 (6)1.5寄存器列表 (8)1.6特殊寄存器说明 (9)1.7性能指标 (11)1.7.1电参数性能 (11)1.7.2极限范围 (12)2功能描述 (13)2.1电流电压瞬态波形计量 (13)2.2有功功率 (14)2.3有功功率防潜动 (14)2.4电能计量 (15)2.5电流电压有效值 (16)2.6过流检测 (17)2.7过零检测 (18)2.8线电压频率检测 (21)3通讯接口 (22)3.1SPI (22)3.1.1工作模式 (22)3.1.2帧结构 (23)3.1.3写入操作时序 (23)3.1.4读出操作时序 (24)3.1.5SPI接口的容错机制 (24)3.2UART (25)3.2.1波特率配置 (25)3.2.2每个字节格式 (25)3.2.3写入时序 (26)3.2.4读取时序 (26)3.2.5时序说明 (27)3.2.6数据包发送模式 (28)3.2.7UART接口的保护机制 (29)4订单信息 (29)5丝印信息 (29)6封装 (30)1产品简述1.1功能简介BL0942是一颗内置时钟免校准电能计量芯片,适用于单相多功能电能表、智能插座、智能家电等应用,具有较高的性价比。

BL0942集成了2路高精度Sigma-Delta ADC,参考电压,电源管理等模拟电路模块,以及处理有功功率、电流电压有效值等电参数的数字信号处理电路。

BL0942能够测量电流、电压有效值、有功功率、有功电能量等参数,可输出快速电流有效值(用于过流保护),以及波形输出等功能,通过UART/SPI接口输出数据,能够充分满足智能插座、智能家电、单相多功能电能表及用电信息大数据采集等领域的需要。

BL0942具有专利防潜动设计,配合合理的外部硬件设计,可确保在无电流时噪声功率不被计入电能脉冲。

DM9000中文手册

dm90001、总体介绍该DM9000是一款完全集成的和符合成本效益单芯片快速以太网MAC 控制器与一般处理接口,一个10/100M 自适应的PHY 和4K DWORD 值的SRAM 。

它的目的是在低功耗和高性能进程的3.3V 与5V 的支持宽容。

DM9000还提供了介质无关的接口,来连接所有提供支持介质无关接口功能的家用电话线网络设备或其他收发器。

该DM9000支持8位,16位和32-位接口访问内部存储器,以支持不同的处理器。

DM9000物理协议层接口完全支持使用10MBps 下3类、4类、5类非屏蔽双绞线和100MBps 下5类非屏蔽双绞线。

这是完全符合I EEE 802.3u 规格。

它的自动协调功能将自动完成配置以最大限度地适合其线路带宽。

还支持IEEE 802.3x 全双工流量控制。

这个工作里面DM9000是非常简单的,所以用户可以容易的移植任何系统下的端口驱动程序。

2、特点支持处理器读写内部存储器的数据操作命令以字节/字/双字的长度进行集成10/100M 自适应收发器支持介质无关接口支持背压模式半双工流量控制模式IEEE802.3x 流量控制的全双工模式支持唤醒帧,链路4K 双字SRAM支持自动加载EEPROM 里面生产商ID 和产品ID支持4个通用输入输出口超低功耗模式功率降低模式电源故障模式可选择1:1YL18-2050S,YT37-1107S 或5:4变压比例的变压器降低格外功率兼容3.3v 和5.0v 输入输出电压100脚CMOS LQFP 封装工艺3、引脚描述I=输入O=输出I/O=输入/输出O/D=漏极开路P=电源LI=复位锁存输入#=普遍低电位介质无关接口引脚引脚号引脚名I/O功能描述37LINK_I I外部介质无关接口器件连接状态38、39、40、41RXD[3:0]I外部介质无关接口接收数据4位半字节输入(同步于接收时钟)43CRS I/O外部介质无关接口的载波检测44COL I/O外部介质无关接口的冲突检测,输出到外部设备45RX_DV I外部介质无关接口数据有效信号46RX_ER I外部介质无关接口接收错误47RX_CLK I外部介质无关接口接收时钟49TX_CLK I/O外部介质无关接口发送时钟50~53TXD[3:0]O外部介质无关接口发送数据低4位输出TXD[2:0]决定内部存储空间基址:TXD[2:0])*10H+300H54MDIO I/O外部介质无关接口串行数据通信57MDC O外部介质无关串行数据通信口时钟,且与中断引脚有关该引脚高电平时候,中断引脚低电平有效;否则高有效注意:以上介质无关端口都内部自带60K欧姆的下拉电阻处理器接口引脚1IOR#I处理器读命令低电平有效,极性能够被EEPROM修改,详细请参考对EEPROM内容的描述2IOW#I处理器写命令低电平有效,同样能修改极性3AEN#I芯片选择,低电平有效4IOWAIT O处理器命令就绪当上一指令没有结束,该引脚电平拉低表示当前指令需要等待14RST I硬件复位信号,高电平有效复位1~682~89SD0~15I/O0~15位的数据地址复用总线,由CMD引脚决定当期访问类型93~98SA4~9I地址线4~9;仅作芯片选择信号(SA4~9:TXD0~2,011)被选中92CMD I访问类型高电平是访问数据端口;低电平是访问地址端口91IO16O字命令标志,默认低电平有效当访问外部数据存储器是字或双字宽度时,被置位100INT O中断请求信号高电平有效,极性能修改37~5356SD31~16I/O双字模式,高16位数据引脚57IO32O双字命令标志,默认低电平有效注意:以上引脚除去SD8,SD9和IO16,都内部自带60K欧姆的下拉电阻EEPROM引脚64EEDI I数据输入引脚65EEDO I/O EEPROM数据引脚与WAKEUP引脚一起定义访问数据存储器的总线宽度WAKEUP EEDO总线宽度0016位0132位108位11未定义66EECK I时钟信号67EECS I/O片选也做LED模式选择引脚高电平时,LED模式1,否则模式注意:EECS EECK EEDO引脚都内部自带60K欧姆下拉电阻时钟引脚21X2_25M O25M晶振输出22X1_25M I25M晶振输入59CLK20MO O20M晶振再生输出给外部介质无关设备,自带60K欧姆下拉电阻LED引脚60SPEED100#O低电平指示100M带宽指示,高电平指示10M带宽61DUP#O全双工指示LEDLED模式0时,低电平显示工作在10M带宽,或在100M带宽浮动62LINK&ACT#O连接LED,在模式0时,只作物理层的载波监听检测连接状态10/100物理层与光纤接口24SD I光纤信号检测PECL电平信号,显示光纤接收是否有效25DGGND P带隙地信号线26BGRES I/O带隙引脚27AVDD P带隙与电源保护环28AVDD P接收端口电源29RXI+I物理层接收端的正极30RXI-I物理层接收端的负极31AGND P接收端口地32AGND P发送端口地33TXO+O物理层发送端口正极34TXO-O发送端口负极35AVDD P物理层发送端口负极各种其他功能引脚16~19TEST1~4I工作模式Test1~4(1,1,0,0)正常工作状态48TEST5I必须接地68~69GPIO0~3I/O通用I/O端口通用端口控制寄存器和通用端口寄存器能编程该系列引脚GPIO0默认输出为高来关闭物理层和其他外部介质无关器件GPIO1~3默认为输入引脚78LINK_O O电缆连接状态显示输出,高电平有效79WAKEUP O流出一个唤醒信号当唤醒事件发生内置60K欧姆的下拉电阻80PW_RST#I上电复位低电平激活DM9000的重新初始化,5us后初始化当该引脚测试到电平变化74,75,77NC无用电源引脚DVDD P数字电源5,20,36,55,72,90,73DGND P数字地15,23,42,5863,81,99,76内部寄存器DM9000(A)包含一系列可被访问的控制状态寄存器,这些寄存器是字节对齐的,他们在硬件或软件复位时被设置成初始值。

台湾联杰国际芯片DM9000CEPdm9000CIEP网络电路图

3

C

Ethernet_RST# R?

R? 10K 0

A

D? 1N4148

1 2

1 3

2

u? RESET_IC_(AP1701DW)

PWRST#

PWRST# CS# Ethernet_IOW# Ethernet_IOR# Ethernet_IRQ

C? R?

47uF 47K

SD0 SD1 SD2 SD3 SD4 SD5 SD6 SD7 SD8 SD9 SD10 SD11 SD12 SD13 SD14 SD15

YT37-1107S

C? 0.1uF

R? 75/1% C?

JP?

8 7 6 5 4 3 2 1

RJ-45

R? 75/1%

R? 75/1%

CS# LED2(IOWAIT / WAKEUP for eeprom) LED1(IO16 for eeprom) PWRST# TEST VDD X2 X1 GND SD AGND BGGND

CS#

LOW ACTIVE

25MHZ/49US

XTAL

C?

C?

22PF

22PF

C0603

C0603

IOR#

LOW ACTIVE

IOW#

LOW ACTIVE

A

A

INT

HIGH ACTIVE

PWRST# LOW ACTIVE

Title DM9000CEP_DEMO

Size Document Number

12 11 10 9 8 7 6 5 4 3 2 1

C? 0.1UF

R? 49.9/1%

C? 0.1uF

TX-

TX-

以太网与无线WIFI传输的机车车辆检测系统

以太网与无线WIFI传输的机车车辆检测系统白琳琳;吴学杰;毛伟成;魏永刚【摘要】为了解决传统车辆检测装置安装布线复杂,传输速率慢的缺点,设计了一种无线网络化的车辆检测系统.该系统以STM32为核心建立主控制器,MSP430单片机为核心建立无线传感器网络节点,通过传感器完成多种车辆振动信号的采集.采用无线WIFI与以太网两种通信方式实现控制指令与采集数据的高速传输,同时设计了基于C#.NET平台的人机交互界面,实现对车辆运行状态的实时监测.通过实验验证,系统能够完成车辆运行过程中速度,加速度等振动信号的高速采集、传输与处理.【期刊名称】《电子器件》【年(卷),期】2018(041)006【总页数】6页(P1543-1548)【关键词】STM32;MSP430;以太网;无线WIFI;C#.NET【作者】白琳琳;吴学杰;毛伟成;魏永刚【作者单位】西南交通大学牵引动力国家重点实验室,成都610036;西南交通大学牵引动力国家重点实验室,成都610036;西南交通大学牵引动力国家重点实验室,成都610036;西南交通大学牵引动力国家重点实验室,成都610036【正文语种】中文【中图分类】TP274轨道交通行业的飞速发展,缓解了交通拥堵的压力,随之而来的机车车辆运行安全与舒适问题得到广泛关注。

我国国家标准局与铁道部制订了 GB/T 5599—1985《铁道车辆动力学性能评定和试验鉴定规范》,通过对车辆运行中测点速度,加速度,位移,以及轮轨力,应变等多种振动信号的采集与处理,得到运行车辆的稳定性与平稳性指标,作为判定车辆在不同速度等级下安全性与舒适性的依据。

目前我国的车辆检测系统一般通过RS232或485接口与上位机通信,采用电缆线的方式实现数据的传输,存在电路连接复杂,线缆安装捆扎费时的缺点,并且在车辆运行过程中容易发生断线损坏,降低检测的可靠性[1]。

另一方面,铁路的不断提速与发展,传统的检测系统已经很难满足控制精度、传输速度以及实时性方面的要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DM9000介绍1、总体介绍该DM9000是一款完全集成的和符合成本效益单芯片快速以太网MAC控制器与一般处理接口,一个10/100M自适应的PHY和4K DWORD值的SRAM 。

它的目的是在低功耗和高性能进程的3.3V与5V的支持宽容。

DM9000还提供了介质无关的接口,来连接所有提供支持介质无关接口功能的家用电话线网络设备或其他收发器。

该DM9000支持8位,16位和32 -位接口访问内部存储器,以支持不同的处理器。

DM9000物理协议层接口完全支持使用10MBps下3类、4类、5类非屏蔽双绞线和100MBps下5类非屏蔽双绞线。

这是完全符合IEEE 8 02.3u规格。

它的自动协调功能将自动完成配置以最大限度地适合其线路带宽。

还支持IEEE 802.3x全双工流量控制。

这个工作里面DM9000是非常简单的,所以用户可以容易的移植任何系统下的端口驱动程序。

2、特点支持处理器读写内部存储器的数据操作命令以字节/ 字/ 双字的长度进行集成10/100M自适应收发器支持介质无关接口支持背压模式半双工流量控制模式IEEE802.3x流量控制的全双工模式支持唤醒帧,链路状态改变和远程的唤醒4K双字SRAM支持自动加载EEPROM里面生产商ID和产品ID支持4个通用输入输出口超低功耗模式功率降低模式电源故障模式可选择1:1或5:4变压比例的变压器降低格外功率兼容3.3v和5.0v输入输出电压100脚CMOS LQFP封装工艺3、引脚描述I=输入O=输出I/O=输入/输出O/D=漏极开路P=电源LI=复位锁存输入#=普遍低电位介质无关接口引脚引脚号引脚名I/O 功能描述37 LINK_I I 外部介质无关接口器件连接38、39、40、41 RXD [3:0] I外部介质无关接口接收数据4位半字节输入(同步于接收时钟)43 CRS I/O 外部介质无关接口的载波检测44 COL I/O 外部介质无关接口的冲突检测,输出到外部设备45 RX_DV I 外部介质无关接口数据有效信号46 RX_ER I 外部介质无关接口接收错误47 RX_CLK I 外部介质无关接口接收时钟49 TX_CLK I/O 外部介质无关接口发送时钟50~53 TXD[3:0] O 外部介质无关接口发送数据低4位输TXD[2:0]决定内部存储空间基址:TXD [2:0]) *10H + 300H54 MDIO I/O 外部介质无关接口串行数据通信57 MDC O 外部介质无关串行数据通信口时钟,且与中断引脚有关该引脚高电平时候,中断引脚低电平有效;否则高有效注意:以上介质无关端口都内部自带60K 欧姆的下拉电阻处理器接口引脚1 IOR# I 处理器读命令低电平有效,极性能够被EEPROM 修改,详细请参考对EEPROM 内容的描述2 IOW# I 处理器写命令低电平有效,同样能修改极性3 AEN# I 芯片选择,低电平有效4 IOWAIT O 处理器命令就绪当上一指令没有结束,该引脚电平拉低表示当前指令需要等待14 RST I 硬件复位信号,高电平有效复位1~6 82~89 SD0~15 I/O0~15位的数据地址复用总线,由CMD引脚决定当期访问类型93~98 SA4~9 I 地址线4~9;仅作芯片选择信号(SA4~9:TXD0~2 ,011)被选中92 CMD I 访问类型高电平是访问数据端口;低电平是访问地址端口91 IO16 O 字命令标志,默认低电平有效当访问外部数据存储器是字或双字宽度时,被置位100 INT O 中断请求信号高电平有效,极性能修改37~53 56 SD31~16 I/O 双字模式,高16位数据引脚57 IO32 O 双字命令标志,默认低电平有效注意:以上引脚除去SD8,SD9和IO16,都内部自带60K 欧姆的下拉电阻EEPROM引脚64 EEDI I 数据输入引脚65 EEDO I/O EEPROM数据引脚WAKEUP引脚一起定义访问数据存储器的总线宽度WAKEUPEEDO 总线宽度0 016位0 132位1 0 8位1 1未定义66 EECK I 时钟信号67 EECS I/O 片选也做LED模式选择引脚高电平时,LED 模式1,否则模式0注意:EECS EECK EEDO引脚都内部自带60K欧姆下拉电阻时钟引脚21 X2_25M O 25M晶振输出22 X1_25M I 25M晶振输入59 CLK20MO O 20M晶振再生输出给外部介质无关设备,自带60K欧姆下拉电阻LED引脚60 SPEED100#O低电平指示100M带宽指示,高电平指示10M带宽61 DUP# O 全双工指示LEDLED模式0时,低电平显示工作在10M带宽,或在100M带宽浮动62LINK&ACT#O连接LED,在模式0时,只作物理层的载波监听检测连接状态10/100 物理层与光纤接口24 SD I 光纤信号检测PECL 电平信号,显示光纤接收是否有效25 DGGND P 带隙地信号线26 BGRES I/O 带隙引脚27 AVDD P 带隙与电源保护环28 AVDD P 接收端口电源29 RXI+ I 物理层接收端的正极30 RXI- I 物理层接收端的负极31 AGND P 接收端口地32 AGND P 发送端口地33 TXO+ O 物理层发送端口正极34 TXO- O 发送端口负极35 AVDD P 物理层发送端口负极各种其他功能引脚16~19 TEST1~4 I 工作模式Test1~4(1, 1,0,0)正常工作状态48 TEST5 I 必须接地68~69 GPIO0~3 I/O 通用I/O端口通用端口控制寄存器和通用端口寄存器能编程该系列引脚GPIO0默认输出为高来关闭物理层和其他外部介质无关器件GPIO1~3默认为输入引脚78 LINK_O O 电缆连接状态显示输出,高电平有效79 WAKEUP O 流出一个唤醒信号当唤醒事件发生内置60K欧姆的下拉电阻80 PW_RST#I上电复位低电平激活DM9000的重新初始化,5us后初始化当该引脚测试到电平变化74,75,77NC 无用电源引脚5,20,36,55,72,90,73DVDD P 数字电源15,23,42,5863,81,99,76DGND P 数字地内部寄存器DM9000(A)包含一系列可被访问的控制状态寄存器,这些寄存器是字节对齐的,他们在硬件或软件复位时被设置成初始值。

以下为DM9000的寄存器功能详解:NCR (00H):网络控制寄存器(Network Control Register )7:EXT_PHY:1选择外部PHY,0选择内部PHY,不受软件复位影响。

6:WAKEEN:事件唤醒使能,1使能,0禁止并清除事件唤醒状态,不受软件复位影响。

5:保留。

4:FCOL:1强制冲突模式,用于用户测试。

3:FDX:全双工模式。

内部PHY模式下只读,外部PHY下可读写。

2-1:LBK:回环模式(Loopback)00通常,01MAC内部回环,10内部PHY 10 0M模式数字回环,11保留。

0:RST:1软件复位,10us后自动清零。

NSR (01H):网络状态寄存器(Network Status Register )7:SPEED:媒介速度,在内部PHY模式下,0为100Mbps,1为10Mbps。

当L INKST=0时,此位不用。

6:LINKST:连接状态,在内部PHY模式下,0为连接失败,1为已连接。

5:WAKEST:唤醒事件状态。

读取或写1将清零该位。

不受软件复位影响。

4:保留。

3:TX2END:TX(发送)数据包2完成标志,读取或写1将清零该位。

数据包指针2传输完成。

2:TX2END:TX(发送)数据包1完成标志,读取或写1将清零该位。

数据包指针1传输完成。

1:RXOV:RX(接收)FIFO(先进先出缓存)溢出标志。

0:保留。

TCR(02H):发送控制寄存器(TX Control Register)7:保留。

6:TJDIS:Jabber传输使能。

1使能Jabber传输定时器(2048字节),0禁止。

注释:Jabber是一个有CRC错误的长帧(大于1518byte而小于6000byte)或是数据包重组错误。

原因:它可能导致网络丢包。

多是由于作站有硬件或软件错误。

5:EXCECM:额外冲突模式控制。

0当额外的冲突计数多于15则终止本次数据包,1始终尝试发发送本次数据包。

4:PAD_DIS2:禁止为数据包指针2添加PAD。

3:CRC_DIS2:禁止为数据包指针2添加CRC校验。

2:PAD_DIS2:禁止为数据包指针1添加PAD。

1:CRC_DIS2:禁止为数据包指针1添加CRC校验。

0:TXREQ:TX(发送)请求。

发送完成后自动清零该位。

TSR_I(03H):数据包指针1的发送状态寄存器1(TX Status Register I)7:TJTO:Jabber传输超时。

该位置位表示由于多于2048字节数据被传输而导致数据帧被截掉。

6:LC:载波信号丢失。

该位置位表示在帧传输时发生红载波信号丢失。

在内部回环模式下该位无效。

5:NC:无载波信号。

该位置位表示在帧传输时无载波信号。

在内部回环模式下该位无效。

4:LC:冲突延迟。

该位置位表示在64字节的冲突窗口后又发生冲突。

3:COL:数据包冲突。

该位置位表示传输过程中发生冲突。

2:EC:额外冲突。

该位置位表示由于发生了第16次冲突(即额外冲突)后,传送被终止。

1-0:保留。

TSR_II(04H):数据包指针2的发送状态寄存器2(TX Status Register II)同TSR_I略。

RCR(05H):接收控制寄存器(RX Control Register )7:保留。

6:WTDIS:看门狗定时器禁止。

1禁止,0使能。

5:DIS_LONG:丢弃长数据包。

1为丢弃数据包长度超过1522字节的数据包。

4:DIS_CRC:丢弃CRC校验错误的数据包。

3:ALL:忽略所有多点传送。

2:RUNT:忽略不完整的数据包。

1:PRMSC:混杂模式(Promiscuous Mode)0:RXEN:接收使能。

RSR(06H):接收状态寄存器(RX Status Register )7:RF:不完整数据帧。

该位置位表示接收到小于64字节的帧。

6:MF:多点传送帧。

该位置位表示接收到帧包含多点传送地址。

5:LCS:冲突延迟。

该位置位表示在帧接收过程中发生冲突延迟。

4:RWTO:接收看门狗定时溢出。

该位置位表示接收到大于2048字节数据帧。

3:PLE:物理层错误。

该位置位表示在帧接收过程中发生物理层错误。

2:AE:对齐错误(Alignment)。

该位置位表示接收到的帧结尾处不是字节对齐,即不是以字节为边界对齐。