电子科大微嵌(ppt)

电子科技大学《微电子器件》课件PPT微电子器件(3-10)

CTE↓

① ②

AE↓ ( NB↓(

l↓, s↓ ) 但会使

rbb’↑,VA↓)

要使 b↓,应: (1) WB↓( 但会使 rbb’↑,VA↓,且受工艺限制)

(2) η↑ ( 采用平面工艺 )

要使 d↓,应:xdc↓ →NC↑( 但会使 BVCBO↓, CTC↑)

要使 c↓,应:

(1) rcs↓

① ② ③

fT

rbb fT Le

2

CTC

3.10.3 高频晶体管的结构

由

M

fT

8 rbbCTC

可知,要提高 M ,应提高 fT ,降低 rbb’

和 CTC,因此应该采用由平面工艺制成的硅 NPN 管,并采用细

线条的多基极条和多发射极条结构。

l B E B E B ….…

S

提高 M 的各项具体措施及其副作用

除以上主要矛盾外,还存在一些相对次要的其它矛盾,在 进行高频晶体管的设计时需权衡利弊后做折衷考虑。

3.11 双极晶体管的开关特性

(自学)

3.12 SPICE 中的双极晶体管模型

(自学)

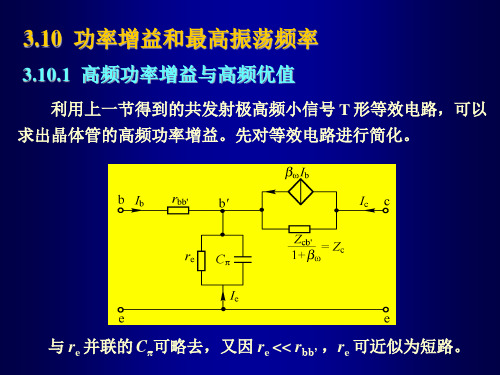

3.10 功率增益和最高振荡频率

3.10.1 高频功率增益与高频优值

利用上一节得到的共发射极高频小信号 T 形等效电路,可以 求出晶体管的高频功率增益。先对等效电路进行简化。

与 re 并联的 Cπ可略去,又因 re << rbb’ ,re 可近似为短路。

再来简化

Zc

Zcb

1 ω

,

1 Zcb

1 rμ

(3) 对 NC 的要求

减小 d 及 rcs 与减小 CTC及提高 BVCBO 对 NC 有矛盾的要求。

这可通过在重掺杂 N+ 衬底上生长一层轻掺杂 N- 外延层来缓解。 外延层厚度与衬底厚度的典型值分别为 10 m 与 200 m 。

西安电子科技大学嵌入式实时操作系统第10章PPT课件

语言 汇编 汇编 ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C

复杂度 高 高 高 低 低 低 低 低 低 低 低 低

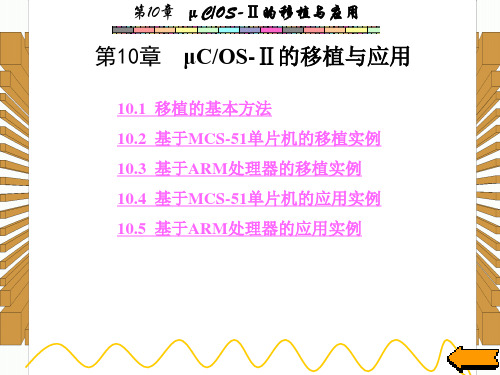

第10章 μC/OS-Ⅱ的移植与应用

移植所要进行的工作可以简单地归纳为如下几条: (1) 声明11个数据类型(OS_CPU.H); (2) 用#define声明4个宏(OS_CPU.H); (3) 用C语言编写10个简单的函数(OS_CPU_C.C); (4) 编写4个汇编语言函数(OS_CPU_A.ASM)。 根据处理器的不同,一个移植实例可能需要编写或改写 50~300行的代码,需要的时间从几个小时到一星期不等。 移植完毕后还要进行测试。

语言 ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C ANSI C

汇编 汇编

复杂度 低 低 低 低 低 低 低 低 低 中 中 高 低 高 高 高 高

第10章 μC/OS-Ⅱ的移植与应用

第10章 μC/OS-Ⅱ的移植与应用

4. INCLUDES.H文件说明 INCLUDES.H是一个主头文件,它包括了所有的头文件, 这样做的好处是使得在应用中无需考虑每个 .C文件到底需 要哪些头文件,还可大大地提高代码的可移植性。唯一的缺 点是它可能会包含一些不相关的头文件,因此可能增加每个 文件的编译时间。一般地,该文件应该包含在所有 .C文件 的第一行,即# include “includes.h”。 10.1.2 OS_CPU.H代码的移植 OS_CPU.H头文件中包含了与编译器有关的数据类型和 与处理器有关的代码,具体如程序清单10.1所示。

电子科大微机电系统(MEMS)概论课件第一章.

电⼦科⼤微机电系统(MEMS)概论课件第⼀章.MEMS & Microsystems—Design andManufacture机械电⼦⼯程学院研究⽣专业课程教材刘晓明,朱钟淦著.《微机电系统设计与制造》国防⼯业出版社,2006参考书籍[美] 徐泰然著,王晓浩等译. MEMS和微系统-设计与制造. 机械⼯业出版社,2003[德]W.Menz著,王春海等译. 微系统技术. 化学⼯业出版社,2003[美]Michael Quirk & Julian Serda著,韩郑⽣等译.半导体制造技术. 电⼦⼯业出版社,2003课程安排课时——40 学时上课安排——第1周-第11周周⼆/ 7-8节,B 208周四/ 3-4节,B 201考试⽅式——闭卷考分⽐例——期末考试60%不设中期考试平时讨论、⼤作业与出勤40%授课内容ü微机电系统(MEMS概论(2 hoursüMEMS的理论基础知识(6 hours ü集成电路基本制造技术(8 hoursüMEMS的制造技术(6 hoursü微传感器(8 hoursü微执⾏器(6 hoursüMEMS的封装与检测(4 hours概论第⼀章微机电系统(MEMS 概论内容提要üMEMS 的基本概念,与宏观机电系统的对⽐特征üMEMS 技术的发展过程与⼤致技术现状üMEMS 典型产品的应⽤⼀、MEMS 的形成与发展1、MEMS 的形成基础机械电⼦学——机械学、电⼦学、计算机技术交叉MEMS ——机/电/磁/光/声/热/液/⽓/⽣/化等多学科交叉学科交叉的产物MEMS传热学⼒学电/磁学光学化学⽣物学量⼦⼒学声学流体⼀、MEMS的形成与发展1、MEMS的形成基础与机械电⼦学的关系基本组成相同不是简单的提升定⼦转⼦扭矩传递齿轮LIGA⼯艺⽣成的微马达MEMS系统框图MEMS的组成要素:微型传感器、微执⾏器、信号处理控制电路、通信系统、微电⼦电源2、MEMS的特点MEMS的定义America——它是由电⼦和机械元件组成的集成微器件、微系统,它是采⽤与集成电路(IC兼容的⼯艺制造的,可批量⽣产。

西安电子科技大学嵌入式实时操作系统第7章PPT课件

2. 源代码 OSSemCreate()函数的源代码如程序清单7.1所示。 OSSemCreate()函数返回之前的ECB数据结构如图7.2所示。

第7章 信号量与互斥信号量

程序清单7.1 OSSemCreate()函数的源代码

说明 该常量为 0 时,屏蔽所有信号量函数

信号量必然包含这三个函数,所以它们没有 单独的配置开关量

第7章 信号量与互斥信号量

6. 任务、中断服务子程序与信号量之间的关系 任务、中断服务子程序与信号量之间的关系如图7.1所 示,其中用钥匙或者旗帜符号来表示信号量,具体说明如下: (1) 如果信号量用于对共享资源的访问,那么信号量就 用钥匙符号。符号旁边的数字N代表可用资源数,对于二值 信号量,该值就是1。

第7章 信号量与互斥信号量

表7.1 信号量管理函数一览表

函数 OSSemCreate() OSSemPend() OSSemPost() OSSemAccept() OSSemDel() OSSemQuery()

功能 建立信号量 等待信号量 发送信号量 无等待地请求信号量 删除信号量 查询信号量的当前状态

*/

第7章 信号量与互斥信号量

return((OS_EVENT*)0);

/*若是,则返回空

指针

*/

}

OS_ENTER_CRITICAL();

/*关中断

*/

pevent = OSEventFreeList;

/*从空余

ECB链表中获得一个事件控制块 */

if (OSEventFreeList != (OS_EVENT *)0) { /*确保ECB

电子科技大学嵌入式软件工程中心ppt课件

嵌入式软件开发工具的分类

• 从以上嵌入式软件开发分类来看,嵌入式 软件开发工具可以分为:

–与嵌入式OS相关的开发工具,用于开发:

• 基于嵌入式OS的应用 • 部分驱动程序等

–与嵌入式OS无关的开发工具,用于开发:

• 基本的驱动程序 • 辅助硬件调试程序 • 系统软件等

运行平台Target

目标机应用系统

调 试

— 应用软件

代 — 应用中间件

理 — 目标机OS

目标机硬件

开发平台Host

宿主机开发环境

运 行

— 编辑 — 编译

库

— 连接

— 调试

宿主机 OS

宿主机硬件

交叉开发环境

电子科技大学嵌入式软件工程中心

嵌入式软件的交叉开发环境

• 宿主机(Host) :是用于开发嵌入式系统的计算 机。一般为PC机(或者工作站),具备丰富的软 硬件资源,为嵌入式软件的开发提供全过程支持。

–调试器通过某种方式能控制目标机上被调试程 序的运行方式

–通过调试器能查看和修改目标机上的内存、寄 存器以及被调试程序中的变量等

电子科技大学嵌入式软件工程中心

交叉调试

非交叉调试

调试器和被调试程序运行在不同 调试器和被调试程序运行在同一

的计算机上

台计算机上

可独立运行,无需操作系统支持

需要操作系统的支持

嵌入式系统及应用

电子科技大学嵌入式软件工程中心

第九章 嵌入式系统软件的开发

电子科技大学嵌入式软件工程中心

主要内容

• 嵌入式软件开发工具 • 嵌入式系统开发模式 • 实时软件分析设计方法

电子科技大学嵌入式软件工程中心

第一节

电子科技大学《微电子器件》课件PPT(3-5)

M

1

1

BVCEO VB

S

1

BVCEO

VB S 1

S

VB

1

BVCBO

S

即

BVCEO

BVCBOS例3. Nhomakorabea 与例 3.1中的晶体管相同, 32.5,S 4。

当BVCBO

100V时,BVCEO

100 4 32.5

42

V

ICEO ~ VCE 曲线中经常 会出现一段 负阻区。图中,

VSUS 称为维持电压。

ICBO 1R

ICS

ICS

I CEO

1 R 1

I CS

如果基区足够长,以至于两个 PN 结之间没有耦合作用,即

R 0

则 3 个电流的大小相同,都等于单个集电结的反向饱和电流。

3.5.2 共基极接法中的雪崩击穿电压

已知 PN 结的雪崩倍增因子 M 可以表示为

1

M 1

xd 0

i

dx

在工程实际中常用下面的经验公式来表示当 已知击穿电压

IC M IE M ICBO AIE ICBO 式中, A M, ICBO M ICBO ,分别代表计入雪崩倍增

效应后的共基极电流放大系数与反向截止电流。

例 3.1 某硅NPN管的 0.98 , 0.99 ,则 0.9702,取 S 4 。

当 VBC

0.4VB 时,M

1 1 (0.4)4

N+ P

E B

ICS N

C

VBC

(3) ICBO :VBC < 0 、IE = 0 时的 IC , ICBO 1R ICS

在共基极电路放大区中,IC IE ICBO

N+ P

电子科技大学,嵌入式系统设计嵌入式系统及应用-Chapter-.ppt

中间件层

嵌入式 CORBA

TCP/IP 网络系统

嵌入式 JAVA

文件 系统

内核

嵌入式 DCOM

面向应用领域 的中间件

操作系统层

电源 管理 嵌入式 GUI

驱动层

板级 FLASH RTC/定 初始化 驱动 时器驱动 串口 驱动 以太网 驱动 LCD 驱动 键盘 驱动 其他 驱动

硬件

电子科技大学嵌入式软件工程中心

嵌入式软件系统的分类

系统软件

控制、管理计算 机系统的资源

嵌 入 式 软 件

嵌入式操作系统 嵌入式中间件(CORBA、 Java) 等等 系统分析设计工具 仿真开发工具 交叉开发工具 测试工具 配置管理工具 维护工具等 手机软件 路由器软件 交换机软件 飞控软件等

支撑软件

辅助软件开发的 工具

应用软件

面向应用领域

电子科技大学嵌入式软件工程中心

嵌入式软件系统的分类

•

从运行平台来分,嵌入式软件可以分为

–

运行在开发平台上的软件 :设计、开发、测试 工具等。

–

运行在嵌入式系统上的软件:嵌入式操作系统、 应用程序、驱动程序及部分开发工具。

电子科技大学嵌入式软件工程中心

嵌入式软件系统的体系结构

应用层

应用 任务1 应用 任务2 …… 应用 任务n

•

发常常涉及其它领域的专门知识,这对软件工程师 非常高,风险也大。现在软件的开销已大大超过了 许多软件的开发和运行涉及机构、体制和管理方式等问题, 提出了很高的要求。 硬件的开销。

还会涉及到人们的观念和心理。这些人的因素,常常成 电子科技大学嵌入式软件工程中心 为软件开发的困难所在,直接影响到项目的成败。

引导/升级系统

电子科大嵌入式系统课件 Software Design of ESS

Problems appeared in the system design

➢ How to acquire the detailed function and performance requirements step by step?

➢ How to utilize the excellent points of UML & DARTS to design an ESS?

Real-Time Systems Lab

LIAO Yong

12

5 Development tools for ESS

University of Electronic Science & Technology of China (UESTC)

Real-Time Systems Lab

LIAO Yong

6

2 How to embark on designing and analyzing a ESS ?

University of Electronic Science & Technology of China (UESTC)

What’s the difference between developing an application

Problems appeared in the system design

➢ How to Decompose the system into concurrent tasks, according to the requirement analysis ?

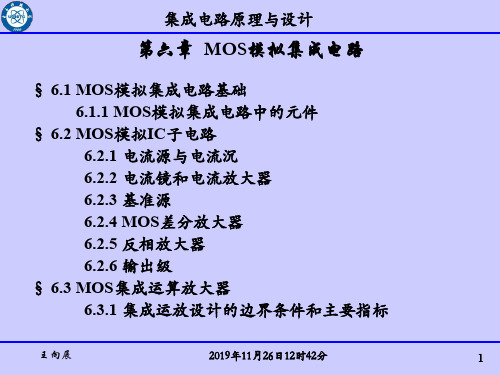

电子科大微固学院专业课集成电路原理与设计课件第六章——考研专业

工作,应使T管工作在饱和 区,即:

王向展

图6.3 基本的电流源结构与I-V特性示意

2019年11月26日12时42分

10

集成电路原理与设计

VDS VGS VT

Vout VSS VDD VGG VDD Vthp Vout VSS VGG Vthp Vout VGG Vthp VSS

1、简单的电压分压器

VREF

VDD

R2 R1 R2

VREF对VDD的灵敏度:

VREF

S

VREF

VREF

VREF VDD

1

VDD

VDD VDD

(6.13)

在近似处理时,应注意此电流镜正常工作时,各管均处于

饱和区,gds远小于gm,gmro >>1。 电路实际工作时,要在输入端、输出端加一定电压才能工

作。在T3饱和的前提下,为使Vi时Ir一定,只有相应地使W3/L3、 W2/L2增大。一般V(min)>2Vth。另一方面,要保证T3饱和,对输 出端电压也有要求:

VDS

2 FB VSB

分析小信号模型等效电路,由(6.6)、(6.7)得:

Rout

Vout I out

r ro2 [( gm2 gmb2 ) ro2 ] r

gm2 ro2 r

可见,最终输出电阻增大为r的gm2ro2倍。

王向展

2019年11月26日12时42分

集成电路原理与设计

第六章 MOS模拟集成电路

§ 6.1 MOS模拟集成电路基础 6.1.1 MOS模拟集成电路中的元件

电子科大微电子工艺(第十章)装配与封装ppt课件

. 减薄到5um的硅片

二、分片

Wafer 台

锯刃

硅片锯和. 被划硅片

三、装架

引线框架

引线

芯片

塑料 DIP

装片用的典. 型引线框架

环氧树脂粘贴:散热加银粉的导热树脂 共晶焊粘贴:散热更好 玻璃焊料粘贴:密封好

.

四、引线键合

芯片表面的压点和引线框架上或基座上的电极内 端电连接的方法。

Die 键合的引线

压点

压模混合物 引线框架

管脚尖

从芯片压焊点. 引线框架的键合

热压键合 超声键合 热超声球键合

几种常用键合引线特性比较

.

钩

Post Device

在测试中的芯片 样品卡

引线键合质量测试:目检和拉力测试。

.

10.3 先进的装配与封装

倒装芯片---Flip chip 球栅阵列---Ball grid array (BGA) 板上芯片---Chip on board (COB) 卷带式自动键合Tape automated bonding (TAB) 多芯片模块---Multichip modules (MCM) 芯片尺寸封装---Chip scale packaging (CSP) 圆片级封装---Wafer-level packaging

硅片测试和拣选

分片

贴片

引线键合

塑料封装

.

最终封装与测试

二、封装技术发展历程

.

三、封装的分类

二维与三维 构造 引脚插入型与表面贴装型

单边、双边、四边与底部引脚

微

金属封装

电

子 封

资料 陶瓷封装

装

塑料封装

气密性封装

性能

非气密性封装

西安电子科技大学嵌入式实时操作系统课件 第1章

第1章 嵌入式系统导论

1.1.2 嵌入式系统的定义

嵌入式计算机系统简称嵌入式系统,它的应用发源于微 机,发展于单片机。那么,究竟什么是嵌入式系统呢?嵌入 式系统的定义是怎样的呢? 依据IEEE(国际电气和电子工程师协会)的定义: “Device used to control, monitor, or assist the operation of equipment, machinery or plants”,即嵌入式系统为控制、监 视或辅助设备、机器甚至工厂运作的装置。它是一种计算机 软件和硬件的综合体,特别强调“量身定制”的原则,也就 是基于某种特殊的用途,设计者就会根据这些用途设计出一 种截然不同的系统来。

在理解嵌入式系统的定义的时候,要分清嵌入式系统与

嵌入式应用系统的区别。嵌入式应用系统是指内部含有嵌入 式系统的设备、装置或者系统,例如手机、数字彩电、空调、 工控单元、PDA、汽车、导弹等。这种区别就好像我们常说 的单片机系统与单片机应用系统的区别一样。尽管人们常常 在不严格的场合将单片机系统和单片机应用系统混称,但是 概念上的差别是很明显的。

第1章 嵌入式系统导论

按照定义,只要满足嵌入式系统三要素的,都可以称为

嵌入式系统。因此,嵌入式系统根据其形态和规模的不同可 分为: (1) 系统级,包括工控机、嵌入到应用系统中的通用计 算机等; (2) 板级,包括各种CPU主板; (3) 芯片级,如CPU、MCU、SOC、DSP、MPU等。

第1章 嵌入式系统导论

第1章 嵌入式系统导论

Wayne Wolf在其所著的嵌入式系统设计教科书上对嵌

入式系统的定义是:“Loosely defined, it is any device that includes a programmable computer but is not itself a generalpurpose computer”,即不严格地定义,嵌入式系统是包含可 编程计算机的任意设备,而它本身并不是被作为通用计算机 而设计的。书中他还说:“一台个人电脑不能称之为嵌入式 计算系统,尽管它常常被用于搭建嵌入式系统。”

电子科技大学《微电子器件》课件PPT微电子器件(4-4)

由

I Dsat

2

VGS VT

2 可知 ,

IDsat 与 VGS 为线性关系。

测量 MOSFET 在饱和区的 IDsat ~ VGS 关系并绘成直线,其在

横轴上的截距即为 VT ,如下图所示,

I Dsat

I Dsat 2 I Dsat 1

0

斜率 2

VT VGS1VGS2

VGS

3、 1 A 法 类似于测量 PN 结的正向导通电压 VF 或击穿电压 VB ,将 漏极电流达到某一规定值 IDT 时的 VGS 作为阈电压 VT 。

4.4 MOSFET 的亚阈区导电

本节以前的漏极电流公式只适用于 VGS > VT ,并假设当 VGS < VT 时 ID = 0 。但实际上当 VGS < VT 时,MOSFET 仍能 微弱导电,这称为 亚阈区导电。这时的漏极电流称为亚阈电 流,记为 IDsub 。

定义:使硅表面处于本征状态的 VGS 称为 本征电压 ,记为

中,得

I Dsub

Z L

qDn

kT q

CD (S)

qNA

np0

exp

qS

kT

1

exp

qVDS kT

Z L

n

CD

(S

)

kT q

2

exp

2qFP

kT

exp

qS

kT

1

exp

(S )

kT q

2

exp

西安电子科技大学嵌入式实时操作系统课件 第11章

第11章 μC/OS-Ⅱ几个版本的区别

11.3 μC/OS-ⅡV2.76与V2.83的区别

V2.76与V2.83之间主要有如下区别: (1) V2.83在用户的工程里增加了APP_CFG .H文件, 用于标明任务的优先级、堆栈长度以及其它与应用程序相关 的配置等信息。

(2) V2.83在用户的工程中增加了OS_TMR.C文件,用

关信息,方便调试。然而,如果OS_TIME_TICK_ HOOK_EN被设置为1,则函数OSTimeTickHook()仍按照标 准的时钟频率执行。

第11章 μC/OS-Ⅱ几个版本的区别

(10) V2.62增加了配置常量OS_TIME_TICK_HOOK_

EN。通常,μC/OS-Ⅱ在时钟中断代码内总会调用函数 OSTimeTickHook(),而需要用到时钟中断而又不需要做其 它操作时,可置OS_TIME_TICK_HOOK_EN = 0,系统编 译时就会省略这段函数代码。 (11) V2.62在μC/OS_Ⅱ.H文件中增加了一个声明 “extern C”,从而使得用户可以用C++编译器来编译μC/OSⅡ。 (12) 一些对系统功能没有影响的代码的改写和删减这里 不再赘述。

第11章 μC/OS-Ⅱ几个版本的区别

(8) V2.62增加了配置常量OS_TASK_SW_HOOK_EN。

通常,μC/OS-Ⅱ都需要编译任务切换扩展函数OSTask SwHook(),而当任务切换且不需要做其它操作时,可置 OS_TASK_SW_HOOK_EN = 0,系统编译时就会省略这段 函数代码。

第11章 μC/OS-Ⅱ几个版本的区别

在中断或应用程序中,通过调用OSTmrSignal()函数以

OS_TMR_CFG_TICK_RATE定义的频率发送已封装好的信 号量OSTmrSemSignal。OSTmrTask()永远等待这个信号量, 当其被发送后,OSTmrTask()再获得另外一个二进制信号量 OSTmrSem,就可以按应用程序中定义的定时器的数据结构 对定时器进行数据更新。 (4) V2.83在μC/OS_Ⅱ.H文件中包含了APP_CFG .H、 OS_CPU .H和OS_CFG .H,这使得用户不需要其它库函数 就能编译μC/OS-Ⅱ。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

不同的存储原理

双极型: 存取速度快,但集成度低,一般用于大 型计算机或高速微机的Cache;

半导体 存储器

易失性 存储器

非易失性 存储器

静态SRAM 速度较快,集成度较低,

MOS型

一般用于对速度要求高、 而容量不大的场合(Cache

) 动态DRAM 集成度较高但存取速度较

低,一般用于需较大容量

掩膜ROM

AB 低位AB

DB

RD/WR

地址 片选控制

译码

主

存

地址锁存

储

数据缓冲

器

一、数据线:如果考虑总线负载问题,可加接数据收发器。

二、读写控制线:考虑有效电平。

三、地址线:字选+片选。

字选:系统地址总线中的低位地址线直接与各存储芯片的地址线连接 。 所需低位地址线的数目N与存储芯片容量L的关系:L=2N。 片选:系统地址总线中余下的高位地址线经译码后用做不同存储芯片

7

M×N)直接相关:

所以,6264容量: 213×8=8K×8

2. 控制信号应包括:片 选信号和读/写信号

14/42

可编程只读存储器PROM

存储单元多采用熔丝-低 熔点金属或多晶硅。写入时 设法在熔丝上通入较大的电 流将熔丝烧断。

产品出厂时存的全是1,用 户可一次性写入,即把某些 1改为0。但只能一次编程。

作业:1,2,10~17 1(9~10)不做

思考:3 ~9

第五章结束

自自动动化化工工程程学学院院

测测试试技技术术及及仪仪器器研研究究所所

肖肖寅寅东东

EE-T-mTEmaELiaELl:iE:l::xyx0dy02ad28ra8-cr-6hc61ehr1e8@r83@31u13eu30sets03ct3.ce.dedu.uc.ncn

的场合(主存)。

一次性可编程PROM

紫外线可擦除EPROM

电可擦除E2PROM

快闪存储器FLASH

磁介质存储器 磁带、软磁盘、硬磁盘( DA、RAID) 光介质存储器 只读型、一次写入型、多次写入型

不同的读写策略

一.数据访问方式

– 并行存储器 (Parallel Memory) – 串行存储器 (Serial Memory)

T5

T3

C

A

T1

+5V

T4

B T2

1. T1和T2组成一个双稳态 触发器,用于保存数据 。T3和T4为负载管。

T6

D

2. 如A点为数据D,则B点 为数据/D。

3. 行选择线有效(高电 平 )时,A 、B处的数据信 息通过门控管T5和T6送 至C、D点。

T7

列选择线

T8

I/O

集成度低,但速度快,价格高, 常用做Cache。

4. 列选择线有效(高电 平 )时,C 、D处的数据

I/O 信息通过门控管T7和T8 送至芯片的数据引脚I/O 。

动态RAM的单管基本存储单元

行选择线 B

刷新放大器

T1 A

存储 电容

C

列选

T2

择线

I/O

集成度高,但速度较慢,价 格低,一般用作主存。

1. 电容上存有电荷时,表示存储 数据A为逻辑1;

电子科大微嵌演示文稿

优选电子科大微嵌

练习:分析图中74LS138各输出端的译码 地址范围。

A3 A4 A5 +5V A6 A7 A8 A9 AEN IOR IOW

0 0 0 1 0

&

218

AH

Y0

B

Y1

C

Y2

G1 Y3

Y4

G2A Y5

Y6

&

G2B Y7

74LS138 3-8译码器

端口译码电路

第五章 习题

的片选。通常IO//M信号也参与片选译码。

11/42

RAM芯片的组成与结构(一)

地址线

存储芯片容量标为“M*N”(bit)

数据线

a0

D0 0,0 D0

……

DN-1 0,N-1 DN-1

A0 A1

地

地 a1

址址

位 线

字线0 位 线

… AL-1

寄译 存 …码

…

器

器 aM-1

0

M-1,0

… ……

N-1

M-1,N-1

2. 行选择线有效时,数据通过 T1送至B处;

3. 列选择线有效时,数据通过 T2送至芯片的数据引脚I/O;

4. 为防止存储电容C放电导致数 据丢失,必须定时进行刷新;

5. 动态刷新时行选择线有效,而 列选择线无效。(刷新是逐行 进行的。)

内存储器与并行总线的接口

微处 理器

或 总线 接口

IO//M 高位AB

二.数据存取顺序

1. 随机存取(直接存取) 可按地址随机访问; 访问时间与地址无关;

– 顺序存取 (先进先出) FIFO、队列(queue)

– 堆栈存储 先进后出(FILO)/后进先出(LIFO); 向下生成和向上生成; 实栈顶SS、堆栈指针SP;

堆栈的生成方式

静态RAM的六管基本存储单元

行选择线

)

D0

控制线

读写控制

1. 该RAM芯片外部共有地址线 2n 根,数据线 1 根;

2. 该类芯片内部一般采用双译码(复合译码、重合选择)方式,基本存储单 元排列成N*N 的正方矩阵,且有M =22n =N2 的关系成立;

静态RAM芯片的引脚特性

从三总线的角度看:

1. 地址线数目A、数据

线数目D与芯片容量(

15 /54

紫外线可擦除ROM (UVEPROM)

浮栅上电荷可长期保存 在 125℃ 环 境 温 度 下 , 70% 的电荷能保存10年以上。

擦除:用紫外线或X射线 擦除。需20~30分钟。

缺点:需要两个MOS管; 编程电压偏高;P沟道管的 开关速度低。

引入浮栅的MOS器件

电可擦除的ROM(EEPROM)

字线M-1

…

d0 数 ( d1 据 三

缓态 … 冲双 dN-1 器 向

)

D0 D1

… DN-1

读写控制逻辑

R/W CE

控制线

1. 该RAM芯片外部共有地址线 L 根,数据线 N 根;

2. 该类芯片内部采用单译码(字译码)方式,基本存储单元排列成M*N的 长方矩阵,且有M=2L的关系成立;

RAM芯片的组成与结构(二)

特点:擦除和写入均利用隧道效应。 浮栅与漏区间的氧化物层极薄(20纳米以下) ,称为隧道区。当隧道区电场大于107V/cm时隧 道区双向导通。

读出

擦除(写1)

写入(写0)

快闪存储器(Flash Memory)

(1)写入利用雪崩注入法 。源极接地;漏极接6V;控 制栅12V脉冲,宽10 s。

存储芯片容量标为“M*1”(bit)

A0 A1

… An-1

X

X X0

地 地 X1

址址

寄 存

…

译 码

…

器

器 XN-1

地址线

D0 0,0 D0

DN-1 0,N-1 DN-1

…

…

N-1,0

…

N-1,N-1

Y0

…

YN-1

Y地址译码器

…

Y地址寄存器

… An An+1

A2n-1

数据线

数(

D

据三 缓态

D 冲双

器向