存储器测试

存储器测试原理

存储器测试原理

存储器测试是一种用于检验计算机存储器功能和可靠性的方法。

在存储器测试中,通常会对存储器进行读写操作,并通过比较存储器接收和输出的数据来检测是否存在错误。

存储器测试的原理包括以下几个方面:

1. 写入测试:将特定的数据写入存储器的单元中,然后读取并比较存储器输出的数据与原始数据是否一致。

如果一致,则表示存储器单元正常。

2. 读取测试:在存储器的单元中预先写入一些数据,然后从存储器中读取并比较输出的数据是否与预期结果一致。

如果一致,则表示存储器单元正常。

3. 位翻转测试:将存储器中某一个或多个特定位的数据进行翻转,然后读取并比较输出的数据。

如果输出与输入相反,则表示存储器单元对于位翻转具有正确的反应。

4. 重复拷贝测试:将一段特定的数据重复拷贝到存储器的不同单元中,并逐一读取并比较输出的数据。

如果每个单元的输出结果都正确,则表示存储器正常。

5. 边界测试:在存储器的边界处,即首地址和末地址处写入特定的数据,然后读取并比较输出的数据。

如果输出结果正确,则表示存储器对边界情况具有正确的处理能力。

以上是存储器测试的一些基本原理,通过这些原理可以检测存储器中的错误,并保证存储器能够正常工作。

存储器测试通常通过软件或硬件工具进行,以确保计算机系统能够正常运行并提供准确的数据存储和读取功能。

存储器测试方法、设备及系统与流程

存储器测试方法、设备及系统与流程随着计算机技术的不断发展,计算机存储器的容量和性能越来越高,但存储器出现故障的概率并不会因此降低。

因此,为了保障计算机的正常运行,存储器的测试工作显得尤为重要。

本篇文章将详细介绍存储器测试方法、设备及系统与流程。

一、存储器测试方法:1、慢速测试法慢速测试是通过使用单元测试的方法来测试存储器中的每一个单元。

测试程序可以在存储器中对每个字节进行写入和读取,然后比较已读取的值与已写入的值是否相同,从而检测出存储器中是否存在故障。

2、快速测试法快速测试是在较短时间内对整个存储器进行测试。

测试程序将一组随机数据写入存储器,接着读取这些数据,然后再重新写入存储器。

最后再次读取存储器中数据,如果已读取的数据能够与写入的数据相匹配,就表明存储器无故障。

3、缺陷测试法缺陷测试是通过创建一些未写入正确值的未用存储器单元,从而测试出存储器中的故障。

测试程序将对存储器进行写入和读取操作,如果读取的数据与待读取的数据不同,就可以推断出存储器存在故障。

此方法需要测试时事先创建有缺陷的存储器单元。

二、存储器测试设备:1、存储器测试仪器存储器测试仪器主要用于检测存储器中是否存在故障,改善存储器的质量。

它主要由存储器测试板卡、测试软件、测试控制卡和测试工作站组成。

2、存储器测试芯片存储器测试芯片是一种专用的集成电路,用于测试 DRAM 和SRAM 存储器中的故障。

它可以与存储器芯片直接连接,进行数据交换,并根据测试程序对存储器单元进行写入和读取操作。

三、存储器测试系统与流程:1、存储器测试系统存储器测试系统主要由测试板卡、测试软件、测试控制卡和测试工作站组成。

测试软件由存储器测试程序和控制程序两部分组成,存储器测试程序用于测试存储器芯片,控制程序用于控制测试过程。

测试控制卡作为中间连接,负责存储器测试程序和工作站、测试板卡之间的数据传输。

2、存储器测试流程存储器测试流程包括以下几个步骤:(1)准备测试:将需要测试的存储器芯片连接至测试平台上,根据程序要求设置测试参数。

计算机内存测试题目及答案

计算机内存测试题目及答案1. 什么是计算机内存?答:计算机内存是一种用来存储程序、数据和操作结果的物理设备,也被称为主存或随机存取存储器(RAM)。

2. 什么是内存地址?答:内存地址是用来唯一标识内存中每个存储单元的数字。

3. 内存大小的单位是什么?答:内存大小的单位通常是字节(Byte),常见的内存容量单位还包括千字节(KB)、兆字节(MB)、千兆字节(GB)、和太字节(TB)。

4. 什么是内存读写速度?答:内存读写速度是指计算机从内存中读取数据或向内存写入数据时所需的时间。

5. 什么是内存的带宽?答:内存的带宽是指在一定时间内传输数据的能力,通常以每秒传输的位数来衡量,单位为兆字节每秒(MB/s)或千兆字节每秒(GB/s)。

6. 什么是内存的时序?答:内存的时序是指内存存取数据的时序规范,包括读写时序、时钟频率、延迟等参数。

7. 什么是内存的 ECC 功能?答:ECC(Error Correcting Code)功能是一种用于检测和纠正内存中的错误的技术,能够提高内存的可靠性。

8. 什么是内存的刷新?答:内存的刷新是指定时扫描内存,检查并修复储存数据中的错误。

9. 什么是内存的缓存?答:内存的缓存是一种高速缓存,用于暂存计算机最常用的数据和指令,以提高访问速度。

10. 什么是内存的双通道模式?答:内存的双通道模式是指计算机使用两个内存通道同时进行数据传输,以提高带宽和性能。

11. 什么是内存的频率?答:内存的频率是指内存模块运行的时钟速度,通常以兆赫兹(MHz)表示。

12. 什么是内存的延迟?答:内存的延迟是指访问内存所需的时间延迟,通常以CL值表示,值越低表示延迟越小。

13. 如何测试计算机的内存稳定性?答:可以使用内存测试软件(如MemTest86+)对计算机的内存进行稳定性测试,检测是否存在错误或故障。

14. 如何选择适合的内存模块?答:在选择内存模块时,需要考虑主板的支持情况、内存类型(如DDR3或DDR4)、内存容量和频率等因素。

存储器测试题

1、现有1024x 1的存储芯片,若用它组成16K X 8的存储器,试求:(1)实现该存储器所需的芯片数量;(2)若将这些芯片分装在若干块板上,每块板的容量为4K X 8,该存储器所需的地址线总位数是多少?其中几位用于选板?几位用于选片?几位用于选片内单元。

2、某存储器容量为16K X 8,用4K X 4的SRAM芯片组成,由R/W线控制读写,设计并画出该存储器的逻辑图,并注明地址分配、片选逻辑及片选信号的极性。

3、用容量为16K X 1的DRAM芯片组成64KB的存储器。

设存储器的读写周期为0.5卩s, CPU在1卩s内至少要访存一次,问哪种刷新方式比较合理?相邻两行之间的刷新间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少?4、现有2K X 1的ROM 4K X 1的RAM和8K X 1的ROM E种存储芯片,若用它们组成容量为16KB的存储器,前4KB为ROM后12KB为RAM(1)各种存储芯片分别用多少片?(2)正确选用译码器及门电路,并画出相应的逻辑结构图。

5、某计算机为定长指令字,指令字长为12位,每个地址码占3位,试提出一种分配方案,使该指令系统包含:4条三地址指令、8条二地址指令、180条单地址指令。

6、某计算机字长为16位,主存容量为64K字,采用单字长单地址指令格式,共有64条指令。

试说明:(1)若采用直接寻址,指令能访问多少主存单元?(2)为扩大寻址范围,采用直接/间接寻址,需要一位间址标志位,指令的寻址范围为多少?指令直接寻址的范围为多少?7、指令格式如下所示,OP为操作码字段,试分析指令格式特点。

31 26 21 18 17 16 15 0①所需芯片数=16K X 8 / 1K X 1 = 128 (片)②板块数=16K X 8 / 4K X 8 = 4 (块);板块上芯片数=4K X 8 / 1K X 1 = 32 (片),8并4串;地址线总数=炯16X 1024 = 炯214 = 14 (根)。

IC测试原理:存储器和逻辑芯片测试

目 的 :这是功能测试,地址解码测试和干扰 测试一个极好的向量。如果选择适当的时序,它还 可以很好地用于写入恢复测试。同时它也能很好地 用于读取时间测试。

其他的测试向量都类似于以上这些向量,都基 于相同的核心理念。

5 动态随机读取存储器(DRAM)

动态随机读取存储器(D R A M )的测试有以 下的一些特殊要求:

读取时间(Access time):通常是指在读使能, 芯片被选中或地址改变到输出端输出新数据的所需 的时间。读取时间取决于存取单元排列次序。

3 存储器芯片所需的功能测试

存储器芯片必须经过许多必要的测试以保证其 功能正确。这些测试主要用来确保芯片不包含以下 任何一种类型的错误:

存储单元短路 : 存储单元与电源或者地短路。 存储单元开路:存储单元在写入时状态不能改变。 相邻单元短路 :根据不同的生产工艺,相邻 的单元会被写入相同或相反的数据。 地址开路或短路 : 这种错误引起一个存储单 元对应多个地址或者多个地址对应一个存储单元。 这种错误不容易被检测,因为我们一次只能检查输 入地址所对应的输出响应,很难确定是哪一个物理 地址被真正读取。 存储单元干扰:它是指在写入或者读取一个存 储单元的时候可能会引起它相邻的存储单元状态的 改变,也就是状态被干扰了。

存储器的测试技术

存储器的测试技术Testing Techniques f or Memories王 健 李金凤 边福强 刘 欢(沈阳化工学院信息工程学院,辽宁沈阳110142)摘 要:集成电路工艺的改进使存储器的测试面临着更大的挑战。

本文从存储器的故障模型入手着重描述了单端口存储器,字存储器, 多端口存储器及存储器组的测试。

测试算法和测试策略要在测试时间,故障覆盖率,面积开支之间进行折衷。

关键词:存储器测试;功能故障模型;March算法;BIST 在一个包含嵌入式存储器,微处理器,DSP处理器及模拟电路的通用超大规模集成电路中嵌入式存储器是最难测试的电路。

测试存储器需要用大量的测试模式来激活存储器并将存储器的单元内容读出来与标准值进行比较。

测试通常采用B IST的结构,该结构不仅可以大大的降低昂贵的存储器测试仪的使用,同时又可以降低测试时间,包括测试控制器,地址产生器,数据产生器,数据比较器四个部分。

1 单端口存储器的测试2003年Zaid al-Ars和Ad J.van de G oor提出了一套较完备的单端口存储器的故障模型,它包含四部分:静态故障,动态故障,静态耦合故障,动态耦合故障。

存储器的测试通常采用March算法,常用的March算法包括MA TS++,March C-,March X,March Y,March B,March U,March G等。

SA ID HAMDIOU I提出动态故障的March RAW算法如图1所示,通过仿真试验可验证March RAW算法即可以测试静态故障又可以测试动态故障。

{ (w0); Θ(r0,w0,r0,r0,w1,r1);Θ(r1,w1,r1,r1,w0,r0); Τ(r0,w0,r0,r0,w1,r1);Τ(r1,w1,r1,r1,w0,r0); (r1)}图1 MAarch RAW算法2 字存储器测试存储器可分为位存储器和字存储器两种结构。

通常字存储器的测试采用反复的应用位存储器的测试算法来实现的,每次循环时改变数据背景。

内存储器部件实验报告

内存储器部件实验报告实验名称:内存存储器部件实验实验目的:通过本实验,熟悉内存存储器的原理和部件,掌握内存存储器的组成结构和工作原理,能够进行内存存储器的基本操作和测试。

实验器材:内存存储器、多媒体教学台、计算机、数据线实验原理:内存存储器是计算机中用于临时存储数据和程序的部件。

内存存储器的主要作用是为CPU提供数据和程序,并且数据的读写速度比硬盘快得多。

内存存储器的工作原理是通过将数据和程序存储在内存芯片中,CPU根据需要从内存中读取数据和程序,处理后再将结果写入内存。

实验内容:1.内存存储器的组成结构:内存存储器主要由存储单元、地址译码器、数据线和控制线等部件组成。

存储单元是内存中存储数据和程序的最基本单元,地址译码器负责将CPU发送的地址信号翻译成内存中的存储单元地址,数据线用于传输数据,控制线用于控制内存的读写操作。

2.内存存储器的工作原理:内存存储器的工作原理是通过地址信号和控制信号控制内存的读写操作。

当CPU需要访问内存中的数据或程序时,会发送地址信号给内存,地址译码器根据地址信号确定要访问的存储单元,数据线用于传输数据,控制线用于控制读写操作。

3.内存存储器的基本操作:内存存储器的基本操作包括读操作和写操作。

读操作是指CPU从内存中读取数据或程序到CPU中进行处理,写操作是指CPU将处理后的数据或程序写入内存中。

内存存储器的读写速度很快,可以满足CPU的数据读写需求。

实验步骤:1.将内存存储器安装在多媒体教学台上,并连接数据线和控制线。

2.打开计算机,进入系统。

3.运行内存存储器测试程序,测试内存存储器的读写速度和容量。

4.对内存存储器进行读操作和写操作,观察内存存储器的工作状态。

5.测试不同大小和型号的内存存储器,比较它们的读写速度和性能。

实验结果:1.经过测试,内存存储器的读写速度在20GB/s以上,容量为8GB。

2.内存存储器的读写速度快,可以满足CPU的数据读写需求。

3.不同大小和型号的内存存储器性能有所差异,需要根据具体需求选择适合的内存存储器。

mbist测试方法

mbist测试方法MBIST测试方法简介MBIST(Memory Built-In Self Test)是一种用于测试集成电路中存储器(Memory)的方法。

在集成电路中,存储器是一个重要的组成部分,负责存储和读取数据。

因此,对存储器进行可靠的测试是确保整个集成电路质量的关键步骤之一。

MBIST测试方法是通过在集成电路中嵌入特定的测试电路来实现的。

这些测试电路可以自动地对存储器进行测试,检测和修复其中的故障。

MBIST测试方法有助于提高集成电路的品质和可靠性,减少故障率和成本。

MBIST测试方法的基本原理是利用测试电路生成一系列的测试模式,将这些测试模式写入到存储器中,并读取存储器的输出数据进行比较。

通过分析比较结果,可以检测存储器中的故障,并根据需要进行修复。

MBIST测试方法的优势在于它可以在制造过程中和设备运行时进行测试。

在制造过程中,MBIST测试方法可以用于检测存储器的制造缺陷,例如漏电、短路等。

而在设备运行时,MBIST测试方法可以用于检测存储器的老化和故障,及时修复或替换损坏的存储器。

MBIST测试方法的实施过程包括以下几个步骤:1. 设计测试电路:根据存储器的特性和需求,设计适合的测试电路。

测试电路应能生成多种测试模式,并能检测和修复存储器中的故障。

2. 集成测试电路:将设计好的测试电路集成到集成电路中。

这个过程需要进行电路布线和物理设计,确保测试电路能够正确地与存储器进行连接。

3. 生成测试模式:根据测试电路的设计,生成一系列的测试模式。

这些测试模式可以覆盖存储器的所有操作模式和边界条件,以确保测试的全面性和准确性。

4. 写入测试模式:将生成的测试模式写入到存储器中。

写入测试模式时,需要确保测试模式能够正确地加载到存储器的各个地址位置。

5. 读取比较数据:读取存储器的输出数据,并与预期的结果进行比较。

比较结果可以用于检测存储器中的故障,并确定是否需要修复。

6. 修复存储器:根据比较结果,确定存储器中的故障类型和位置。

存储器实验报告实验结果

一、实验目的1. 了解存储器的概念、分类和工作原理;2. 掌握存储器扩展和配置方法;3. 熟悉存储器读写操作;4. 分析存储器性能,提高存储器使用效率。

二、实验环境1. 实验设备:计算机、存储器芯片、编程器、示波器等;2. 实验软件:Keil uVision、Proteus等。

三、实验内容1. 存储器芯片测试2. 存储器扩展实验3. 存储器读写操作实验4. 存储器性能分析四、实验结果与分析1. 存储器芯片测试(1)实验目的:测试存储器芯片的基本性能,包括存储容量、读写速度等。

(2)实验步骤:① 将存储器芯片插入编程器;② 编程器读取存储器芯片的容量、读写速度等信息;③ 利用示波器观察存储器芯片的读写波形。

(3)实验结果:存储器芯片的存储容量为64KB,读写速度为100ns。

2. 存储器扩展实验(1)实验目的:学习存储器扩展方法,提高存储器容量。

(2)实验步骤:① 将两块64KB的存储器芯片并联;② 利用译码器将存储器地址线扩展;③ 连接存储器芯片的读写控制线、数据线等。

(3)实验结果:存储器容量扩展至128KB,读写速度与原存储器芯片相同。

3. 存储器读写操作实验(1)实验目的:学习存储器读写操作,验证存储器功能。

(2)实验步骤:① 编写程序,实现存储器读写操作;② 将程序编译并烧录到存储器芯片;③ 利用示波器观察存储器读写波形。

(3)实验结果:存储器读写操作正常,读写波形符合预期。

4. 存储器性能分析(1)实验目的:分析存储器性能,优化存储器使用。

(2)实验步骤:① 分析存储器读写速度、容量、功耗等参数;② 比较不同存储器类型(如RAM、ROM、EEPROM)的性能;③ 提出优化存储器使用的方法。

(3)实验结果:① 存储器读写速度、容量、功耗等参数符合设计要求;② RAM、ROM、EEPROM等不同存储器类型具有各自的特点,可根据实际需求选择合适的存储器;③ 优化存储器使用方法:合理分配存储器空间,减少存储器读写次数,降低功耗。

nandtest 用法

nandtest 用法1. 引言1.1 概述:本篇长文将介绍nandtest的用法。

nandtest是一种用于检测和测试NAND闪存器件的工具。

随着闪存技术的广泛应用,nandtest成为了一个重要的工具,可以帮助我们验证和保证闪存器件的质量和可靠性。

1.2 文章结构:本文首先概述了nandtest的基本信息,并给出了文章目录以便读者快速了解全文内容。

然后详细介绍了nandtest的使用方法,包括它适用的场景和使用步骤。

接下来,我们将深入探讨nandtest的主要功能,分别介绍其三个核心功能。

最后,在结论部分总结nandtest的优点和局限性,并对未来发展提出展望或建议。

1.3 目的:本篇长文旨在帮助读者全面了解nandtest的用法,使读者能够熟练地在实际工作中应用这一工具。

通过掌握nandtest的基本操作步骤和核心功能,读者可以准确、高效地进行NAND闪存器件的测试与验证工作。

同时,本文也会对nandtest进行评价和总结,帮助读者更好地理解该工具的优缺点和发展前景。

2. nandtest 用法:2.1 什么是nandtestnandtest是一种测试工具,用于测试嵌入式系统中的NAND闪存设备。

NAND闪存是一种非易失性存储器,广泛应用于移动设备和嵌入式系统中。

nandtest可以通过验证数据可靠性和存储器稳定性来评估NAND闪存设备的质量,并帮助开发人员识别潜在的硬件或固件问题。

2.2 使用场景nandtest主要适用于以下场景:- 嵌入式开发:开发人员可以使用nandtest来评估他们所使用的NAND闪存设备的性能和可靠性。

- 硬件制造商:硬件制造商可以使用nandtest来检查他们生产出来的NAND 闪存设备是否符合规格和标准。

- 故障排除:当出现系统故障或数据损坏时,nandtest可以帮助技术人员确定是硬件还是软件引起的问题。

2.3 使用步骤下面是使用nandtest的基本步骤:步骤1: 准备测试环境在开始测试前,需要确保已经正确连接了NAND闪存设备,并且系统正常运行。

实验3 存储器 实验报告

实验3 存储器实验报告一、实验目的本次实验的主要目的是深入了解存储器的工作原理和性能特点,通过实际操作和观察,掌握存储器的读写操作、存储容量计算以及不同类型存储器的区别和应用。

二、实验设备1、计算机一台2、存储器实验装置一套3、相关测试软件三、实验原理存储器是计算机系统中用于存储数据和程序的重要部件。

按照存储介质和工作方式的不同,存储器可以分为随机存取存储器(RAM)和只读存储器(ROM)。

RAM 可以随机地进行读写操作,但断电后数据会丢失。

ROM 在正常工作时只能读取数据,且断电后数据不会丢失。

存储器的存储容量通常以字节(Byte)为单位,常见的存储容量有1GB、2GB、4GB 等。

存储容量的计算方法是:存储容量=存储单元个数 ×每个存储单元的位数。

四、实验内容与步骤1、熟悉实验设备首先,仔细观察存储器实验装置的结构和接口,了解各个部分的功能和作用。

2、连接实验设备将计算机与存储器实验装置通过数据线正确连接,并确保连接稳定。

3、启动测试软件打开相关的测试软件,进行初始化设置,选择合适的实验模式和参数。

4、进行存储器读写操作(1)随机写入数据:在测试软件中指定存储单元地址,输入要写入的数据,并确认写入操作。

(2)随机读取数据:指定已写入数据的存储单元地址,进行读取操作,将读取到的数据与之前写入的数据进行对比,验证读写的准确性。

5、计算存储容量通过读取存储器的相关参数和标识,结合存储单元的个数和每个存储单元的位数,计算出存储器的实际存储容量。

6、比较不同类型存储器的性能(1)分别对 RAM 和 ROM 进行读写操作,记录操作的时间和速度。

(2)观察在断电和重新上电后,RAM 和ROM 中数据的变化情况。

五、实验结果与分析1、读写操作结果经过多次的读写操作验证,存储器的读写功能正常,读取到的数据与写入的数据一致,表明存储器的读写操作准确无误。

2、存储容量计算结果根据实验中获取的存储器参数,计算得出的存储容量与标称容量相符,验证了存储容量计算方法的正确性。

hbm测试原理

hbm测试原理【引言】随着科技的不断发展,硬件测试技术也在不断进步。

其中,HBM(High-Bandwidth Memory)测试作为一种新兴的存储器测试技术,备受业界关注。

本文将详细介绍HBM测试的原理、应用领域以及我国的发展现状与展望。

【HBM测试的原理概述】1.测试方法HBM测试主要采用脉冲宽度调制(PWM)技术和频率调制(FM)技术。

通过改变脉冲宽度和频率,来检测存储器模块的性能和稳定性。

2.测试过程HBM测试过程主要包括以下几个阶段:(1)初始化:对存储器模块进行初始化,包括配置寄存器、设置时序等。

(2)测试模式设置:根据测试需求,设置相应的测试模式,如PWM或FM模式。

(3)数据采集:在设定好的测试模式下,对存储器模块进行数据读写操作,并采集相关性能参数。

(4)数据分析:对采集到的数据进行分析,评估存储器模块的性能和稳定性。

(5)结果输出:将分析结果输出,便于用户查看和评估。

3.测试指标HBM测试的主要指标包括:读写速度、数据传输率、稳定性和可靠性等。

这些指标可以帮助用户全面了解存储器模块的性能。

【HBM测试的应用领域】HBM测试广泛应用于计算机、通信、消费电子等领域,对于提高存储器模块的性能和稳定性具有重要意义。

【我国HBM测试的发展现状与展望】近年来,我国在HBM测试技术方面取得了显著成果,部分企业已具备了自主研发和生产HBM测试设备的能力。

然而,与国际先进水平相比,我国在HBM测试领域仍有一定差距。

未来,我国HBM测试技术将继续朝着更高精度、更高效、更智能的方向发展。

【总结】本文对HBM测试的原理、应用领域以及我国的发展现状与展望进行了详细介绍。

作为一种高效、可靠的存储器测试技术,HBM测试在业界得到了广泛认可。

我国在HBM测试领域虽有突破,但仍需不断努力,以缩小与国际先进水平的差距。

存储器测试标准(一)

存储器测试标准(一)•什么是存储器测试标准?存储器测试标准是指用来测试计算机内存性能指标的标准。

可以帮助用户快速了解计算机内存的性能和稳定性,确保计算机的正常运行。

常见的测试标准有Memtest86、Prime95、AIDA64等。

•Memtest86Memtest86是一款开源的内存测试工具,可以测试各种类型的内存。

通过在内存中写入和读取不同数据,检查内存中的错误。

可以测试内存容量、时序、频率、电压等参数,精准地检测出内存中的故障。

•Prime95Prime95是一款高性能的计算质数的软件。

它通过计算给定的整数是否是素数来测试计算机的稳定性和性能。

在测试过程中,可以测试CPU和内存的性能表现。

通过不断加强计算难度,可以检测计算机在不同负载下的表现。

•AIDA64AIDA64是一款全面的硬件信息检测工具。

它可以测试CPU、内存、显卡、硬盘等硬件部件的性能表现。

通过不同的测试模式,可以测试计算机的稳定性、性能和温度。

同时,也可以显示计算机的硬件信息,帮助用户了解计算机的配置和性能。

•总结存储器测试标准是保障计算机稳定性和性能的必备工具。

不同的测试标准适用于不同的硬件部件和测试需求。

用户可以根据自己的需求选择不同的测试标准,确保计算机的性能和稳定性。

•如何使用存储器测试标准?使用存储器测试标准需要注意以下几点:1.下载并安装对应的测试软件。

2.关闭电脑中所有正在运行的软件,确保只有测试软件在运行。

3.首先进行系统和硬件信息的检测,确保计算机的硬件能够满足测试要求。

4.根据测试需要选择相应的测试模式和参数,进行测试。

5.根据测试结果进行相应的调整和优化,确保计算机的稳定性和性能。

•存储器测试标准的应用领域存储器测试标准广泛应用于计算机硬件领域。

主要应用于以下几个方面:1.电脑硬件制造商:测试硬件尤其是内存的性能和稳定性,确保硬件的质量。

2.个人用户:测试内存性能,优化电脑性能,保持系统的稳定性。

3.软件开发人员:测试软件在不同硬件环境下的性能和稳定性,保证软件的可靠性。

存储器芯片测试原理及应用

存储器芯片测试原理及应用存储器芯片是计算机系统中很常见的重要组成部分,在计算机系统中主要用于存储各种数据和程序。

存储器芯片的质量和性能直接影响着计算机整体的运行效果和稳定性,因此如何对存储器芯片进行测试和检测就显得非常重要。

1. 存储器芯片测试原理存储器芯片测试主要涉及到两个方面,一方面是静态测试,另一方面是动态测试。

1.1 静态测试静态测试主要用于检测存储器芯片的单元内存单元是否异常,具体方法是将测试的存储器芯片中的每一个单元都设置成一个非常规数值,并将存储器进行读取操作,如果读取到的数值与设置的不符,则表示该单元异常。

在具体实现上,静态测试可以通过在测试前写入指定值、读取该值并进行比较的方式来检测存储器芯片的单元内存单元是否异常,如常用的0x55、0xff等非常规数值。

1.2 动态测试动态测试主要用于检测存储器芯片是否能够正常地进行读写操作,具体方法是通过向存储器芯片写入一定的数据模式,并进行读取操作,然后根据读取到的数据,来判断存储器芯片是否异常。

在具体实现上,动态测试可以通过写入若干个连续的数据、读取这些数据并进行比较的方式来检测存储器芯片是否正常。

常用的动态测试模式有行测试、列测试等。

2. 存储器芯片测试应用在实际应用中,存储器芯片测试主要用于以下三个方面:2.1 出厂测试存储器芯片通常是在生产厂家出厂前进行测试,以确保所有的存储器芯片都是可靠的,能够在正常的使用环境下稳定工作。

在出厂测试中,可以通过对存储器芯片进行全面的静态测试和动态测试,来确保存储器芯片的质量和性能。

2.2 维修测试在计算机系统使用过程中,如果发现存储器芯片出现故障,那么就需要对存储器芯片进行维修测试,以确定故障的具体原因,并进行修复。

在维修测试中,可以通过对存储器芯片进行一定的静态测试和动态测试,来确定故障原因,并进行修复。

2.3 质量检测为了保证计算机系统的正常工作,需要对所使用的存储器芯片进行定期的质量检测,以确定存储器芯片是否出现了潜在的故障或问题。

DRAM和SRAM存储器完全测试

DRAM和SRAM存储器完全测试摘要:动态DRAM存储器和静态SRAM存储器型号众多,应用广泛,检测难度比较大。

正达测试仪可以对数千种DRAM和SRAM存储器进行完全测试。

本文以对型号为KM44C4100AS-6的大容量动态DRAM存储器的检测实例,介绍DRAM和SRAM存储器完全测试的测试方法和应用意义。

同时,也指出对DRAM和SRAM 存储器功能精确检测不合适和不可靠的两种测试方式。

关键词:DRAM存储器 SRAM存储器完全测试抽样测试0.前言旅游部门评定酒店。

A城市评定方法:只对酒店做外观观察。

若某酒店门窗破损外墙皮脱落,一定不是好酒店。

若某酒店门窗完好外墙干净,应该是好酒店。

通过改进观察技术,发现某酒店一块玻璃上存在一小块灰尘,或许不是好酒店。

B城市评定方法:除了外观观察之外,一定要进入酒店内部。

检查酒店的软硬件设施和服务运转情况。

A城市的评定方法简单便捷。

有合理性,也有盲目性。

就如同使用电路测试仪对器件进行VI曲线测试。

B城市的评定方法科学准确,结论可靠。

就如同使用电路测试仪对器件进行功能测试。

本文为:器件功能测试之——对DRAM和SRAM存储器完全测试。

1.存储器完全测试特点1.1存储器完全测试的基本方法存储器完全测试的基本方法是:向存储器所有存储单元逐一写入一些数据,然后再读回数据。

如果读回数据和写入数据一致,则存储器通过完全测试。

1.2存储器完全测试的主要特点这里面的重点是:对存储器的所有存储单元毫无遗漏地逐一测试。

这就好比前言中B城市对某酒店的评定方法,无论是一千间客房的大型酒店,还是五十间客房的小型酒店,进入酒店内部检查时,检查的方法是对所有客房全检,而不是对部分客房抽检。

对于小型酒店而言,耗费的时间较少。

但对于大型酒店而言,耗费的时间会很长。

所以,不同于对普通数字IC器件/模拟IC器件瞬间完成功能测试,在对DRAM和SRAM存储器进行完全测试时,测试小容量存储器的全过程时间一般会需要几分钟,测试大容量存储器的全过程时间甚至需要一小时以上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4k 16k 64k 256k 1M 4M 16M 64M

7 5 3 2 1.3 1 0.5 0.35

0.07 0.1 0.15 0.3 0.2 0.3 0.3 0.6

Time

* The failure rate may increase when a component is used in an 'unfriendly' environment, caused by a stress condition. * An important stress condition is the temperature.

Memory cell array

Read/write logic

Data

* For this model, one is only able to detect a fault.

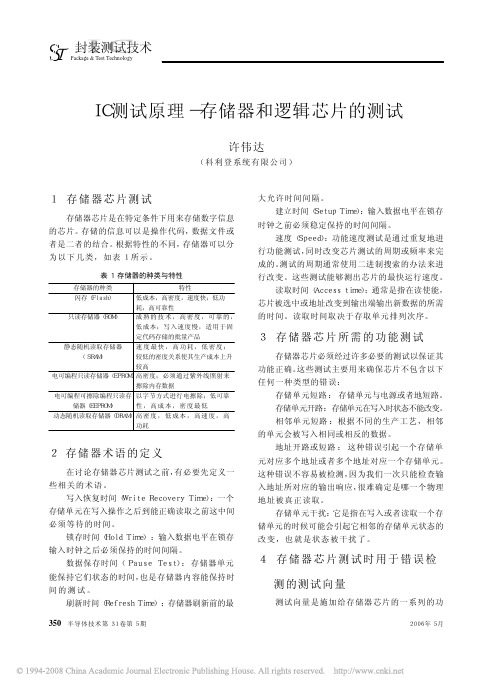

Chap5. MEMORY TESTING.1

Testing Semies in semiconductor memories have been very impressive. * Their density (bit/chip & bit/area) is ever increasing. * Algorithms with a test time of order O(n^2) are no longer acceptable for testing current mega- and multimega-bit memory chip, where n is the number of bits. * The price of memory chips tends to be stable over longer periods of time. * This makes testing memories an area of concern for practitioners as well as theoreticians who are interested in new test algorithms.

Chap5. MEMORY TESTING.7

Test Time as a Function of Memory Size

* Cycle time: 100 ns

Algorithm complexity Capacity

Testing time (in seconds) 64n 0.1 0.4 1.7 6.7 26.8 1.8 n•log2n 0.023 0.1 0.47 2.1 9.2 40.3 3n3/2 0.63 5.03 40.3 5.4 Mins 43 Mins 5.7 Hrs 2n 2 54 14 Mins 3.8 Hrs 61 Hrs 41 Days 2 Years

Chap5. MEMORY TESTING.10

5

Classification of Failure Mechanisms

* Electrical stress * Intrinsic fa ilure m echanisms

. Electrical overstress . Electrostatic discharge . Gate oxide breakdown . Ionic contamination . Surface charge spreading . Charge effects: Slow trapping, Hot electrons . Piping . Dislocations . Packaging . Metallization . Bounding . Die attachment failures . Particle contamination . Radiation

MTBF = Mean Time Between Failures MTPF = Mean Time between failures due to Permanent Faults ?982 Digital Press, DEC

* Only 2%~13% of the failures are caused by permanent faults.

Chap5. MEMORY TESTING.11

* Extrinsic f ailure mechanisms

Functional DRAM Chip Model

Address Refresh

Address latch Column decoder Refresh logic

Row decoder

Memory cell array

Memory Testing

* Market Share * Test Time * Failure Rate * Functional DRAM Model & Functional Faults * Test Algorithms * DC & AC Parametric Tests * DFT & BIST Aspects * Built-In Testing Schemes * Embedded RAM Tests

n

16k 64k 256k 1M 4M 16M

Mins

Chap5. MEMORY TESTING.8

4

The Importance of Non-Permanent Faults

System CMUA PDP-10 Cm* LSI-11 C.vmp TMR Telettra 1Mx37 RAM Technology ECL NMOS LSI-11 TTL MOS MTBF (hr) MTPF (hr) MTBF/MTPF (ratio) 0.03~0.06 0.03 0.02~0.07 0.06~0.13 0.07 44 800~1600 128 4200 97~328 4900 80~170 1300 106 1450

DRAM Cell Parameters

* The memory cells are placed closely together, which makes them more sensitive to influences of neighboring cell and increases the likelihood of disturbances due to noise on the address and data lines.

100M

# of memory cells per chip # of transistors per chip 64M 16M 4M 1M 80586?

10M 1M 100k

4k 16k 1k 4004 8080 256k

80486 68040 80386 LSI logic 64k 68020 gate array 80286 68000 8086 8085 Microprocessor Memory

Write driver

Sense amplifiers

Data register

Data flow Control flow

Data Data Read/write out in & chip enable

Chap5. MEMORY TESTING.12

6

Functional Faults

* Cell stuck * Read/write line stuck * Data line stuck * Driver stuck * Chip-select line stuck * Open in data line

Chap5. MEMORY TESTING.2

1

Memory Market Share

* DRAM chips are the major part of the memory market.

1988 DRAMs SRAMs ROMs EPROMs EEPROMs* Total 56 17 8 17 2 1990 54 22 8 14 2 1994 58 21 6 12 3

* Cell can be set to 0 but not to 1 (or vice-versa) * Pattern sensitive interaction between cells

Chap5. MEMORY TESTING.13

Reduced Functional Model

Address Address decoder

100% 100% 100%

* Includes flash EEPROMs

?990 Integrated Circuit Engineering Corporation

Chap5. MEMORY TESTING.3

Number of Bits per DRAM: The -Rule

* Historically the number of bits per chip has quadrupled roughly every 3.1 (or ) years.

Chap5. MEMORY TESTING.9

Failure Rate Representation: Bathtub Curve

Burn-in Useful life Wearout

Wearout failures Random failures

Failure rate

Early failures

10k

1k70

74

78

82 Year

86

90

94

?990 Integrated Circuit Engineering Corporation