DSP实验二

dsp原理与应用实验报告总结

dsp原理与应用实验报告总结DSP(Digital Signal Processing)数字信号处理是利用数字技术对信号进行处理和分析的一种方法。

在本次实验中,我们探索了DSP的原理和应用,并进行了一系列实验以验证其在实际应用中的效果。

以下是对实验结果的总结与分析。

实验一:数字滤波器设计与性能测试在本实验中,我们设计了数字滤波器,并通过性能测试来评估其滤波效果。

通过对不同类型的滤波器进行设计和实现,我们了解到数字滤波器在信号处理中的重要性和应用。

实验二:数字信号调制与解调本实验旨在通过数字信号调制与解调的过程,了解数字信号的传输原理与方法。

通过模拟调制与解调过程,我们成功实现了数字信号的传输与还原,验证了调制与解调的可行性。

实验三:数字信号的傅里叶变换与频谱分析傅里叶变换是一种重要的信号分析方法,可以将信号从时域转换到频域,揭示信号的频谱特性。

本实验中,我们学习了傅里叶变换的原理,并通过实验掌握了频谱分析的方法与技巧。

实验四:数字信号的陷波滤波与去噪处理陷波滤波是一种常用的去除特定频率噪声的方法,本实验中我们学习了数字信号的陷波滤波原理,并通过实验验证了其在去噪处理中的有效性。

实验五:DSP在音频处理中的应用音频处理是DSP的一个重要应用领域,本实验中我们探索了DSP在音频处理中的应用。

通过实验,我们成功实现了音频信号的降噪、均衡和混响处理,并对其效果进行了评估。

实验六:DSP在图像处理中的应用图像处理是另一个重要的DSP应用领域,本实验中我们了解了DSP在图像处理中的一些基本原理和方法。

通过实验,我们实现了图像的滤波、边缘检测和图像增强等处理,并观察到了不同算法对图像质量的影响。

通过以上一系列实验,我们深入了解了DSP的原理与应用,并对不同领域下的信号处理方法有了更深刻的认识。

本次实验不仅加深了我们对数字信号处理的理解,也为日后在相关领域的研究与实践提供了基础。

通过实验的结果和总结,我们可以得出结论:DSP作为一种数字信号处理的方法,具有广泛的应用前景和重要的实际意义。

DSP实验二、TMS320F28335 按键输入 控制LED亮灭

继续我的第二个实验;实现按键控制LED亮灭:功能描述:上电默认LD3亮;触动一次按键SW12,LD3灭再按一次按键SW12,LD3亮再触动一次按键SW12,LD3灭再按一次按键SW12,LD3亮。

实现每触动一次按键,LED执行一次由亮到灭,或者由灭到亮,也就是实现一次状态反转。

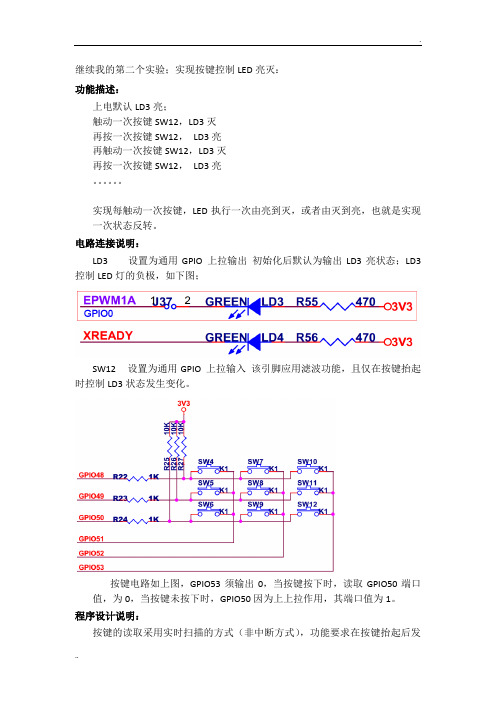

电路连接说明:LD3 设置为通用GPIO 上拉输出初始化后默认为输出LD3亮状态;LD3控制LED灯的负极,如下图;SW12 设置为通用GPIO 上拉输入该引脚应用滤波功能,且仅在按键抬起时控制LD3状态发生变化。

按键电路如上图,GPIO53须输出0,当按键按下时,读取GPIO50端口值,为0,当按键未按下时,GPIO50因为上上拉作用,其端口值为1。

程序设计说明:按键的读取采用实时扫描的方式(非中断方式),功能要求在按键抬起后发生LED状态翻转;所以要记录上一次按键值,并且将当前值==0&&上一次值==1时,做为按键抬起有效,控制LED发生状态翻转。

主要程序如下:while(1){EALLOW;last_Key_SW12 = new_Key_SW12; //保存旧值new_Key_SW12 = Key_SW12();//读取新值if( last_Key_SW12==0 && new_Key_SW12==1)LD3_TOGGLE();EDIS;}经实际测试,上述程序可以实现LD3的翻转,基本达到设计要求。

但是在测试过程中,时好时坏,有时能够看见LED快速翻转,说明按键有抖动的情况,这里可以考虑IO口滤波,即在初始化时,设置IO采样周期以及量化串口,设置如下:采样周期设置为200时,不再出现抖动现象,按键稳定操作。

源程序如下:#include"DSP2833x_Device.h"// DSP2833x Headerfile Include File#include"DSP2833x_Examples.h"// DSP2833x Examples Include File#define LD3_ON() GpioDataRegs.GPACLEAR.bit.GPIO0 = 1#define LD3_OFF() GpioDataRegs.GPASET.bit.GPIO0 = 1#define LD3_TOGGLE() GpioDataRegs.GPATOGGLE.bit.GPIO0 = 1#define LD4_ON() GpioDataRegs.GPBCLEAR.bit.GPIO34 = 1#define LD4_OFF() GpioDataRegs.GPBSET.bit.GPIO34 = 1#define Key_SW12() GpioDataRegs.GPBDAT.bit.GPIO50/** main.c*/int main(void) {unsigned char last_Key_SW12=1;//保留上一次扫描结果,上电默认为未按下状态unsigned char new_Key_SW12=1;//保留当前扫描结果,上电默认为未按下状态InitSysCtrl();DINT;IER = 0x0000;IFR = 0x0000;InitPieCtrl();InitPieVectTable();InitGpio();EALLOW;//GPIO0 LD3 控制LED负极GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 0;//0 gpio modeGpioCtrlRegs.GPADIR.bit.GPIO0 = 1;//1 output 0 inputGpioCtrlRegs.GPAPUD.bit.GPIO0 = 0;//1 enable pullup 0 disable pullup//GPIO34 LD4 控制LED负极GpioCtrlRegs.GPBMUX1.bit.GPIO34 = 0;//0 gpio modeGpioCtrlRegs.GPBDIR.bit.GPIO34 = 1;//1 output 0 inputGpioCtrlRegs.GPBPUD.bit.GPIO34 = 0;//1 enable pullup 0 disable pullup//GPIO50 按键矩阵SW12输入端GpioCtrlRegs.GPBMUX2.bit.GPIO50 = 0;//0 gpio modeGpioCtrlRegs.GPBDIR.bit. GPIO50 = 0;//1 output 0 inputGpioCtrlRegs.GPBPUD.bit. GPIO50 = 0;//1 enable pullup 0 disable pullup GpioCtrlRegs.GPBCTRL.bit.QUALPRD2= 200;//采样周期=2*Tsysclkout*200GpioCtrlRegs.GPBQSEL2.bit.GPIO50 = 2;//采样窗内3次采样结构相同//GPIO53 按键矩阵负极输出0GpioCtrlRegs.GPBMUX2.bit.GPIO53 = 0;//0 gpio modeGpioCtrlRegs.GPBDIR.bit. GPIO53 = 1;//1 output 0 inputGpioCtrlRegs.GPBPUD.bit. GPIO53 = 0;//1 enable pullup 0 disable pullup GpioDataRegs.GPBCLEAR.bit.GPIO53 = 1;LD3_ON();//默认输出亮状态LD4_OFF();EDIS;while(1){EALLOW;last_Key_SW12 = new_Key_SW12; //保存旧值new_Key_SW12 = Key_SW12();//读取新值if( last_Key_SW12==0 && new_Key_SW12==1) LD3_TOGGLE();EDIS;}}。

DSP实验报告定时器2

实验二DSP系统定时器的使用一、实验目的:1、掌握5402 DSP片上定时器的初始化设置及应用;2、掌握DSP系统中实现定时的原理及方法;3、了解5402 DSP中断寄存器IMR、IFR的结构和使用;4、掌握5402 DSP系统中断的初始化设置过程和方法;5、掌握在C语言中嵌入汇编语句实现数字I/O的方法。

二、实验原理:1、定时器及其初始化在5402内部包括两个完全相同的定时器:定时器0和定时器1。

每个定时器分别包括3个寄存器:定时器周期寄存器PRD、定时器寄存器TIM、定时器控制寄存器TCR,其中TCR 寄存器中包括定时器分频系数TDDR、定时器预分频计数器PSC两个功能寄存器。

通过PRD 和TDDR可以设置定时器的初始值,TIM(16bits)和PSC(4bits)是用于定时的减法计数器。

CLKOUT是定时器的输入时钟,最大频率为100Mhz。

定时器相当于20bit的减法计数器。

定时器的结构如图1所示。

图1 定时器的组成框图定时器的定时周期为:CLKOUT×(TDDR+1)×(PRD+1)其中,CLKOUT为时钟周期,TDDR和PRD分别为定时器的分频系数和时间常数。

在正常工作情况下,当TIM减到0后,PRD中的时间常数自动地加载到TIM。

当系统复位或者定时器单独复位时,PRD中的时间常数重新加载到TIM。

同样地,每当复位或PSC减到0后,定时器分频系数TDDR自动地加载到PSC。

PSC在CLKOUT作用下,作减1计数。

当PSC 减到0时,产生一个借位信号,令TIM作减l计数。

TIM减到0后,产生定时中断信号TINT,传送至CPU和定时器输出引脚TOUT。

例如:欲设置定时器0的定时周期为1ms,当DSP工作频率为100Mhz时,通过上式计算可得出:TDDR=15,PRD=6520。

2、定时器的使用下面是一段定时器应用程序,每检测到一次中断,ms+1,利用查询方式每计500个数就令XF引脚的电平翻转一次,在XF引脚输出一矩形波信号,因定时器1ms中断一次,故500ms就使LED翻转一次,这样LED指示灯就不停地闪烁。

dsp实验2:Code Composer Studio 入门

苏州职业大学实训报告

图2.2创建工程文件

选择菜单“Project”的“Rebuild All”项,或单击工具条中的按钮;注意编

图 2.4修改工程文件

通过以上设置操作,重新编译后,程序中的用户堆栈的尺寸被设置成 1024 个字。

6.基本调试功能

(1)下载程序:执行File Load Program ,在随后打开的对话框中选择刚刚建立的

C:\ICETEK\F2812\DSP281x_examples\Lab0101-UseCCS\Debug\volume.out 文件。

设置软件调试断点:在项目浏览窗口中,双击volume.c 激活这个文件,移动光标到

图 2.6设置图形显示功能

-在弹出的图形窗口中单击鼠标右键,选择“Clear Display”。

-按Alt+F5 运行程序.观察input 窗口的内容。

10.选择菜单File→workspace→save workspacs As…,输入文件名11.退出CCS 。

五.实验结果:

通过对工程文件“volume”的编译、执行后得到结果的图形显示如下:。

实验二 利用DSP实现图像的灰度处理

北京交通大学电子信息学院

灰度变换程序

在dm642main.c中图像显示(bt656_display_start(vpHchannel0);)之前添加:removeColor();。 函数体如下: void removeColor() /***************灰度显示处理算法程序************/ { int i,j; //奇数行 for(i=intALines;i<intDLines;i++)//行数 { for(j=intAPixels/2;j<intDPixels/2;j++) //每行像素数 { /***********CbCr分量值赋为0x80*************/ *(Uint8 *)(tempCbbuffer + i * (numPixels >> 1) + j) = 0x80; *(Uint8 *)(tempCrbuffer + i * (numPixels >> 1) + j) = 0x80; } } //偶数行 for(i=numLines/2+intALines;i<numLines/2+intDLines;i++)//行数 { for(j=intAPixels/2;j<intDPixels/2;j++) //每行像素数 { /***********CbCr分量值赋为0x80*************/ *(Uint8 *)(tempCbbuffer + i * (numPixels >> 1) + j) = 0x80; *(Uint8 *)(tempCrbuffer + i * (numPixels >> 1) + j) = 0x80; } } 北京交通大学电子信息学院 } Leading Digital Signal Processing

DSP实验二 拨码开关实验

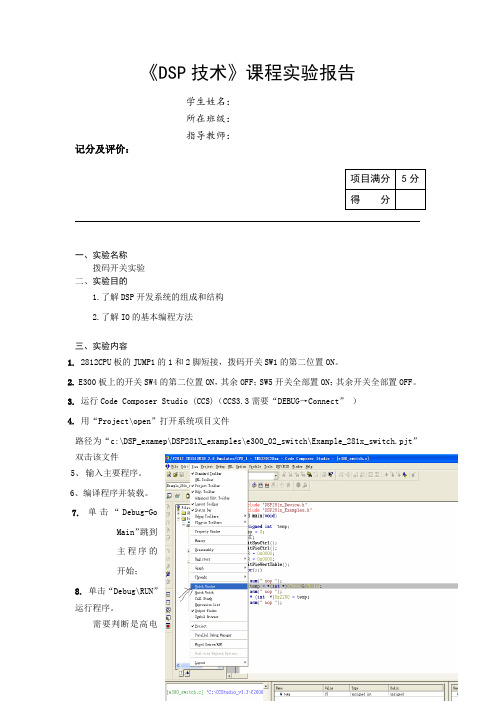

《DSP技术》课程实验报告学生姓名:所在班级:指导教师:记分及评价:项目满分5分得分一、实验名称拨码开关实验二、实验目的1.了解DSP开发系统的组成和结构2.了解IO的基本编程方法三、实验内容1. 2812CPU板的JUMP1的1和2脚短接,拨码开关SW1的第二位置ON。

2.E300板上的开关SW4的第二位置ON,其余OFF;SW5开关全部置ON;其余开关全部置OFF。

3.运行Code Composer Studio (CCS)(CCS3.3需要“DEBUG→Connect”)4. 用“Project\open”打开系统项目文件路径为“c:\DSP_examep\DSP281X_examples\e300_02_switch\Example_281x_switch.pjt”双击该文件5、输入主要程序。

6、编译程序并装载。

7.单击“Debug-GoMain”跳到主程序的开始;8. 单击“Debug\RUN”运行程序。

需要判断是高电平亮,还是低电平亮,可以使用中断调试。

在运行状态,在需要设置断点的位置的右边,双击,就可以产生红点。

表明设置了断点。

在view目录下,(如右边图所示:)打开watch window,(此项是用来检查和编辑变量或C表达式可以不同格式显示变量值,还可以显示数值、结构或指针等包含多个元素的变量),在本实验中观察temp变量的变化。

步骤:在debug目录下点run,在断点处,程序会停下来,可以观察temp变量的值。

(也可按“F10”单步运行程序,观察temp变量的值。

)9. 任意拨动E300底板上的拨动开关,观察LED和拨动开关的对应情况。

(LED1-LED7分别对应DSP数据总线的D0-D7)10.单击“Debug \ Halt”暂停持续运行,开关将对灯失去控制.11.关闭所有窗口,本实验完毕.四、实验程序与结果分析实验程序:#include "DSP281x_Device.h" // DSP281x Headerfile Include File#include "DSP281x_Examples.h" // DSP281x Examples Include Filevoid main(void){unsigned int temp;temp = 0;DINT;InitSysCtrl();InitPieCtrl();IER = 0x0000;IFR = 0x0000;InitPieVectTable();for(;;){asm(" nop ");temp = *(int *)0x2200&0x00ff;if(temp!=0x80){temp=(temp<<1)&0x00ff;asm(" nop ");* (int *)0x2200 = temp;}else * (int *)0x2200 =0x01;asm(" nop ");}}结果分析:多次拨动E300底板上的拨码开关,观察LED亮灭后,我们发现拨动开关的对LED1-LED7分别对应DSP数据总线的D0-D7,并且LED低电平时导通。

DSP实验报告_6

实验一: 闪灯实验熟悉DSP 软硬件测试系统实验目的1.了解SHARC 系列高性能数字信号处理器的程序开发过程和编程语言;2.熟悉集成开发工具VisualDSP++, 学会使用VisualDSP++进行SHARC 系列ADSP 的程序开发、编译与调试;3.掌握SHARC 系列ADSP 的程序加载设计和加载过程。

实验内容利用波形产生信号板, 结合FPGA 编程技术和程序编程器, 编写测试ADSP21065L 和FPGA 之间硬件连接的应用程序, 同时完成应用程序的加载和脱机操作, 在信号指示灯“HL2”上产生可调周期的脉冲信号, “点亮”与“熄灭”指示灯HL2。

实验要求通过DSP 编程, 在其FLAG11引脚上模拟如下波形的周期信号:要求:(1) 500H T ms >,500L T ms >. (2) 并用示波器查看波形, 测量信号周期。

实验步骤1. 熟悉电路图, 清楚波形产生电路板ADSP21065L 与可编程FPGA 器件之间的连接关系;2. 编写FPGA 程序。

在FPGA 内部将ADSP21065L 的标志引脚FLAG11(引脚号26)设置为输出, 作为FPGA 的输入信号, 在FPGA 内部编程将该信号直接输出在发FPGA 的37引脚号上, 设置37引脚为输出信号, 驱动板上的HL2 LED 指示灯;3. 启动VisualDsp++4.5,选择project 工程选项菜单, 创建一个名称为Test.dpj 的工程文件, 选择处理器的型号为ADSP-21065L ;4.弹出一个对话框, 选择是否需要加入VDSP kernel ,选择“NO ”;5. 在工程中加入以下参考源文件:\exp1\test(boot)\ boot1.asm 和boot1.ldf 6.编译, 链接调试, 生成可执行文件。

7.运行程序, 可以看到波形发生电路板上的指示灯“HL2”不断闪动。

8. 利用示波器观测系统时钟,并测量产生信号的波形和周期。

DSP实验指导书输入输出

7).程序单步执行

按F8,就可观察到程序单步运行的状态,并可观察D2的发光情况。

8).程序全速运行

按F5,就可观察到程序在全速运行状态下,D2的发光情况。并用示波器观察I/O管脚的波形。如果D2的闪烁不明显,可修改延时子程序。

GEL_MapAdd(0x1000,1,0xF000,1,1);/* External SRAM */

}

menuitem "F2407 DEBUGGER";

hotmenu flash_disable()

{

*(int *)SCSR2 = MP;

}

hotmenu flash_enable()

{

*(int *)SCSR2 = MC;

delay(1000);/* 延时子程序 */

delay(1000);/* 延时子程序 */

asm(" clrcxf");

*PADATDIR=*PADATDIR&0x0FF00;// IOPA端口设置为输出方式

*PBDATDIR=*PBDATDIR&0x0FF00;

*PCDATDIR=*PCDATDIR&0x0FF00;

}

SECTIONS

{

.vectors:>VECS PAGE 0

.text:>FLASH PAGE 0

.cinit :>FLASH PAGE 0

.data :>FLASH PAGE 0

.stack :>B0 PAGE 1

DSP实验报告(二)

DSP实验报告(二)实验二应用FFT对信号进行频谱分析一、实验目的1、在理论学习的基础上,通过本次实验,加深对快速傅里叶变换的理解,熟悉FFT算法及其程序的编写。

2、熟悉应用FFT对典型信号进行频谱分析的方法。

3、了解应用FFT进行信号频谱分析过程中可能出现的问题,以便在实际中正确应用FFT。

二、实验原理与方法①一个连续信号的频谱可以用它的傅立叶变换表示为+ Xa(jW)=-jWtx(t)edtòa-如果对该信号进行理想采样,可以得到采样序列x(n)=xa(nT)同样可以对该序列进行z变换,其中T为采样周期X(z)=+ x(n)z-n+ -令z为ejw,则序列的傅立叶变换X(ejw)=x(n)ejwn-其中ω为数字频率,它和模拟域频率的关系为w=WT=W/fs式中的是采样频率。

上式说明数字频率是模拟频率对采样率的归一化。

同模拟域的情况相似。

数字频率代表了序列值变化的速率,而序列的傅立叶变换称为序列的频谱。

序列的傅立叶变换和对应的采样信号频谱具有下式的对应关系。

1X(e)=Tjw+ - w-2pXa(j)T即序列的频谱是采样信号频谱的周期延拓。

从式可以看出,只要分析采样序列的谱,就可以得到相应的连续信号的频谱。

注意:这里的信号必须是带限信号,采样也必须满足Nyquist定理。

在各种信号序列中,有限长序列在数字信号处理中占有很重要的地位。

无限长的序列也往往可以用有限长序列来逼近。

有限长的序列可以使用离散傅立叶变换。

当序列的长度是N时,定义离散傅立叶变换为:X(k)=DFT[x(n)]=其中W=e2pj-NN-1n=0WNkn它的反变换定义为:1x(n)=IDFT[X(k)]=N根据式和,则有N-1n=0X(k)WNknX(z)|z=Wnk=NN-1n=0x(n)WNnk=DFT[x(n)]j2pN可以得到X(k)2pk的点,就NN是将单位圆进行N等分以后第k个点。

所以,X(k)是z变换在单位圆上的等距采样,或者说是序列傅立叶变换的等距采样。

DSP原理及应用实验二---堆栈的使用方法

• 1、实验要求: 用软件仿真的方法编译并调试幻灯 片第3页的实验参考程序,在存储器 中观察正确结果。

• 2、实验步骤

请认真倾听教师讲解的要点,也可参阅附 件1及附件2,结合思考题完成实验。写实验 报告时自行写出实验步骤。 操作步骤要点: (1)新建项目/新建文件/添加文件到项目/编 辑文件; (2)点“rebuild all”工具进行编译、汇编和 链接; (3)装载上一步生成的out文件; (4)运行后点“view/memory”观察运行结果。

• 3、实验程序——堆栈的使用方法

(1)汇编主程序文件

(3)链接命令文件

(2)中断向量表文件

• 4、实验思考题:

(1)修改主程序,实现堆栈区100个单元全 部数据变为“DEAD”。 (2)通过单步调试,观察SP和寄存器内容的 变化,简述堆栈的特点? (3) 重新编写主程序,用其它指令。

dsp实验报告

dsp实验报告实验一:CCS入门实验实验目的:1. 熟悉CCS集成开发环境,掌握工程的生成方法;熟悉SEED-DEC643实验环境; 掌握CCS集成开发环境的调试方法。

2.学习用标准C 语言编写程序;了解TI CCS开发平台下的C 语言程序设计方法和步骤; 熟悉使用软件仿真方式调试程序。

3. 学习用汇编语言编写程序; 了解汇编语言与 C 语言程序的区别和在设置上的不同;了解TMS320C6000 汇编语言程序结果和一些简单的汇编语句用法学习在CCS 环境中调试汇编代码。

4. 在了解纯C 语言程序工程和汇编语言程序工程结构的基础上,学习在C 工程中加入汇编编程的混合编程方法; 了解混合编程的注意事项;理解混合编程的必要性和在什么情况下要采用混合编程5. 熟悉CCS集成开发环境,掌握工程的生成方法; 熟悉SEED-DEC643实验环境;掌握CCS集成开发环境的调试方法。

实验原理:CCS 提供了配置、建立、调试、跟踪和分析程序的工具,它便于实时、嵌入式信号处理程序的编制和测试,它能够加速开发进程,提高工作效率。

CCS 提供了基本的代码生成工具,它们具有一系列的调试、分析能力序。

使用此命令后,要重新装载.out 文件后,再执行程序。

使用 CCS常遇见文件简介1. program.c: C 程序源文件;2. program.asm: 汇编程序源文件;3. filename.h: C 程序的头文件,包含DSP/BIOS API模块的头文件;4. filename.lib: 库文件;5. project.cmd: 连接命令文件;6. program.obj: 由源文件编译或汇编而得的目标文件;7. program.out: 经完整的编译、汇编以及连接后生成可执行文件; 8. program.map: 经完整的编译、汇编以及连接后生成空间分配文件; 9.project.wks: 存储环境设置信息的工作区文件。

P.S(CMD文件中常用的程序段名与含义1. .cinit 存放C程序中的变量初值和常量;2. .const 存放C程序中的字符常量、浮点常量和用const声明的常量;3. .text 存放C程序的代码;4. .bss 为C 程序中的全局和静态变量保留存储空间;5. .far 为C 程序中用far声明的全局和静态变量保留空间;6. .stack 为 C 程序系统堆栈保留存储空间,用于保存返回地址、函数间的参数传递、存储局部变量和保存中间结果;7. .sysmem 用于 C 程序中malloc、calloc 和 realloc 函数动态分配存储空间。

dsp实验报告

dsp实验报告DSP实验报告一、引言数字信号处理(Digital Signal Processing,DSP)是一种对数字信号进行处理和分析的技术。

它在许多领域中被广泛应用,如通信、音频处理、图像处理等。

本实验旨在通过实际操作,探索和理解DSP的基本原理和应用。

二、实验目的1. 理解数字信号处理的基本概念和原理;2. 掌握DSP实验平台的使用方法;3. 进行一系列DSP实验,加深对DSP技术的理解。

三、实验器材和软件1. DSP开发板;2. 电脑;3. DSP开发软件。

四、实验内容1. 实验一:信号采集与重构在此实验中,我们将通过DSP开发板采集模拟信号,并将其转换为数字信号进行处理。

首先,我们需要连接信号源和开发板,然后设置采样频率和采样时间。

接下来,我们将对采集到的信号进行重构,还原出原始模拟信号,并进行观察和分析。

2. 实验二:滤波器设计与实现滤波器是DSP中常用的模块,用于去除或增强信号中的特定频率成分。

在此实验中,我们将学习滤波器的设计和实现方法。

首先,我们将选择合适的滤波器类型和参数,然后使用DSP开发软件进行滤波器设计。

最后,我们将将设计好的滤波器加载到DSP开发板上,并进行实时滤波处理。

3. 实验三:频谱分析与频域处理频谱分析是DSP中常用的方法,用于分析信号的频率成分和能量分布。

在此实验中,我们将学习频谱分析的基本原理和方法,并进行实际操作。

我们将采集一个包含多个频率成分的信号,并使用FFT算法进行频谱分析。

然后,我们将对频谱进行处理,如频率选择、频率域滤波等,并观察处理后的效果。

4. 实验四:音频处理与效果实现音频处理是DSP中的重要应用之一。

在此实验中,我们将学习音频信号的处理方法,并实现一些常见的音频效果。

例如,均衡器、混响、合唱等。

我们将使用DSP开发软件进行算法设计,并将设计好的算法加载到DSP开发板上进行实时处理。

五、实验结果与分析通过以上实验,我们成功完成了信号采集与重构、滤波器设计与实现、频谱分析与频域处理以及音频处理与效果实现等一系列实验。

DSP实验二拨码开关实验

实验二拨码开关实验—、实验目的二、实验设备运算机,版本软件,DSP仿真器,E300实验箱,2812CPU板。

三、实验原理8位的数字量输入(由拨码开关产生),当拨码打到靠近LED时为低。

相反为高。

通过74LS244(可读)缓冲连接到DSP的数据总线的低8位。

CPU通过读指令读取到拨码开关产生的8位输出的数字量,然后CPU通过写指令把读出的8位数字量写入(0x2200)单元内,使连接到DSP的数据总线的低8位的74LS273的输出端产生高低信号,现在LED灯产生亮灭。

当对应LED灯点亮时说明输出为低,熄灭时为高。

(器件74LS244和74LS273详细的介绍请参看数据手册)数字量输入输出单元的资源分派如下:基地址:2000h(当CS1为0时分派有效)数字量分派空间为数据空间地址:基地址+0x2200(低8位,只读)拨码开关扩展工作原理说明:74LS244片选号、74LS273片选信号和74LS273复位信号由E300上CPLD译码产生。

本实验利用DSP数据总线的低8位。

实验任务一:一、编写程序完成将拨码开关的信息读入DSP,然后再将该信息回写,操纵led灯。

调整"数字输入输出单元"的开关K1~K8,观看LED1~LED8灯亮灭的转变。

2、本实验的程序流程框图如下:3、输入要紧程序#include "" 2812CPU板的JUMP1的1和2脚短接,拨码开关SW1的第二位置ON。

2.E300板上的开关SW4的第二位置ON,其余OFF;SW5开关全数置ON;其余开关全数置OFF。

3.运行Code Composer Studio (CCS)(需要“DEBUG→Connect”)4. 用“Project\open”打开系统项目文件途径为“c:\DSP_examep\DSP281X_examples\e300_02_switch\”双击该文件5、输入要紧程序。

六、编译程序并装载。

DSP实验报告2-数字信号处理

23 系 2012 级 丛松宇 PB12210075

3. clear; n=1:8; for i=1:4 x(i)=i; end for i=5:8 x(i)=9-i; end close all; subplot(2,4,1); stem(x);grid on; title('8 点三角波序列'); subplot(2,4,2); stem(abs(fft(x,8)));grid on; n=1:16; for i=9:16 x(i)=0; end subplot(2,4,3); stem(x);grid on; title('16 点三角波序列'); subplot(2,4,4); stem(abs(fft(x,16)));grid on; n=1:8; for i=1:4 x(i)=5-i; end

23 系 2012 级 丛松宇 PB12210075

1.② n=0:15; q=8;p=8; x=exp(-1*(n-p).^2/q); close all; subplot(3,2,1); stem(x),grid on title('q=8,p=8 的时域特性'); subplot(3,2,2); stem(abs(fft(x))),grid on;title('频域特性'); q=8;p=13; x=exp(-1*(n-p).^2/q); subplot(3,2,3); stem(x),grid on title('q=8,p=13 的时域特性'); subplot(3,2,4); stem(abs(fft(x))),grid on;title('频域特性'); q=8;p=14; x=exp(-1*(n-p).^2/q); subplot(3,2,5); stem(x),grid on title('q=8,p=14 的时域特性'); subplot(3,2,6); stem(abs(fft(x))),grid on;title('频域特性');

DSP实验报告_百度文库(精)

实验0 实验设备安装才CCS调试环境实验目的:按照实验讲义操作步骤,打开CCS软件,熟悉软件工作环境,了解整个工作环境内容,有助于提高以后实验的操作性和正确性。

实验步骤:以演示实验一为例:1.使用配送的并口电缆线连接好计算机并口与实验箱并口,打开实验箱电源;2.启动CCS,点击主菜单“Project->Open”在目录“C5000QuickStart\sinewave\”下打开工程文件sinewave.pjt,然后点击主菜单“Project->Build”编译,然后点击主菜单“File->Load Program”装载debug目录下的程序sinewave.out;3.打开源文件exer3.asm,在注释行“set breakpoint in CCS !!!”语句的NOP处单击右键弹出菜单,选择“Toggle breakpoint”加入红色的断点,如下图所示;4.点击主菜单“View->Graph->Time/Frequency…”,屏幕会出现图形窗口设置对话框5.双击Start Address,将其改为y0;双击Acquisition Buffer Size,将其改为1;DSP Data Type设置成16-bit signed integer,如下图所示;6.点击主菜单“Windows->Tile Horizontally”,排列好窗口,便于观察7.点击主菜单“Debug->Animate”或按F12键动画运行程序,即可观察到实验结果:心得体会:通过对演示实验的练习,让自己更进一步对CCS软件的运行环境、编译过程、装载过程、属性设置、动画演示、实验结果的观察有一个醒目的了解和熟悉的操作方法。

熟悉了DSP实验箱基本模块。

让我对DSP课程产生了浓厚的学习兴趣,课程学习和实验操作结合为一体的学习体系,使我更好的领悟到DSP课程的实用性和趣味性。

实验二基本算数运算2.1 实验目的和要求加、减、乘、除是数字信号处理中最基本的算术运算。

DSP实验注意事项 (2)

5、为了便于文件的管理,把要做的实验复制 到C盘的CCS安装目录里的myproject里面。 一般CCS在C盘的安装目录为ti5000或ti。 如做FFT实验时,要复制D盘ti5416里面的 FFT文件夹: D:\TI5416\FFT -> C:\ti5000\myproject的文件夹路 径包含到预处理里面,编译程序会搜索这个路 径,找到片上外设驱动程序。 具体做法是:单击菜单栏上Project ->Build options->Compiler 选择Preprocessor,把驱动程序的路径填入 “Include search path”中。驱动程序已经放 在C:\ti\myprojects\JXXY_DRIVER里面。这 时要填入的路径是 C:\ti\myprojects\JXXY_DRIVER。路径不同 请做相应的修改。

1、除了按键和开关之外,尽量不要触 摸实验箱。不要碰DSP芯片。 2、实验箱电源的开关顺序。先插上总 电源,再按箱上的总开关,然后开5v 的LED电源,最后开芯片的3.5v电源 (从右到左)。如果关闭,则顺序相 反。

3、每人固定使用一台电脑。 开机时,如有需要选择用户名,则请 进入用户名为user的 4、文件夹说明 C:\ti5000--CCS的安装目录 (备注:如果没有ti5000这一目录,请 找ti目录) D:\ti5416--实验箱配套的程序目录

6、如出现异常不能调试,请复位CPU。做法 是按菜单栏Debug->reset CPU,之后要 重新加载程序。如果再不行,先关掉CCS, 然后断掉实验箱的电源进行热复位。打开 电源,重新启动CCS。

DSP原理与应用实验2DSP 数据存取实验

课程名称DSP原理与应用

实验序号实验2

实验项目DSP 数据存取实验实验地点

实验学时实验类型

指导教师实验员

专业班级

学号姓名

年月日

1、装载程序memory.out,进行调试。

运行到main 函数入口:

2、修改程序区的存储单元:

修改前:

此时入口地址为10801200,数据地址为01BCD4F6

修改中:

注意:修改前面的入口地址之后,一定要重新设置数据存储地址修改后:

当前语句被改成了“NOP”。

将地址0x10801200 上的数据改回0x01BCD4F6,程序又恢

复成原样。

3、断点调试:

(1)、运行到第一个断点:

我们可以memory 窗口中从0x80000080 开始的16 个单元的值被写入0x00000000 到0x0000000。

(2)、运行到第二个断点:

我们可观察到memory 窗口中从0x80000100 开始分16 个单元中的值被均被写入0x00001234。

(3)、运行到第三个断点:

我们可以观察到0x80000080 开始的16 个单元的值复制到以0x80000100 开始的16 个单元,数据发送了变化,因此数据颜色变为红色。

DSP实验二时域采样和频域采样实验报告

数字信号处理实验报告实验二时域采样和频域采样班级: 电子信息工程16 姓名:**学号: ********** 2018年 10 月 17 日一、实验目的时域采样理论与频域采样理论是数字信号处理中的重要理论。

要求掌握模拟信号采样前后频谱的变化,以及如何选择采样频率才能使采样后的信号不丢失信息;要求掌握频率域采样会引起时域周期化的概念,以及频率域采样定理及其对频域采样点数选择的指导作用。

二、实验原理与方法1、时域采样定理的要点a) 对模拟信号)(t x a 以间隔T 进行时域等间隔理想采样,形成的采样信号的频谱)(ˆΩj X 是原模拟信号频谱()aX j Ω以采样角频率s Ω(T s /2π=Ω)为周期进行周期延拓。

公式为:)](ˆ[)(ˆt xFT j X a a =Ω )(1∑∞-∞=Ω-Ω=n s a jn j X T b) 采样频率s Ω必须大于等于模拟信号最高频率的两倍以上,才能使采样信号的频谱不产生频谱混叠。

利用计算机计算上式并不方便,下面我们导出另外一个公式,以便用计算机上进行实验。

理想采样信号)(ˆt x a 和模拟信号)(t x a 之间的关系为: ∑∞-∞=-=n a a nT t t x t x)()()(ˆδ对上式进行傅立叶变换,得到:dt e nT t t x j X t j n a a Ω-∞∞-∞-∞=⎰∑-=Ω])()([)(ˆδ dt e nT t t x t j n a Ω-∞-∞=∞∞-∑⎰-)()( δ=在上式的积分号内只有当nT t =时,才有非零值,因此:∑∞-∞=Ω-=Ωn nT j aae nT xj X )()(ˆ上式中,在数值上)(nT x a =)(n x ,再将T Ω=ω代入,得到:∑∞-∞=-=Ωn nj aen x j X ω)()(ˆ上式的右边就是序列的傅立叶变换)(ωj eX ,即T j a e X j X Ω==Ωωω)()(ˆ上式说明理想采样信号的傅立叶变换可用相应的采样序列的傅立叶变换得到,只要将自变量ω用T Ω代替即可。

DSP实验报告

DSP实验报告02071445张渊实验一—VISUALDSP++的使用入门实验目的熟悉VISUAL DSP++的开发环境。

针对ADSP-Blackfin533 DSP,利用几个用C、C++和汇编语言写成的简单例子来描述VISUAL DSP+十编程环境和调试器(debugger)的主要特征和功能。

对于运行在其它类型Blackfin处理器的程序只需对其链接描述文件(.LDF)做一些修改,就可用于其它芯片或者ADSP-Blackfin533的硬件仿真。

实验内容一、练习一1. 实验步骤l) 进入Visual DSP+十并打开一个工程(Project)进入Visual DSP++,显示Visual DSP++的集成开发和调试环境窗口(Integrated Development and Debugger Environment,简称IDDE)。

装载dotprodc工程,并列出相应的源文件。

在输出窗口(Output Window)中显示简要信息。

2) 编译dotprodc工程在菜单Project中选择Build Project来对工程进行编译。

在本例子中,编译器检测到一个未定义的错误,显示为:“.\dotprod_main.c”,line 115:error #20:identifier“itn”is undefined itn i;在输出窗口中对该行文字用鼠标双击,环境会自动打开dotprod_main.c文件,并将光标定位在出错行。

你可以看见单词“int”被错写成“itn”。

将该错误改正后,保存并重新编译。

如果再没有错误出现,这时工程已被成功编译,就可以用VisualDSP++的debugger来调试程序。

3) 运行VsualDSP++调试器在调试过程中需定义不同的对象和处理器类型,选取菜单Sessions中NeW Session项来重新定义。

NeW Session 对话框图7.2所示:4) 运行dotprod.c从Debug菜单中选择Run项,程序将被执行,其输出结果在Output window中显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信号与信息处理综合实验(DSP部分)学院:信息与通信工程学院班级:2013211125姓名:商晴庆学号:班内序号:组号:2016年4月实验二 FFT的实现一、实验目的(1)进一步熟悉DSK6416开发平台,掌握调试功能;(2)充分理解FFT过程,并编码实现功能。

二、程序功能(1)基础:将FFT结果写入SDRAM中,并读取出来。

(2)提高:其他点数的FFT三、模块描述(1)GBLCTL寄存器配置部分:static EMIFA_Config MyEmifaConfig ={EMIFA_GBLCTL_RMK(EMIFA_GBLCTL_EK2RATE_FULLCLK, //1 X EMIF input clockEMIFA_GBLCTL_EK2HZ_CLK, //eclkout2 continue output during holdEMIFA_GBLCTL_EK2EN_ENABLE, //eclkout2 enable outputEMIFA_GBLCTL_BRMODE_MRSTATUS, //bus request is memory access or refresh pending/in progressEMIFA_GBLCTL_NOHOLD_DISABLE,EMIFA_GBLCTL_EK1HZ_CLK, //eclkout1 continue output during holdEMIFA_GBLCTL_EK1EN_ENABLE, //eclkout1 enable outputEMIFA_GBLCTL_CLK4EN_ENABLE, //clkout4 output enableEMIFA_GBLCTL_CLK6EN_ENABLE //clkout6 output enable),(2)CECTL0-3寄存器配置部分0xffffffd3, //64BIT SDRAM0xffffffe3,0x22a28a22,0x22a28a22,(3)SDCTL寄存器配置部分EMIFA_SDCTL_RMK(EMIFA_SDCTL_SDBSZ_4BANKS, //SDRAM bank size 4 banksEMIFA_SDCTL_SDRSZ_11ROW, //row number = 11EMIFA_SDCTL_SDCSZ_8COL, //column number = 8EMIFA_SDCTL_RFEN_ENABLE, //SDRAM refresh enable//EMIFA_SDCTL_INIT_NO, //SDRAM 配置完每个CE空间后,不初始化EMIFA_SDCTL_INIT_YES, //SDRAM 配置完每个CE空间后,初始化EMIFA_SDCTL_TRCD_OF(2), //TRCD = (Trcd / Tcyc) - 1EMIFA_SDCTL_TRP_OF(2), //TRP = (Trp / Tcyc) - 1,3个EMIFA_SDCTL_TRC_OF(8),EMIFA_SDCTL_SLFRFR_DISABLE //self refresh mode disable),(4)SDTIM寄存器配置部分EMIFA_SDTIM_RMK(EMIFA_SDTIM_XRFR_DEFAULT, //EXT TIMER defaultEMIFA_SDTIM_PERIOD_OF(2083) //refresh period,clockout1 = 10ns),EMIFA_SDEXT_RMK(EMIFA_SDEXT_WR2RD_OF(0), //cycles between write to read command = 1,subtract 1 is 0EMIFA_SDEXT_WR2DEAC_OF(1), //cycles between write to precharge = 2EMIFA_SDEXT_WR2WR_OF(1), //cycles between write to write = 2EMIFA_SDEXT_R2WDQM_OF(1), //cycles between read to bex = 2EMIFA_SDEXT_RD2WR_OF(0), //cycles between read to write = 1EMIFA_SDEXT_RD2DEAC_OF(1), //EMIFA_SDEXT_RD2RD_OF(0), //EMIFA_SDEXT_THZP_OF(2), //Troh = 3 cycleEMIFA_SDEXT_TWR_OF(1), //Twr = 1 clock +6 nsEMIFA_SDEXT_TRRD_OF(0), //Trrd = 12nsEMIFA_SDEXT_TRAS_OF(5), //Tras = 42nsEMIFA_SDEXT_TCL_OF(1) //cas latency = 3 clock),(5)CE0SEC~CE3SEC寄存器配置部分0x00000002,0x00000002,0x00000002,0x00000002(6)数据空间分配部分#pragma DATA_SECTION(sdram_data,".off_ram");unsigned int sdram_data[0x10000];//extern far void vectors();(7)主函数部分void main(){//int out[NUMSAMPLES];DSK6416_init();CSL_init(); //初始化CSLEMIFA_config(&MyEmifaConfig);//配置EMIFAint i;i = 0;short w[2*N] = {0};int x[2*N];int y[2*N] = {0};int m[N];double scale = 32767.5;gen_twiddle(w, N, scale);for(i=0; i<N; i++){x[2*i] = 1000 * cos(i*PI/32) + 1000*cos(i*PI/16);x[2*i + 1] = 0;sdram_data[2*i] = x[2*i];sdram_data[2*i + 1] = x[2*i +1];}// fftDSP_fft16x32(w,N,x,y);// 存储幅值for(i = 0; i < N; i++){m[i] = y[2*i] * y[2*i] + y[2*i + 1] * y[2*i + 1];sdram_data[i + 2*N] = m[i];}// 检测写入是否成功for(i=0; i<N; i++){if(sdram_data[i+ 2*N]!=m[i])break;}if(i == N){DSK6416_LED_on(0);DSK6416_LED_on(2);DSK6416_LED_on(1);}}static short d2s(double d){if (d >= 32767.0) return 32767;if (d <= -32768.0) return -32768;return (short)d;}int gen_twiddle(short *w, int n, double scale){int i, j, k;for (j = 1, k = 0; j < n >> 2; j = j << 2){for (i = 0; i < n >> 2; i += j){w[k + 5] = d2s(scale * cos(6.0 * PI * i / n));w[k + 4] = d2s(scale * sin(6.0 * PI * i / n));w[k + 3] = d2s(scale * cos(4.0 * PI * i / n));w[k + 2] = d2s(scale * sin(4.0 * PI * i / n));w[k + 1] = d2s(scale * cos(2.0 * PI * i / n));w[k + 0] = d2s(scale * sin(2.0 * PI * i / n));k += 6;}}return k;}四、程序流程图(1)FFT流程图(2)SDRAM写入和检测五、功能测试FFT结果:六、组内分工(1)商晴庆主要负责基础工程的搭建,并且完成了各种寄存器的配置;(2)赵建博主要负责分析FFT功能实现部分;(3)对于实验中出现的问题,两人共同分析解决。

七、问题分析(1)预计出现FFT结果时,图像显示为空。

解决方法:同时设置了两个断点,使运行时,两次都走到第一断点处停止,故没有得到正确的FFT结果,后来先设置一个断点运行一次,再设置另一断点后运行一次,顺利得到FFT的结果。

(2)运行后LED灯不亮。

解决方法:同样是因为断点设置的问题,后先后设置两个断点后,问题顺利解决。

八、心得体会通过本次实验,对CCS软件的使用和功能有了更进一步的了解。

由于有了第一次DSP实验的练习,对前期整个工程的路径配置就熟练了很多,很快就完成了前期操作。

这次实验要求我们明确掌握FFT的基本原理和具体实现。

由于对课本知识复习的不够,在具体实现时遇到了一点困难,觉得无从下手,实验过程中通过仔细研究FFT的原理,顺利完成了实验要求。

另外,实验中CCS软件断点设置部分的小插曲拉慢了我们实验过程,导致最后的结果迟迟出不来,我们要从中吸取教训,不能急,要一步一步来,另外要更加了解CCS功能的正确使用。

作为小组实验,我的队友在解决问题的过程中发挥了很大的作用,不慌不忙,有问题及时请教身边的同学。

在这种小组合作的实验中,我的综合素质有了提高,希望在今后的实验中可以学到更多。