硬件课程设计报告_基于RISC处理器结构的模型机

实验一 简化的RISC_CPU设计

5、状态控制器

指令周期是由8个时钟组成,每个时钟都要完成固定的操作: 第6个时钟:空操作。此时如果操作为STO,datactl_ena 为1;如果操作为ADD,ANDD,XORR和LDA,则rd为 1,否则个控制信号全为0; 第7个时钟:若操作符为SKZ且累加器值为0,则PC值再 增1(即inc_pc变为1),跳过一条指令,否则PC无变化。

3

2、 什么是CPU

CPU即中央处理单元的缩写,它是计算机的核 心部件。计算机进行信息处理可分为两个步骤: (1)将数据和程序(即指令序列)输入到计算机 的存储器中; (2)从第一条指令的地址起开始执行该程序,得 到所需结果,结束运行。

4

2、 什么是CPU

CPU的作用是协调并控制计算机的各个部件并 执行程序的指令序列,使其有条不紊地进行。因此 它必须具有以下基本功能: • 取指令:当程序已经在存储器中时,首先根据程 序入口地址取出一条程序,为此要发出指令地址及 控制信号。 • 分析指令:即指令译码,这是对当前取得的指令 进行分析,指出它要求什么操作,并产生相应的操 作控制命令。 • 执行指令:根据分析指令时产生的“操作命令”形 成相应的操作控制信号序列,通过运算器、存储器 及输入/输出设备的执行,实现每条指令的功能,其 中包括对运算结果的处理以及下条指令地址的形成。

18

模块3

累加器

19

模块三 累加器

累加器用于存放当前的结果,它也是双目运算 中的一个数据来源; 复位后,累加器的值是零; 当累加器通过ena口收到来自CPU状态控制器 load_acc信号时,在clk1时钟正跳沿时就收到来自 于数据总线的数据。

20

模块4

算数运算器

21

模块四 算术运算器

计算机组成原理课程设计报告(基本模型机设计与实现)

本科生课程实习学生姓名学生学号所在专业所在班级指导教师职称时间成绩目录一、课程设计题目 (2)二、课程设计使用的实验设备 (2)三、课程设计内容与步骤 (2)1、所设计模型机的功能与用途 (3)2、数据通路图 (4)3、微代码定义 (4)4、微程序流程图 (5)5、微指令二进制代码 (6)6、本课程设计机器指令 (7)7、模型机的调试与实现 (7)(1)接线图 (7)(2)写程序 (8)(3)运行程序 (8)四、总结 (9)参考文献 (9).一、课程设计题目基本模型机设计与实现二、课程设计使用的实验设备TDN-CM计算机组成原理教学实验系统一台,排线若干三、课程设计内容与步骤不见实验过程中,各部件单元的控制信号是认为模拟产生的,而本次课程实习将能在为程序控制下自动产生各部件单元控制信号,实现特定指令的功能。

这里,计算机数据通路的控制将由微程序控制器来完成,CPU从内存中取出一条机器指令到指令执行结束的一个指令周期全部由微指令组成的序列来完成,即一条机器指令对应一个微程序。

本课程设计采用六条机器指令:IN(输入)、AND(与运算)、DEC(自增1)、STA(存数)、OUT(输出)、JMP(无条件跳转),其指令格式如下:其中IN、DEC为单字长,其余为双字长指令,********为addr对应的二进制地址码。

1、所设计模型机的功能与用途本次课程设计设计的模型机包括六条指令,输入、与运算、自增、存数、输出、无条件跳转。

利用此模型机可完成两个数的与运算,一个数从键盘输入,另个数从内存中读取,再将运算结果自增1,把最后结果保存到内存中,并且将运算结果输出2、数据通路图3、微代码定义C字段A字段B字段4、微程序流程图控制程序流程图当拟定“取指”微指令时,该微指令的判别测试字段为P(1)测试;控制台操作为P(4)测试,它以控制台开关SWB、SWA作为测试条件,共三路分支。

5、微程序设计完毕后,将每条微指令代码化,将流程图转化为二进制代码表6、本课程设计机器指令7、模型机的调试与实现(1)接线图(2)写程序A、现将机器指令对应的微代码正确写入2816中。

实验五:基于RISC处理器构成模型机实验

实验五基于RISC处理器构成模型机实验

一、实验目的

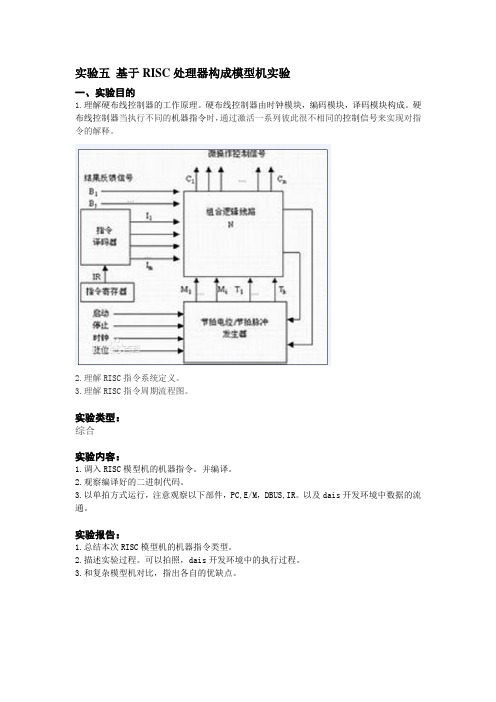

1.理解硬布线控制器的工作原理。

硬布线控制器由时钟模块,编码模块,译码模块构成。

硬布线控制器当执行不同的机器指令时,通过激活一系列彼此很不相同的控制信号来实现对指令的解释。

2.理解RISC指令系统定义。

3.理解RISC指令周期流程图。

实验类型:

综合

实验内容:

1.调入RISC模型机的机器指令。

并编译。

2.观察编译好的二进制代码。

3.以单拍方式运行,注意观察以下部件,PC,E/M,DBUS,IR。

以及dais开发环境中数据的流通。

实验报告:

1.总结本次RISC模型机的机器指令类型。

2.描述实验过程。

可以拍照,dais开发环境中的执行过程。

3.和复杂模型机对比,指出各自的优缺点。

计算机硬件课程设计--复杂模型机设计报告

计算机硬件课程设计--复杂模型机设计报告硬件课程设计复杂模型机设计报告一.实验目的:经过一系列硬件课程的学习及相关实验后,做一个综合的系统性的设计,这在硬件方面是一个提高,进一步培养实践能力。

二.实验内容:搭建一台8位模型机,指令系统要求有10条以上,其中包括运算类指令、传送类指令、控制转移类指令、输入输出指令、停机指令等。

三.实验思路:1、确定设计目标:确定所设计计算机的功能和用途。

2、确定指令系统:确定数据的表示格式、位数、指令的编码、类型、需要设计哪些指令及使用的寻址方式。

3、确定总体结构与数据通路:总体结构设计包含确定各部件设置以及它们之间的数据通路结构,列出各种信息传送路径以及实现这些传送所需要的微命令。

4、设计指令执行流程:数据通路确定后,就可以设计指令系统中每条指令的执行流程。

根据指令的复杂程度。

每条指令所需要的机器周期数。

对于微程序控制的计算机,根据总线结构,需要考虑哪些微操作可以安排在同一个微指令中。

5、确定微程序地址:根据后续微地址的形成方法,确定每条微程序地址及分支转移地址。

6、根据微指令格式,将微程序流程中的所有微操作进行二进制代码化,写入到控制存储器中的相应单元中。

7、组装、调试:在总装调试前,先按功能模块进行组装和分调,因为只有功能模块工作正常后,才能保证整机的运行正确。

四.实验原理:1.指令系统及指令格式:指令系统包括:算术逻辑运算指令、访存指令、控制转移指令、I/O指令、停机指令。

一般指令格式:OP-CODE RS RDDATA/ADDR00 M OPCODE RDDATA/ADDR指令系统如: ADD RS,RD MOV DATA,RDMOV RS,[ADDR] JZ ADDRIN RD HALT其中RS 、RD为R0、R1、R2中之一,DATA 为立即数,ADDR为内存地址。

2.微指令格式:WE A9 A80 0 0 INPUT0 0 1 RAM读1 0 1 RAM写1 1 0 LED,写接口0 1 1 无0 1 0 写接口3.微程序地址入口的形成:P(1)是用来译码指令寄存器的I7、I6、I5、I4 ,用于一般指令,微程序入口址为OP+10HP(2)是用来译码指令寄存器的I3、I2 ,用于不同寻址方式指令,入口地址转OP+20HP(3)是用来译码判断标志位C、Z ,用于条件转移指令,条件成立转OP+30H,条件不成立转OP+20HP(4)是用来译码控制台操作的SWB、SWA ,用于手动操作。

计算机组成原理课设报告(设计一台嵌入式CISC模型机)

计算机组成原理课程设计(论文)说明书题目:设计一台嵌入式CISC模型机系别:专业:学生姓名:学号:一.CISC 模型机数据通路框图总体设计如下二.操作控制器的逻辑框图外部时钟 复位信号指令寄存器IR三.模型机的指令系统3.1指令系统3.2本模型机中的指令系统中共有10条基本指令,下表列出了每条指令的格式、汇编符号和指令功能。

说明:①对Rs 和Rd 的规定:②模型机规定数据的表示采用定点整数补码表示,单字长为8位,其格式如下:3.3设计时序产生器电路T1、T2、T3、T4与CLR 、Q 之间的关系图四.微程序流程图Q CLR T1 T2 T3 T400五.编写汇编语言源程序由给出的题目(范例)和设计的指令系统编写相应的汇编语言源程序。

算法思想为:采用R0寄存器存放从开关输入的任意一个整数,R1存放准备参加累加运算的奇数,R2存放累加和,用一个循环程序实现如下:MOV R3,0MOV R2,0MOV R1,5L2:IN1 R0Test R0JS L1L3:INC R2CMP R2,R1JB L2L4:OUT1 R3JMP L4L1:CMP R0,R3JB L3MOV1 R0,R3JMP L3六.机器语言源程序根据设计的指令格式,将汇编语言源程序手工转换成机器语言源程序,并将其设计到模型机中的ROM中去。

与3.3.8中汇编语言源程序对应的机器语言源程序如下:助记符地址(十六进制)机器代码功能MOV R3,O 00 0001 0011 0→R3010000 000MOV R2,0 02 0001 0010 0→R203 0000 0000MOV R1,5 04 0001 0001 5→R105 0000 0101L2:IN1 R0 06 0000 0000 (SW) →R0Test R0 07 0111 0000 80H-ACJS L1 08 1000 0000 若SF=1 L1→PC09 0001 0001L3:INC R2 0A 0100 0010 (R2)+1→R2CMP R2,R1 0B 0110 1001 (R2)-(R1)JB L2 0C 1001 0000 L2→PCOD 0000 0110L4:OUT1 R3 0E 0011 1100 (R3)→LEDJMP L4 0F 0101 0000 L4→PC10 0000 1110L1:CMP R0,R3 11 0110 0011 (R0)-(R3)JB L3 12 1001 0000 L3→PC13 0000 1010MOV1 R0,R3 14 0010 0011 R0→R3JMP L3 15 0101 0000 L3→PC16 0000 1010七.机器语言源程序的功能仿真波形图及结果分析;输入数值: 85,05,83,87,89输出结果: 89结果分析:05是正数,判断为负直接跳出,83<85<87<89所以 89最大,与仿真波形图结果相同八.故障现象和故障分析1.问题:为微程序流程图分配首地址时出现错误,导致不能正确译码。

计算机硬件基于微程序的复杂模型机课程设计报告

硬件课程设计报告——基于微程序的复杂模型机设计硬件课程设计报告——基于微程序的复杂模型机设计一、硬件课程设计目的经过一系列硬件课程的学习及相关实验之后,做一个综合的系统性设计,这在硬件方面是一个提高,可进一步培养实践能力。

二、硬件课程设计内容搭建一台8位模型机,指令系统要求有10条以上,其中包括运算类指令、传送类指令、控制转移类指令、输入输出指令、停机指令等。

三、指令系统列表采用的一般指令格式为:7 4 3 2 1 0四、微操作流程图R1->BUSR1->BUS BUS->DR2 R1->BUS BUS->DR2 R1->BUS五、验证程序IN R0MOV R1,05HADD R1,R0MOV R1,[R0]SUB R0,R1JNZ P1MOV [R0],R0AND R0,R1P0: OUT R0P1: OR R0,R1JMP P0六、机器指令及微程序机器指令如下:$P0000 ; IN R0$P0121$P0205 ; MOV R1,05H$P0354 ; ADD R1,R0$P0441 ; MOV R1,[R0]$P0531 ; SUB R0,R1$P0660$P0731 ; JZ(JC)$P0870 ; MOV[R0],R0$P0984 ; AND R0,R1$P0A10 ; OUT R0$P3132 ;JZ(YES)$P3294 ;OR R0,R1$P33A0$P340A ;JMP微指令如下:$M00018001 ;00→01$M0101ED82 ;PC→AR,PC+1$M0200C050 ;RAM→BUS,BUS→IR,P(1)$M10001001 ;INPUT→R0$M1201ED83 ;PC→AR,PC+1$M03009001 ;RAM→BUS,BUS→R1$M1301A404 ;R0→BUS,BUS→DR1$M0401B205 ;R1→BUS,BUS→DR2$M05619A01 ;DR1减DR2→R0$M1401E206 ;R0→BUS,BUS→AR$M06000901 ;RAM→BUS,BUS→R1$M1501A407 ;R1→BUS,BUS→DR1$M0701B208 ;R0→DR2,BUS→DR2$M08959B41 ;DR1加DR2→R1$M1601ED89 ;PC→AR,PC+1$M0900E0E0 ;RAM→BUS,BUS→AR,P(3)$M3000D181 ;RAM→BUS,BUS→PC$M20018001 ;空操作$M1701E20A ;R0→BUS,BUS→AR$M0A028401 ;R0→BUS,BUS→RAM$M1801A40B ;R0→BUS,BUS→DR1$M0B01B20C ;R1→BUS,BUS→DR2$M0CB99A01 ;DR1DR2→R0$M1901A40D ;R0→BUS,BUS→DR1$M0D01B20E ;R1→BUS,BUS→DR2$M0EE99A01 ;DR1+DR2→R0$M1A01ED8F ;PC→AR,PC+1$M0F00D181 ;RAM→BUS,BUS→PC$M11030201 ;R0→OUTPUT七、实验截图八、心得体会实验总体来说还是比较容易的,就是在输入微程序和老师的测试程序时比较费力,弄不好又要重新输入(后来听说可以使用软件直接烧制)。

硬件课设-微型复杂模型机

南京理工大学硬件课程设计(I)实验报告学院:计算机科学与工程学院专业:计算机科学与技术姓名:姜茜学号:912106840208姓名:付艳荣学号:912106840109一、课程设计目的综合运用所学计算机原理知识,设计并实现较为完整的计算机。

经过一系列硬件课程的学习及相关实验后,做一个综合的系统性的设计,这在硬件方面是一个提高,进一步培养实践能力。

二、课程设计要求搭建一台8位模型机,指令系统要求有10条以上,其中包括运算类指令、传送类指令、控制转移类指令、输入输出指令等,并且有各种不同的寻址方式。

数据格式及指令系统1、数据格式模型机规定采用定点补码表示法表示数据,且字长为8位,其格式如下:其中第7位为符号位,数值表示范围是:-1≤X<1。

2、指令格式模型及设计三大类指令共十五条,其中包括运算类指令、控制转移类指令、数据传送类指令。

指令系统应包括:算术逻辑运算指令、访存指令、控制转移指令、I/O指令。

指令格式如下:所有单字节指令(ADD、AND、INC、SUB、OR、RR、HLT 和 MOV)格式如下:其中,OP-CODE 为操作码,RS为源寄存器,RD为目的寄存器,并规定:IN和 OUT 的指令格式为:其中括号中的 1 表示指令的第一字节,2 表示指令的第二字节,OP-CODE 为操作码,RS为源寄存器,RD 为目的寄存器,P 为 I/O 端口号,占用一个字节。

系统设计五种数据寻址方式,即立即、直接、间接、变址和相对寻址。

其中M 为寻址模式,具体见下表,以 R2 做为变址寄存器 RI。

三、课程设计内容1、指令系统列表2、微操作流程图序号 汇编指令OP-CODERS RD P/D 功能1 IN R0,P 0000 / 00 P 从端口P 输入数据到R02 MOV R0,R2 0001 00 10 / 将R0寄存器值移动至R1寄存器3 ADD R1,R0 0010 01 00 / R0+R1值送到R14 SHL R0 0011 / 00 / R0值左移一位5LOAD R0,[R2+5] 0100 00 [R2+15] /将R0的值放到[R2+15]的内存地址空间6 AND R0,R1 0101 00 02 / R0,R1逻辑与送到R17 JMP 0BH 0110 / / / 跳转指令,跳到0BH 处8 OUT P,R0 0111 00 / P 把R0数据输出到端口P9 INC R1 1000 / 01 / R1寄存器值自增110 STORE [40H],R0100100[40H]/将R0的值存入内存的40H 单元3、微程序列表//** Start Of MicroController Data **//$M 00 000001 $M 01 006D42 $M 02 107050 //IN 指令$M 03 106004 $M 04 183001 //MOV 指令$M 06 00B401 //ADD 指令$M 08 002409 $M 09 04B201 //SHL 指令$M 0B 03B201NOPPA-〉AR PC+1-〉ARMEM-〉P<1>P->A RI/O-> R0R0->R2R0-.>ALU -AA+B->R 1A+B->R 1左移一位R0-.AL U-APC->AR PC+1->MEM-.>AL U-A R1->ALU-BR0-.>ALU -AA+B->R1MEM->R0PC->AR PC+1->R1->ALU-P->A RMEM->PCPC->AR PC+1->PR0->I/OA+1->R1MEM->ARR0->MEM$M 0C 002413//LOAD指令$M 0D 00980E$M 0E 006D4F$M 0F 10A020$M 20 04E221$M 21 10B001//AND指令$M 23 002424$M 24 013201$M 25 200626//JMP指令$M 26 105141//OUT指令$M 28 106029$M 29 280401//INC指令$M 2B 06B201//STORE指令$M 2D 006D6E$M 2E 10602F$M 30 006D44$M 31 001606$M 32 001607$M 33 001609$M 34 001410$M 35 001612$M 36 006C14$M 37 006C15$M 38 006D57$M 39 006D5A$M 3A 006D60$M 3B 006D50$M 3C 006D5C$M 3D 006D5E$M 3E 006D68$M 3F 006D6C; //** End Of MicroController Data **// 4、验证程序//***** Start Of Main Memory Data *****// $P 00 00(1)IN R0,P 从端口P输入数据到R0$P 01 00(2)MOV R0,R2 将R0寄存器值移动至R2寄存器$P 02 12(3)ADD R0,R1 R0+R1值送到R1$P 03 21(4)SHL R0 R0值左移一位$P 04 30(5)LOAD [R2+5] ,R0 将[R2+5]的值放到R0的内存地址空间$P 05 40$P 06 0F(6)AND R0,R1 R0,R1逻辑与送到R1$P 07 51(7)JMP 0BH 跳转指令,跳到0BH处$P 08 60$P 09 0B(8)OUT P,R0 把R0数据输出到端口P$P 0B 70$P 0C 47(9)INC R1 R1寄存器值自增1$P 0D 85(10)STORE [40H],R0 将R0的值存入内存的40H单元$P 0E 90$P 0F 40; //***** End Of Main Memory Data *****//四、课程设计总结从最开始做实验,我们就逐渐体会到了硬件课设的魅力所在,首先接线方面稍不留意就会造成打错,所以对我们严谨求实的态度有了新的要求,同时也对计算机这门学科有了新的认识:软件与硬件的统一、程序与电路的融合。

计算机硬件课程设计报告--基于微程序的复杂模型机设计

计算机硬件课程设计报告--基于微程序的复杂模型机设计硬件课程设计报告——基于微程序的复杂模型机设计一、实验目的经过一系列硬件课程的学习及相关实验后,做一个综合的系统性的设计,这在硬件方面是一个提高,进一步培养实践能力。

二、实验内容搭建一台8位模型机,指令系统要求有10条以上,其中包括运算类指令、传送类指令、控制转移类指令、输入输出指令、停机指令等。

三、设计思路1.确定设计目标:确定所设计计算机的功能和用途。

2.确定指令系统:确定数据的表示格式、位数、指令的编码、类型、需要设计哪些指令及使用的寻址方式。

3.确定总体结构与数据通路:总体结构设计包含确定各部件设置以及它们之间的数据通路结构,列出各种信息传送路径以及实现这些传送所需要的微命令。

4.设计指令执行流程:数据通路确定后,就可以设计指令系统中每条指令的执行流程。

根据指令的复杂程度。

每条指令所需要的机器周期数。

对于微程序控制的计算机,根据总线结构,需要考虑哪些微操作可以安排在同一个微指令中。

5.确定微程序地址:根据后续微地址的形成方法,确定每条微程序地址及分支转移地址。

6.根据微指令格式,将微程序流程中的所有微操作进行二进制代码化,写入到控制存储器中的相应单元中。

7.组装、调试:在总装调试前,先按功能模块进行组装和分调,因为只有功能模块工作正常后,才能保证整机的运行正确。

四、指令系统列表指令系统应包括:算术逻辑运算指令、访存指令、控制转移指令、I/O指令、停机指令。

一般指令格式:模型机的指令系统:四、 微操作流程图0POAD JM STORLOAMOV00六、实现程序$P0030 $P0140 $P0201 $P0335 $P0450 $P0511 $P0625 $P0760 $P0861 $P0955 $P0A90 $P0B90 $P0C80$P0D03$P0E70$P0F00$P1080$P1101$P1240$P1300七、微指令$M00018001 $M0101ED82 $M0200C050 $M1301ED85 $M0500E006 $M06009001 $M10019201 $M1101A203 $M0301B404 $M04959A01 $M1201ED87 $M0700E008$M08028201 $M1601A209 $M0901B40A $M0A699A01 $M1531820B $M0B11880C $M0C019801 $M1401ED8D $M0D00D181 $M1901ED8E $M0E009001 $M1701ED8F $M0F00E020 $M20011001 $M1801EDA1 $M2100E022 $M22030201八、截图Read r0Mov r0,r1Read r1Add r0,r1Xor r0,r1Rcl r1Mov 90h,r0Out r003HIn r0 00hOut r0 01hJmp 00h九、心得体会硬件课程设计,从开始做的时候一片迷茫,到通过请教同学和查询书本而一点点的变清晰,再到最后自己做出来感觉很有成就感。

关于RISC实验报告

实验名称:基于RISC技术的模型计算机设计一、实验目的:1.了解精简指令系统计算机(RISC)和复杂指令系统九三级(CISC)的体系结构特点和区别。

前面组成原理部分的“复杂模型机”是基于复杂指令系统(CISC)设计的模型机,本书中所提到的复杂指令系统计算机可参照组成原理部分的“复杂模型机”来理解2.掌握RISC处理器的指令系统特征和一般设计原则二、实验设备:PC机一台,TD-CMA实验系统一套三、实验内容:1.指令系统设计本实验采用RISC思想设计的模型机选用常用的五条指令:MOV、ADD、LOAD、STORE、JMP作为指令系统,寻址方式采用寄存器查询制及直接寻址两种方式。

指令格式采用单字节及双字节两种格式:单字节指令(MOV、ADD、JMP、SUB)格式如下:7 6 5 4 3 2 1 0OP-CODE RS RD 其中,OP-CODE为操作码,RS为源寄存器、RD为目的寄存器,并规定:RS或RD 选定的寄存器00 R001 R110 R211 A双字节指令(LOAD、SA VE)格式如下:7 6 5 4 (1) 3 2 (1) 1 0 (1) 7-0(2)OP-CODE RS RD P根据上述指令个是,列出本模型机的五条机器指令的具体格式、汇编符号和指令功能:操作码指令名0 0 0 0 MOV0 0 0 1 ADD0 0 1 0 SUB0 1 0 0 JMP1 0 0 0 LOAD0 1 1 1 STA2.RISC处理器的模型计算机系统设计3.控制器设计四、实验原理图:数据通路图:指令周期流程图:PC->ARMOVADDS1运行微程序S1LOADSAVEJMPRAM->IRS1PC->AR RAM->ARRS->RD PC+1PC->ARRAM->ARRS->PC T1T2T4T1T2T3PC+1RS->B RS->RAM S1S1T3T4ALU->RDPC+1PC+1RS->RDPC+1PC+1S1五、VHDL 程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY RISC ISPORT(T1,T2,T3,T4,I7,I6,I5,I4,I3,I2,I1,I0,CLR,Q:IN STD_LOGIC;LDR0,LDR1,LDR2,R0_B,R1_B,LD,R2_B,PC_B,LDAR,IOM,RD,WR,LDIR,LDPC,LDAC,LDD R,ALU_B: OUT STD_LOGIC;S:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY RISC;ARCHITECTURE ART OF RISC ISSIGNALMOV,ADD,JMP,LOAD,STA,SUB,RS_B,LDRi,F,CLK,CLK11,M1,M2,M3,M4:STD_LOGIC; BEGINM1<=Q AND T1;M2<=Q AND T2;M3<=Q AND T3;M4<=Q AND T4;MOV<=(NOT I7)AND(NOT I6)AND(NOT I5)AND(NOT I4);ADD<=(NOT I7)AND(NOT I6)AND(NOT I5)AND(I4);SUB<=(NOT I7)AND(NOT I6)AND(I5)AND(NOT I4);JMP<=(NOT I7)AND(I6)AND(NOT I5)AND(NOT I4);LOAD<=(I7)AND(NOT I6)AND(NOT I5)AND(NOT I4);STA<=(NOT I7)AND(I6)AND(I5)AND(I4);CLK11<=(LOAD OR STA)AND T4;SS0:PROCESS(ADD,SUB)BEGINIF ADD='1' THEN S<="1001";ELSE S<="1011";END IF;END PROCESS;SS1: PROCESS(CLK11,CLR)BEGINIF CLR='0' THEN F<='0';ELSIF (CLK11'EVENT AND CLK11='0') THEN F<=NOT F;END IF;END PROCESS;SS2: PROCESS(CLR,T1,T2,T3,LOAD,F,STA)BEGINIF CLR='0' THEN RD<='0';WR<='0';ELSE RD<=(T2 AND(NOT F)) OR ( T1 AND( LOAD OR STA)AND F)OR (T2 AND LOAD AND F);WR<=T3 AND STA AND F;END IF;END PROCESS;PC_B<=NOT( (T1 AND (NOT F) )OR ((LOAD OR STA)AND T4 AND (NOT F)));ALU_B<=NOT((ADD OR SUB) AND T4);RS_B<=NOT(((MOV OR ADD OR JMP OR SUB)AND T3 AND (NOT F)) OR (STA AND T3 AND F));LD<=NOT(T3 AND JMP AND (NOT F));IOM<=NOT( T2 OR (T1 AND (LOAD OR STA) AND F)OR (T3 AND STA AND F) );LDPC<=(M3 AND (NOT F))OR (M3 AND (LOAD OR STA)AND F );LDDR<=(ADD OR SUB) AND M3 AND (NOT F);LDIR<=M2 AND (NOT F);LDAR<=M1 OR ((LOAD OR STA)AND (NOT F)AND M4) OR(M1 AND(LOAD OR STA)AND F);LDRi<=((ADD OR SUB) AND M4 AND (NOT F))OR (LOAD AND M2 AND F) OR (MOV AND M3 AND (NOT F));R0_B<=RS_B OR ( I3) OR ( I2);R1_B<=RS_B OR ( I3) OR (NOT I2);R2_B<=RS_B OR (NOT I3) OR ( I2);LDAC<=LDRi AND (I1) AND (I0);LDR0<=LDRi AND (NOT I1) AND (NOT I0);LDR1<=LDRi AND (NOT I1) AND (I0);LDR2<=LDRi AND (I1) AND (NOT I0);END ARCHITECTURE ART;六、实验步骤:1.编译,编辑所设计的CPLD芯片程序,并配置引脚打开Quartus Ⅱ,选择File→New Project Wizard,输入目标路径,工程名及顶层设计实体名,区分大小写。

1、基于RISC处理器构成模型计算机实验

1、基于RISC 处理器构成模型计算机实验一.实验目的1.了解精简指令系统计算机(RISC)和复杂指令系统计算机(CISC)的体系结构特点和区别。

2.掌握 RISC 处理器的一般设计原则和指令系统特征。

二.实验设备1.TDN-CM++教学实验系统一台。

2.PC 微机一台。

三.实验原理(一)本实验中 RISC 处理器指令系统的定义1.选用使用频度比较高的五条基本指令:MOV、ADD、STORE、LOAD、JMP2.寻址方式采用寄存器寻址及直接寻址两种方式。

3.指令格式采用单字长及双字长两种格式:其中 Rs、Rd 为不同状态,则选中不同寄存器:MOV、ADD、JMP 三条指令为单周期执行完成。

STORE、LOAD 两条指令为两周期执行完成,A 为存或取数的直接地址。

第一机器周期完成取操作码、作标记;第二机器周期完成取直接地址并完成取数或存数。

(二)本实验 RISC 处理器的设计与实现1.本处理器的时钟及节拍电位如图 1-1 所示图1-1 时序电路图2.本模型机采用的数据通路图如图 1-2 所示:图1-23.本通路中除 PLD 单元由 CPLD 来设计,其他单元全是由板上的单元电路来实现。

4.指令周期流程图如图 1-3 所示:5.本实验指令系统如下:6.本实验为方便用实验装置上的显示灯来观察结果,将 RISC 处理器中的地址寄存器等都是用板上的单元电路来构成,只将上述数据框图中的 PLD 模块由 CPLD 来实现。

只要将时序信号 TS1-TS4 引入 CPLD 既可。

将存储器 RAM 、CPLD 构成的处理器的外总线都挂至总线单元,既构成一基本完整的精简指令系统(RISC )计算机。

图1-3(三)CPLD 芯片设计程序1.顶层模块电路图(top.sch):见图 1-4。

2.用 ABEL 语言设计 PLD 子模块的功能描述程序。

四.实验步骤1.编译所设计的程序,将生成的 JED 文件下载至 CPLD 芯片 ispLSI1032 中。

计算机硬件课程设计——基于微程序的复杂模型机设计

计算机硬件课程设计---基于微程序的复杂模型机设计一、实验题目:设计一台有微程序控制的8位模型机,指令系统要求达到10条指令以上。

二、实验目的:(1)在掌握部件单元电路实验的基础上,进一步将其组成系统,构造一台复杂模型计算机,建立一台基本完整的整机。

(2)为其定义至少十条机器指令,并编写相应的微程序,通过联机调试,观察计算机执行指令:从取指令、指令译码、执行指令等过程中数据通路内数据的流动情况,进一步掌握整机概念。

三、实验设备:TDN-CM+教学实验系统一套、PC微机一台四、实验原理与指令设计:(1)实验原理:①数据格式模型机规定数据采用定点整数补码表示,字长为8位,其格式如下:其中,第7位为符号位,数值表示范围是-27 ≤X≤27-1②机器指令格式单字节指令寻址方式采用寄存器直接寻址,其格式如下:双字节指令采用直接寻址,其格式如下其中,OP-CODE为操作码,RS为源寄存器,RD为目标寄存器,并规定:③微指令格式:其中,A、B、C三个字段的编码方案如下表:WE,A9,A8三个字段编码方案如下:运算器逻辑功能表(2)指令设计:模型机可设计4大类指令共16条,其中包括算术逻辑指令、访存指令、控制转移指令、I/O指令、停机指令。

我们设计的十条指令及其操作码与指令格式如下所示:指令代码指令格式功能IN Rd 0000 xxRd input->RdMOV Rs,Rd 0001 RsRd Rs->RdMOV Rd,X 0010 xxRd X X->RdLOAD Rd,X 0011 xxRd X [X]->RdADD Rs,Rd 0100 RsRd Rs+Rd->RdSUB Rd,X 0101 xxRd X Rd-X->RdJZ X 0110 xxxx X 若ZF=1,X->PC若ZF=0,PC+1->PCJMP X 0111 xxxx X X->pc OUT Rs 1000 Rsxx Rs->output STOR Rs,X 1001 Rsxx X Rs->[X] 机器指令的微操作流程图如下0 1代码文件名为test.txt,其内容如下:$P0000 ; IN R0$P0112 ; MOV R0,R2$P0221 ; MOV R1,0$P0300$P0438 ; LOAD R0,[50]$P0550$P0641 ; ADD R0,R1$P0752 ; SUB R2,1$P0801$P0960 ; JZ NEXT2$P0A0D$P0B70 ; JMP NEXT1$P0C04$P0D80 ; OUT R0$P0E90$P0F40 ; STOR R1,[40]$M00018001 ;00->01$M0101ED82 ;PC->AR,PC+1$M0200C050 ;RAM->BUS,BUS→IR $M10001001 ;INPUT->R0$M11019201 ;RS->RD$M1201ED83 ;PC->AR,PC+1$M03009001 ;RAM->BUS,BUS->R1$M1301ED84 ;PC->AR,PC+1$M0400A005 ;RAM->BUS,BUS->DR1$M0501B206 ;RS->DR2$M0695EB47 ;DR1+DR2->AR$M07009001 ;RAM->BUS,BUS->RD$M1401A408 ;RS->DR1$M0801B209 ;RD->DR2$M09959B41 ;[DR1]+[DR2]->RD$M1501ED8A ;PC->AR PC+1->PC$M0A00B00B ;RAM->BUS BUS->DR1$M0B01A40C ;RD->DR2$M0C619B41 ;[DR1]-[DR2]->RD$M1601ED8D ;PC->AR PC+1->PC$M0D00D0E0 ;RAM→BUS,BUS→PC,P(3)$M3000D181 ;RAM->BUS BUS->RD$M20018001 ;空操作$M1701ED8E ;PC->AR PC+1->PC$M0E00D181 ;RAM->BUS BUS->PC$M18030201 ;R0->OUTPUT$M1901EDB1 ;PC->AR PC+1->PC$M3100E032 ;RAM->BUS BUS->AR$M32028201 ;RS->BUS BUS->RAM五、实验步骤:(1)按照下图,在实验联接器件。

RISC模型机的设计及实现

《计算机组成与系统结构》课程设计报告报告题目:RISC模型机的设计及实现作者所在系部:计算机科学与工程系作者所在专业:计算机科学与技术作者所在班级:0作者姓名:0指导教师姓名:0完成时间:0目录目录 (1)内容摘要 (2)关键词 (2)课程设计任务书 (3)第1章绪论 (4)1.1 设计地点 (4)1.2 设计目的 (4)1.3 设计内容 (4)1.4 实验的环境: (4)第2章基础知识 (5)2.1 概述 (5)2.2 主要技术要点 (6)2.2.1 ALU部件 (6)2.2.2. 存储体 (6)2.2.3 控制器 (6)第3章系统设计与实现 (7)3.1 模型机结构 (7)3.2 程序设计原理 (7)3.2.1 数据格式及指令格式 (7)3.2.2 指令系统 (8)3.3 机器指令设计 (9)3.4 联机实验 (10)3.4.1 实验连线 (10)3.4.2 实验步骤 (10)3.4.3 实验测试: (12)第4章实验总结 (13)参考资料 (13)内容摘要计算机系统是包括计算机硬件和软件的一个整体,两者不可分割,但处于不同的层次上。

计算机系统的层次结构模型中,第0层是硬件内核(逻辑线路),第1、2层是指令系统和实现该指令系统所采用的技术(组合逻辑技术、微程序控制技术、PLA控制技术),第3、4层为系统软件,第5层为应用软件,第6层是系统分析。

计算机组成原理涉及到的是第0、1、2这3层。

本次计算机组成原理的课程设计主要是实现一个较完整的模型机,在实验中了解,熟悉完整的单台计算机基本组成原理,掌握计算机中数据表示方法、运算方法、运算器的组成、控制器的实现、存储器子系统的结构与功能、输入/输出系统的工作原理与功能。

以及增强自己的动手能力。

课设主要依托组成原理实验室设备EL-JY-II来完成的,在实验当中利用了实验设备厂商开发的工具以及部分源程序代码。

在此说明。

在实验中我要感谢杨老师的辛勤付出,每天来到实验室指导我们进行实验,在此特别提出感谢。

硬件课程设计报告

课程设计报告课程名称:计算机硬件系统设计课程设计实验地点:专业班级:学号:学生姓名:指导教师:成绩:2013 年6 月24日至2013年7 月5日目录计算机组成原理部分 (1)复杂模型机的设计与实现 (1)一、设计目的 (1)二、实验设备 (1)三、设计要求 (1)四、设计内容 (6)五、程序代码 (12)计算机接口部分 (13)汽车信号灯控制系统 (13)一、设计目的 (13)二、实验环境 (13)三、设计要求 (13)四、设计内容 (14)五、程序代码 (18)总结与心得 (24)计算机组成原理部分复杂模型机的设计与实现一、设计目的综合应用所学计算机组成原理和汇编语言知识,设计并实现较为完整的模型计算机,培养学生独立分析和设计计算机硬件系统的能力。

二、实验设备1. 硬件环境:Dais-CMB+计算机组成原理教学实验系统一台,排线若干,PC机。

2. 软件环境:操作系统,Dais-CMB+应用软件。

三、设计要求3.1、设计任务1. 熟悉实验环境,即实验中涉及的硬件和软件,掌握这些环境工具的功能和使用方法。

本实验中主要是Dais-CMB+软件及其工作环境。

Dais-CMB+计算机组成原理教学实验系统一台,排线若干。

连接方法是:用二芯排线把位于实验装置左上方运算器的左下侧CYCZ接口与位于实验装置红色拨码开关右下方的FCFZ接口相连接。

在联机状态下,首先应打开mXj.abs,然后点击“!”图标进入链接装载,一旦屏幕自动弹出动态调试窗口表示代码及微代码下载已成功,已进入windows在线集成调试环境。

2. 综合应用所学计算机原理知识,设计并实现较为完整的模型计算机。

3. 使用模型计算机指令编制程序完成下列功能之一:(1)乘法运算。

(2)除法运算。

(3)连加和连减运算。

4. 将程序译成二进制代码,并将二进制代码写入主存。

3.2、拟定数据格式及指令系统1.数据格式模型机规定采用定点补码表示数据,且字长为8位,其格式如下:其中第7位为符号位,数值表示范围是:-128≤X≤127(定点整数),-1≤X<1(定点小数)。

基于RISC

基于RISC芯片指令集是计算机软硬件之间的沟通语言,指令集架构是打通软硬件之间的桥梁。

目前的主流指令集包括Intel的X86、ARM等,在日常生活中最为常见的是使用X86的电脑芯片,以及使用ARM的移动设备芯片。

但这些处理器指令集架构较为复杂,并且有相关知识产权的限制,因此ACM图灵奖获得者、伯克利大学教授David Patterson主导了RISC-V指令集技术。

RISC-V和以往商业指令集最大的差异化,体现在RISC-V可以被任何学术机构和商业组织免费使用,而以往的ARM架构都是要授权付费的。

但值得注意的是RISC-V并不是第一个开源的处理器指令集架构,以往开源的指令集有OpenRISC和SPARCV8等。

但OpenRISC和SPARC V8指令集都未被业界广泛采纳,设计已经相当陈旧落伍。

即便是比较流行的X86和ARM,其指令集架构设计也有十年以上的历史,代表了上个世代的处理器内核。

因此免费开源只是RISC-V可以成为通用处理器架构的一个基本条件,此外RISC-V指令集架构还具备模块化、极简和可扩展的特点,强调通用内核与专用内核之间的融合,立足于新一代的内核技术发展趋势。

由于其免费和指令集设计的自身优势,很多大公司都在为其站台,包括西部数据、英伟达、三星、Ceva等。

同时RISC-V已有流片样品出来了,此前的开源指令集架构的实现基本上只限于FPGA上。

RISC-V的出现和壮大对于中国芯片产业来说,意义重大。

目前国产芯片基本均使用的是国外的指令集架构,但国外的指令集架构本质上是一种授权付费的,或者根本不开放,很难实现国产自主。

飞腾、展讯、华为、华芯通使用的是ARM指令集,北大众志、兆芯、海光使用的是Intel X86,龙芯、君正使用的是MIPS。

而RISC-V是一个全球范围通用的免费开源指令集架构,其生态也在不断壮大,因此RISC-V是有望实现国产自主的指令集架构。

36氪近日接触到的新帆就是基于RISC-V自主设计芯片内核。

基于RISC的模型CPU CORE设计

摘要与CISC(Complex Instruction Set Computer 复杂指令集的计算机)CPU、超长指令集(VLIW)CPU相比,RISC (精简指令集计算机 Reduced Instruction Set Computer)CPU 注重从提高执行指令效率的角度出发,更致力于一个时钟周期内执行,格式简单指令的开发。

通过优先选取使用频率高的简单指令,避免复杂指令,将指令长度固定,减少指令格式和寻址方式种类等方法来提高运算速度。

本文详细介绍了16位RISC CPU的设计过程,本文的设计方法是:把CPU 划分为控制单元、运算单元、存储单元、输入输出单元等几个模块,分别进行设计,首先设计各个模块中各器件元件的内部结构图,确定变量,以及各个单元的VHDL代码,然后设计指令系统,本文共设计了21条指令,分别包括运算指令、传送指令、比较指令、转移指令、输入输出指令、处理机控制类指令等。

在设计过程中以硬布线控制逻辑为主,不用或者少用微码控制等措施,采用由CPU整体系统设计到划分的各个模块的方法来实现功能划分。

本文使用的开发工具是Quartus Ⅱ,从模块设计到VHDL代码编写,在到指令的操作码的实现等都是在Quartus Ⅱ软件实现的。

最后用Quartus Ⅱ中的仿真功能,对设计的系统中的各个模块分别进行功能仿真,以检查设计的各个单元是否能够满足要求,是否能够实现各条指令的功能等。

本文设计中也使用了两级流水线来提高系统在执行指令时的效率。

关键词:RISC CPU ;VHDL ;功能仿真;指令系统;Quartus ⅡABSTRACTCompare to CISC (Complex Instruction Set Computer Complex Instruction Set Computer) CPU, VLIW (VLIW) CPU , RISC (reduced instruction set computer Reduced Instruction Set Computer) CPU to execute instructions to improve the efficiency of focus from the point of view, but also to In a single clock cycle execution, the format development of simple instructions. High frequency of use by giving priority to select the simple instructions, to avoid complex instructions, the instruction length is fixed, reduced instruction formats and addressing modes and other types of methods to improve processing speed.This paper describes a 16-bit RISC CPU design process, this design method is: the CPU is divided into the control unit, operation unit, storage unit, input and output units, and several other modules were designed, first of all the various components of each module design Components of the internal structure to determine the variables, and the VHDL code for each unit, and then design instruction, this paper designed a total of 21 instructions, respectively, including the operation instructions, transfer instructions, compare instructions, transfer instructions, input and output instructions, processor control Class instruction and so on. In the design process to hard-wired control logic oriented, not less microcode or control measures, used by the CPU to the overall system design approach by the various modules to achieve the function of division.Development tools used in this article is Quartus Ⅱ, VHDL code from the module design to writing, to the instruction opcode in the implementation of the software are all implemented in the Quartus Ⅱ. Finally, the simulation function Quartus Ⅱ, the design of the system, each module in the functional simulation, respectively, to check whether the design can meet the requirements of each unit, whether it can achieve the functions of the instruction. This design also uses a two-stage pipeline to improve the efficiency in the implementation of instruction. Key words: RISC CPU; VHDL; functional simulation; command systems; Quartus Ⅱ目录1 绪论 (1)1.1 CPU发展现状 (2)1.2 RISC CPU的应用 (3)1.3 本文主要工作 (3)2 CPU内部结构 (4)2.1 设计思想 (4)2.2 RISC 结构采用的基本技术 (5)2.3 控制单元 (5)2.3.1 指令寄存器 IR (6)2.3.2 程序控制器 CTRL (6)2.3.3 程序计数器 PCount (7)2.4 输入输出单元 (8)2.4.1 输入控制器 DataIN (8)2.4.2 输出控制器 DataOUT (8)2.5 存储单元 (9)2.5.1 指令内存 Pmar、Pcache (9)2.5.2 数据内存 DMAR DCACHE (10)2.5.3 指令缓冲器 IBUFFER (10)2.6 运算单元 (11)2.6.1 累加器 A (11)2.6.2 运算器 ALU (11)2.6.3 寄存器 B (13)3 指令系统 (14)3.1 概述 (14)3.1.1 指令格式 (14)3.1.2 寻址方式 (15)3.2 指令功能和类型 (15)3.2.1 算术运算指令 (15)3.2.2 逻辑运算指令 (16)3.3 输入输出指令 (18)3.4 数据传送指令 (19)3.4.1 读内存指令 (19)3.4.2 寄存器之间数据传送指令 (20)3.5 转移指令 (20)3.6 比较指令 (21)3.7 系统控制类指令 (22)3.8 逻辑控制电路设计 (23)3.8.1指令流程图 (23)3.8.2 微命令逻辑表达式 (26)3.8.3 指令译码的逻辑实现 (27)4 功能仿真 (28)4.1 功能仿真环境简介 (28)4.1.1 波形图的建立 (28)4.1.2 功能仿真过程 (29)4.2 程序计数器(PCount)的功能仿真 (29)4.3 控制单元功能仿真 (31)4.3.1 指令寄存器(IR)功能仿真 (32)4.3.2 控制器(CTRL)功能仿真 (33)4.4 运算单元的功能仿真 (34)4.4.1 累加器A的功能仿真 (35)4.4.2 寄存器B的功能仿真 (35)4.4.3 ALU的功能仿真 (36)4.5 存储单元的功能仿真 (38)4.5.1 指令存储器的功能仿真 (39)4.5.2 数据存储器的功能仿真 (39)结束语 (41)参考文献: (42)附录 (43)附录一:CPU设计总图 (43)附录二:CPU连线图 (44)致谢 (59)1 绪论随着计算机的发展,自动化、智能化的程度越来越高,强大的功能也带来了硬件结构的更加复杂。

基于RISC处理器模型机的设计

基于RISC处理器模型机的设计

王冬

【期刊名称】《中国水运(下半月)》

【年(卷),期】2009(009)002

【摘要】介绍了RISC机的工作特性,讨论了RISC设计的一般原则,以及进一步应用VHDL在MAX+plusII 的环境下设计RISC处理器模型机,以实现具有高效率、不断流、指令并行度ILP较高的处理器.

【总页数】3页(P113-115)

【作者】王冬

【作者单位】塔里木大学,信息工程学院,新疆,阿拉尔,843300

【正文语种】中文

【中图分类】TP15

【相关文献】

1.基于RISC处理器模型机的设计 [J], 王冬

2.基于RISC处理器PowerPC405EP的网络打印机控制器设计 [J], 杨凡

3.基于64位RISC处理器的片上系统芯片(SOC)设计及应用简介 [J], 王一利;施冬云

4.基于现场可编程门阵列的RISC处理器设计 [J], 东野长磊

5.基于RISC处理器与Qtopia的智能家居设计 [J], 黄根勇;

因版权原因,仅展示原文概要,查看原文内容请购买。

基于RISC架构的微处理器DXP-1结构与控制设计的开题报告

基于RISC架构的微处理器DXP-1结构与控制设计的开题报告1.项目背景微处理器是现代计算机技术的基础,其发展历程已经经历了数十年,其性能和使用范围得到了极大的提升和拓展。

在众多微处理器中,基于精简指令集计算机(RISC)架构的微处理器以其高效的指令集和架构设计,在很多计算机领域得到了广泛应用。

因此,该课题旨在设计一款基于RISC架构的微处理器DXP-1,从架构设计到控制逻辑实现,最终呈现一个完整的微处理器原型。

2.研究内容本课题主要研究内容包括以下几个方面:(1)RISC架构设计:结合RISC架构的特点,设计处理器指令集、寄存器、流水线结构等特性,保证微处理器的高效性和功能性。

(2)微处理器控制逻辑设计:根据RISC架构的指令执行流程和处理器结构,对微处理器进行控制逻辑设计,实现指令译码、执行、转发等功能。

(3)系统总体设计:概述处理器的总体结构和工作流程。

包括指令流水线和控制单元的互动、数据寄存器和内存的交互以及运算器和指令编码的互联实现。

3.研究意义(1)对RISC架构的微处理器进行研究,能够提高计算机领域的理论知识水平,并推动计算机科学的发展。

(2)通过对微处理器控制逻辑设计的研究,可以深入理解微处理器底层的运行机制,提高对控制逻辑的理解和应用能力。

(3)构建一款RISC架构的微处理器DXP-1,是未来嵌入式系统开发和计算机体系结构研究中的弥足珍贵的资源和实验平台。

4.研究方法本课题主要采用以下研究方法:(1)文献调研:阅读大量的相关文献,对RISC架构、微处理器控制逻辑和流水线结构进行深入的理论学习。

(2)理论分析:对所学知识结合实际需求,对处理器的设计、控制逻辑、流水线结构等进行理论上的分析和讨论。

(3)硬件实现:采用硬件描述语言,如Verilog或VHDL,将理论设计转化为硬件实现的语言描述,并通过EDA软件进行仿真和测试。

5.预期成果(1)设计出一款基于RISC架构的微处理器DXP-1,包括指令集、寄存器、数据通路等设计,实现一定的运算和数据存储功能。

基于RISC处理器结构的模型机设计

I7,I6,I5,I4,I3,I2,I1,I0

PIN ;

PC_B, ALU_B ,CS,WR

PIN ;

LD,LDAR,LDAC,LDIR,LDPC PIN ;

CLR, R0_B,R1_B,R2_B

PIN ;

LDDR, LDR0,LDR1,LDR2 PIN ;

MOV,ADD,JMP,LOAD,STA NODE ISTYPE 'COM' ;

对原理图及ABEL语言程序都要进行编译,双击选中对象右侧的Compile命令,通过会显示绿色的对号,最终生成扩展名为jed的文件

LDDR, LDR0,LDR1,LDR2 PIN ;

WR =!(T3&STA&F); ABEL程序的基本格式 (1)选用使用频率比较高的五条基本指令:MOV、ADD、STORE、LOAD、JMP。 四、具体实验步骤及结果分析

PC_B =(!T1&!(LOAD&T3)&!(STA&T3))#F; CS =(!T2&!F)#(!T1&!(T2&LOAD)&!(T3&STA)&F); LDIR =T3&!F; LDPC =!T2&!(JMP&T3); LDDR =(!ADD&T4); ALU_B =!(ADD&T4); WR =!(T3&STA&F); LD =!(JMP&(T3#T4))#F; LDAR =T2#LOAD&T4&!F#STA&T4&!F; RS_B =((!(MOV&T3)&!(ADD&T3)&!(JMP&(T4#T3)))&!F)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬件课程设计报告姓名:学院:计算机科学与技术专业:网络工程时间:2010年12月17日题目:基于RISC处理器结构的模型机一、设计目的随着计算机技术要求的不断发展,为增强计算机系统的功能,简化编译器的工作量,更好的改善计算机的性能,减少系统的辅助开销,提高计算机的运行速度和效率,计算机结构设计者一直在致力研究为系统结构提供更好的硬件支持。

设计RISC及其一般遵循以下原则:1、确定指令系统时,选取使用频率最高的一些简单指令,以及很有用但不复杂的指令。

2、指令长度固定,指令格式限制在1-2种之内,大大减少指令系统的寻址方式,一般不超过2种。

3、大部分指令在一个及其周期内完成。

4、只有取、存指令可以访问存储器,其他指令的操作一律在寄存器间进行,大大增加寄存器的数量。

5、一硬布线控制为主,很少户不用微程序控制。

6、特别重视编译优化工作,支持高级语言的实现。

二、设计内容与要求1、选用使用频率比较高的五条基本指令:MOV ADD STORE LOAD JMP,成功执行后添加一条指令,如:SUB。

2、寻址方式采用寄存器寻址级直接寻址两种方式。

3、指令格式采用单字长级双字长两种格式。

4、设计不采用微程序,在CPLD中设计控制逻辑。

单字长指令格式:操作码RS RD双字长指令格式:操作码RS RDADDR其中RS RD为不同状态,则选中不同的寄存器:RS或RD 寄存器00 R001 R110 R211 AC指令系统如下:MOV RS, RDADD RS,RDJMP RSLOAD [ADDR] ,RDSTORE RS,[ADDR]MOV ADD JMP三条指令为单周期执行完成,STORE LOAD两条指令为两周期执行完成,ADDR为存或取数的直接地址。

第一及其周期完成取操作码、作标记;第二机器周期完成取直接地址并完成取数或存数。

5、CPLD芯片设计顶层模块电路图(top.sch)6、RISC模型机的连线图三、设计原理目前在RISC处理机中主要采用如下的技术:1、延时转移技术在RISC处理机中,指令一般采用流水线方式工作。

取指令和执行指令并行运行。

如果取指令和执行指令需要一个周期,那么,在正当情况之下,每个周期就能执行完一条指令。

人后,在遇到转移指令时,流水就有可能断流。

由于转移的目的地址要在指令执行完后才能产生,这是下一条指令已经取出来了,因此,必须把取出来的指令作废,并按照转移地址重新取出正确的指令。

为解决上述问题,可以使比一期自动调整指令序列,在转移地址后插入一条有效的指令,而转移指令好像被延迟执行了,这种技术成为延迟转移技术。

2、重叠寄存器窗口技术由于RISC程序中有很多的CALL和RETURN指令,因而在执行CALL指令时,必须保存现场,另外,还要把执行子程序的参数从主程序中传输出去,在执行RETURN指令时,要把保存的结果传输加主程序。

为了尽量减少访问存储器的次数,在RISC处理机中采用重叠寄存器宣传品技术。

3、硬连实现为主,微程序固件为辅主要采用硬联逻辑来实现指令系统,对于那些必须的少量的复杂指令,可以采用微程序实现。

微程序便于实现复杂指令,便于修改指令系统,增强了机器的灵活性和适应性,但执行速度低。

4、强调优化编译系统设计编译器必须努力优化寄存器的分配和使用,提高寄存器的使用效率,减少访问存储器的次数,为了使RISC处理机中的流水线高效率的工作,尽量不断流,编译器不必分析所放弃的数据流和控制流,当发现有可能断流时,要调整指令序列,对有些可以通过流量重新命名来消除数据相关的,要尽量消除,这样,可以提高流水线的执行效率,缩短程序的执行时间。

四、设计结果及分析1、指令执行流程2、RISC数据通路3、ABEL程序的基本格式Module 模块名//模块开始[title '标题说明'][Declarations] //说明部分[器件名device '器件的工业标号' ;][低层模块名INTERFACE(输入->输出);][例化名FUNCTIONL_BLOCK 低层模块名;]信号名, 信号名pin [引脚号, 引脚号] [istype '属性' ];信号名, 信号名node [istype '属性' ];[常量说明语句;][集合的定义;][宏定义语句;]//逻辑关系描述部分Equations //逻辑方程[truth-table(输入变量-> 输出变量) 真值表;][state-diagram(状态变量) 状态图描述;][test-vectors(输入变量-> 输出变量) 测试向量表;] //测试向量部分end 模块名//模块结束[MODULE低层模块名]……4、PLD的ABEL程序MODULE PLDT1,T2,T3,T4 PIN ;I7,I6,I5,I4,I3,I2,I1,I0 PIN ;PC_B, ALU_B ,CS,WR PIN ;LD,LDAR,LDAC,LDIR,LDPC PIN ;CLR, R0_B,R1_B,R2_B PIN ;LDDR, LDR0,LDR1,LDR2 PIN ;MOV,ADD,JMP,LOAD,STA NODE ISTYPE 'COM' ;RS_B, LDRi NODE ;F NODE ISTYPE 'REG';EQUATIONSMOV=!I6&!I5&!I4;ADD=!I6&!I5&I4;JMP=!I6&I5&!I4;LOAD=!I6&I5&I4;STA=I6&!I5&!I4;F.AR=CLR;F.CLK=!((LOAD#STA)&T4);F:=!F.FB;PC_B=(!T1&!(LOAD&T3)&!(STA&T3))#F;CS=(!T2&!F)#(!T1&!(T2&LOAD)&!(T3&STA)&F);LDIR=T3&!F;LDPC=!T2&!(JMP&T3);LDDR=(!ADD&T4);ALU_B=!(ADD&T4);WR=!(T3&STA&F);LD=!(JMP&(T3#T4))#F;LDAR=T2#LOAD&T4&!F#STA&T4&!F;RS_B=((!(MOV&T3)&!(ADD&T3)&!(JMP&(T4#T3)))&!F)#(!(STA&T3)&F);LDRi=(!(MOV&T3)&!(ADD&T4)#F)&(!(LOAD&T2)#!F);R0_B=RS_B#I3#I2;R1_B=RS_B#I3#!I2;R2_B=RS_B#!I3#I2;LDAC=LDRi#!I1#!I0;LDR0=LDRi#I1#I0;LDR1=LDRi#I1#!I0;LDR2=LDRi#!I1#I0;END5、操作步骤(1)在ispDesignEXPERT系统中建立RISC设计项目,包括顶层模块原理图(top.sch),PLD 子模块程序,经编译,将生成的JED文件下载至CPLD芯片ispLSI1032中。

ispEXPERT使用提示a、建立新设计项目选File->New project->命名b、选择器件在source in project表中双击器件名->选择1K、1032、60、84PLCCc、添加源文件选中器件->选SOURCE的NEW->选AEL_HDL或chematicd、编译、仿真选中源文件->双击右边的Compile logic->选中测试向量文件->双击Compile Test Vectors ->双击Functional Smulation->单击“!”(2)按所给的接线图连接线路。

(3)用所设计的指令系统,编写一段机器指令程序。

(4)运行CMPP20进行联机,进入软件界面,将上述程序装载到实验系统的RAM中。

(5)装载机器指令后,选择RISC通路图,按相应功能键即可联机运行、监控、调试程序。

(6)修改顶层模块电路图(top.sch),添加一条指令SUB。

修改后图如下:6、测试程序$P0030 LOAD [40],R0 [40]->R0$P0140$P0203 MOV RO,Ac R0->Ac$P0310 ADD Ac,R0 R0+Ac->R0$P0440 STORE RO,[0A] R0->[0A]$P050A$P0630 LOAD [41],R0 [41]->R0$P0741$P0820 JMP R0 R0->PC$P4034$P4100五、对这个设计题目的评价该实验连线较复杂,需要仔细与耐心,首次使用ABEL语言、ispEXPERT软件,能使学生对ABEL语言有一定了解,并熟悉ispEXPERT软件的应用,对进一步学习起到启蒙作用。