QUARTUSⅡ10波形仿真(ModelSim)入门教程

Quartus-II调用modelsim仿真方法

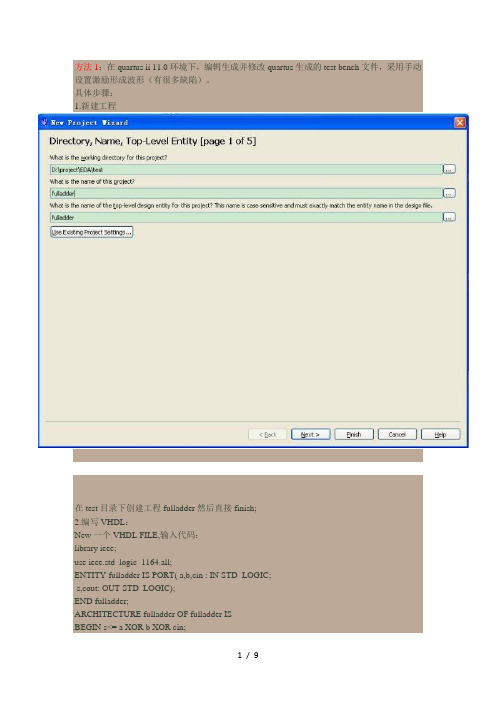

方法1:在quartus ii 11.0环境下,编辑生成并修改quartus生成的test bench文件,采用手动设置激励形成波形(有很多缺陷)。

具体步骤:1.新建工程在test目录下创建工程fulladder然后直接finish;2.编写VHDL:New一个VHDL FILE,输入代码:library ieee;use ieee.std_logic_1164.all;ENTITY fulladder IS PORT( a,b,cin : IN STD_LOGIC;s,cout: OUT STD_LOGIC);END fulladder;ARCHITECTURE fulladder OF fulladder ISBEGIN s<= a XOR b XOR cin;cout <=(a AND b) OR (a AND cin) OR (b AND cin);END fulladder;保存在test目录下,文件名为默认fulladder。

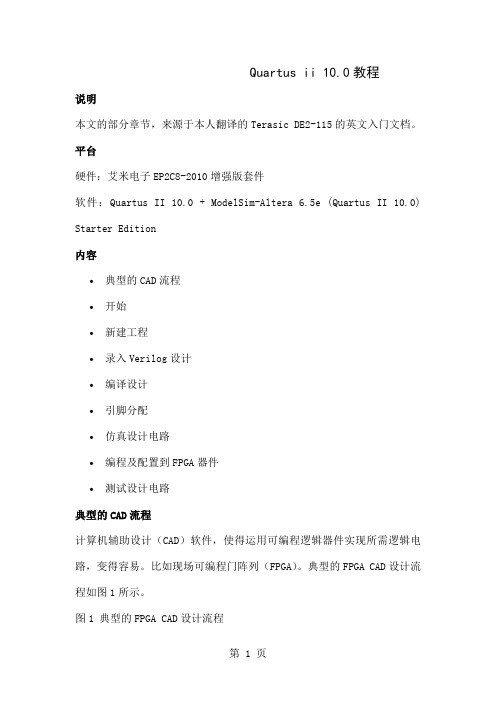

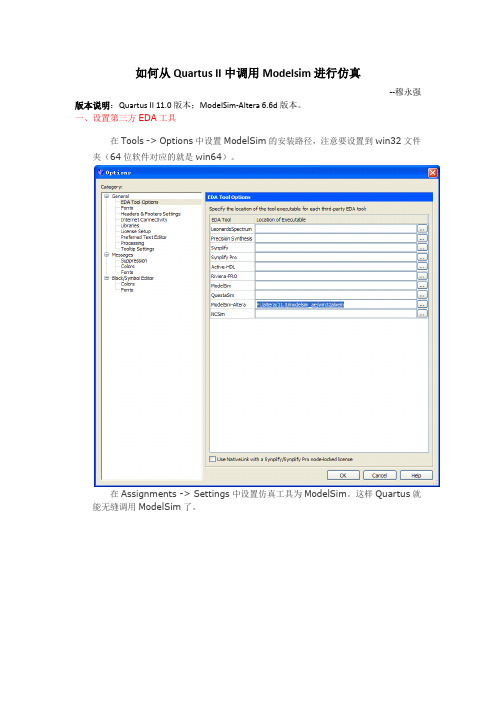

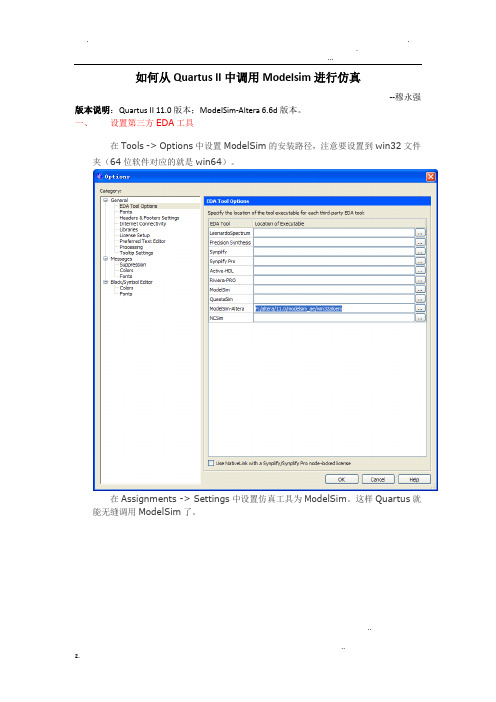

3. 在Quartes II 11.0界面菜单栏中选择 Tools-->options选项卡中选中EDA tool options,在该选项卡中下面的ModelSim-Altera一项指定安装路径为(如d:/Altera/11.0/modelsim_ae/win32aloem)4.在Quartes II 11.0界面菜单栏中选择Assignments->Settings。

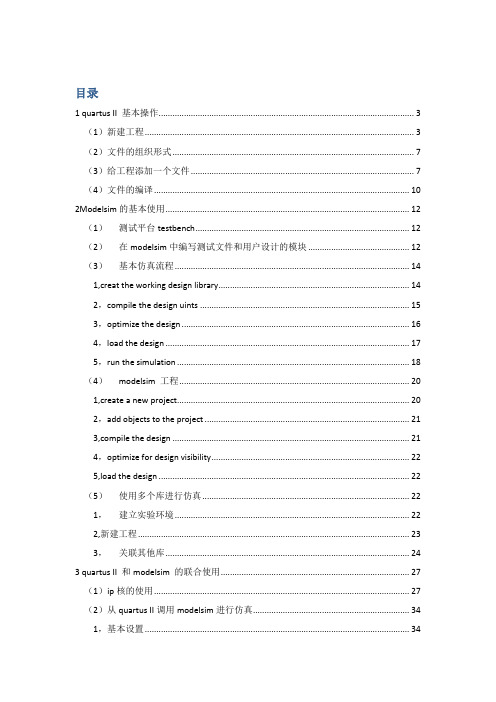

选中该界面下EDA Tool settings中的Simulation一项;Tool name中选择ModelSim-Altera;Format for output netlist中选择开发语言的类型VHDL或其它,如图:然后点击APPLY应用和OK。

5.设置完成后,编译工程:在Quartus II 11.0界面菜单栏中选择菜单栏选择Processing-->start Compilation,等待编译,无错后会在test目录下生成simulation目录,执行下一步。

Quartus调用ModelSim仿真教程

选择 Specify Design Unit 工作库下的目标文件,点 Next,出现下面对话框

可以指定 Testbench 的名称以及要编译到的库等, 此处我们使用默认设置直接点 Finish。 这时在 Testbench 内会出现对目标文件的各个端口的定义和调用函数

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

5.4 编译待测文件

9 ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ @ 珠联璧合 xlzhu xlzhu@

调用 Model Sim 仿真教程 Quartus Quartus调用 调用Model ModelSim Sim仿真教程

2.3 破解详解 (1)产生 License 运行安装文件夹的 crack 目录下的 keygen.exe 文件,点击 generate

生成 license.dat 文件

(2)拷贝 License 文件到安装目录 将生成的 license 文件复制到 modelsel se 的安装目录 D:\Modeltech_6.0\win32 下。 (3)建立环境变量 右键点击桌面我的电脑图标,属性->高级->环境变量->(系统变量)新建。按下图所示 内 容 填 写 , 变 量 值 内 如 果 已 经 有 别 的 路 径 了 , 请 用 “;” 将 其 与 要 填 的 路 径 分 开 。 \license.dat LM_LICENSE_FILE = D:\Modeltech_6.0\win32 D:\Modeltech_6.0\win32\license.dat

安装目录下有安装文件 mti60se 和破解文件夹 crack。 破解文件夹内存放 keygen 和安装 说明。

如何能从Quartus II中调用Modelsim进行仿真

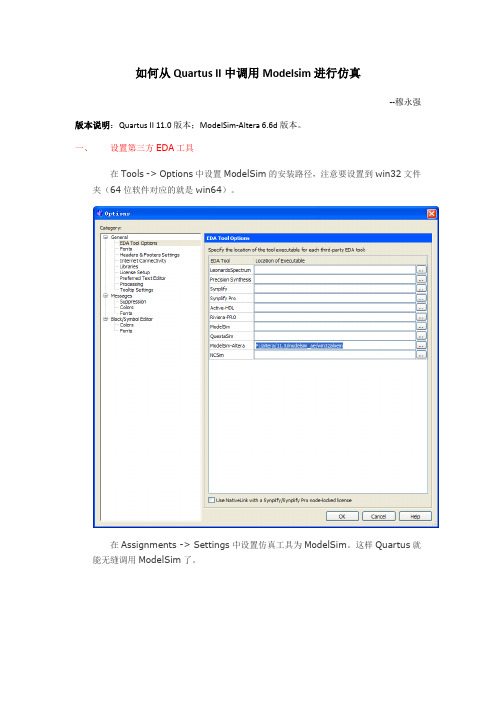

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\modelsim文件夹下的.vt格式文件。

打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

quartus的modesim仿真过程

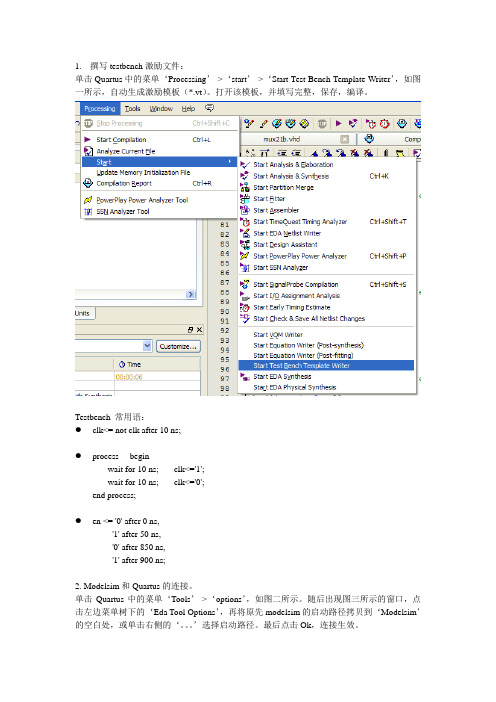

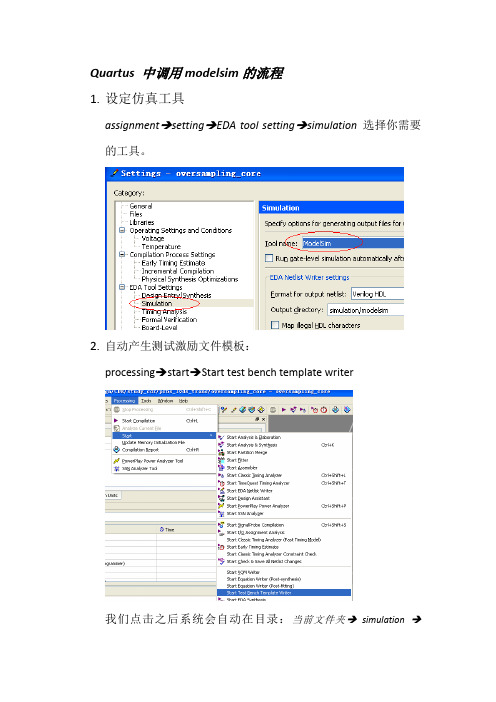

1.撰写testbench激励文件:单击Quartus中的菜单‘Processing’->‘start’->‘Start Test Bench Template Writer’,如图一所示,自动生成激励模板(*.vt)。

打开该模板,并填写完整,保存,编译。

Testbench 常用语:●clk<= not clk after 10 ns;●process beginwait for 10 ns; clk<='1';wait for 10 ns; clk<='0';end process;●en <= '0' after 0 ns,'1' after 50 ns,'0' after 850 ns,'1' after 900 ns;2. Modelsim和Quartus的连接。

单击Quartus中的菜单‘Tools’->‘options’,如图二所示。

随后出现图三所示的窗口,点击左边菜单树下的‘Eda Tool Options’,再将原先modelsim的启动路径拷贝到‘Modelsim’的空白处,或单击右侧的‘。

’选择启动路径。

最后点击Ok,连接生效。

图二图三3. 设置编译信息。

单击Quartus中的菜单‘Assignment’->‘Settings’,如图四所示。

随后进入图五所示的Settings 界面,点击左侧菜单树‘EDA Tool Settings’下的‘Simulation’,右边的窗口出现Simulation 界面,并进行如图五的设置。

其中点中‘Compile test bench’左边的圈圈后,再点击右侧的按钮‘Test Benches。

’进入图六所示的界面,点击右上按钮‘New’进入图七所示的‘New Test Bench Settings’界面,填入相关信息:激励文件名(1),激励文件实体名(2),激励文件中的例化名(3),最大仿真时间(4),和激励文件的具体路劲(5)。

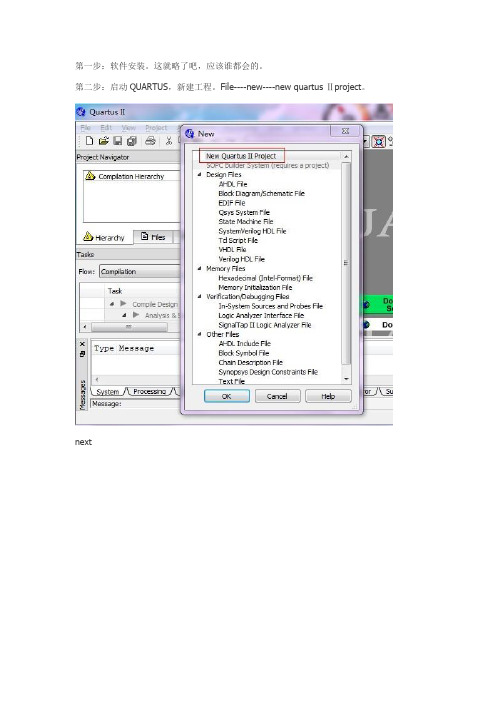

使用QUARTUSⅡ及MODELSIM进行Verilog程序的综合及仿真

第一步:软件安装。

这就略了吧,应该谁都会的。

第二步:启动QUARTUS,新建工程。

File----new----newquartus Ⅱproject。

next下图中,在1处填入工程文件夹(路径中不要使用中文),2处填写工程名,3处填写该工程的顶层模块名(默认情况下工程名和顶层模块名相同),然后NEXT。

下一个对话框是添加已有文件的,没有的话就next。

再下一个对话框是设备设置,可next。

再下一个对话框是仿真设置,这个会在下面详细设置,这里直接next。

然后finish。

第三步:新建Verilog文件。

file---new---verilog HDL file。

然后先保存为adder.v。

第四步:编写程序。

第五步:仿真的设置(重要)。

1.Tools----options----EDA Tool Options,在modelsim后的路径里填入modelsim程序的路径。

2.assignments----setting----EDA Tools Settings----simulation。

在tool name里选择modelsim,format for output netlist里选择verilog HDL,time scale 里根据仿真程序选择。

设置好后勾选compile test bench,然后打开后面的test benches。

3.在TEST benches对话框里点击new。

4.在test bench name中填写仿真模块名,在top level module in test bench中填写仿真模块中的顶层模块名(默认与仿真模块名相同),然后点击下面的File name后文件添加按钮(3),找到你已经编写好的仿真程序,然后点击Add添加。

说明:Quartus中提供了自动生成testbench文件的功能,但内容不全,建议自己编写,保存格式为verilog文件(.v)。

5.一顿点OK,直到回到主界面。

Quartus_ii_10.0教程(包含modelsim仿真)word精品文档12页

Quartus ii 10.0教程说明本文的部分章节,来源于本人翻译的Terasic DE2-115的英文入门文档。

平台硬件:艾米电子EP2C8-2010增强版套件软件:Quartus II 10.0 + ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition内容•典型的CAD流程•开始•新建工程•录入Verilog设计•编译设计•引脚分配•仿真设计电路•编程及配置到FPGA器件•测试设计电路典型的CAD流程计算机辅助设计(CAD)软件,使得运用可编程逻辑器件实现所需逻辑电路,变得容易。

比如现场可编程门阵列(FPGA)。

典型的FPGA CAD设计流程如图1所示。

图1 典型的FPGA CAD设计流程CAD流程包含以下步骤:•设计输入——所需电路可通过原理图方式或硬件描述语言方式(如Verilog或VHDL)进行设计。

•综合——输入的设计被综合进入由逻辑元素(LEs,FPGA芯片提供)组成的电路中。

•功能仿真——综合电路被测试以验证其功能是否正确,次仿真不考虑时序因素。

•布局布线——CAD Fitter工具决定网表中定义的LEs如何布置成FPGA芯片中的实际LEs。

•时序分析——分析已布局布线电路中的不同路径的传播延迟,用以指示所需电路的性能。

•时序仿真——测试已布局布线电路,验证其是否在功能和时序上都正确。

•编程及配置——设计的电路,通过编程配置开关,被实现到一个物理的FPGA芯片。

配置开关用于配置LEs和建立所需线路连接。

本指南介绍Quartus II软件的基本特征。

展示如何使用Verilog硬件描述语言来设计和实现电路。

使用GUI来实现Quartus II指令。

通过本份指南,读者将学习到:•新建工程•使用Verilog代码录入设计•将综合的电路布局到Altera FPGA•分配电路的输入输出到FPGA上的指定引脚•仿真设计电路•编程配置艾米电子EP2C8核心板上的FPGA芯片1. 开始在Quartus II中设计的每个逻辑电路或子电路,叫做一个工程。

如何从Quartus II中调用Modelsim进行仿真

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\models im文件夹下的.vt格式文件。

打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

如何从QuartusII中调用Modelsim进行仿真

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

..二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\modelsim文件夹下的.vt格式文件。

..打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

..其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

QUARTUS II10.1调用modelsim仿真

QUARTUS II 10.1调用ModelSim-Altera仿真的过程(以上软件在六维空间上面都有,只有QUARTUS需要破解,破解方法在另外一篇文章中详述)。

我是个菜鸟,刚接触这个QUARTUS仿真,以前的版本都是直接利用自带的仿真软件,建立一个波形文件vector wavefile(后来发现这个文件可以在QUARTUS里面直接转化成TESTBENCH文件),现在10.0以后不支持直接这么仿真了,而是建议用外部的仿真器仿真(不知道我理解的对不对)。

害的我费了老大的劲,关键是我是初级的水平,能不能整点容易的。

废话少说,主要是发泄一下我的积怨。

(本文参考“Quartus II 调用ModelSim 仿真”一文)1.建立工程文件,这个我就不多说了。

网上有很多,不过在这里,我想提示一下就是工程文件名称要跟顶层实体名称一致(如果只有一个文件的话,那么工程名要跟MODUEL(Verilog HDL),ENTITY(VHDL)后面的名称一致,还有一个就是这里要跟文件名一致,这个文件是顶层文件),这个名称一致的问题至关重要,在后面还有很多地方要一致,就是大家记住一句话,所有的MODUEL和ENTITY的名称要和文件名一致,我就是后面TESTBENCH 中的MODUEL名称和文件名称不一致导致我出错好久。

2.建立Verilog文件(此处为顶层文件),文件名要和项目名一致,且和MODUEL名一致。

文件如下:在保存之前:保存之后,是自动添加到项目中的,只要文件名一致:3.设置仿真器:Assignments---settings---这里tool name:Format for output netlist:用哪个选哪个,后面的不用改(这个是综合的时候用的,用于生成网表文件),还有个东西就是TESTBENCH 在后面讲。

这里设置完了之后编译源文件就能在那个目录下面生成simulation\modelsim文件夹。

modelsim怎么仿真波形

modelsim怎么仿真波形ModelSim是一款用于硬件描述语言(HDL)仿真的软件,它支持Verilog、VHDL等多种硬件描述语言。

使用ModelSim进行波形仿真的基本步骤如下:1.新建工程:首先,在ModelSim中创建一个新的工程。

点击左上角的“File”菜单,选择“Project”,然后在弹出的界面中输入工程名字和选择工程路径,点击“OK”完成新建工程。

2.新建或导入工程文件:完成新建工程后,会弹出添加文件界面。

你可以选择“Create New File”来新建工程文件,或者通过“Add Existing File”来加入已有的工程文件。

3.文档编译:添加文件后,文件会有一个问号表示状态未知,需要右键点击选择“Compile all”进行编译。

编译成功后,文档显示为对勾。

4.开始仿真:在“Project”界面点击“Simulate”后,选择“start simulation”。

并选择你的测试文件(tb)作为仿真主文件。

注意,若在“Library”界面直接点击上方的Simulate可能会报错,需要在该界面的work下,选择需要仿真的文件,右键进行Simulate。

5.添加仿真波形:在仿真阶段,会自动出现sim界面。

此时,你需要手动添加观测信号。

在出现的objects窗口中选择你想观察的信号,右键选择“Add to”,然后选择“wave”,再选择“selected signal”。

6.调整仿真时间并运行仿真:你可以设置仿真时间,然后点击仿真图标开始仿真。

仿真结果会在波形窗口中显示出来,你可以放大或缩小波形以便观察。

以上就是在ModelSim中进行波形仿真的基本步骤。

如果你在使用过程中遇到任何问题,建议查阅ModelSim的官方文档或者在线教程,这些资源提供了详细的帮助和指导。

modelsim教程

ModelSim教程简介ModelSim是一种常用的硬件描述语言仿真器,它广泛应用于数字电路设计、验证和测试。

本教程将介绍ModelSim的基本知识和使用方法,帮助读者快速上手ModelSim,并顺利完成数字电路仿真和验证工作。

目录1.安装ModelSim2.创建工程3.设计代码编写4.编译和仿真5.波形查看和分析6.仿真高级特性7.总结安装 ModelSim首先,您需要下载和安装 ModelSim。

您可以从 Mentor Graphics(ModelSim的开发商)的官方网站上找到适用于您的操作系统版本的安装程序。

下载完成后,按照安装向导的提示进行安装,并确保将安装目录添加到系统的环境变量中。

创建工程在开始使用 ModelSim之前,您需要创建一个工程,用于组织和管理您的设计代码。

以下是创建ModelSim工程的基本步骤:1.打开 ModelSim,并选择“File -> New -> Project”。

2.在弹出的对话框中,选择要保存工程的目录和工程名称,并点击“Next”。

3.在下一步中,您可以选择是否添加已有文件到工程中,或者选择直接创建新的设计文件。

完成后,点击“Next”。

4.在下一步中,您可以选择激活某些特性,如代码覆盖率、时序分析等。

完成后,点击“Next”。

5.最后,点击“Finish”来完成工程的创建。

设计代码编写在 ModelSim中,您可以使用HDL(硬件描述语言)编写您的设计代码。

常用的HDL语言包括VHDL和Verilog。

以下是一个简单的VHDL代码示例:-- Counter.vhdentity Counter isport (clk :in std_logic;rst :in std_logic;count :out unsigned(7downto0));end entity Counter;architecture Behavioral of Counter issignal internal_count :unsigned(7downto0); beginprocess(clk, rst)beginif rst ='1'theninternal_count <= (others=>'0');elsif rising_edge(clk) thenif internal_count =8theninternal_count <= (others=>'0');elseinternal_count <= internal_count +1;end if;end if;end process;count <= internal_count;end architecture Behavioral;编译和仿真编译和仿真是在ModelSim中运行设计代码并生成波形的关键步骤。

quartus II和modelsim的基本使用

目录1 quartus II 基本操作 (3)(1)新建工程 (3)(2)文件的组织形式 (7)(3)给工程添加一个文件 (7)(4)文件的编译 (10)2Modelsim的基本使用 (12)(1)测试平台testbench (12)(2)在modelsim中编写测试文件和用户设计的模块 (12)(3)基本仿真流程 (14)1,creat the working design library (14)2,compile the design uints (15)3,optimize the design (16)4,load the design (17)5,run the simulation (18)(4)modelsim 工程 (20)1,create a new project (20)2,add objects to the project (21)3,compile the design (21)4,optimize for design visibility (22)5,load the design (22)(5)使用多个库进行仿真 (22)1,建立实验环境 (22)2,新建工程 (23)3,关联其他库 (24)3 quartus II 和modelsim 的联合使用 (27)(1)ip核的使用 (27)(2)从quartus II调用modelsim进行仿真 (34)1,基本设置 (34)2,仿真 (39)(3)modelsim 直接仿真quartus II的IP核。

(39)1,脚本记录文件 (40)2,仿真需要的库 (51)3,关联库并仿真 (52)我所使用的是quartus II verison 11.1,使用的语言是verilog HDL,打开软件界面如下图所示:1 quartus II 基本操作(1)新建工程选择file菜单下的new project wizard,会弹出如下图所示界面:点击next,来到下面的页面:第一栏要输入的是工程的存储路径,我输入的是:G:/code/verilog test/20150411_basic_tool/t1第二栏是工程的名字:basic_tool第三栏里会自动填入和工程名字一样的字符,默认工程中顶层模块的名字和工程名相同,顶层模块在工程的编写过程中是可以更改的,这个先不用管它。

Quartus 调用modelsim仿真的简单流程

Quartus 中调用modelsim的流程1.设定仿真工具assignment→setting→EDA tool setting→simulation选择你需要的工具。

2.自动产生测试激励文件模板:processing→start→Start test bench template writer我们点击之后系统会自动在目录:当前文件夹→simulation →modelsim (这个文件夹名字跟你选的仿真工具有关) 中产生一个测试激励文件xxx.vt(Verilog test bench) 或者xxx.vht(VHDL test bench), 文件名跟你工程中的Top module 的名字一样,后缀为.vt或者.vht。

3.编辑走动生成的test bench文件我们加入自己需要的激励以及初始化语句,这里我们还要修改test bench的模块名字为tb(我们会看到这个名字和后面的设定有联系)。

4.连接test bench,我们需要从Quartus中自动调用仿真工具,所以需要设定Native Link选项。

a)还是在simulation的设置页面里,设定Native Link对话框中的设定。

我们这里因为需要工具自动调用激励所以选中b)点击右边的Test Benches, 我们需要在这里设定一个相关联的test bench.这里会弹出一个让你指定test bench的对话框,因为我们之前没有指定任何的test bench,所以这里是空白的。

c)指定test bench因为我们是第一次产生test bench,点击new.点击New之后会产生一个New Test bench setting的对话框,在这里你将test bench和你的相应的test bench file 进行绑定。

我们这里在Test bench name的对话框中输入一个名字”my_1st_tb”, 我们将看到,在下面的Top level module in test bench对话框中也自动显示”my_1st_tb”. 注意这个名字应该和你的test bench 中的module name一直,我们之前在第3步的时候将test bench的module name已经改成了tb,所以我们这里应该把对话框中的名字改成tb。

Quartus II 波型仿真

Quartus II 波型仿真

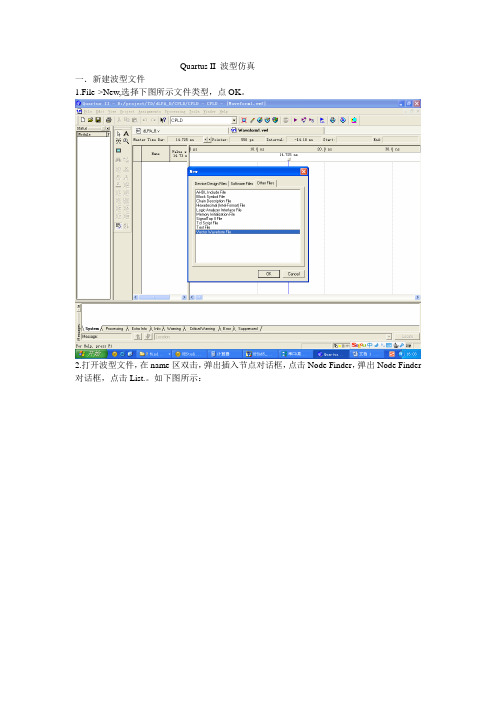

一.新建波型文件

1.File->New,选择下图所示文件类型,点OK。

2.打开波型文件,在name区双击,弹出插入节点对话框,点击Node Finder,弹出Node Finder 对话框,点击List.。

如下图所示:

选中想要查看的输出以及相关的输入,点击>。

全选时,选择>>,同样想取消某个节点时,选择<, 全部取消<<。

3.输入定义及设置

点击OK打开波形定义窗口,在对应的输入名称上,点击右键,选择value,设置输入波形。

或者直接在名称对应的左侧点击需要的波形,

注意CLK时钟信号的设置,根据实际情况设置时钟周期及仿真时间。

时钟结束时间等于Edit 中设置的仿真结束时间。

完成所有的输入设置后,保存文件。

二.仿真

1.。

选择Edit ,设置仿真结束时间,栅格及时间标记条。

根据需要改变栅格的大小,如下图所示:

设置需要查看的时间标记,如下图所示,点击ADD.及OK。

2.设置完成后保存文件,选择编译,编译通过后选择开始仿真。

3. 仿真完成后弹出仿真报告界面。

选择放大镜,单击或右击,来放大或缩小显示的波形。

如下图所示为手动不时分情况下,J5 J6 J7 J8=1101时的波形图,从图中可见,TXVON=1和RXVON=0,功放开,低噪放关。

仿真完成。

王盼

09年4月9日。

modelsim 10仿真教程

Modelsim仿真教程一、前期准备1、正确安装好modelsim和quartus软件。

我用的平台的版本是Modelsim SE10.1和Quartus II10.1。

2、在ModelSim中加入Quartus提供的仿真库在ModelSim中进行仿真需要加入Quartus提供的仿真库,原因是下面三个方面:·Quartus不支持Testbench;·调用了megafunction或者lpm库之类的Altera的函数;·时序仿真要在Modelsim下做仿真。

下面以Altera器件为例,介绍如何在ModelSim中加入Altera的仿真库,Quartus II 软件中自带有Altera的仿真库,只要把它拿到ModelSim中去编译一下就可以了,具体步骤如下:(1).设置仿真库路径打开ModelSim安装目录(我用的是ModelSim SE10.1版本,安装在C:\modeltech_10.1目录下),新建文件夹altera,我们就在该目录下存放预编译的各种Altera库。

启动ModelSim SE,在主窗口执行【File】/【Change Directory】命令将路径转到altera文件夹。

(2).新建库Quartus II中提供的仿真库文件存放的路径是....\altera\10.1sp1\quartus\eda\sim_lib,每个库文件提供了两种形式:.v(Verilog)格式和.vhd(VHDL)格式两种,根据你所用的语言选择使用。

用于编译资源库的文件有220model.v,220model.vhd,220pack.vhd,altera_mf.v,altera_mf.vhd,altera_mf_components.vhd,altera_primitives.v,altera_primitives.vhd,altera_primitives_components.vhd文件。

Quartus 调用ModelSim-Altera进行波形仿真

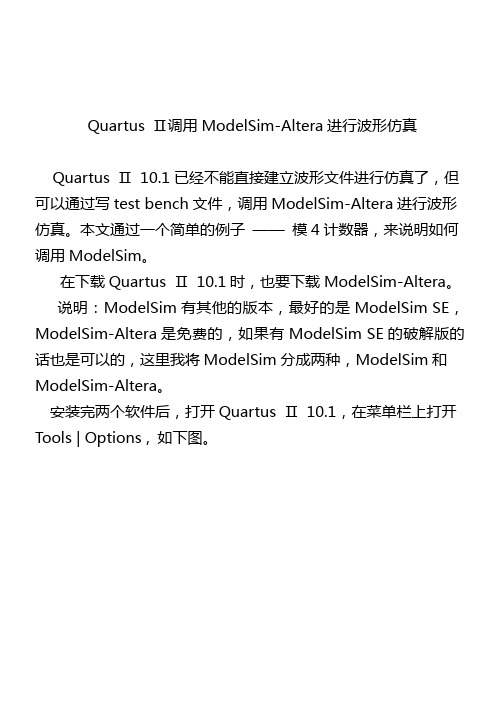

QuartusⅡ调用ModelSim-Altera进行波形仿真QuartusⅡ10.1已经不能直接建立波形文件进行仿真了,但可以通过写test bench文件,调用ModelSim-Altera进行波形仿真。

本文通过一个简单的例子——模4计数器,来说明如何调用ModelSim。

在下载QuartusⅡ10.1时,也要下载ModelSim-Altera。

说明:ModelSim有其他的版本,最好的是ModelSim SE,ModelSim-Altera是免费的,如果有ModelSim SE的破解版的话也是可以的,这里我将ModelSim分成两种,ModelSim和ModelSim-Altera。

安装完两个软件后,打开QuartusⅡ10.1,在菜单栏上打开Tools|Options,如下图。

设置ModelSim.exe的路径,有哪个版本就设置哪个,都有的话都设置。

设置完之后,新建一个工程CNT4。

只进行仿真的话,该页可不设置。

这里可以选择仿真工具ModelSim和ModelSim-Altera(亦可不设置,在后面可以设置),以及语言种类,这里以ModelSim-Altera和VHDL语言为例介绍。

新建一个VHDL文件,代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; ENTITY CNT4ISPORT(CLK:IN STD_LOGIC;Q:OUT STD_LOGIC_VECTOR(3DOWNTO0));END CNT4;ARCHITECTURE BEH OF CNT4ISSIGNAL Q1:STD_LOGIC_VECTOR(3DOWNTO0);BEGINPROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1'THENQ1<=Q1+1;END IF;END PROCESS;Q<=Q1;END BEH;按菜单栏Processing|Start Compilation进行编译,也可以按工具栏上的快捷键。

Quartus系列:QuartusII原理图调用ModelSim进行仿真

Quartus系列:QuartusII原理图调⽤ModelSim进⾏仿真1.新建⼀个⼯程,创建⼀个原理图⽂件,并在其中进⾏原理图电路绘制,本例以⼀个2输⼊与门为例,如下图所⽰:绘制好电路图后,保存绘制好的电路⾄新建的⼯程,如下图所⽰:因为原理图⽂件ModelSim等第三⽅仿真器并不识别,所以需要将其输出为Veilog或者VHDL⽂件,操作如下:点击当前选项后弹出如下对话框,选择要⽣成的对应的硬件描述语⾔⽂件,点击OK按钮完成对应⽂件的⽣成(⽣成⽂件的路径为当前项⽬⽂件夹下),本⽂中以Verilog为例:确认⽂件⽣成后,在⼯程中单击原理图⽂件,将其从当前⼯程中移除后,右击"Files"如下图所⽰:点击选项后,在弹出的对话框中增加⽣成的源⽂件,如下图所⽰:通过上述步骤,即可将源⽂件加⼊到⼯程中.2 选择"Processing"中的"Start Compilation"完成对项⽬的编译。

3 参考“Quartus II 调⽤ModelSim仿真调试”中的步骤,即可完成对应的ModelSim调⽤仿真。

4 如果想使⽤Quartus中的波形⽂件作为调⽤ModelSim的仿真激励,那么只需要注意以下事项:使⽤波形⽂件完成仿真后,⽣成的波形⽂件本⾝是不能为第三⽅仿真⼯具识别,同样需要将其输出为Verilog或者VHDL等格式,如下图所⽰:单击“Export...”在弹出的对话框中保存⽣成的testbench,此时的testbench中即包含了波形仿真时的激励,但是这个testbench的⽂件后缀为“*.vt”。

选择菜单栏下的Assignments->Settings,在弹出的界⾯中选择EDA Tool Settings->Simulation,设置如下图所⽰:其中“3”指定到⽣成的testbench即可。

最后,如果确实不想将原理图转换为Verilog或者VHDL进⾏仿真,即不想将原理图⽂件从项⽬中移除,那么可以只⽣成功能仿真⽹表进⾏仿真,在指定好testbench后,选择"Tools"->"EDASimulation Tool"->"Run EDA Gate Level Simulation"进⾏仿真。

如何在quartusii里使用modelsim

当我们使用 QuartusII,可是大部分朋友都习习用 Modelsim SE来做仿真,因为 Quaruts 有好多自己器件的特点,因此造成了在仿真上的麻烦,自然网路上也有一些解说,可是都是不太系统,特别是对初学者来说,使用的时候仍是感觉一头雾水。

本文的目的就是一个怎样在 Quartus 使用 Quartus 和 Modelsim 仿真的例子。

2.成立 QuartusII 工程。

这里目的不过成立一个很简单很简单的QuartusII 的工程,逻辑采纳原理图方式绘制。

里面就是一个简单的DFF,输入信号:datain , clkdataout3.Quartus II内部时序仿真在 Quartus 内部使用时序仿真,很简单,帮助文件的你能够点击 Help-> Tutorial假如不知道怎样使用请参照帮助文件。

里面有很详尽的怎样创立一个Wave 仿真文件的教程这里就不罗嗦了。

对于怎样仿真这里也不空话了。

我们进入中心问题。

4.Modelsim SE的仿真生成 TestBench 文件因为我们上边已经制作了一个时序仿真文件*.vwf .Quartus II 供给了把这样文件变换成Testbench 的功能。

详细的操作以下:在工程菜单里面双击 *.vwf文件,是之翻开成为目前激活文件。

而后点击菜单Files-> Export会直接翻开一个输出框:我们后边会使用Verilog 文件进行仿真,因此这里把后缀名*;.vt改成为*.VOk 就生成了TestBeanch 文件。

设置启动 Modelsim怎样在 Quartus II 里面使用 Modelsim. 只要要在Assignment->setting里面选择以下的选项,在进行整个工程进行编译的时候会自动调用系统的Modelsim SE .在编译最后会调用Modelsim .点击 Work 你能够看见对于 Altera 的库文件都编译进来了。

下边是要点:新建一个工程文件。

在Quartus中调用Modelsim进行仿真

在QuartusⅡ中调用ModelSim进行仿真Quartus Ⅱ版本:Quartus Ⅱ10.0 (32-bit);安装路径为D:\Myfiles\QUARTUS_10.0 ModelSim版本:ModelSim SE 6.5;安装路径为D:\Myfiles\ModelsimSE一、Quartus设置(1)在QuartusⅡ中指明仿真工具及其路径(2)在QuartusⅡ中编译所需的元器件库二、建立工程及仿真(1)在QuartusⅡ中建立工程counter,并指明仿真工具(2)顶层文件代码(3)激励文件代码(4)在Quartus中添加testbench文件(5)在Quartus中全编译工程(6)前仿真(7)后仿真一、QuartusⅡ的相关设置(1)在QuartusⅡ中指明仿真工具及其路径在QuartusⅡ中执行Tools\Options,打开EDA Tool Options选项卡。

我们使用ModelSim 进行仿真,所以在ModelSim对应的Location of Executable中选择ModelSim的安装路径D:\Myfiles\ModelsimSE\win32,如图1所示:图1(2)在QuartusⅡ中编译所需的元器件库1)在ModelSim安装路径D:\Myfiles\ModelsimSE中新建文件夹modelsimSE_lib,用于存放编译的文件2)在QuartusⅡ10.0中执行Tools\Launch EAD Simiulation Library Compiler,在打开的界面中Executable location一项选择ModelSim的安装路径D:\Myfiles\ModelsimSE\Win32在Avaliable families中根据自己需要选择可能用的到器件系列,如cyclone、stratix等;在这里可以多选择一些,以备能用到,并且一次编译后,以后就不用再编译了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

QUARTUSⅡ10仿真(ModelSim)入门教程平台

软件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition

内容

1 设计流程

使用ModelSim仿真的基本流程为:

图1.1 使用ModelSim仿真的基本流程

2 开始

2.1 新建工程

打开ModelSim后,其画面如图2.1所示。

图2.1 ModelSim画面

1. 选择File>New>Preject创建一个新工程。

打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。

一般情况下,设定Default Library Name为work。

指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。

该对话框如图

2. 2所示,此外还允许通过选择.ini文件来映射库设置,或者将其直接拷贝至工程中。

图2.2 创建工程的对话框

2. 按照图2.3所示,设置Project Name为LED_FLOW,Project Location为D:/led_flow。

图2.3 输入工程信息

当单击OK按钮后,在主体窗口的下方将出现Create Project标签,如图2.4所示。

图2.4 Project标签

3. 之后,将出现Add Items to the Project的对话框,如图2.5所示。

图2.5 在工程中,添加新项目

2.2 在工程中,添加新项目

在Add Items to the Project对话框中,包括以下选项:

∙Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL或文本文件

∙Add Existing File——添加一个已存在的文件

∙Create Simulation——创建指定源文件和仿真选项的仿真配置

∙Create New Folder——创建一个新的组织文件夹

1. 单击Create New File。

打开图

2.6所示窗口。

图2.6 创建工程文件夹

2. 输入文件名称:LED_FLOW,然后选择文件类型为Verilog。

图2.7 输入工程文件信息

3. 单击OK,关闭本对话框。

新的工程文件将会在工程窗口显示。

单击Close,以关闭Add Items to the Project。

图2.8 新的设计文件LED_FLOW.v

4. 双击打开LED_FLOW.v文件(注意:若是Verilog文件已经关联了其他的文本编辑器,则双击后在关联的文本编辑器中打开)。

图2.9 LED_FLOW代码输入窗口

在LED_FLOW.v输入下面的测试平台代码:

`timescale 1ns/1ns

module LED_FLOW;

reg CLOCK_50M;

reg RST_N;

wire [9:0] LED;

led led_inst

(

.clk_50M(CLOCK_50M),

.reset_n(RST_n),

.led(LED)

);

initial

begin

CLOCK_50M = 0;

while (1)

#10 CLOCK_50M = ~CLOCK_50M;

end

initial

begin

RST_N = 0;

while (1)

#10 RST_N = 1;

end

initial

begin

$display($time,"CLOCK_50M=%d RST_N=%d LED =%d", CLOCK_50M, RST_N, LED); end

endmodule

录入完代码后,单击Save。

图2.10 输入testbench代码

5. 选择File>New>Source>Verilog,创建新的Verilog文件,如图2.11所示。

图2.11 创建新的Verilog文件

6. 录入下面的代码,录入画面如图2.12 所示。

`timescale 1ns/1ns

module led(

input clk_50M, // System clock 50MHz input reset_n, // System reset

output reg [9:0] led // led

);

reg [13:0] counter = 0;

reg [3:0] state = 0;

always @ (posedge clk_50M, negedge reset_n)

if (!reset_n)

counter <= 0;

else

counter <= counter + 1'b1;

always @ (posedge counter[13])

if (!reset_n)

state <= 0;

else

begin

if (state == 4'b1001)

state <= 0;

else

state <= state + 1'b1;

end

always @ (posedge clk_50M, negedge reset_n)

if (!reset_n)

led <= 0;

else

begin

case (state)

4'b0000: led <= 10'b00000_00001;

4'b0001: led <= 10'b00000_00010;

4'b0010: led <= 10'b00000_00100;

4'b0011: led <= 10'b00000_01000;

4'b0100: led <= 10'b00000_10000;

4'b0101: led <= 10'b00001_00000;

4'b0110: led <= 10'b00010_00000;

4'b0111: led <= 10'b00100_00000;

4'b1000: led <= 10'b01000_00000;

4'b1001: led <= 10'b10000_00000;

default: led <= 10'b00000_00001;

endcase

end

endmodule

图2.12 录入新文件

7. 选择File>Save,输入文件名:led.v,单击Save,如图2.13所示。

图2.13 保存led.v

8. 选择Project>Add to Project>Existing File,如图2.14所示。

图2.14添加文件到工程中

9. 单击Browse,选择led.v,如图2.15 所示。

图2.15 选择待加入工程的文件

10. 单击打开,在Add file to the project窗口,单击OK。

2.3 编译文件

在Project标签下的Status列的问号,表示文件尚未编译进工程,或者在最后编译前,源文件有所改动。

欲编译文件,选择Compil e<Compile ALL,或者右击Project标签,选择Compile>Compile All。

1. 倘若此处没有错误,编译成功的消息,就会在Transcript窗口如图

2.6所示。

图2.16 编译成功

3 仿真工程

3.1 开始仿真

1. 单击Library图标,选择work,单击+以展开选项,然后选择LED_FLOW。

单击右键,选择编译,如图3.1所示。

图3.1 单击Simulate

2. 单击Simulate,到达图

3.2所示画面。

图3.2 仿真窗口

4. 在图3.2中,单击LED_FLOW,单击右键,然后选择Add>To Wave>All Items in region,然后单击左键。

出现图3.3所示画面。

图3.3 Add To Wave

3.2 仿真设置

1. 完成上述最后一步后,波形窗口出现。

图3.4 波形窗口

2. 在Run Length列输入仿真时间长度为10ms,如图

3.5所示。

图3.5 设置Run Length

3. 单击Run按钮,如图3.6所示。

图3.6 运行仿真

4. 运行若干秒后,将会如图3.9所示的仿真结果。

图3.7 显示仿真结果

5. 连续单击Zoom Out 图标,可查看仿真的完整波形,如图3.8所示。

图3.8 波形窗口

6. 单击鼠标所指的+,展开LED_FLOW的波形,如图3.9所示。

图3.9 展开波形

通过放大/缩小波形,可以观察到LED的值在保持变化,即LED的时序效果。

若将其移植到Quartus II中,适当配置后,经过综合、时序分析、引脚分配、配置及下载等,即可实现跑马灯的效果。

至此,仿真的所有进程完毕。